Изобретение относится к декодированию с низкой плотностью проверки четности, технике моделирования и может быть использовано при цифровом моделировании характеристик помехоустойчивых низкоплотностных декодеров с использованием архитектуры «маркерного кольца» с тактовым стробированием.

Известна архитектура декодера, описанная в патенте США «QC-LDPC decoder, method for performing layered decoding and storage device», US 20200014402 A1, МПК H03M 13/11, опубл. 20.01.2020. Данный декодер содержит аппаратный ускоритель для выполнения части или всех операций обработки информации, включая проверку четности, обновление контрольного узла и обновление узла переменных.

Недостатком способа декодирования QC-LDPC кода, характеризующегося использованием средств программного аппаратного ускорителя для выполнения декодирования QC-LDPC кода (англ. a quasi-cyclic low-density parity-check - квази-циклический код низкой плотности), является то, что аппаратный ускоритель не позволяет распределить пространства хранения для области памяти данных на основе структуры матрицы проверки кода QC-LDPC и установление индекса для адресации данных процессором общего назначения.

Наиболее близким по своей технической сущности к заявленному способу является способ, описанный в патенте Китая «QC-LDPC decoder, method for performing layered decoding and storage device», US 10581460 B2, МПК H03M 13/11, опубл. 03.03.2020. Способ декодирования включает в себя: деление проверочной матрицы закодированного сообщения QC-LDPC на М уровней, где М является положительным целым числом.

Недостатком способа является то, что для реализации декодера тактовая частота для синхронизации строительных блоков применена ко всему декодеру, что увеличивает энергопотребление декодера и может вызывать конфликт доступа к памяти.

Техническим результатом является уменьшения смещения тактовых импульсов и оптимизации энергопотребления. Стробирование тактовой частоты в структурных блоках декодера позволяет значительно снизить энергопотребление без ухудшения других параметров декодера, в частности его производительности исправления ошибок.

Сущность изобретения.

Решаемой технической задачей изобретения является снижение динамического энергопотребления при неизменной пропускной способности декодера.

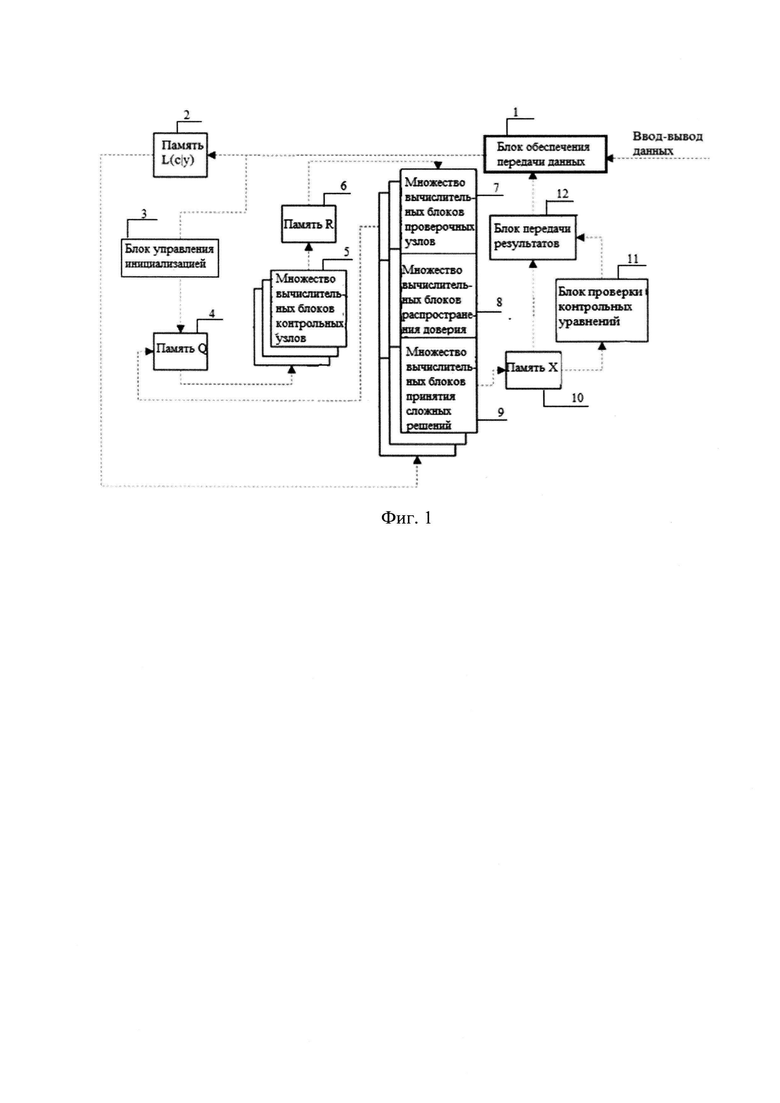

Сущность изобретения поясняется приведенными далее фигурами. На фиг. 1 представлена предлагаемая частично-параллельная архитектура декодера. Такая архитектура QC-LDPC декодера соответствует представлению о сети «маркерного кольца». Гибкость предлагаемой архитектуры обусловлена тем, что можно легко спроектировать декодер для различных параметров матрицы контроля четности. Такими настраиваемыми параметрами матрицы являются: выбор регулярной или нерегулярной структуры матрицы с различной длиной блока (N), кодовой скоростью (R) и размером подматрицы (Р).

Структура декодера состоит из: 1 - блок обеспечения передачи данных, 2 - память L(c|y), 3 - блок управления инициализацией, 4 - память Q, 5 - множество вычислительных блоков контрольных узлов, 6 - память R, 7 - множество вычислительных блоков проверочных узлов, 8 - множество вычислительных блоков распространения доверия, 9 - множество вычислительных блоков принятия сложных решений, 10 - память X, 11 - блок проверки контрольных уравнений, 12 - блок передачи результатов.

Блок обеспечения передачи данных 1 принимает данные, подлежащие декодированию, в виде значения логарифмического отношения правдоподобия (LLR) и сохраняет их в надлежащем порядке в памяти L(c|y)

2. Полученные данные также передаются в блок управления инициализацией 3 декодера, который заполняет память Q 4. Запуск инициализации во время передачи данных позволяет сократить время, за которое QC-LDPC декодер завершает процесс декодирования. После завершения инициализации начинается процесс вычисления сообщений множества вычислительных блоков контрольных узлов 5. Множество вычислительных блоков проверочных узлов 7 получают данные из памяти Q 4, выполняют вычисления и сохраняет результаты в памяти R 6. В разработанной структуре декодера память представляет собой специфический интерфейс между вычислительными модулями. Передача сообщений между узлами осуществляется через память Q 4 (сообщения контрольных узлов) и память R 6 (сообщения проверочных узлов) в соответствии с алгоритмом декодирования min-sum. Окончательный результат декодирования отправляется на выход декодера через блок передачи результатов 12. Сообщение блока передачи результатов содержит счетчик, который увеличивается с каждой итерацией. Если счетчик достигает заданного максимального значения, декодирование прерывается, и декодер сигнализирует об ошибочном результате декодирования.

Предлагаемый способ снижения динамической энергии заключается в следующем.

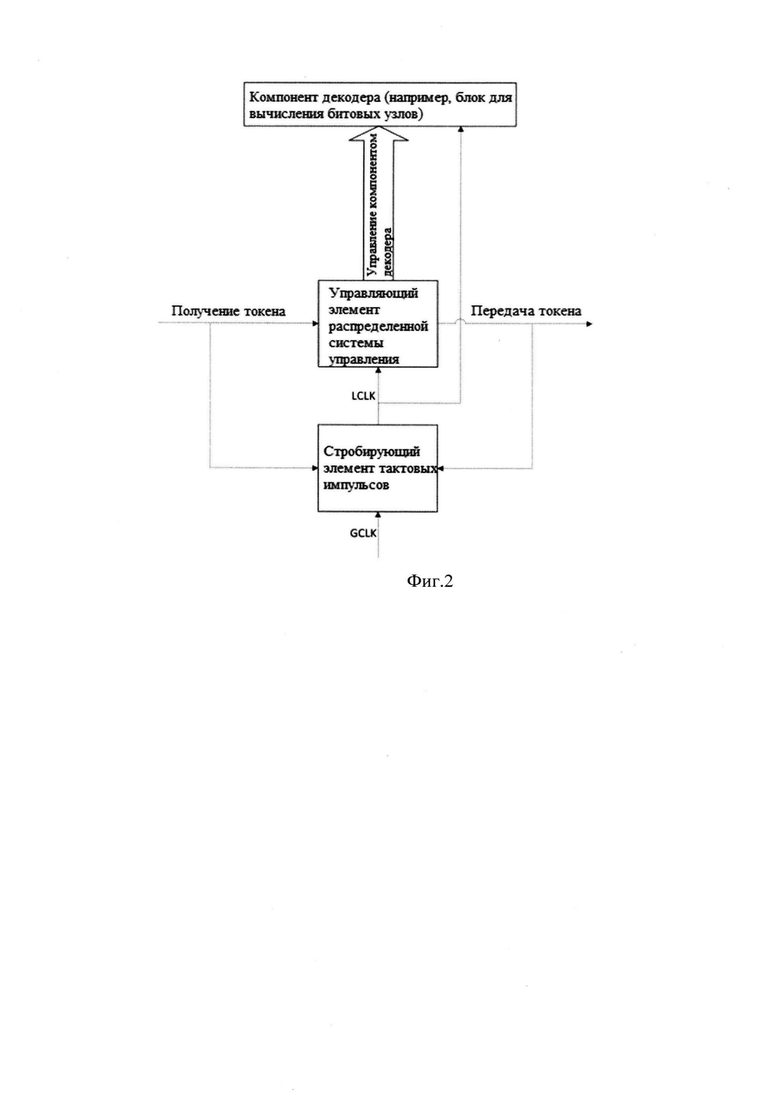

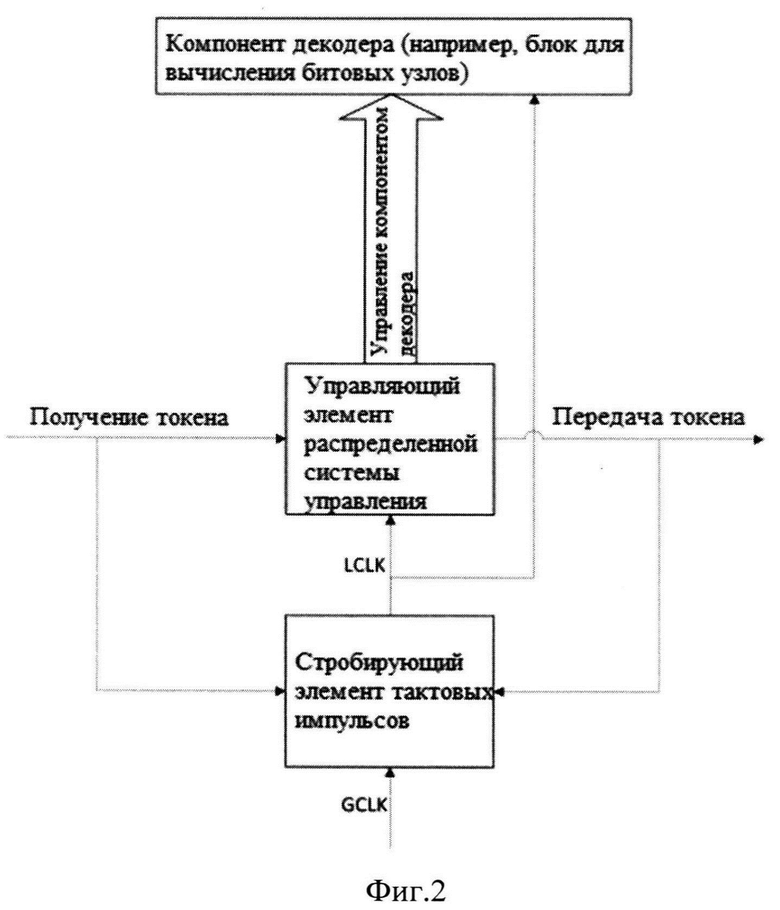

Архитектура «маркерного кольца» с распределенной системой управления реализует синхронизацию модулей, активируя выбранный блок управления с помощью передачи токена, осуществляя вместе с вычислительными элементами, управляемыми этим блоком. После завершения вычислений модуля и передачи токена тактовый сигнал, распространяемый в соответствующем вычислительном блоке, блокируется. На фиг. 2 показана структурная схема тактового стробирования и активации элемента распределенного управления с использованием токена в архитектуре, основанной на кольце токенов.

Сразу после получения токена элемент стробирования тактового сигнала, активирует локальный тактовый сигнал (LCLK), что позволяет разблокировать схему стробирования глобального тактового сигнала (GCLK). LCLK передается элементу распределенной системы управления, который начинает управлять элементом декодера (множеством вычислительных блоков и памятью). В то же время на этот вычислительный блок подается локальный тактовый сигнал LCLK. После завершения локальных вычислений система управления передает токен следующему элементу системы управления и блокирует LCLK. Такая схема обработки позволяет значительно снизить энергопотребление за счет включения тактового сигнала, подаваемого на вычислительную логику, только в нужном временном интервале.

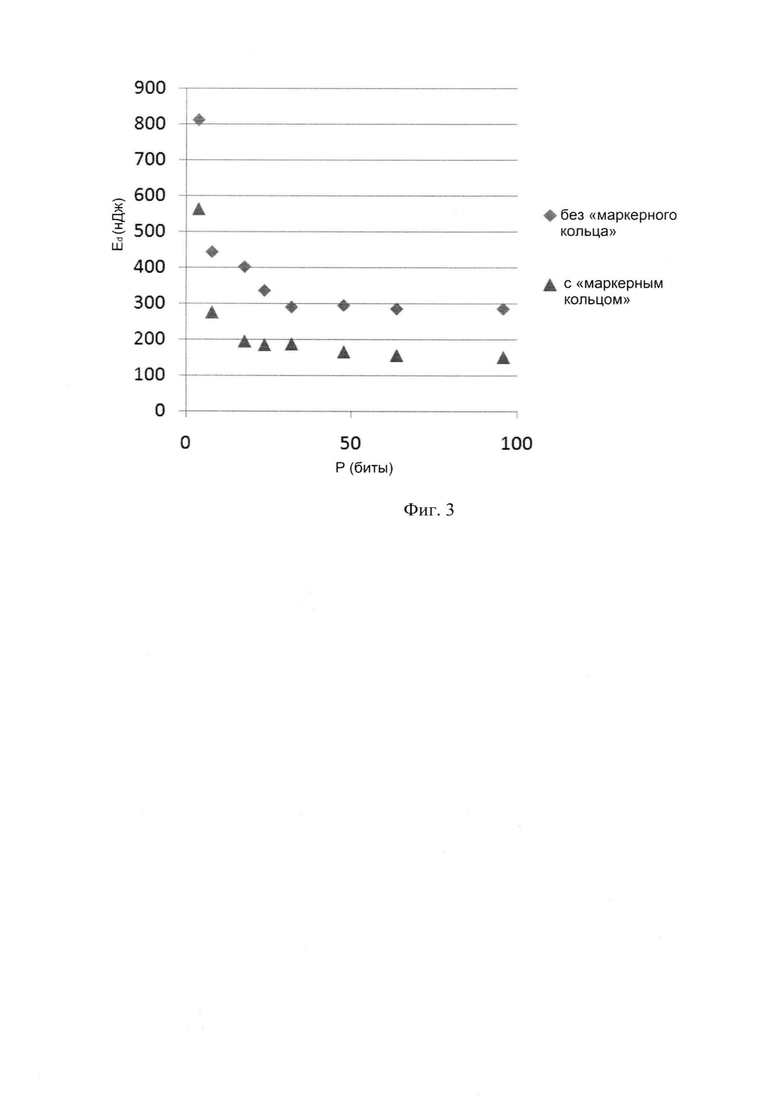

Достигаемое снижение динамической энергии за счет применения архитектуры «маркерного кольца» подтверждается программно полученными данными вычислений, представленными на фиг. 3. Фиг. 3 Влияние значения размера матрицы Р на среднее значение динамической энергии на итерацию Ed для декодера QC-LDPC с архитектурой, основанной на «маркерном кольце». Представлено сравнение архитектур декодеров при одинаковом размере матрицы Н, но разных значениях Р.

Таким образом, при малых значениях размера матрицы (Р=8) среднее значение динамической энергии на итерацию снижается от 443 нДж без использования архитектуры «маркерного кольца» до 273 нДж с использованием предлагаемой архитектуры, выигрыш достигает 61% и выигрыш составляет 54% при Р=24 и 52% при Р=94.

Технический результат достигается за счет того, что декодер использует распределенную систему управления и схему обработки «маркерного кольца», благодаря чему стробирование тактовой частоты в структурных блоках декодера снижает энергопотребление без ухудшения других параметров декодера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ организации системы декодирования с низкой плотностью проверок на четность | 2024 |

|

RU2840331C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ КОДОВ С НИЗКОЙ ПЛОТНОСТЬЮ ПРОВЕРОК НА ЧЕТНОСТЬ | 2017 |

|

RU2739465C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2014 |

|

RU2656830C2 |

| СПОСОБЫ И УСТРОЙСТВО LDPC-ДЕКОДИРОВАНИЯ | 2005 |

|

RU2392737C2 |

| Способ декодирования данных на основе LDPC кода | 2020 |

|

RU2747050C1 |

| СПОСОБЫ И СИСТЕМЫ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ LDPC КОДОВ | 2016 |

|

RU2716044C1 |

| УЛУЧШЕННОЕ ВЫКАЛЫВАНИЕ И СТРУКТУРА КОДА С МАЛОЙ ПЛОТНОСТЬЮ ПРОВЕРОК НА ЧЕТНОСТЬ (LDPC) | 2017 |

|

RU2718171C1 |

| ВЫСОКОСКОРОСТНЫЕ ДЛИННЫЕ LDPC КОДЫ | 2017 |

|

RU2733826C1 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2012 |

|

RU2595585C2 |

| СПОСОБ И УСТРОЙСТВО ПОМЕХОУСТОЙЧИВОГО ДЕКОДИРОВАНИЯ СИГНАЛОВ, ПОЛУЧЕННЫХ С ИСПОЛЬЗОВАНИЕМ КОДА ПРОВЕРКИ НА ЧЕТНОСТЬ С НИЗКОЙ ПЛОТНОСТЬЮ | 2013 |

|

RU2522299C1 |

Изобретение относится к декодированию с низкой плотностью проверки четности. Технический результат - снижение энергопотребления без ухудшения параметров декодера. Для этого декодирование выполняется конвейерным способом с использованием матрицы контроля четности (МКЧ) с настраиваемыми параметрами: регулярные или нерегулярные матрицы с увеличением блока, кодовой скорости и размером подматрицы, с блочной структурой, где по меньшей мере две матрицы подблоков данных МКЧ считываются и записываются в каждом из множества тактов. Декодер с архитектурой «маркерного кольца» с распределенной системой управления реализует синхронизацию модулей декодера для значительного снижения динамической мощности. Активация выбранного блока управления с помощью передачи токена осуществляется вместе с вычислительными элементами, управляемыми этим блоком управления. После завершения вычислений модуля и передачи токена тактовый сигнал, распространяемый в соответствующем вычислительном блоке, блокируется. 3 ил.

Способ декодирования данных на основе LDPC кода, включающий деление проверочной матрицы закодированного сообщения QC-LDPC на М уровней, отличается тем, что синхронизацию модулей частично-параллельной архитектуры декодера выполняют за счет активации выбранного блока управления с помощью передачи токена, после чего тактовый сигнал, распространяемый в соответствующем вычислительном блоке, блокируют, затем после получения токена элемент стробирования тактового сигнала активирует локальный тактовый сигнал (LCLK), тем самым происходит разблокировка схемы стробирования глобального тактового сигнала (GCLK), и LCLK передается элементу распределенной системы управления, который начинает управлять вычислительными модулями и памятью, в то же время на эти вычислительные модули подают локальный тактовый сигнал LCLK, а после завершения локальных вычислений система управления передает токен следующему элементу системы управления и блокирует LCLK.

| US 10581460 B2, 03.03.2020 | |||

| СПОСОБЫ И СИСТЕМЫ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ LDPC КОДОВ | 2016 |

|

RU2716044C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ LDPC-КОДОВ | 2013 |

|

RU2549134C1 |

| ЗАЖИМНОЕ ПРИСПОСОБЛЕНИЕ К СВАЙНОМУ НАГОЛОВн1Тк? | 0 |

|

SU168191A1 |

| US 7903160 B2, 08.03.2011. | |||

Авторы

Даты

2024-01-11—Публикация

2023-04-04—Подача