Область техники, к которой относится изобретение

Настоящее изобретение относится к технологиям мобильного радиоинтерфейса, в частности к способам и системам для кодирования и декодирования двоичных кодов с низкой плотностью проверок на четность (Low density parity check, LDPC).

Уровень техники

LDPC кодер в передатчике используют для кодирования исходных слов для генерирования кодовых слов. LDPC декодер в приемнике используют для декодирования принятых кодовых слов. В IEEE 802.11ad стандарте были приняты LDPC коды различной скорости и в настоящее время предлагают применять в усовершенствованном IEEE 802.11ay стандарте. На сегодняшний день, длинные LDPC коды, предложенные для LDPC кодовой скорости 7/8, имеют длину кодового слова, отличную от длин кодового слова, используемых для разных кодовых скоростей для длинных LDPC кодов. Однако, использование разной LDPC длины кодового слова для разных скоростей кодирования для длинных LDPC кодов может повлиять на выполнение процессов блокинга и деблокинга в передатчике и в приемнике соответственно. Соответственно, желательно иметь согласованную длину кодового слова для разных скоростей кодирования.

Раскрытие сущности изобретения

Согласно примерным вариантам осуществления предоставлен новый высокоскоростной длинный LDPC код, включающий в себя LDPC код со скоростью 7/8 (1344, 1176), который сохраняет длину кодового слова равную 1344, используемую другими LDPC кодами, которые имеют разные кодовые скорости, для упрощения реализации и повышения эффективности использования спектра с меньшим нулевым заполнением при кодировании, и выполнение блокинга с одной несущей (SC) по сравнению с другими возможными решениями.

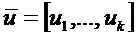

Согласно примерному аспекту предложены способ и система для кодирования исходного слова, содержащие: прием вектора

либо:

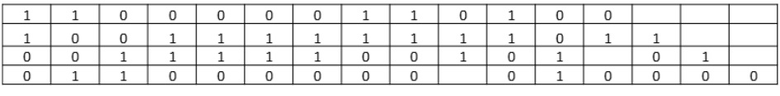

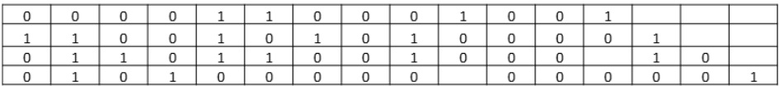

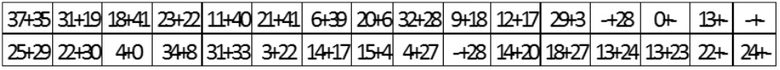

В некоторых примерах разные строки в промежуточной базовой матрице проверки на четность суммируют для получения H1. В некоторых примерах Hl является:

В соответствии с примерным аспектом предоставляют способ для кодирования исходного слова, содержащий: прием вектора

В соответствии с примерным аспектом предоставлен способ для кодирования исходного слова, содержащий: прием вектора

Краткое описание чертежей

В качестве примера, со ссылкой на прилагаемые чертежи, которые показывают примерные варианты осуществления настоящего изобретения и на которых:

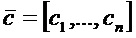

Фиг. 1A является блок-схемой, иллюстрирующей пример системы связи в соответствии с одной реализацией настоящего изобретения;

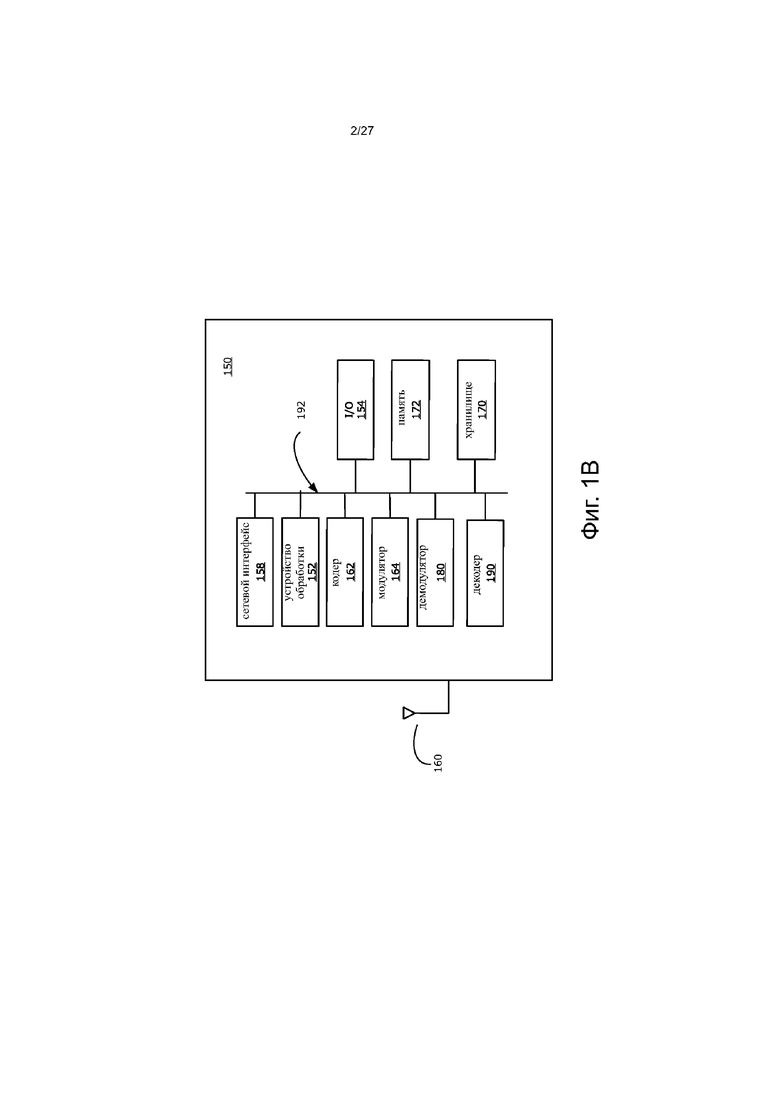

Фиг. 1B является блок-схемой, иллюстрирующей примерную систему обработки в соответствии с одной реализацией настоящего изобретения;

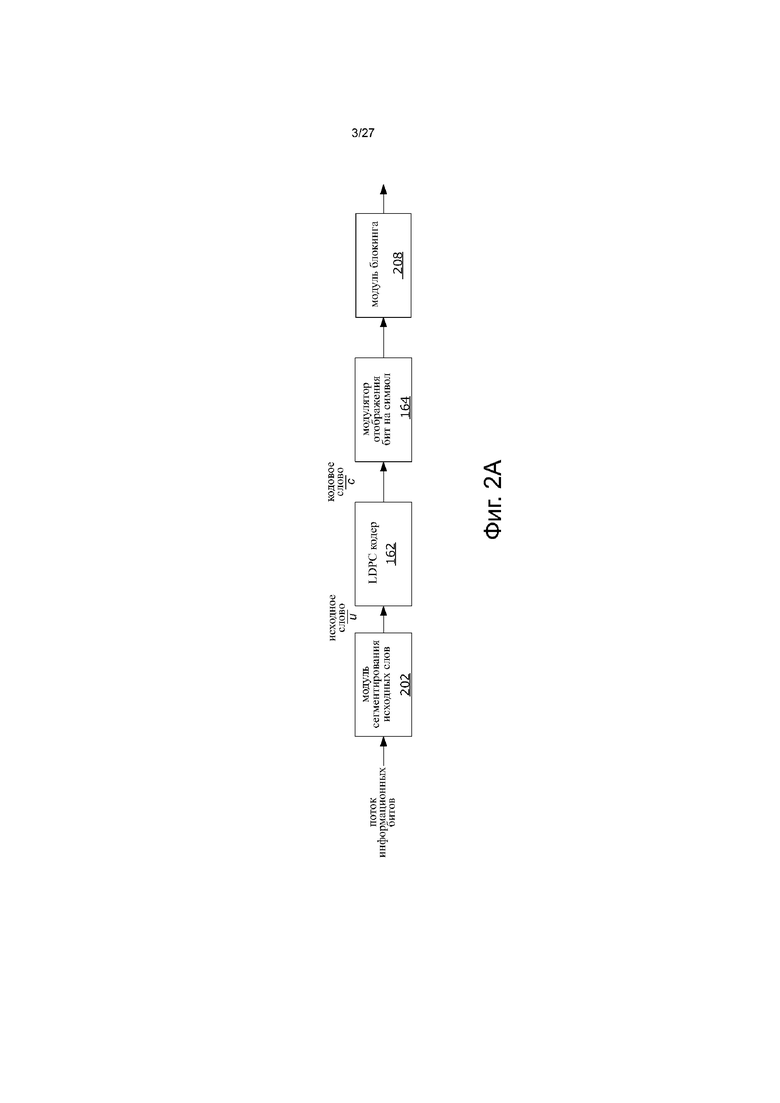

Фиг.2A является блок-схемой, представляющей пример реализации передатчика настоящего изобретения;

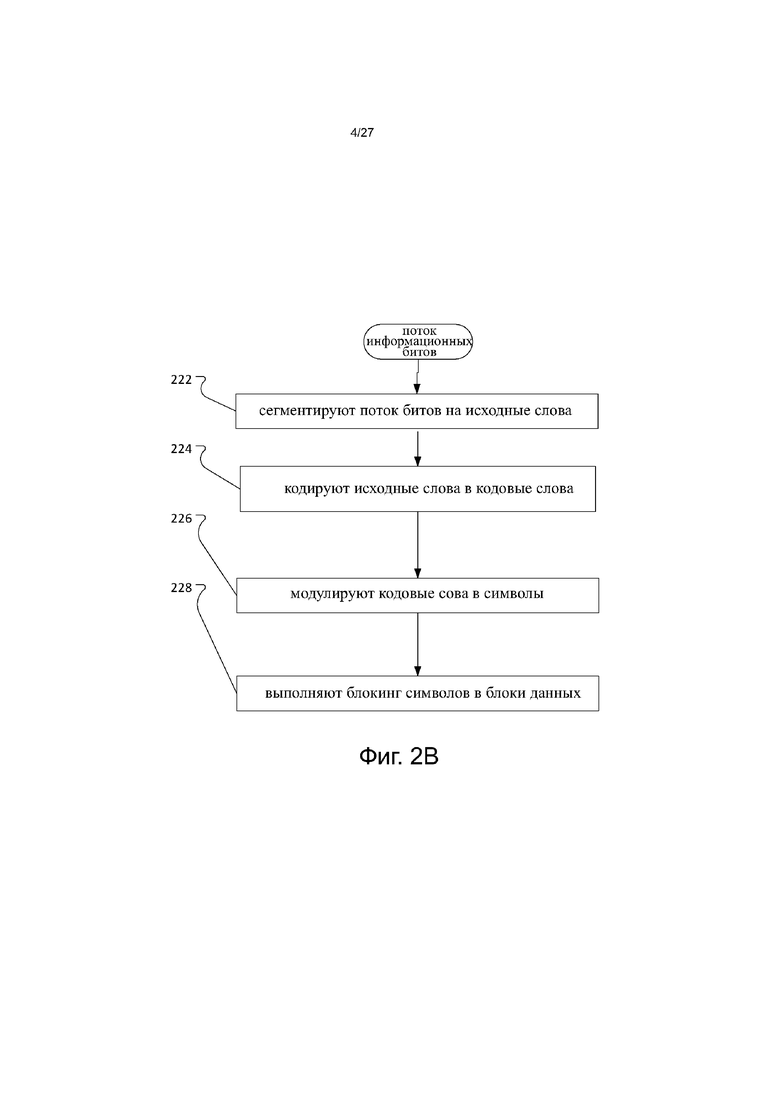

Фиг.2B является блок-схемой, иллюстрирующей примерные этапы в способе обработки потока информационных битов настоящего изобретения;

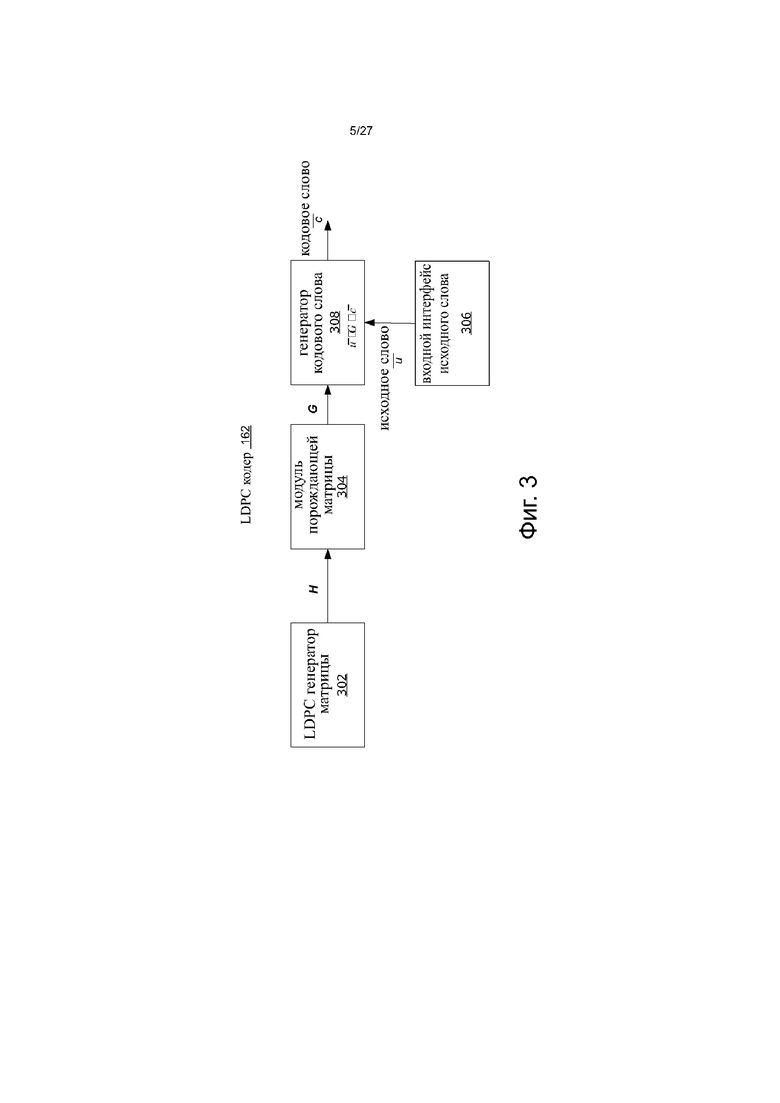

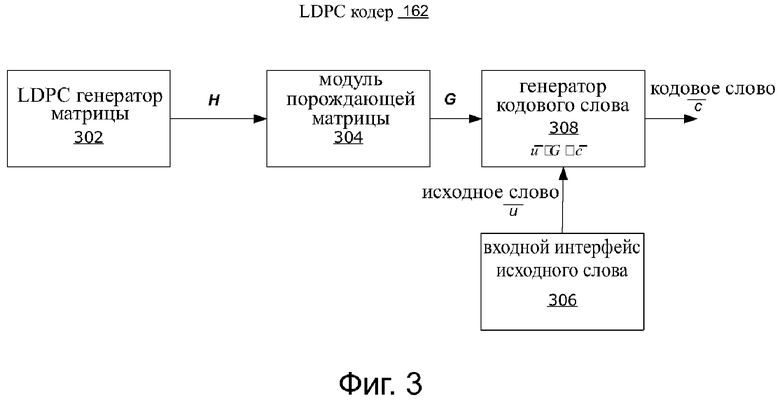

Фиг.3 является блок-схемой, представляющей пример реализации LDCP кодера по настоящему изобретению;

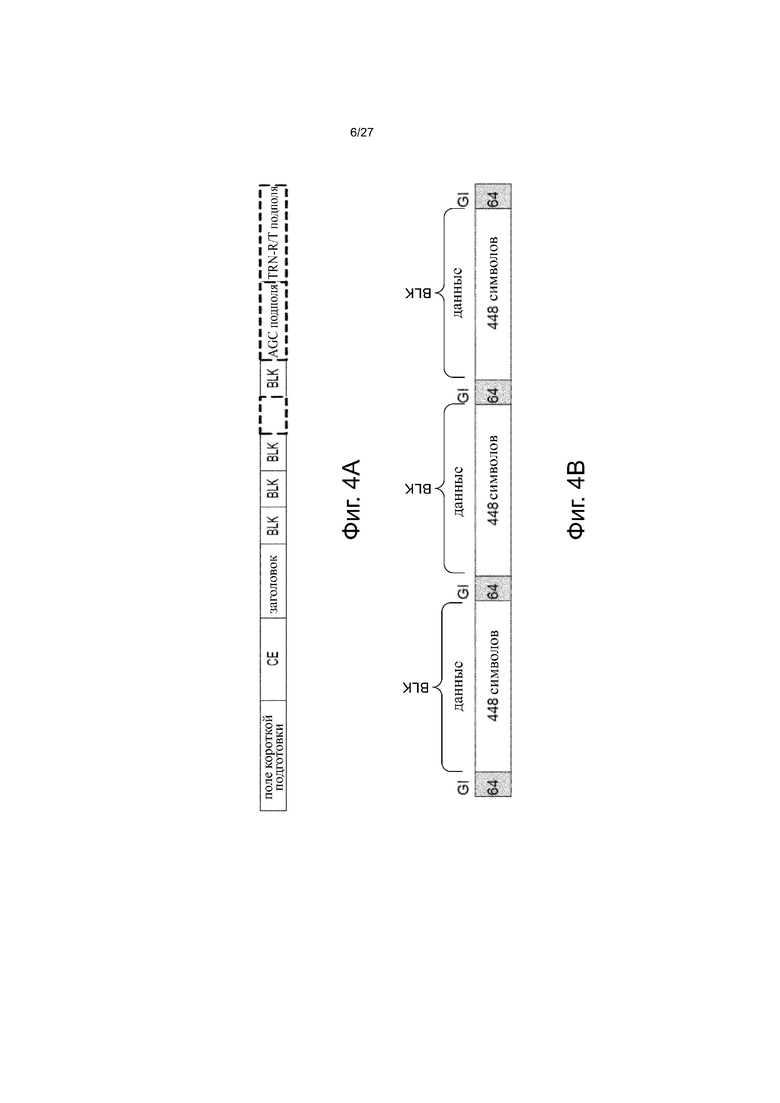

Фиг.4А является схемой, иллюстрирующей пример формата кадра с одной несущей 802.11ad;

Фиг. 4B является схемой, иллюстрирующей пример структуры блоков данных формата кадра с одной несущей 802.11ad;

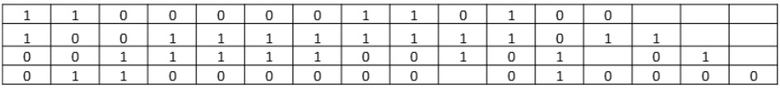

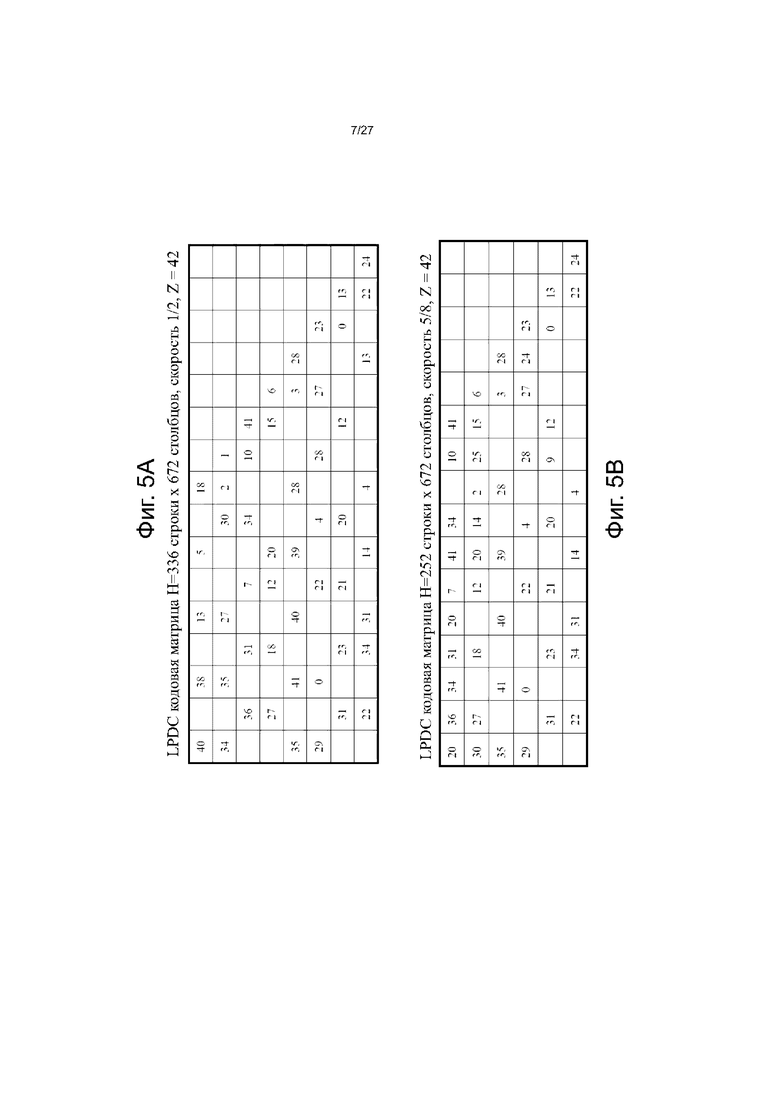

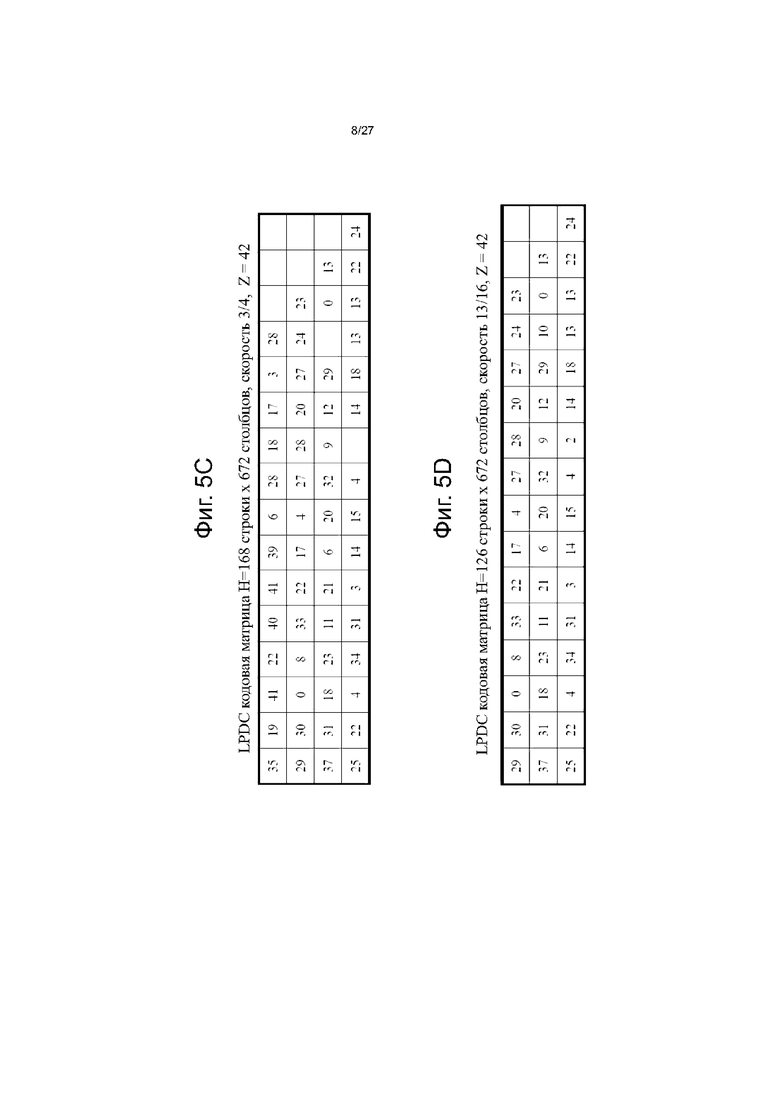

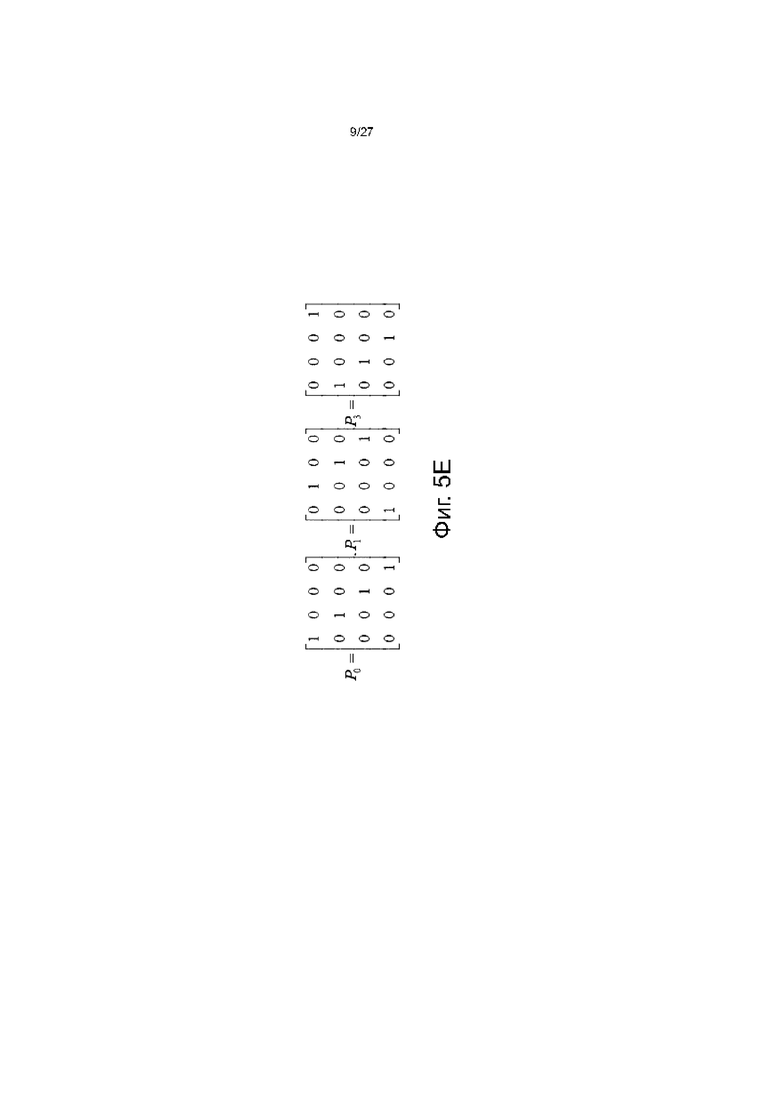

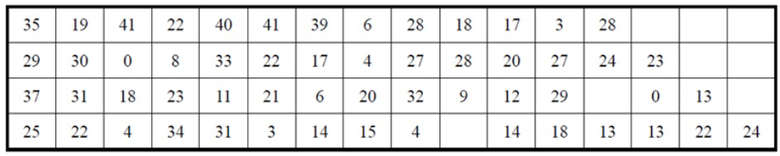

Фиг.5A-5D показывают разделенные LDPC матрицы проверки на четность, указанные в IEEE802.11ad, с длиной кодового слова равной 672, и на фиг.5E показаны подматрицы циклической перестановки, полученные из 4 × 4 единичной матрицы;

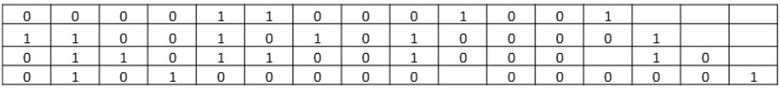

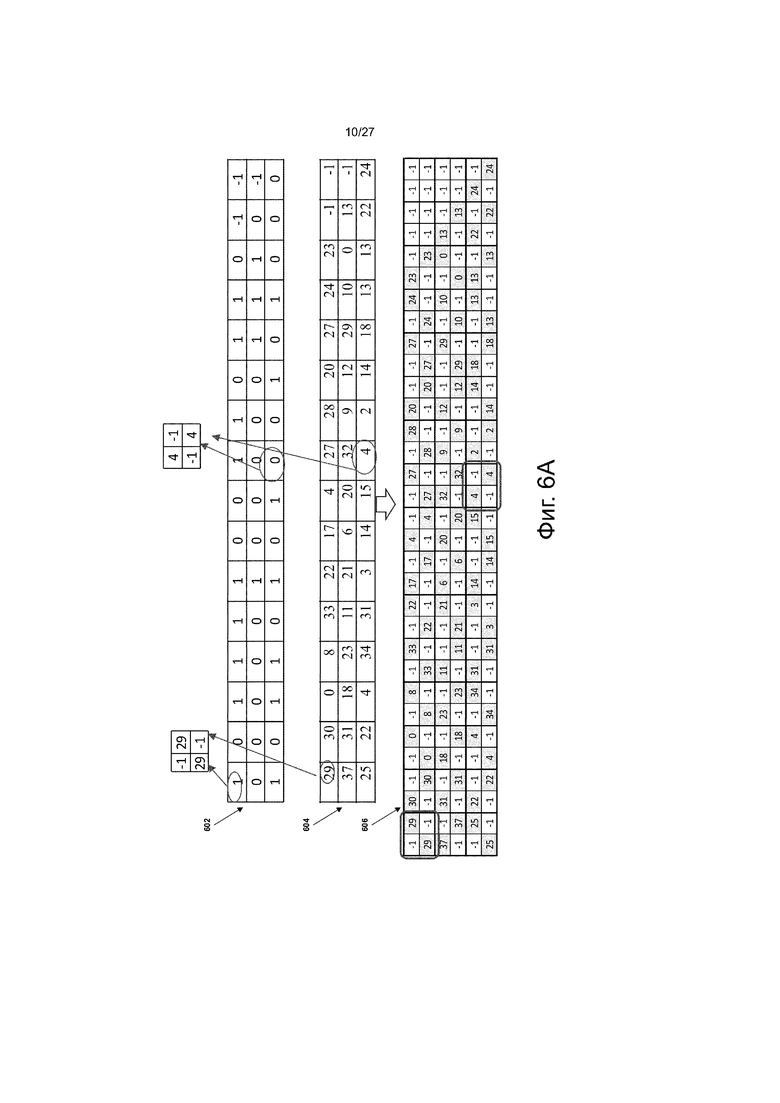

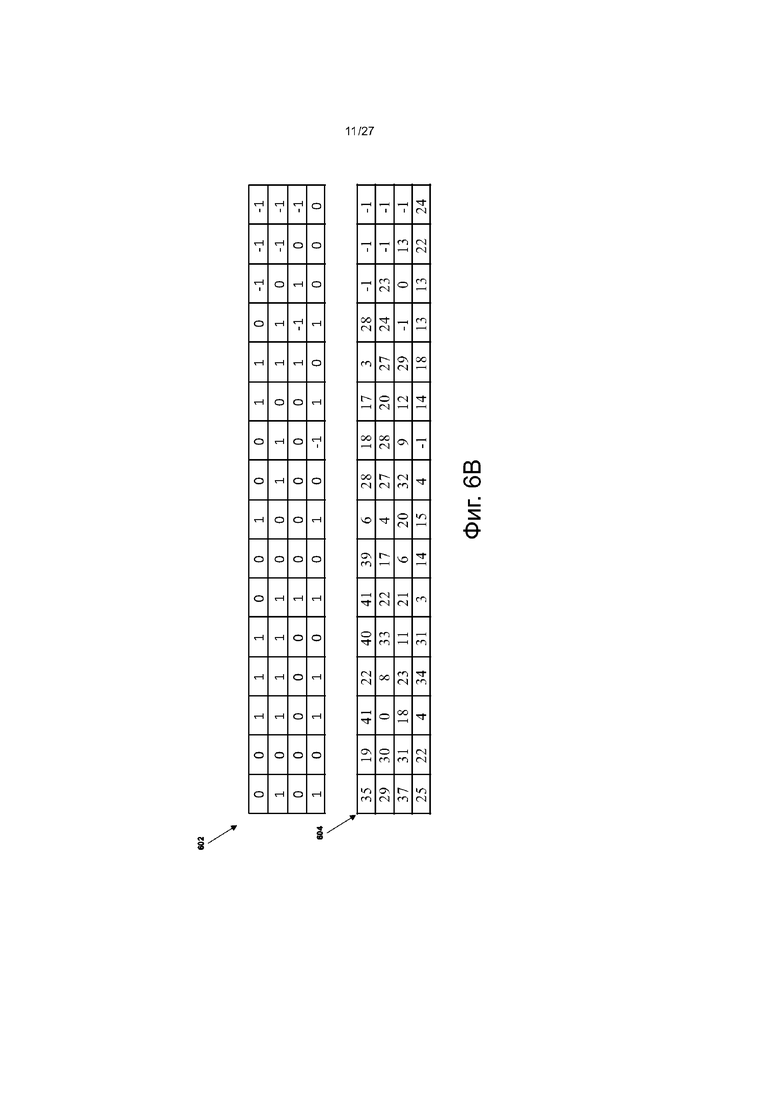

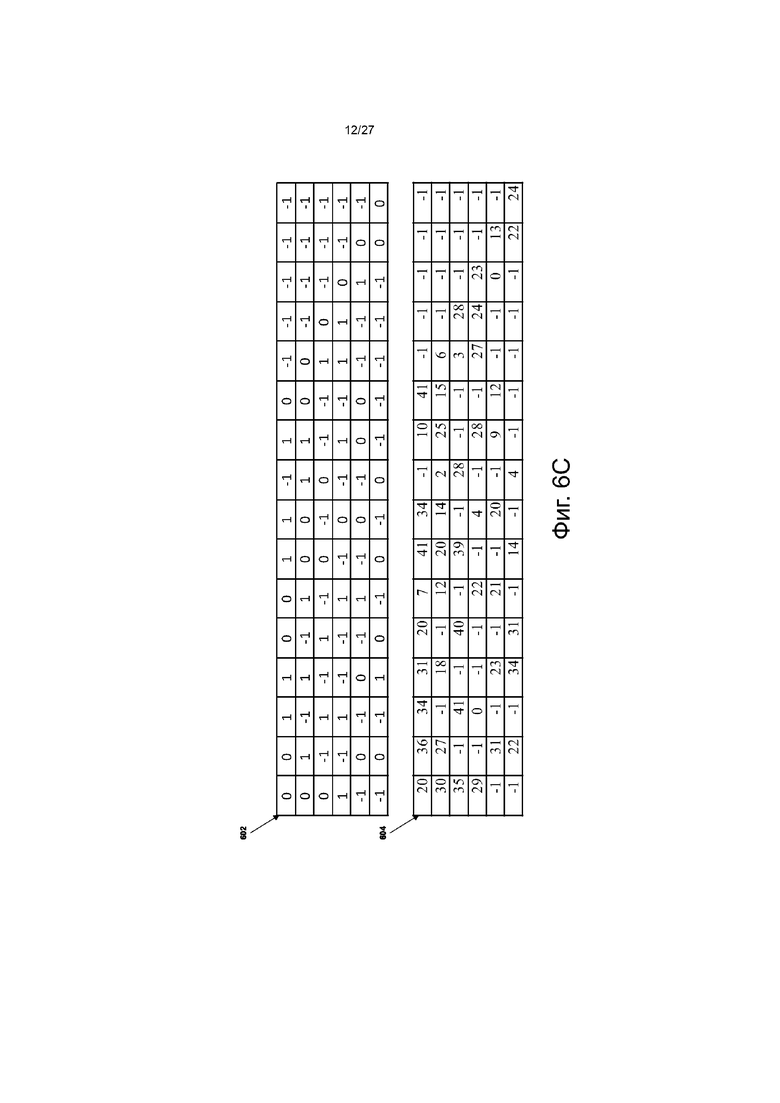

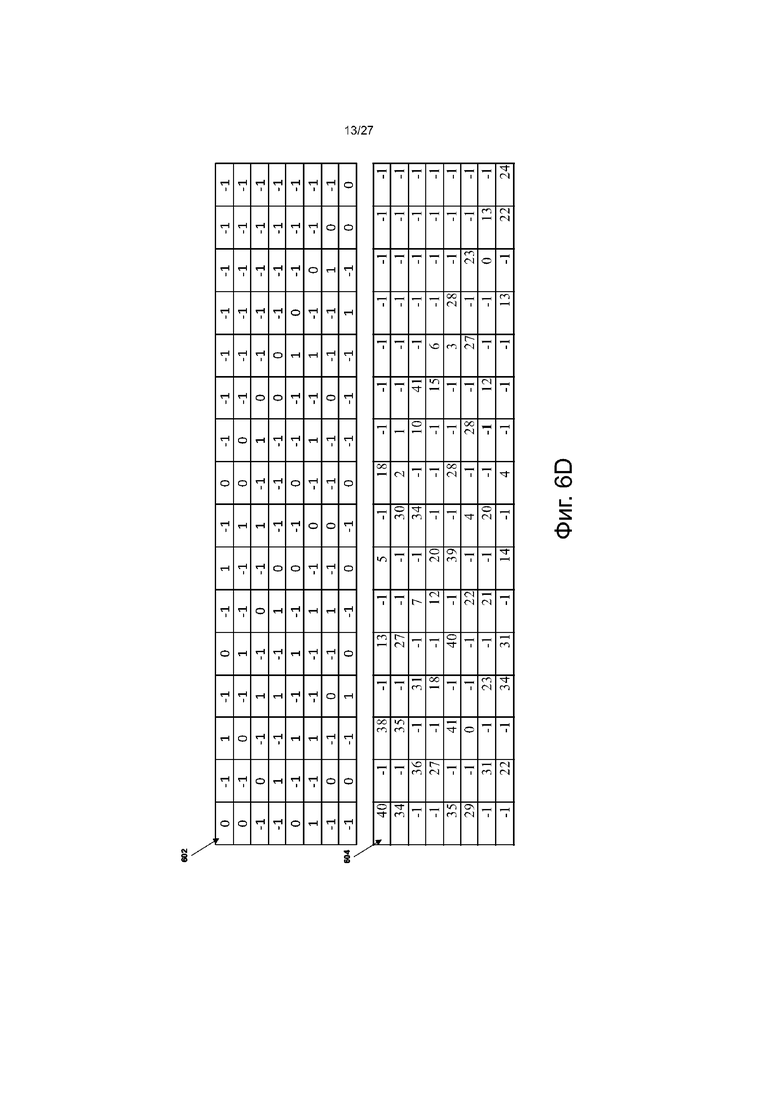

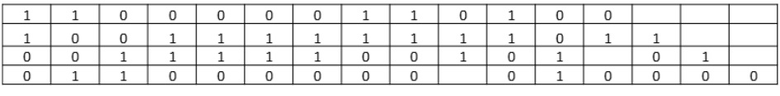

Фиг. 6A-6D показывают разделенные LPDC матрицы проверки на четность, предложенные в IEEE802.11ay, с длиной кодового слова равной 1344;

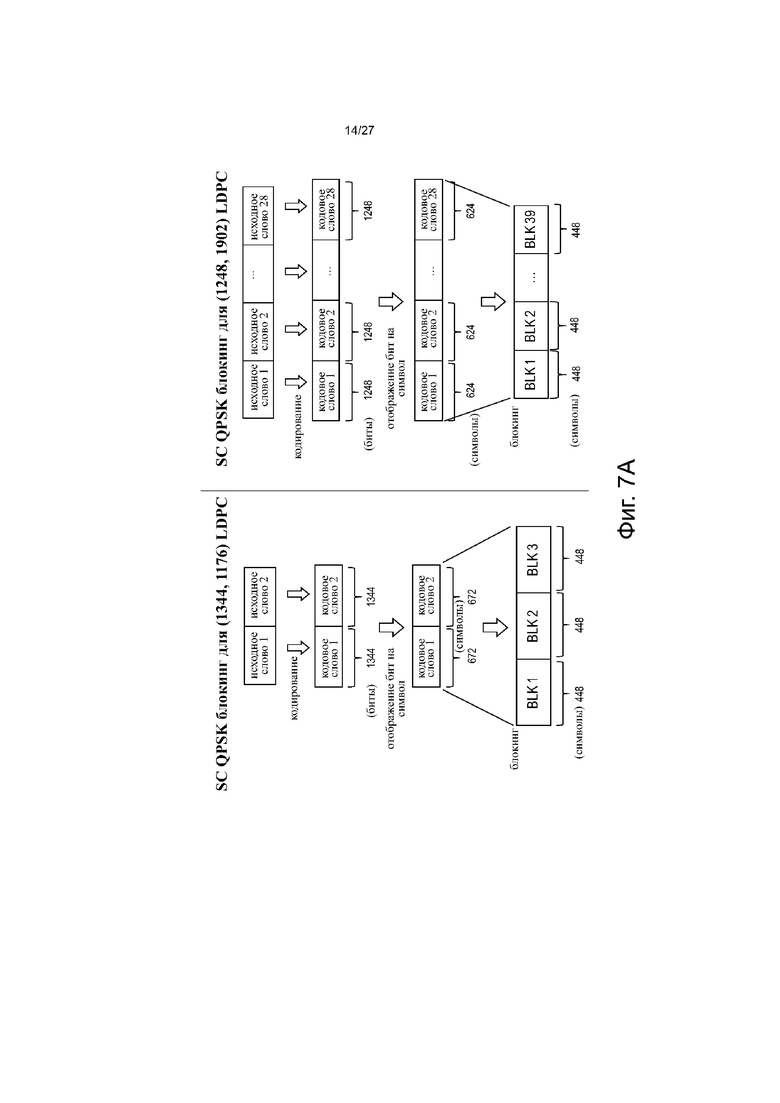

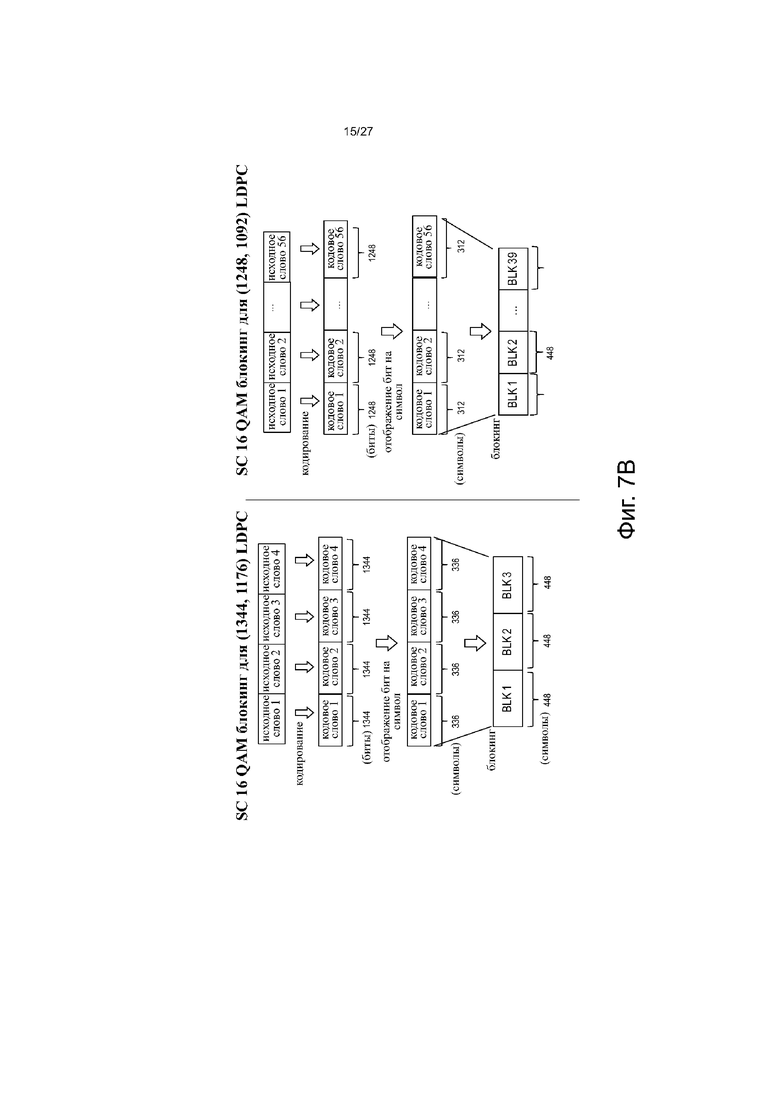

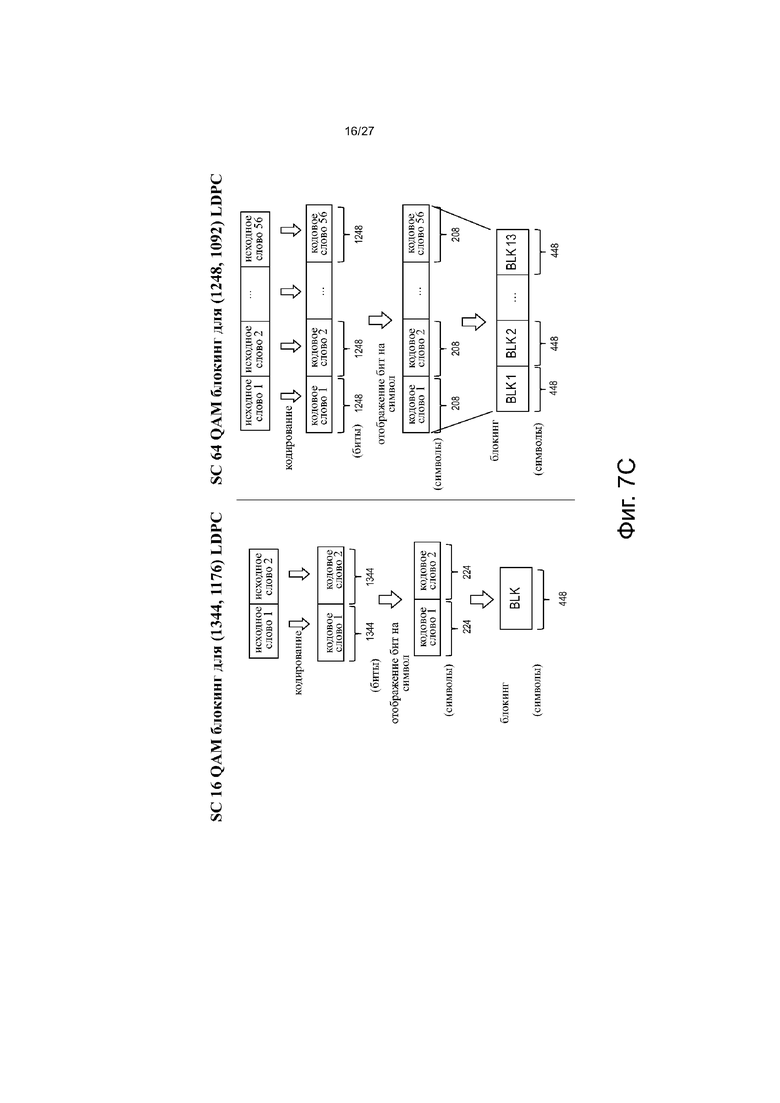

Фиг.7А-7С иллюстрируют схемы, показывающие процессы блокинга с одной несущей с разными технологиями модуляции;

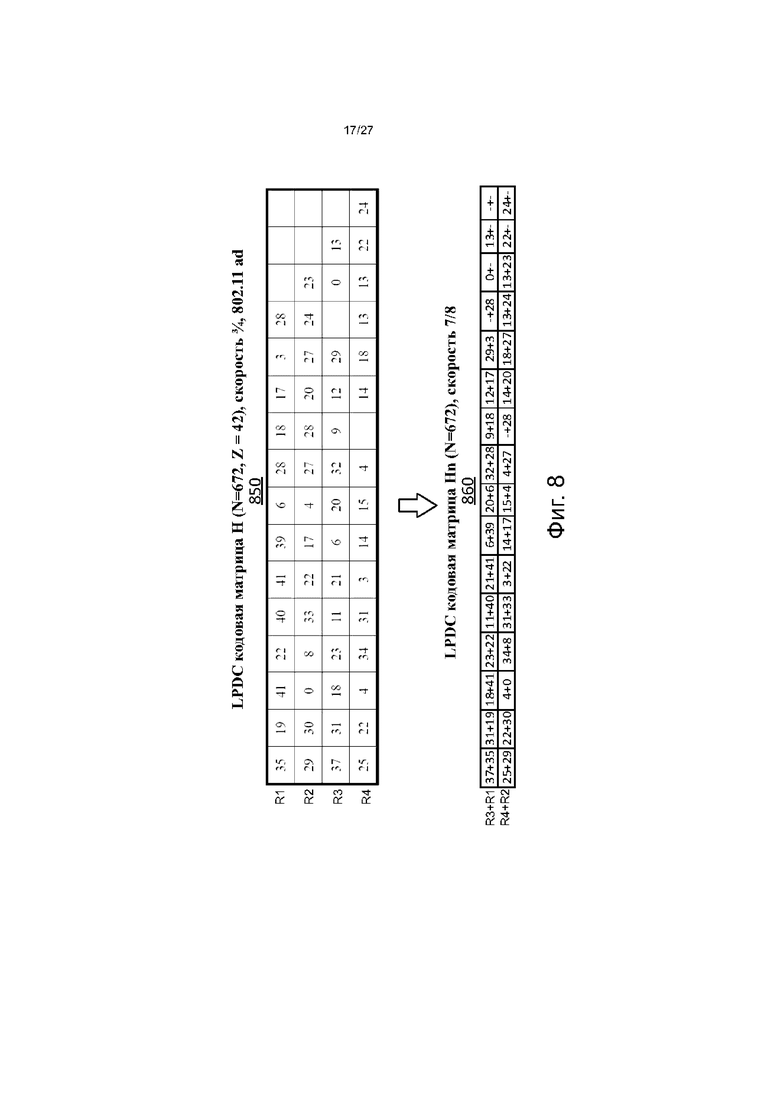

Фиг.8 иллюстрирует LDPC матрицу Hn с короткой длиной кодовой скорости 7/8 на основании скорости 3/4 LDPC в 802.11;

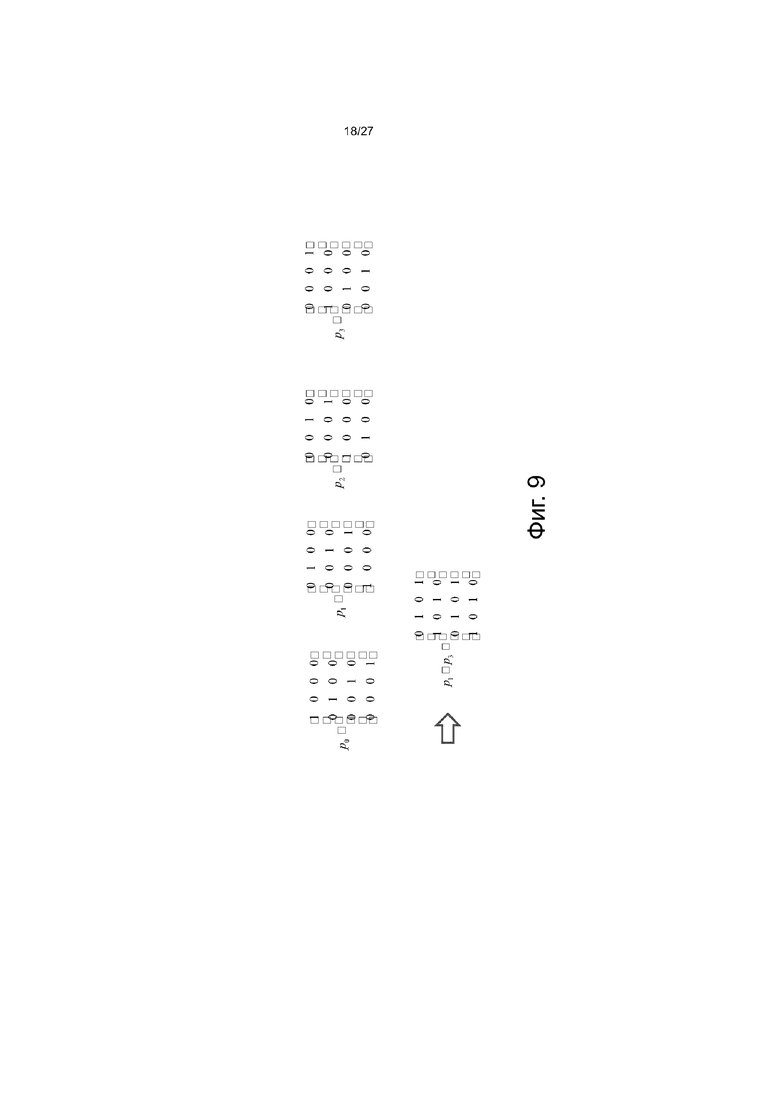

Фиг.9 представляет собой схему, иллюстрирующую пример суммирования матриц циклической перестановки для упрощенного случая Z = 4;

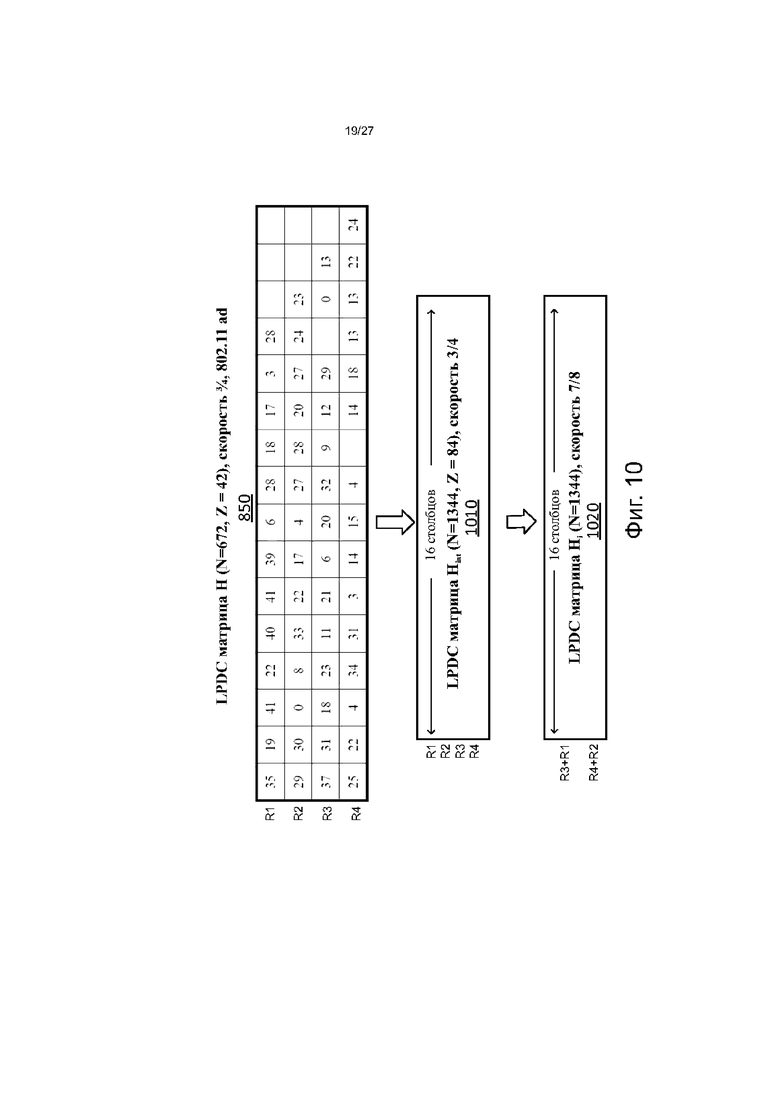

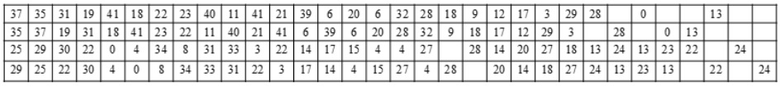

Фиг.10 иллюстрирует способ генерирования LDPC матрицы H1 длиной 1344 с кодовой скоростью 7/8 на основании скорости 3/4 LDPC в 802.11 согласно настоящему изобретению;

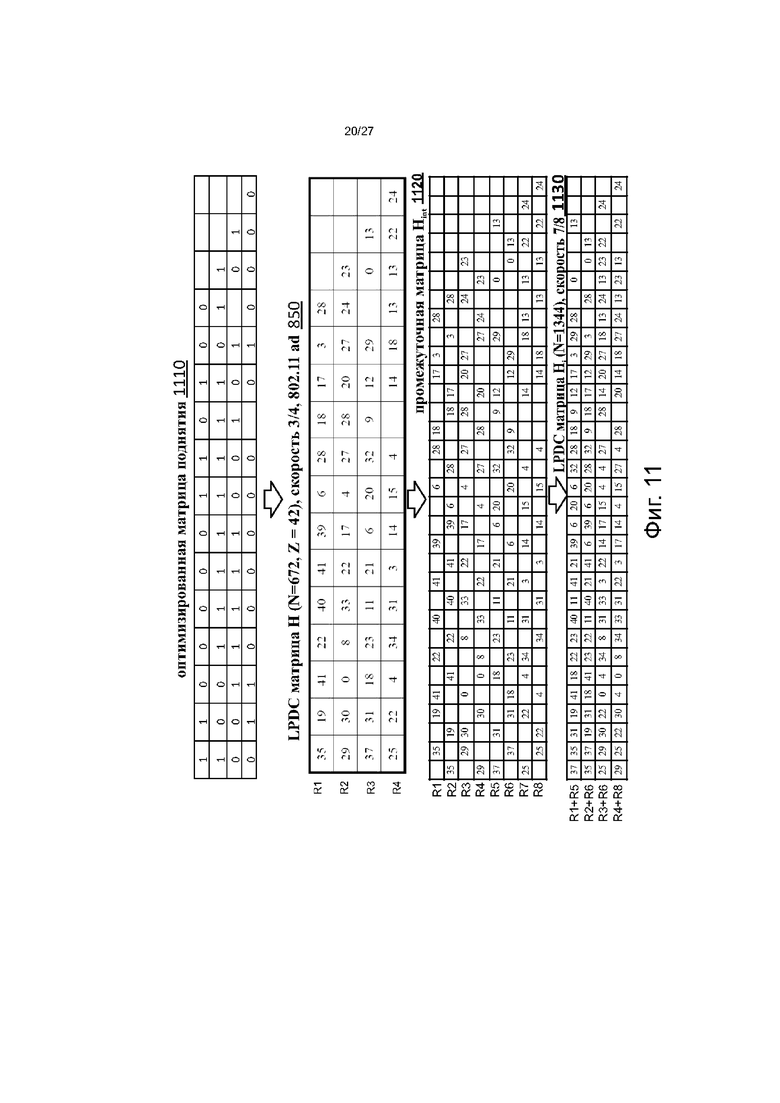

Фиг.11 иллюстрирует другой пример дополнительного способа генерирования LDPC матрицы H1 длиной 1344 с кодовой скоростью 7/8 на основании LDPC скорости 3/4 в 802.11 согласно настоящему изобретению;

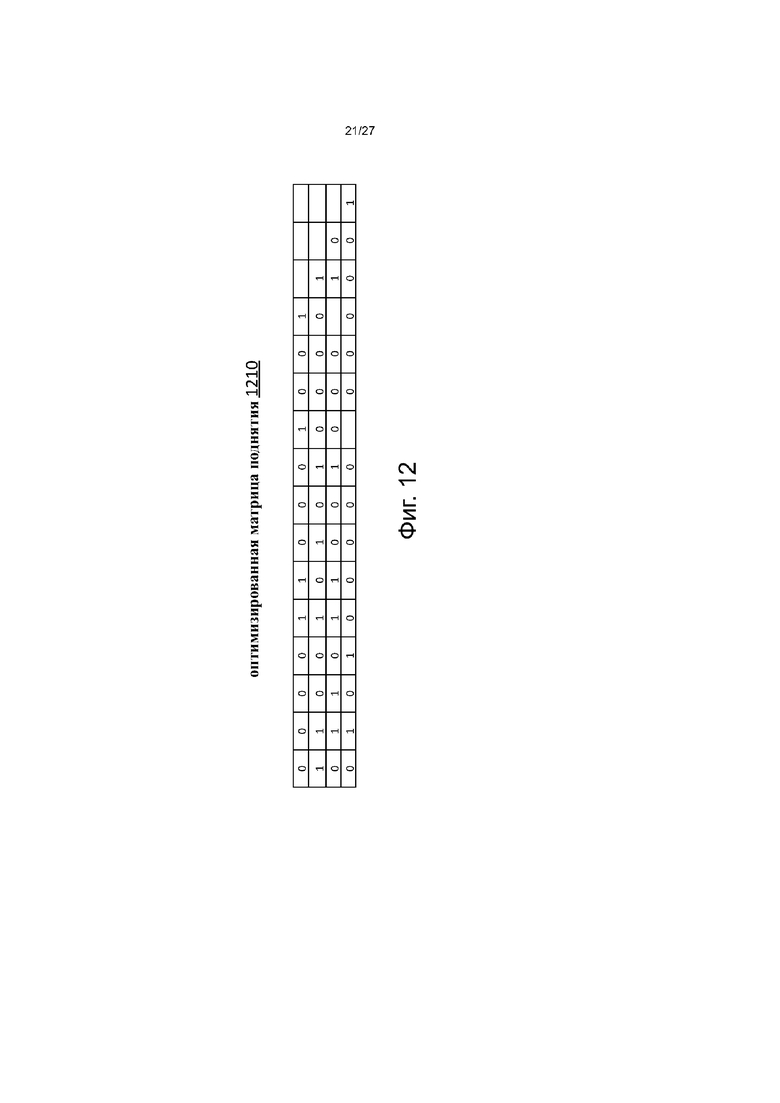

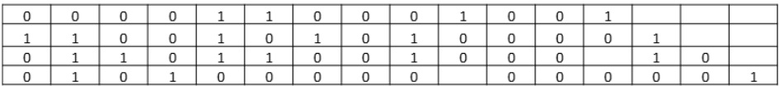

Фиг.12 показывают альтернативную матрицу поднятия для использования в способе по фиг.11;

Фиг.13 иллюстрирует еще один пример дополнительного способа генерирования LDPC матрицы H1 длиной 1344 кодовой скорости 7/8 на основании LDPC скорости 3/4 в 802.11 согласно настоящему изобретению;

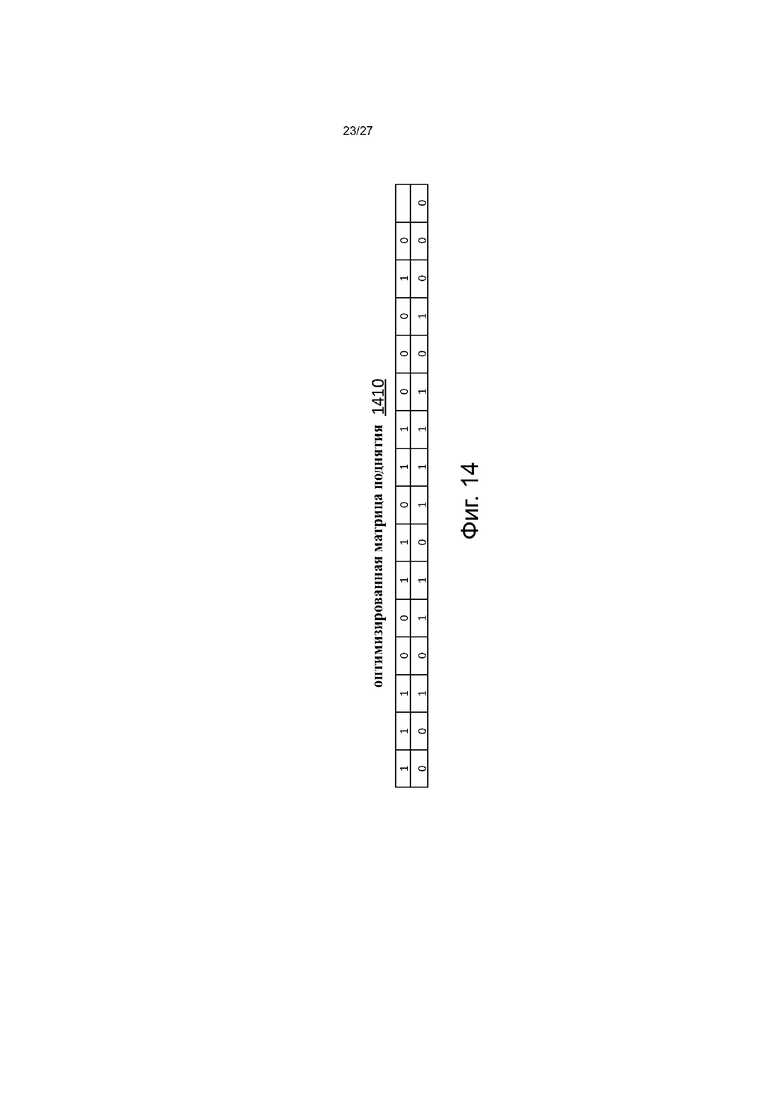

Фиг. 14 показывает альтернативную матрицу поднятия для использования в способе по фиг. 13;

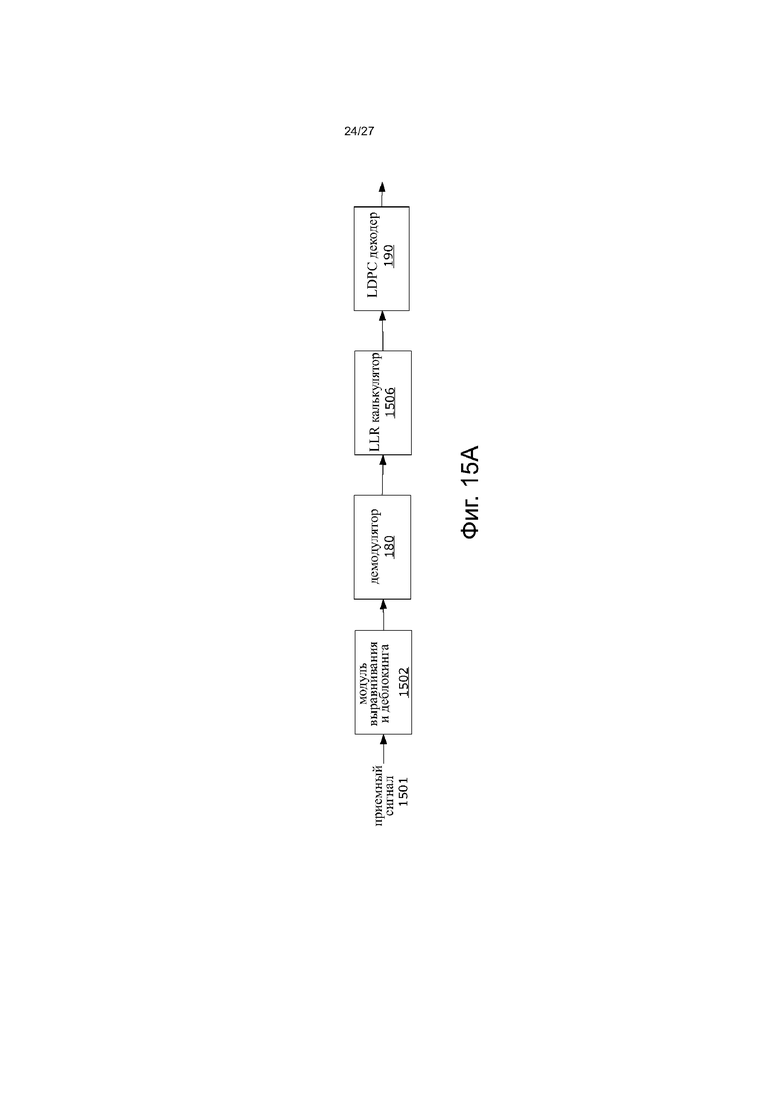

Фиг. 15А является блок-схемой, представляющей пример реализации приемника настоящего изобретения;

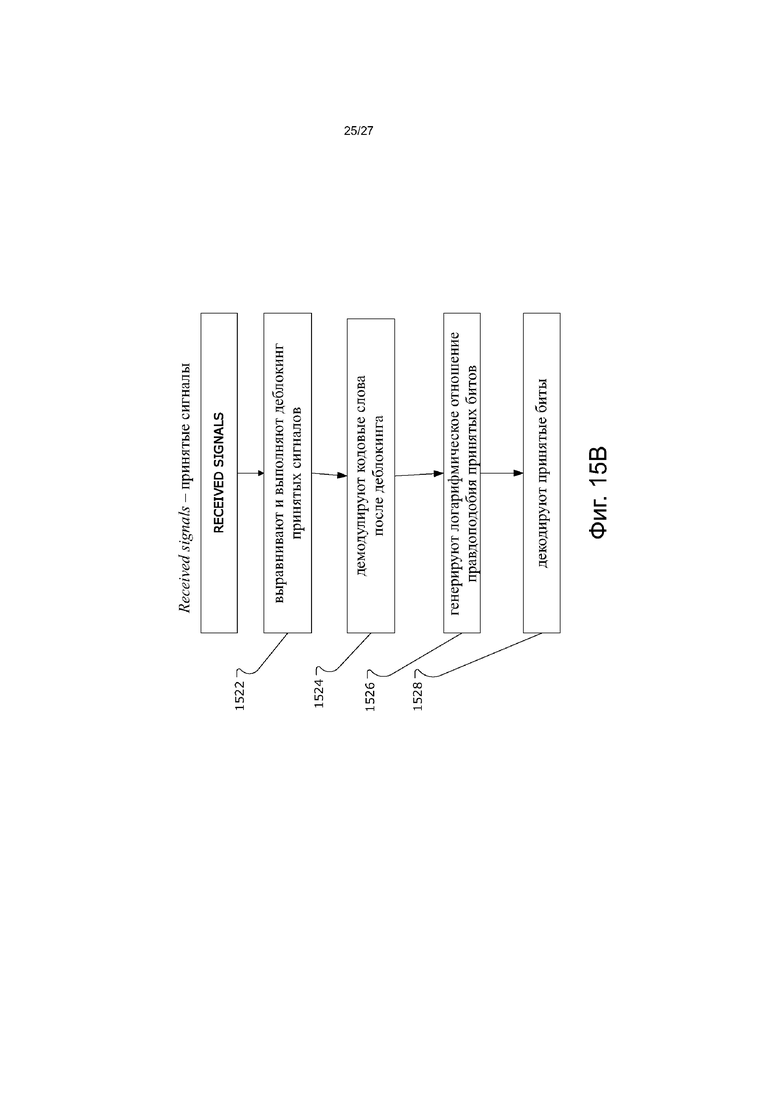

Фиг. 15B является блок-схемой, представляющей примерные этапы в процессе декодирования принятого сигнала согласно одному варианту осуществления настоящего изобретения;

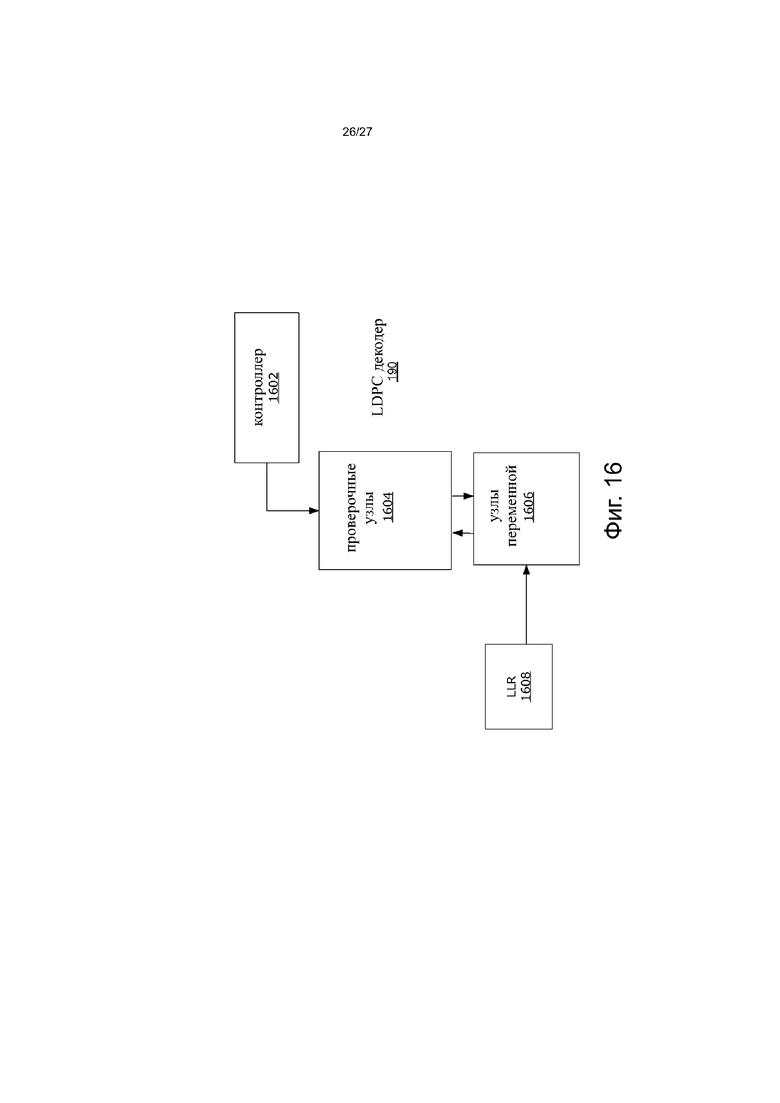

Фиг. 16 является блок-схемой, представляющей примерную реализацию LDCP декодера по настоящему изобретению; и

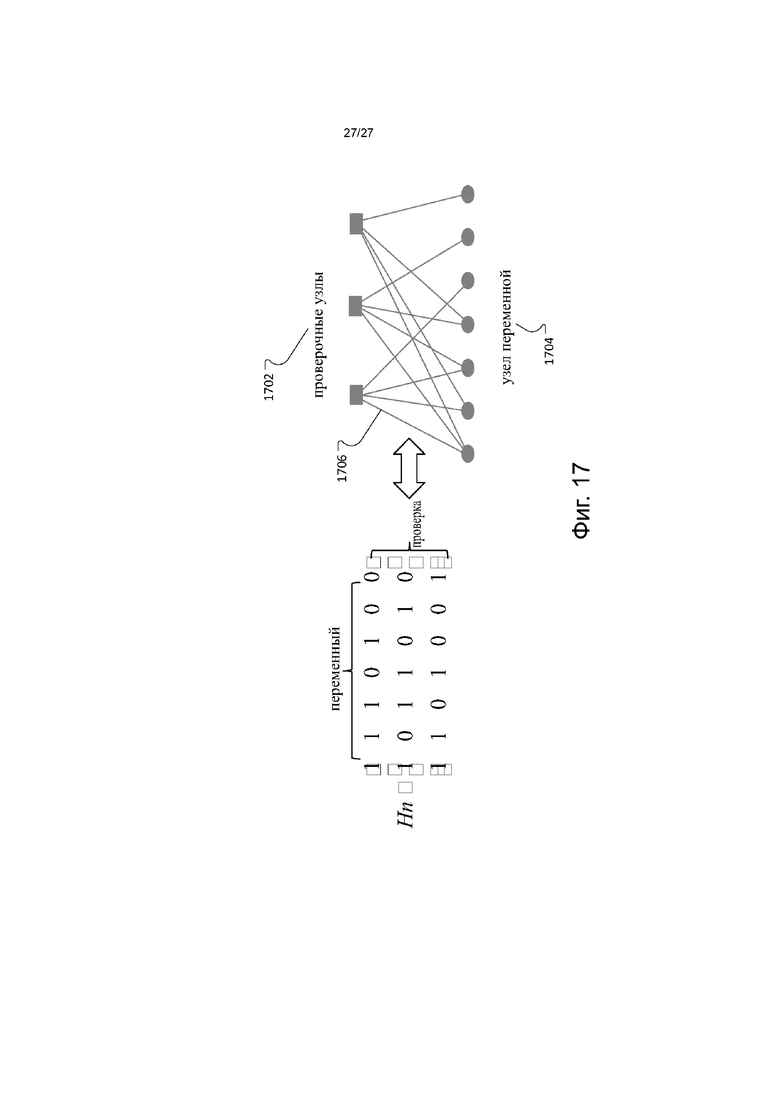

Фиг.17 показывает схему, иллюстрирующую пример процесса LDPC декодирования.

Одинаковые ссылочные позиции используют на всех чертежах для обозначения аналогичных элементов и признаков. Несмотря на то, что аспекты изобретения будут описаны со ссылкой на проиллюстрированные варианты осуществления, следует понимать, что настоящее изобретение не предназначено для ограничения изобретения такими вариантами осуществления.

Осуществление изобретения

Настоящее изобретение раскрывает способы, устройства и системы для кодирования исходных слов и декодирования кодовых слов в беспроводной сети. Главным образом, настоящее изобретение относится к сетям, совместимым со стандартом 802.11ay, но также настоящее изобретение может также применяться к другим системам, основанным на блочном кодировании.

Длинные LDPC кодовые слова, имеющие длину 1344 бита для более низких кодовых скоростей ½, 5/8, ¾ и 13/16, могут быть сгенерированы на основании двухэтапного поднятия соответствующих 672-битовых LDPC кодовых слов, указанных в IEEE 802.11ad. Тем не менее, остается необходимость в подходящем LDPC коде с более высокой скоростью, такой как кодовая скорость 7/8, который использует длинное кодовое слово такой же длины, что и длинное кодовое слово с более низкой скоростью, такой как 1344 бит. В этом отношении, настоящее изобретение описывает высокоскоростной длинный LDPC код, такой как LDPC код со скоростью 7/8, имеющий кодовое слово длиной 1344 бита.

В качестве контекста, представления, относящиеся к LDPC кодам в отношении усовершенствования 802.11ay стандарта, включают в себя «IEEE 802.11-16/0676-01-00ay-length-1344-LDPC-codes-for-11ay» [REF 1] и «IEEE 802.11-16/1495-00-00ay-rate-7-8-ldpc-code-for-11ay» [REF2]. [REF1] предлагает LDPC код длиной 7/8, генерируемый путем выкалывания первых 96 битов четности кодовых слов LDPC скорости 13/16 длиной 1344 бита. Однако, этот процесс выкалывания, применяемый к LDPC коду длиной 1344, приводит к LDPC коду со скоростью 7/8 с длиной кодового слова равной 1248 бит по сравнению с длиной кодового слова равной 1344 LDPC кодов с более низкой скоростью. Различные LDPC размеры кодового слова будут влиять на реализацию кодирования и блокинга с одной несущей (SC) (отображение символов на блоки) в передатчике и приемнике. Соответственно, желательно, чтобы длина кодового слова для разных кодовых скоростей была одинаковой.

[REF 2] предлагает высокоскоростной (7/8) короткий LDPC код с длиной кодового слова 672 бита, который сохраняет коэффициент расширения 42 и длину кодового слова 672 без изменений, указанных для кодов с более низкой скоростью в 802.11ad. [3]. Настоящее изобретение описывает высокоскоростной длинный LDPC код, который реализован с использованием длины кодового слова, которую также могут применять к кодам с более низкой скоростью.

Пример среды, в которой могут работать LDPC системы кодирования, подробно описанные ниже, будет предоставлен со ссылкой на фиг.1А и 1В. На фиг.1А показана сеть 100 связи, содержащая множество станций (STAs) 102 и точку доступа (AP) 104. Каждая из STA 102 и AP 104 может включать в себя передатчик, приемник, кодер и/или декодер как описано в настоящем документе. Сеть 100 может работать в соответствии с одним или несколькими стандартами, или технологиями связи или данных, включающие в себя, помимо прочего, сети IEEE 802.11, телекоммуникационные сети пятого поколения (5G) или четвертого поколения (4G), «Долгосрочное развитие» (LTE), проект партнерства третьего поколения (3GPP), универсальная система мобильной связи (UMTS) и другие сети беспроводной или мобильной связи. STA 102 обычно может быть любым устройством, выполненным с возможностью обеспечивать беспроводную связь или использовать протокол 802.11. STA 102 может быть ноутбуком, настольным РС, PDA, точкой доступа или телефоном Wi-Fi, беспроводным приемопередающим устройством (WTRU), мобильной станцией (MS), мобильным терминалом, смартфоном, сотовым телефоном или другими компьютерами с поддержкой беспроводной связи. или мобильным устройством. В некоторых вариантах осуществления STA 102 содержит машину, которая имеет возможность отправлять, принимать или отправлять и принимать данные в сети 100 связи, но которая выполняет основные функции, отличные от связи. В одном варианте осуществления машина включает в себя устройство или приспособление со средством передачи и/или приема данных через сеть 100 связи, но таким устройством или приспособлении обычно не управляет пользователь для достижения основной цели связи. AP 104 может содержать базовую станцию (BS), усовершенствованный узел B (eNB), беспроводной маршрутизатор или другой сетевой интерфейс, который функционирует как точка беспроводной передачи и/или приема для STA 102 в сети 100. AP 104 подключена к транзитной сети 110, которая выполненная с возможностью осуществлять обмен данными между AP 104 и другими удаленными сетями, узлами, AP и устройствами (не показаны). AP 104 может поддерживать связь с каждой STA 102 путем установления каналов связи восходящей линии связи и нисходящей линии связи с каждой STA 102, как показано стрелками на фиг. 1A. Связь в сети 100 может быть незапланированной, запланированной AP 104 или объектом планирования или управления (не показан) в сети 100, или смесь запланированных и незапланированных коммуникаций.

Фиг. 1B иллюстрирует примерную систему 150 обработки, которая может быть использована для реализации способов и систем, описанных в данном документе, таких как STA 102 или AP 104. Система 150 обработки может быть базовой станцией, беспроводным маршрутизатором, мобильным телефоном, например, или любой подходящей системой обработки. Могут быть использованы другие системы обработки, подходящие для реализации настоящего изобретения, которые могут включать в себя компоненты, отличные от тех, которые описаны ниже. Хотя на фиг.1В показан один экземпляр каждого компонента, в системе 150 обработки может быть несколько экземпляров каждого компонента.

Система 150 обработки может включать в себя одно или более устройств 152 обработки, таких как процессор, микропроцессор, специализированная интегральная схема (ASIC), программируемая пользователем полевая матрица (FPGA), выделенная логическая схема или их комбинации. Система 150 обработки также может включать в себя один или несколько интерфейсов 154 ввода/вывода (I/O), которые могут обеспечивать взаимодействие с одним или несколькими соответствующими устройствами ввода и/или вывода (не показаны). Одно или несколько устройств ввода и/или устройств вывода могут быть использованы в качестве компонента системы 150 обработки или могут быть внешними по отношению к системе 150 обработки. Система 150 обработки может включать в себя один или несколько сетевых интерфейсов 158 для проводной или беспроводной связи, такой как, но не ограничиваясь этим, интернет, P2P сеть, WAN, LAN, WLAN и/или сеть сотовой или мобильной связи, такая как 5G, 4G, LTE или другая сеть, как отмечено выше. Сетевой интерфейс (интерфейсы) 208 может включать в себя проводные линии связи (например, Ethernet кабель) и/или беспроводные линии связи (например, одну или несколько радиочастотных линий) для внутрисетевой и/или межсетевой связи. Сетевой интерфейс (интерфейсы) 158 может обеспечивать беспроводную связь через один или несколько передатчиков, или передающих антенн, одного или нескольких приемников, или приемных антенн и, например, различные аппаратные и программные средства обработки сигналов. В этом примере показана одиночная антенна 160, которая может служить как передающей, так и приемной антенной. Однако, в других примерах могут быть отдельные антенны для передачи и приема. Сетевой интерфейс (интерфейсы) 158 может быть выполнен с возможностью отправлять и принимать данные в транзитную сеть 110 или другие пользовательские устройства, точки доступа, точки приема, точки передачи, сетевые узлы, шлюзы или ретрансляционные узлы (не показаны) в сети 100.

Система 150 обработки также может включать в себя один или несколько блоков 170 хранения, которые могут включать в себя блок хранения массовой информации, такой как твердотельный накопитель, накопитель на жестких дисках, накопитель на магнитном диске и/или накопитель на оптических дисках. Система 150 обработки может включать в себя одно или несколько память 172, которые могут включать в себя энергозависимую или энергонезависимую память (например, флэш-память, оперативную память (RAM) и/или постоянную память (ROM)). Постоянная память (памяти) 172 может хранить инструкции для выполнения устройством (устройствами) 152 обработки, например, для осуществления настоящего изобретения. Память (памяти) 172 может включать в себя другие программные инструкции, например, для реализации операционной системы и других приложений/функций. В некоторых примерах один или несколько наборов данных и/или модулей могут быть предоставлены внешней памятью (например, внешним диском в проводной или беспроводной связи с системой 150 обработки) или могут быть предоставлены временным или постоянным машиночитаемым носителем информации. Примеры постоянных считываемых компьютером носителей включают в себя RAM, ROM, стираемое программируемое ROM (EPROM), электрически стираемое программируемое ROM (EEPROM), флэш-память, CD-ROM или другое портативное запоминающее устройство.

В примерных вариантах осуществления система 150 обработки включает в себя кодер 162 для кодирования исходных слов в кодовые слова и модулятор 164 для модуляции кодовых слов в символы. Как объяснено ниже, кодер 162 выполняет LDPC кодирование исходных слов для генерирования кодовых слов в битах. Модулятор 164 выполняет модуляцию кодовых слов (например, с помощью технологий модуляции, таких как BPSK, QPSK, 16QAM или 64QAM). В некоторых примерах инструкции, закодированные в памяти 172, могут конфигурировать устройство 152 обработки для выполнения функций кодера 162 и/или модулятора 164, так что кодер 162 и/или модулятор 164 могут не быть отдельными физическими модулями системы 150 обработки. В некоторых примерах кодер 162 и модулятор 164 могут быть воплощены в модуле передатчика в системе 150 обработки. В некоторых примерах передающая антенна 160, кодер 162 и модулятор 164 могут быть воплощены в качестве компонента передатчика, внешнего по отношению к системе 150 обработки, и может просто передавать исходные слова из системы 150 обработки.

Система 150 обработки может включать в себя демодулятор 180 и декодер 190 для обработки принятого сигнала. Демодулятор 180 может выполнять демодуляцию принятого модулированного сигнала (например, сигнала BPSK, QPSK, 16QAM или 64QAM). Затем декодер 190 может выполнить соответствующее декодирование демодулированного сигнала, чтобы восстановить исходный сигнал, содержащийся в принятом сигнале. В некоторых примерах инструкции, закодированные в памяти 172, могут конфигурировать устройство 152 обработки выполнить функций демодулятора 180 и/или декодера 190 так, что демодулятор 180 и/или декодер 190 могут не быть отдельными физическими модулями системы 150 обработки. В некоторых примерах демодулятор 180 и декодер 190 могут быть воплощены в модуле приемника в системе 150 обработки. В некоторых примерах приемная антенна 160, демодулятор 180 и декодер 190 могут быть воплощены как компонент приемника, внешний по отношению к системе 150 обработки и может просто передавать сигнал, декодированный из принятого сигнала, в систему 150 обработки.

Могут использовать шину 192, обеспечивающую связь между компонентами системы 150 обработки, включающую в себя устройство (устройства) 152 обработки, интерфейс (интерфейсами) 154 ввода/вывода, сетевой интерфейс (интерфейсы) 158, кодер 162, модулятор 164, блок (блоки) 170 хранения, память (памяти) 172, демодулятор 180 и декодер 190. Шина 192 может быть любой подходящей архитектурой шины, включающей в себя, например, шину памяти, периферийную шину или видео шину.

Связь между STA 102 и AP 104 в сети 100 может быть реализована путем кодирования исходных слов, подлежащих передаче, с использованием технологий кодирования с низкой плотностью проверок на четность (LDPC), и/или путем декодирования кодовых слов, принятых с использованием технологий декодирования LDPC кода. После того, как исходные слова кодируют с помощью технологий LDPC кодирования, когда кодированные кодовые слова передают в сигнале из AP 104 в STA 102 или из STA 102 в AP 104, LDPC информация кодирования передаваемого сигнала может содержаться в передаваемом кадре. После того, как переданный сигнал будет принят STA 102 или AP 104 с LDPC информацией кодирования принятого сигнала, STA 102 или AP 104 может затем выбрать соответствующие технологии LDPC декодирования для декодирования принятого сигнала.

Передатчик и кодер

На фиг.2А представлен пример реализации передатчика STA 102 или AP 104. Передатчик может включать в себя модуль 202 сегментирования исходных слов, LDPC кодер 162, модулятор 164 отображения битов на символ и модуль 208 блокинга.

Фиг.2B иллюстрирует примерные этапы обработки входного потока информационных битов передатчиком.

Модуль 202 сегментирования исходных слов может быть использован для сегментирования входных потоков информационных битов на исходные слова

Исходное слово

Затем K-битные исходные слова

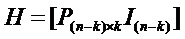

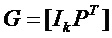

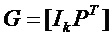

LDPC генератор 302 матрицы используют для генерирования LDPC матрицы H, проверки на четность, которая представляет собой двоичную (N-K) x N матрицу, например, N = 1344, K = 1176. LDPC коды функционально определяют посредством разреженной матрицей проверки на четность. (n, k) LDPC код является линейным двоичным блочным кодом C с k-мерным подпространством, равным {0, 1}n. Использование гауссовского исключения и переупорядочения столбцов может привести к эквивалентной матрице с проверкой на четность в систематической форме

На основании LDPC матрицы H проверки на четность, сгенерированной LDPC генератором 302 матрицы, модуль 304 порождающей матрицы генерирует порождающую матрицу G. Порождающая матрица G в систематической форме, которая соответствует H, может быть представлена как

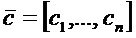

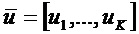

Интерфейс 306 ввода исходного слова принимает исходные слова из модуля 202 сегментирования исходных слов. Как обсуждалось ранее, принятое исходное слово может рассматриваться как вектор

В одном варианте осуществления порождающая матрица G может быть предварительно сохранена в LDPC кодере 162. После того, как исходные слова

Ссылаясь на фиг.2А и фиг.2В, кодированные кодовые слова

Модулированные кодовые слова могут быть дополнительно собраны в блоки данных (BLKs) с соответствующим размером в модуле 208 блокинга (этап 228). В варианте осуществления собранные блоки данных могут содержать 448 символов.

Фиг. 4A иллюстрирует пример блока данных или структуры кадра с одной несущей (SC), который может быть использован для упаковки собранных блоков данных (BLKs). Проиллюстрированный кадр, который указан в IEEE 802.11ad, включает в себя короткое настраиваемое поле (STF), поле оценки канала (CE), PHY заголовок, блоки данных SC (BLKs) и возможные автоматической регулировки усиления (AGC) и TRN-R/T подполя для подготовки формирования луча. Кадр может включать в себя множество BLKs, как показано на фиг.4А.

Фиг. 4B иллюстрирует пример конструкции блоков данных SC (BLKs) в соответствии со стандартом 802.11ad. На фиг. 4B каждый BLK состоит из 448 символов. 64-битный защитный интервал (GI) используется между каждыми двумя смежными BLKs для разделения соседних блоков данных.

LDPC коды с длиной кодового слова 672 в 802.11ad

Варианты осуществления высокоскоростного длинного LDPC кода, представленного в изобретении, основаны на LDPC кодах, указанных в IEEE 802.11ad, и, соответственно, теперь будет предоставлено краткое описание LDPC кодов IEEE 802.11ad, чтобы облегчить понимание вариантов осуществления, подробное описанных ниже. Поскольку кодированные LDPC кодовые слова

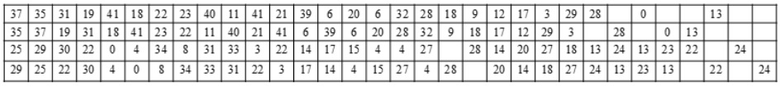

Фиг. 5A-5D иллюстрируют матрицы H проверки на четность четырех LDPC кодов, указанных в 802.11ad, со скоростями 1/2, 5/8, 3/4 и 13/16. В 802.11ad каждый LDPC код имеет общую длину кодового слова 672 бита. Кодовая скорость K/N обозначает, что исходное слово

Значение индекса i в каждом непустом элементе соты в матрице H обозначает подматрицу Pi циклической перестановки, полученную из ZXZ единичной матрицы P0 путем циклического сдвига столбцов матрицы P0 в правые столбцы i. Пустые записи указывают ZXZ матрицу всех нулей.

Фиг.5E иллюстрирует пример подматриц P1 и P3 циклической перестановки, полученных из примера Z x Z единичной матрицы P0, для которой Z = 4. P1 получают путем смещения столбцов P0 вправо на один элемент, и P3 получают путем смещения столбцов P0 вправо на три элемента. Как видно на фиг.5W, единичная матрица P0 включает в себя Z «1», расположенные по диагонали по всей матрице, причем все остальные значения равны «0».

На фиг.5А местоположение соты матрицы, имеющее значение индекса i = «0», представляет подматрицу P0, которая является 42 x 42 единичной подматрицей, и расположение верхней левой соты со значением индекса i = «40» на фиг.5А представляет подматрицу, полученную путем смещения столбцов P0 вправо на 40 элементов. Аналогично, любые ненулевые значения i подматрицы Pi на фиг.5B-5D также могут быть получены из соответствующей единичной матрицы P0.

На фиг.5А показана LDPC матрица Н проверки на четность с кодовой скоростью 1/2, H = 336 строк х 672 столбца, с Z = 42. На фиг. 5В показана LDPC матрица Н проверки на четность с кодовой скоростью 5/8 Н = 252 строк х 672 столбца с Z = 42. На фиг. 5C показана LDPC матрица Н проверки на четность с кодовой скоростью 3/4 H = 168 строк x 672 столбцов с Z = 42. На фиг. 5D показана LDPC матрица Н проверки на четность с кодовой скоростью 13/16 H = 126 строк x 672 столбцов с Z = 42. На фиг.5А-5D пустые записи представляют Z x Z подматрицы со всеми нулевыми записями.

Низкоскоростные LDPC коды с длинной длиной кодового слова 1344, предложенные для 802.11ay

Фиг. 6A-6D иллюстрируют четыре низкоскоростных LDPC кода, предложенные для 802.11ay в [REF 1] со скоростями 13/16, 3/4, 5/8 и 1/2. Как отмечено выше, кодовая скорость K/N обозначает, что исходное слово

Длинные LDPC коды, показанные на фиг.6A-6D, генерируют посредством двухэтапного процесса поднятия. В примере, показанном на фиг.6А, LDPC код 606 скорости 13/16 (1344, 1092) с длиной кодового слова 1344 генерируют путем применения матрицы 602 поднятия к базовой матрице 604. Базовая матрица 604 является LDPC секционированной матрицей длиной 672 скорости 13/16, указанная IEEE 802.11ad. Базовая матрица 604 скорости 13/16 с 3 строками и 16 столбцами подматриц соответствует коэффициенту поднятия Z = 42, применяемому к исходной матрице 126 строк x 672 столбцов из «1» и «0». Соответственно, первый подъем посредством коэффициента поднятия Z = 42 обеспечивает базовую матрицу 604 скорости 13/16, которую затем поднимают второй раз посредством применения матрицы 602 поднятия, чтобы генерировать LDPC код 606 скорости 13/16.

Как показано на фиг.6А, матрица 602 поднятия имеет такое же количество строк и столбцов (3 × 16), что и матрица 604 скорости 13/16 в 802.11ad. Каждому элементу соты в матрице 602 понятия назначают одно из трех возможных значений «1», «0» и «-1». Если подматрица базовой матрицы 604 является нулевой (то есть, имеет все нулевые записи), что обозначено как «-1», соответствующая запись в матрице 604 поднятия также обозначена как «-1». Например, запись в строке 1, столбец 16 матрицы 604 поднятия соответствует подматрице в строке 1, столбце 16 базовой матрицы 602. Как запись матрицы 604 поднятия, так и подматрица базовой матрицы 602 имеют значение «-1».

Для генерирования LDPC кода 606 13/16 с длиной кодового слова 1344 матрицу 602 поднятия применяют к LDPC базовой матрице 604 13/16 с длиной кодового слова 672. В частности, для подматрицы, имеющей значение «V» базовой матрицы 604, если запись соответствующей матрицы 602 поднятия имеет значение «1», применение матрицы 602 поднятия к базовой матрице 604 генерирует 4 подматрицы следующим образом:

Для подматрицы, имеющей значение «V» базовой матрицы 604, если запись соответствующей матрицы 602 поднятия имеет значение «0», применение матрицы 602 поднятия к базовой матрице 604 генерирует 4 подматрицы следующим образом:

На фиг.6А в примере подматрицы в строке 1 столбец 1 базовой матрицы 604, который имеет значение «29», в качестве соответствующей записи в строке 1 столбец 1 матрицы 602 поднятия имеет значение «1», применяя запись матрицы 602 поднятия с соответствующей подматрицей базовой матрицы 604, генерируют 4 подматрицы следующим образом:

Кроме того, в примере подматрицы в строке 3 столбец 9 базовой матрицы 604, который имеет значение «4», в качестве соответствующей записи в строке 3 столбца 9 матрицы 602 поднятия имеет значение «0», применяя запись матрицы 602 поднятия с соответствующей подматрицей базовой матрицы 604, генерируют 4 подматрицы следующим образом:

Для подматриц со значением «-1» в базовой матрице 604 соответствующие записи матрицы 602 поднятия также имеют значение «-1». Применение одной записи со значением «-1» в матрице 602 поднятия к соответствующей подматрице в базовой матрице 604 генерирует четыре нулевые подматрицы.

Аналогично, те же самые правила, описанные выше, для получения LDPC кода 606 скорости 13/16 с его длиной кодового слова 1344, могут применяться с соответствующими матрицами 602 поднятия, как показано на фиг. 6B-6D, к длине 672 кодового слова, кодовым скоростям 3/4, 5/8 и 1/2 базовых матриц 604, указанных в IEEE 802.11ad, для генерирования соответствующих LDPC кодов скорости 3/4, 5/8 и 1/2, каждый из которых имеет длину кодового слова 1344.

Высокоскоростной LDPC код

Стандарт IEEE 802.11ad определяет LDPC код с высокой кодовой скоростью 7/8 (REF 2). Аналогично, как отмечено выше, [REF 1] был предложен LDPC код скорости 7/8 с длиной кодового слова 1248. Генерируют LDPC код скорости 12/8 длины 1248 [REF 1] посредством выкалывания первых 96 битов четности из LDPC кода скорости 13/16 (1344,1092), представленный матрицей 606, показанной на фиг.6А, которая, как указано выше, получена из базового LDPC кода скорости 13/16 длины 672, указанного в 802.11ad. В реализации, передатчик не передает выколотые биты и приемник устанавливает равное правдоподобие для 1/0 для выколотых битов. Соответственно, предложенный LDPC код со скоростью 7/8 на фиг. 6A, который генерируют посредством выкалывания, приводит к длине кодового слова 1248, а не к длине кодового слова 1344, предложенной для длинного кода низкоскоростных LDPC кодов.

Как отмечалось выше в отношении фиг.4А, 4В, перед передачей LDPC кодовые слова

Например, на фиг.7А слева показан пример SC QPSK блокинга для LDPC кода со скоростью 7/8, который использует длину кодового слова 1344 (N = 1344, K = 1176), и справа показан пример SC QPSK блокинга для DLPC кода со скоростью 7/8, который использует выколотую длину кодового слова 1248 (N = 1248, K = 1092). Пример на фиг. 7А использует QPSK модуляцию для отображения битов на символы. При (N = 1344, K = 1176) QPSK 1344-битное кодовое слово после модуляции становится 672-символьным кодовым словом. Каждые три SC блока данных (BLK1, BLK2, BLK3), каждый из которых содержит 448 символов, составлены из 2 кодовых слов символов (каждый блок состоит из 1 или 2 кодовых слов). Для сравнения, при (N = 1248, K = 1092) QPSK 1248-битовое кодовое слово после модуляции становится 624-символьным кодовым словом. В результате, процесс блокинга становится более сложным: каждые 39 блоков данных составляют из 28 кодовых слов, и каждый блок данных составлен из одного или двух кодовых слов.

На фиг.7В показаны примеры SC 16QAM блокинга с (1344, 1176) LDPC (левая сторона) по сравнению с (1248, 1092) LDPC (правая сторона). С (1344, 1176) LDPC, с 16QAM, одно 1344-битное кодовое слово после модуляции становится одним 336-символьным кодовым словом. Каждые три SC блока данных построены из четырех 336 символьных кодовых слов, причем каждый блок данных из 448 символов составлен из двух символьных кодовых слов. Однако, с (1248, 1092) LDPC каждое из кодированных кодовых слов содержит 1248 битов, которые становятся кодовым словом из 312 символов после 16 QAM модуляции. В результате, процесс блокинга становится более сложным: каждые 39 блоков данных составлены из 56 кодовых слов.

Аналогично, на фиг.7С показаны примеры SC 64QAM блокинга с (1344, 1176) LDPC (левая сторона) по сравнению с (1248, 1092) LDPC (правая сторона). С (1344, 1176) LDPC, с 64QAM, одно 1344-битное кодовое слово после модуляции становится одним 224 символьным кодовым словом. Каждый блок данных из 448 символов составлен из двух 224 символьных кодовых слов. Однако с (1248, 1092) LDPC одно 1248-битное кодовое слово после модуляции становится одним 208 символьным кодовым словом. В результате процесс блокинга становится более сложным: каждые 13 блоков данных составлены из 28 кодовых слов и каждый блок данных составлен из 3 или 4 кодовых слов.

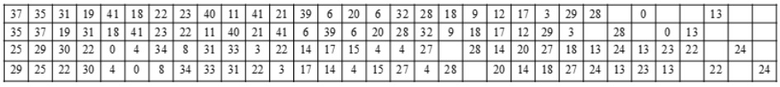

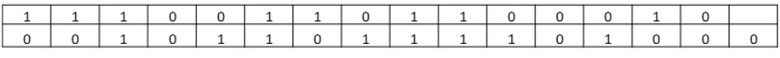

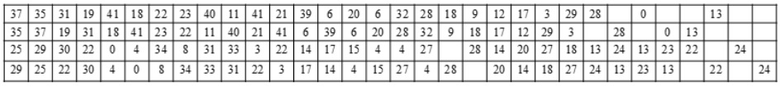

[REF 2] предлагает высокоскоростной LPDC код 7/8 для короткой длины кодового слова N = 672. Ссылаясь на фиг.8, LPDC матрицу Hn 860 скорость 7/8 длины 672 в [REF 2] получают путем суммирования строк из LDPC матрицы H 850 заданной скорости ¾ в 802.11ad длины 672 (672, 504). Как отмечено выше, LDPC матрицу H 850 заданной скорости ¾ в 802.11ad длины 672 получают с использованием коэффициента поднятия Z = 42 для разделения исходной двоичной матрицы из 168 строк (N-K = 168) на 672 столбца (N = 672), обеспечивая LPDC базовую матрицу H 850 3/4 скорости 672 длины, которая может быть представлена как 4 строки (R = (N-K/42)) и 16 столбцов (C = N/42), причем каждая подматрица Pi представлена в элементе массива значением индекса i, которое представляет циклический сдвиг, примененный к единичной матрице (или «пусто» или «-» для обозначения «нулей» всей нулевой подматрицы). Выбранные строки из базовой LPDC матрицы H 850 3/72 длины 672 суммируют вместе для обеспечения LPDC матрицы Hn 850 3/4 672 длины. В частности, подматрицы из первой строки R1 и третьей строки R3 базовой матрицы H 850 суммируют для предоставления подматриц для соответствующих записей столбцов в первой строке новой LDPC матрицы Hn 850, и подматрицы из второй строки R2 и четвертой строки R4 базовой матрицы H 850 суммируют с использованием сложения по модулю-2 для предоставления подматриц для соответствующих записей столбцов во второй строке новой LDPC матрицы Hn 850. Для пояснения на фиг. 9 показано добавление матриц циклической перестановки для упрощенного случая, где Z = 4, с использованием сложения по модулю-2.

Высокоскоростной 7/8 длинный LDPC код с длиной N=1344

Далее будут описаны примерные варианты осуществления, которые, в частности, относятся к высокоскоростному длинному LDPC коду, который обеспечивает длину кодового слова, соответствующую заданной для низкоскоростных кодов, а именно N=1344.

Фиг.10 представляет способ генерирования 7/8 LDPC матрицы H1 1020 с длиной кодового слова N = 1344 согласно одному примерному варианту осуществления. В примере, показанном на фиг. 10, в качестве базовой матрицы используют LDPC матрицу H 850 со скоростью ¾, заданной в 802.11ad, длиной 672 (672, 504), однако, коэффициент поднятия увеличивают с Z = 42 до Z = 84 для получения LDPC матрицы Hint 1010 скорости ¾ длины 1344 в качестве промежуточной матрицы. В частности, для построения LDPC матрицы Hint 1010 скорости ¾ с размером кодового слова 672 x 2 = 1344, структура базовой матрицы 850 и сдвиги положения столбца остаются прежними, но коэффициент поднятия увеличивается с Z = 42 до Z = 84. Например, двоичная базовая матрица 850 3/4 с длиной кодового слова 672 стандарта 802.11ad содержит 168 строк x 672 столбца, Z = 42. Как показано на фиг.10, разделенная базовая матрица 840 3/4 содержит 4 строки x 16 столбцов подматриц, и каждая подматрица имеет размер Z x Z (42 x 42). Когда коэффициент Z поднятия увеличивают с 42 до 84, промежуточная разделенная LDPC матрица Hint 1010 скорости ¾ длиной 1344 включает в себя 4 строки x 16 столбцов подматриц, представляющих двоичную матрицу из 336 строк x 1344 столбцов.

В примерном варианте осуществления выбранные строки промежуточной LDPC матрицы Hint скорости ¾ длины 1344 суммируют для генерирования LDPC матрицы Hl 1020 скорости 7/8 с длиной кодового слова N = 1344. В частности, подматрицы из первой строки R1 и третьей строки R3 промежуточной LDPC матрицы Hint суммируют с использованием сложения по модулю 2 для предоставления подматрицы для соответствующих записей столбцов в первой строке новой LDPC матрицы Hl 1020, и подматрицы из второй строки R2 и четвертой строки R4 промежуточной LDPC матрицы Hint суммируют с использованием сложения по модулю 2 для предоставления подматрицы для соответствующих записей столбца во второй строке новой LDPC матрицы Hl 1020.

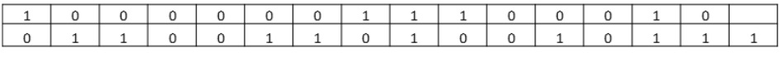

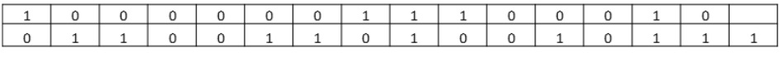

Фиг. 11 представляет дополнительный примерный вариант осуществления способа для генерирования LDPC матрицы HL 1130 со скоростью 7/8 с длиной кодового слова N = 1344 в соответствии с одним примерным вариантом осуществления. В примере по фиг.11 LDPC матрицу H 850 скоростью ¾, указанной в 802.11ad, длиной 672 (672, 504) снова используют в качестве базовой матрицы, однако вместо использования расширенного коэффициента поднятия, как обсуждалось в непосредственно предшествующем примере, используют матрицу 1110 поднятия для генерирования промежуточной матрицы Hint 1120. Матрицу 1110 поднятия выбирают посредством поиска оптимизации с использованием критерия для получения оптимизированной частоты ошибок. В проиллюстрированном варианте осуществления матрицу 1110 поднятия выбирают так, что ее первая и третья строка являются дополнительными и ее вторая и четвертая строка являются дополнительными.

Матрицу 1110 поднятия применяют к LDPC матрице H 850 с заданной в 802.11ad скорости ¾ длины 672 (672, 504) для генерирования промежуточной матрицы Hint 1120 таким же образом, как описано выше в отношении фиг.6A-6D. Полученная промежуточная матрица Hint 1120 включает в себя 8 строк по 32 столбца элементов подматрицы, причем каждый элемент подматрицы обозначен индексным значением i, указывающим циклический сдвиг, примененный к ZXZ (Z = 42) единичной матрице P0, или нулевым значением для указания всех «0» подматрицы. Таким образом, разделенная промежуточная матрица Hint 1120 представляет собой двоичную матрицу размером 336 строк на 1344 столбцов.

Как показано на фиг.11, периодические строки промежуточной матрицы Hint 1120 суммируют для генерирования 7/8 LDPC матрицы Hl 1130 с длиной кодового слова N = 1344. В частности, подматрицы из первой строки R1 и пятой строки R5 промежуточной матрицы Hint 1120 суммируют с использованием сложения по модулю 2, чтобы обеспечить подматрицы для соответствующих записей столбцов в первой строке новой LDPC матрицы Hl 1130. Аналогично, вторая и шестая строки промежуточной матрицы Hint 1120 суммируют во второй строке новой LDPC матрицы Hl 1130; третья и седьмая строки промежуточной матрицы Hint 1120 суммируются для получения третьей строки новой LDPC матрицы Hl 1130; и четвертая и восьмая строки промежуточной матрицы Hint 1120 суммируют для получения четвертой строки новой LDPC матрицы Hn 1130. Как показано на фиг.11, разделенная LDPC матрица Hl 1130 включает в себя 4 строки из 32 столбцов элементов подматрицы, каждый элемент подматрицы представляет ZXZ подматрицу с Z = 42, так что двоичная матрица Hl имеет размер 168 строк на 1344 столбца.

Должно быть понятно, что пример на фиг.11 основан на комбинации этапа поднятия и этапа суммирования для генерирования матрицы Hl 1130.

По меньшей мере, в некоторых примерах вместо оптимизированной матрицы 1110 поднятия, показанной на фиг.11, может использоваться другая оптимизированная матрица поднятия, и в этой связи, на фиг.12 показан пример дополнительной оптимизированной матрицы 1210 поднятия, которая может быть использована в нескольких примерах вместо матрицы 1110 поднятия.

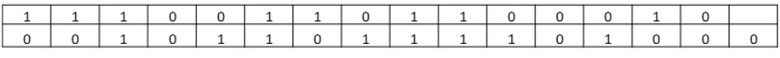

Фиг. 13 представляет дополнительный примерный вариант осуществления способа для генерирования LDPC матрицы Hl 1330 со скоростью 7/8 с длиной кодового слова N = 1344 в соответствии с другим примерным вариантом осуществления. В примере, показанном на фиг.13, LDPC матрица H 850 с скоростью ¾, заданной в 802.11ad, длиной 672 (672, 504) снова используют в качестве базовой матрицы и, в частности, используют для генерирования 7/8 LPDC матрицы Hn 860 длины 672 в качестве промежуточной матрицы таким же образом, как описано выше со ссылкой на фиг. 8. Матрица 1310 поднятия, оптимизированная по 2 строкам на 16 столбцов, применяется с использованием тех же технологий матрицы поднятия, описанных выше, к 7/8 LPDC матрице Hn 860 длины 672 для получения LDPC матрицы Hl 1330 скорости 7/8 длины 1344. Как показано на фиг.13, разделенная LDPC матрица Hl 1320 включает в себя 8 строк по 32 столбца элементов подматрицы, причем каждый элемент подматрицы представляет ZXZ подматрицу с Z = 42, например, двоичную матрицу Hl 1320 с размером 336 строк на 1344 столбца.

В примерном варианте осуществления выбирают оптимизированную матрицу поднятия путем выполнения поиска оптимизации матрицы поднятия, которая обеспечивает оптимизированную частоту ошибок. В случае оптимизированной матрицы 1310 поднятия в некоторых примерах вариантов осуществления применяют случайный перемежитель между кодированием в LDPC кодере и модуляцией в бит-символьном модуляторе 206.

По меньшей мере в некоторых примерах, вместо оптимизированной матрицы 1310 поднятия, показанной на фиг. 13, может быть использована другая оптимизированная матрица поднятия, и в этой связи, на фиг. 14 показан пример дополнительной оптимизированной матрицы 1410 поднятия, которая может быть использована в некоторых примерах вместо матрицы 1310 поднятия. В случае оптимизированной матрицы 1410 поднятия в некоторых примерах вариантов осуществления используют между кодированием в LDPC кодере и модуляцией в бит-символьном модуляторе 206 регулярный перемежитель строка-столбец.

По меньшей мере, в некоторых конфигурациях варианты осуществления 7/8 LDPC матрицы Н1 длиной 1344 обеспечивают LDPC структуру, которая может обеспечивать одну или несколько из следующих признаков: быть обратно совместимой с 11ad; возможность использования 11ad; обеспечивать LDPC код со скоростью 7/8, который поддерживает длину кодового слова равной 1344 неизменной по сравнению с другими LPDC кодами с различными скоростями кодирования, предлагаемыми IEEE 802.11ay; снизить избыточность (заполнение нулями) при кодировании и блокинге с одной несущей; оптимизировать новый 7/8 LDPC код для получения сопоставимой или повышенной производительности по сравнению с решением выкалывания.

Декодер и способ декодирования

LDPC кодированный сигнал может быть принят в приемнике STA 102 или AP 104. Как проиллюстрировано в примере на фиг. 15A, приемник включает в себя модуль 1502 выравнивания и деблокинга, демодулятор 180, LLR калькулятор 1506 и LDPC декодер 190. Возможно, LLR калькулятор 1506 может быть компонентом демодулятора 180. Как показано на фиг.15B, принятый LDPC кодированный сигнал обрабатывают модулем 1502 выравнивания и деблокинга, который сначала выравнивает принятый сигнал 1501 для снижения межсимвольной помехи, вызванной каналом, по которому передают принятый сигнал, и затем выполняют деблокинг выровненного сигнала для восстановления символов кодовых слов (этап 1522). Демодулятор 180 демодулирует символы кодовых слов после деблокинга в кодовые слова в битах (этап 1524), например, посредством BPSK, QPSK, 16QAM или 64QAM. LLR калькулятор 180 может быть использован для генерирования логарифмического отношения правдоподобия значения битов символов кодового слова после деблокинга (этап 1526). Логарифмическое отношение правдоподобия может быть использовано в качестве входного значения LDPC декодера 190. Затем LDPC декодер 190 может использовать LDPC матрицу Нn, которую применяют при кодировании исходных слов, для декодирования демодулированного сигнала, причем сигнал имеет вектор S строки 1 × N (этап 1528). LDPC декодер 190 генерирует вектор

Как описано выше, LDPC информация кодирования передаваемого сигнала может содержаться в передаваемом кадре, например, информация LPDC кода Hn = (N-K) x N скорости K/N LDPC матрицы, используемой для кодирования исходных слов. В одном варианте осуществления настоящего изобретения LPDC код Hn = (N-K) x N скорости K/N может быть использован в LDPC декодере 190 с коэффициентом Z поднятия. Как описано в процессе кодирования, Hn содержит множество подматриц, и каждая подматрица имеет размер Z x Z. Способы генерирования матрицы проверки на четность были описаны в процессе кодирования.

Кодовые слова в битах могут быть декодированы с помощью матрицы H1, например, с использованием алгоритма передачи сообщений (MPA) со LLR значениями. Как показано в примере на фиг.17, LDPC декодирование с использованием MPA представляет собой алгоритм итеративного декодирования, который использует структуру графа Таннера, который является графическим представлением LPDC матрицы H1 проверки на четность. В LDPC декодере 190 каждый проверочный узел 1702 определяет значение стертого бита на основе LLR значения, если он является единственным стертым битом в своем уравнении проверки на четность. Сообщения, передаваемые вдоль ребер 1706 графа Таннера. Для каждой итерации алгоритма каждый переменный узел 1704 отправляет сообщение («внешняя информация») каждому проверочному узлу 1702, к которому подключен переменный узел 1704. Каждый проверочный узел 1702 отправляет сообщение («внешняя информация») переменным узлам 1704, к которым подключен проверочный узел 1702. «Внешний» в данном контексте означает, что информация, которой уже обладают проверочные узлы 1702 или переменные узлы 1704, не передается этому узлу. Апостериорная вероятность для каждого бита кодового слова вычисляют на основании принятого сигнала в LLR калькуляторе 1506 и ограничений четности, определенных в H1, а именно, чтобы быть действительным кодовым словом

В многоуровневой архитектуре LDPC декодера 190 Z процессоры параллельных проверочных узлов последовательно обрабатывают сообщения ребер относительно подматрицы Z строк матрицы проверки на четность. В одном примере Z = 42, и ребра равны 16. Структура циклического сдвига упрощает архитектуру декодера, которая позволяет обеспечить параллельные процессоры простой многорегистровой схемой циклического сдвига. При завершении процесса обработки уровня, повторно инициализируют процессоры проверки на четность и выполняют процесс обработки следующего уровня.

Настоящее изобретение предоставляет некоторые примерные алгоритмы и вычисления для реализации примеров раскрытых способов и систем. Однако настоящее изобретение не связано каким-либо конкретным алгоритмом или расчетом. Хотя настоящее изобретение описывает способы и процессы с этапами в определенном порядке, один или несколько этапов способов и процессов могут быть опущены или изменены в зависимости от ситуации. Один или несколько этапов могут быть выполнены в порядке, отличном от того, в котором они описаны, в зависимости от ситуации.

Посредством вышеописанных вариантов осуществления настоящее изобретение может быть реализовано с использованием только аппаратного обеспечения, или с использованием программного обеспечения и необходимой универсальной аппаратной платформы, или с помощью комбинации аппаратного и программного обеспечения. Исходя из такого понимания, техническое решение по настоящему изобретению может быть воплощено в форме программного продукта. Программный продукт может храниться на энергонезависимом или постоянном носителе данных, который может быть компактным диском только для чтения (CD-ROM), флэш-накопителем USB или жестким диском. Программный продукт включает в себя ряд инструкций, которые позволяют компьютерному устройству (персональному компьютеру, серверу или сетевому устройству) выполнять способы, предусмотренные в вариантах осуществления настоящего изобретения.

Хотя настоящее изобретение и его преимущества были описаны подробно, следует понимать, что различные изменения, замены и изменения могут быть сделаны в настоящем документе без отклонения от изобретения, как определено в прилагаемой формуле изобретения.

Кроме того, объем настоящего изобретения не предназначен для ограничения конкретными вариантами осуществления способа, машины, способа изготовления, композиции вещества, средств, способов и этапов, описанных в описании. Специалист в данной области техники легко поймет из настоящего изобретения, что процессы, машины, способ изготовления, композиция вещества, средство, способы или этапы, существующие в настоящее время, или которые будут разработаны позднее, выполняют, по существу, ту же функцию или предназначены для получения, по существу, того же результата, что и соответствующие варианты осуществления, описанные в данном документе, могут быть использованы в соответствии с настоящим изобретением. Соответственно, прилагаемая формула изобретения включает в себя такие процессы, машины, способы производства, композиции веществ, средства, способы или этапы.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБЫ И СИСТЕМЫ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ LDPC КОДОВ | 2016 |

|

RU2716044C1 |

| MCS ДЛЯ ДЛИННЫХ LDPC КОДОВ | 2017 |

|

RU2725430C1 |

| УСТРОЙСТВО И СПОСОБ ДЛЯ ГЕНЕРИРОВАНИЯ МАТРИЦЫ ПРОВЕРКИ ЧЕТНОСТИ В СИСТЕМЕ СВЯЗИ С ИСПОЛЬЗОВАНИЕМ ЛИНЕЙНЫХ БЛОЧНЫХ КОДОВ И УСТРОЙСТВО ПЕРЕДАЧИ/ПРИЕМА И СПОСОБ ДЛЯ ИСПОЛЬЗОВАНИЯ ЭТОГО | 2010 |

|

RU2537806C2 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ И УСТРОЙСТВО СВЯЗИ | 2017 |

|

RU2740154C1 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ И УСТРОЙСТВО СВЯЗИ | 2017 |

|

RU2740151C1 |

| АППАРАТУРА, СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ И АППАРАТУРА СВЯЗИ | 2018 |

|

RU2758968C2 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ, ПРИСПОСОБЛЕНИЕ И УСТРОЙСТВО СВЯЗИ | 2018 |

|

RU2769096C2 |

| Способ и устройство обработки информации и устройство связи | 2017 |

|

RU2667772C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ | 2005 |

|

RU2370886C2 |

| СПОСОБ КОДИРОВАНИЯ КОДА РАЗРЕЖЕННОГО КОНТРОЛЯ ЧЕТНОСТИ | 2004 |

|

RU2308803C2 |

Группа изобретений относится к технологиям мобильного радиоинтерфейса и может быть использована для кодирования и декодирования двоичных кодов с низкой плотностью проверок на четность (LDPC). Техническим результатом является обеспечение согласования длины кодового слова для разных скоростей кодирования. Способ содержит этапы, на которых: принимают вектор

1. Способ кодирования исходного слова, содержащий этапы, на которых:

принимают вектор

генерируют вектор

H1 получают из базовой матрицы H проверки на четность посредством применения оптимизированной матрицы поднятия к базовой матрице H проверки на четность, причем оптимизированная матрица поднятия является либо:

либо:

2. Способ по п. 1, в котором H1 получают из базовой матрицы H проверки на четность посредством:

применения оптимизированной матрицы поднятия к базовой матрице H проверки на четность для получения промежуточной матрицы проверки на четность;

суммирования разных строк в промежуточной базовой матрице проверки на четность для получения Hl.

3. Способ по п. 2, в котором применение матрицы поднятия к базовой матрице H проверки на четность для получения промежуточной матрицы проверки на четность содержит:

применение оптимизированной двоичной матрицы поднятия с 4 строками на 16 столбцов к разделенной матрице с 4 строками на 16 столбцов для получения промежуточной матрицы проверки на четность с 8 строками и 32 столбцами подматриц размером 42 бита на 42 бита, каждая из которых является либо циклической перестановкой двоичной единичной матрицы 42 бита на 42 бита, либо содержит все нулевые значения.

4. Способ по п. 2, в котором суммирование разных строк в промежуточной базовой матрице проверки на четность для получения Hl содержит:

суммирование первой и пятой строк промежуточной матрицы проверки на четность для получения первой строки Hl;

суммирование второй и шестой строк промежуточной матрицы проверки на четность для получения второй строки Hl;

суммирование третьей и седьмой строк промежуточной матрицы проверки на четность для получения третьей строки Hl и

суммирование четвертой и восьмой строк промежуточной матрицы проверки на четность для получения четвертой строки Hl.

5. Способ по любому из пп.1-4, в котором базовая матрица H проверки на четность является LDPC матрицей, определенной в 802.11ad для скорости ¾ длины 672 кодовых слова.

6. Способ по любому из пп.1-5, в котором H1 представляет собой

7. Способ по п.1, в котором суммируют строки 1 и 3 промежуточной базовой матрицы проверки на четность.

8. Способ по п.1 или 7, в котором суммируют строки 2 и 4 промежуточной базовой матрицы проверки на четность.

9. Способ по любому из пп.1-8 в котором матрица поднятия составлена из пустых записей строка-столбец и непустых записей строка-столбец и пары обеих непустых записей, соответствующие суммированным подматрицам промежуточной базовой матрицы проверки на четность, являются комплементарными.

10. Способ кодирования исходного слова, содержащий этапы, на которых:

принимают вектор

генерируют вектор

H1 получают из базовой матрицы H проверки на четность посредством суммирования различных строк в базовой матрице H проверки на четность для получения промежуточной матрицы проверки на четность и применения матрицы поднятия к промежуточной базовой матрице проверки на четность для получения H1.

11. Способ по п. 10, в котором матрица поднятия представляет собой

или

12. Способ по п. 10 или 11, в котором базовая матрица H проверки на четность является LDPC матрицей, определенной в 802.11ad для скорости ¾ длины 672 кодовых слова.

13. Способ кодирования исходного слова, содержащий этапы, на которых:

принимают вектор

генерируют вектор

H1 получают из базовой матрицы H проверки на четность, предназначенной для поддержки генерирования кодового слова для размера вектора кодового слова в размере вектора слова, который меньше K/N, причем

14. Способ по п.13, в котором H1 получают из базовой матрицы H проверки на четность посредством суммирования различных строк в базовой матрице H проверки на четность для получения промежуточной матрицы проверки на четность, и применения матрицы поднятия к промежуточной базовой матрице проверки на четность для получения Н1.

15. Способ по п. 13 или 14, в котором базовая матрица H проверки на четность представляет собой матрицу с низкой плотностью проверок на четность (Low density parity check, LDPC) с низкой скоростью 3/4, предназначенную для поддержки генерирования кодового слова для размера выходного вектора кодового слова, равного 672 битам из размера входного вектора исходного слова, равного 504 бит, причем базовая матрица H проверки на четность может быть разделена на матрицу из 4 строк по 16 столбцов:

при этом каждый разделенный матричный элемент представляет соответствующую подматрицу размером 42 на 42 бита, в котором каждая подматрица размером 42 на 42 бита является либо циклической перестановкой двоичной единичной матрицы размером 42 бита на 42 бита, либо содержит все нулевые значения, элементы, которые соответствуют циклической перестановке двоичной единичной матрицы, указаны целочисленным индексным значением, указывающим циклический сдвиг, примененный к двоичной единичной матрице, для получения подматрицы, соответствующей элементу, при этом элементы, соответствующие подматрице, содержащей все нулевые значения, обозначены пустым элементом.

16. Способ по п. 13 или 14, в котором N = 1344 и отношение K / N составляет 7/8.

17. Способ по п.13, в котором N = 1344 и отношение K / N составляет 7/8 и

увеличение коэффициента поднятия, применяемого к базовой матрице H проверки на четность, для получения расширенной базовой матрицы проверки на четность, содержит: увеличение размера двоичной единичной матрицы размером 42 бита на 42 бита до двоичной единичной матрицы размером 84 бита на 84 и определение расширенной матрицы 4 строки на 16 столбцов подматриц размером 84 на 84 бита, соответствующей базовой матрице Н проверки на четность; а

суммирование различных строк в расширенной базовой матрице проверки на четность для получения H1 содержит: суммирование подматриц из первой строки и третьей строки расширенной базовой матрицы проверки на четность с использованием сложения по модулю 2 для предоставления подматриц для соответствующих записей столбцов в первой строке H1 1020 и суммирование подматриц из второй строки и четвертой строки расширенной базовой матрицы проверки на четность, используя сложение по модулю 2 для предоставления подматриц для соответствующих записей столбцов во второй строке Hl 1020.

18. Способ по п.13, в котором N = 1344, а отношение K/N составляет 7/8, при этом:

этап применения матрицы поднятия к базовой матрице Н проверки на четность для получения промежуточной матрицы проверки на четность содержит подэтап, на котором применяют оптимизированную двоичную матрицу поднятия с 4 строками на 16 столбцов к разделенной матрице с 4 строками на 16 столбцов для получения промежуточной матрицы проверки на четность с 8 строками и 32 столбцами подматриц размером 42 бита на 42 бита, каждая из которых является либо циклической перестановкой двоичной единичной матрицы 42 бита на 42 бита, либо содержит все нулевые значения; а

этап суммирования разных строк в промежуточной базовой матрице проверки на четность для получения H1 содержит подэтапы, на которых: суммируют первую и пятую строки промежуточной матрицы проверки на четность для получения первой строки H1; суммируют вторую и шестую строки промежуточной матрицы проверки на четность для получения второй строки Hl; суммируют третью и седьмую строки промежуточной матрицы проверки на четность для получения третьей строки Hl и суммируют четвертую и восьмую строки промежуточной матрицы проверки на четность для получения четвертой строки H1, причем матрица поднятия является:

или

19. Способ по п.18, в котором H1 представлена:

20. Способ по п.14, в котором N = 1344 и отношение K/N составляет 7/8, при этом:

этап суммирования различных строк в базовой матрице Н проверки на четность для получения промежуточной матрицы проверки на четность содержит подэтапы, на которых суммируют первую строку и третью строку разделенной базовой матрицы проверки на четность и суммируют вторую строку и четвертую строку разделенной базовой матрицы проверки на четность для получения промежуточной матрицы проверки на четность, имеющей две строки и представленной в виде:

при этом этап применения матрицы поднятия к промежуточной базовой матрице проверки на четность для получения H1 содержит подэтап, на котором применяют оптимизированную двоичную матрицу поднятия 2 строки на 16 столбцов к разделенной промежуточной матрице проверки на четность 2 строки на 16 столбцов для получения Hl с 4 строками и 32 столбцами подматриц 42 бита на 42 бита, каждая из которых является либо циклической перестановкой из двоичной единичной матрицы 42 бита на 42 бита, либо содержит все нулевые значения.

21. Способ по п.14, в котором матрица поднятия представлена:

22. Способ по п.14, в котором матрица поднятия представлена:

23. Способ по п.13 или 14, в котором H1 представлена как:

24. Устройство, характеризующееся тем, что выполнено с возможностью осуществления способа по любому из пп. 1-23.

25. Машиночитаемый носитель данных, хранящий программу, при этом программа вызывает, при исполнении, выполнение компьютером способа по любому из пп. 1-23.

| US 8443254 B2, 14.05.2013 | |||

| US 8910025 B2, 09.12.2014 | |||

| US 7346832 B2, 18.03.2008 | |||

| US 8433984 B2, 30.04.2013 | |||

| СПОСОБ ДЛЯ КОДИРОВАНИЯ СООБЩЕНИЯ K' ДАННЫХ ДЛЯ ПЕРЕДАЧИ ОТ ПЕРЕДАЮЩЕЙ СТАНЦИИ К ПРИНИМАЮЩЕЙ СТАНЦИИ И СПОСОБ ДЛЯ ДЕКОДИРОВАНИЯ, ПЕРЕДАЮЩАЯ СТАНЦИЯ, ПРИНИМАЮЩАЯ СТАНЦИЯ И ПРОГРАММНОЕ ОБЕСПЕЧЕНИЕ | 2007 |

|

RU2438236C2 |

Авторы

Даты

2020-10-07—Публикация

2017-03-03—Подача