Изобретение относится к специализированной вычислительной технике и может быть использовано при создании быстродействующих устройств обработки информации и вычислительной техники.

Известны различные аналого-цифровые преобразователи (АЦП), обеспечивающие преобразование аналогового сигнала в двоичный код, построенные на основе использования электронных функциональных элементов [У. Титце, К. Шенк. Полупроводниковая схемотехника. - М.: Мир, 1983]. Недостатками данных АЦП являются низкое быстродействие, уменьшающееся с ростом разрядности АЦП, и большая сложность.

Также известны АЦП на основе модуляторов типа Маха-Цендера [Семенов А.С. и др. Интегральная оптика для систем передачи и обработки информации. - /М.: Радио и связь, 1990. - 176 с., рис. 7, 6], обеспечивающие преобразование электрического входного сигнала в код Грея. Недостатками данных АЦП являются: невозможность преобразования входного аналогового сигнала в позиционный двоичный код, низкое общее быстродействие АЦП. Наиболее близким по технической сущности к предлагаемому устройству является параллельный АЦП [Волович Г.И. Схемотехника аналоговых и аналого-цифровых устройств. - 2-е изд. - М.: «Додека», 2007, с.436, рис.9.4], включающий 2N-1 компараторов, где N - разрядность АЦП, включенных параллельно источнику входного сигнала, источник опорного напряжения, с выхода которого с помощью резистивных делителей формируется эквидистантное опорное напряжение для компараторов. Сигналы с выходов компараторов преобразуются в двоичное число с помощью приоритетного шифратора, выход которого является выходом АЦП. Недостатком данного устройства является высокая сложность его технической реализации.

Заявленное изобретение направлено на решение задачи упрощения устройства и повышения быстродействия преобразования в позиционный двоичный код электрических аналоговых сигналов.

Поставленные задачи возникают при создании быстродействующих устройств обработки информации в системах управления и связи, обеспечивающих обработку информации в гигагерцовом диапазоне.

Технический результат достигается тем, что в устройство введены N-выходной делитель напряжения и (N+1) разрядных блоков, выходы которых являются выходами (N+1) разрядов АЦП, которые являются соответствующими выходами устройства, каждый j-й разрядный блок (j =1,2,..., N-1) содержит первый электронный ключ, блок вычитания, второй электронный ключ, повторитель напряжения, компаратор в режиме нуль-индикации, при этом N-й разрядный блок содержит блок вычитания, второй электронный ключ, повторитель напряжения, компаратор в режиме нуль-индикации, а нулевой разрядный блок содержит первый электронный ключ, выход источника опорного напряжения подключен ко входу делителя напряжения, i-й выход которого подключен ко входу вычитаемого блока вычитания i-го разрядного блока (i=1...N), вход устройства подключен ко входу уменьшаемого блока вычитания N-го разрядного блока, а вход уменьшаемого блока вычитания i-го разрядного блока объединен с информационными входами первого и второго электронных ключей, при этом выход второго электронного ключа i-го разрядного блока подключен через компаратор к выходу i-го разрядного блока и является соответствующим выходом устройства для i-го разряда АЦП, а в i-м разрядном блоке выход блока вычитания подключен к управляющим входам первого и второго электронных ключей и входу повторителя напряжения, выход которого объединен с выходом первого электронного ключа (i-1)-го разрядного блока и подключен ко входу уменьшаемого блока вычитания (i-1)-го разрядного блока, кроме выхода повторителя напряжения первого разрядного блока, объединенного с выходом первого электронного ключа нулевого разрядного блока и подключенного к выходу нулевого разряда АЦП.

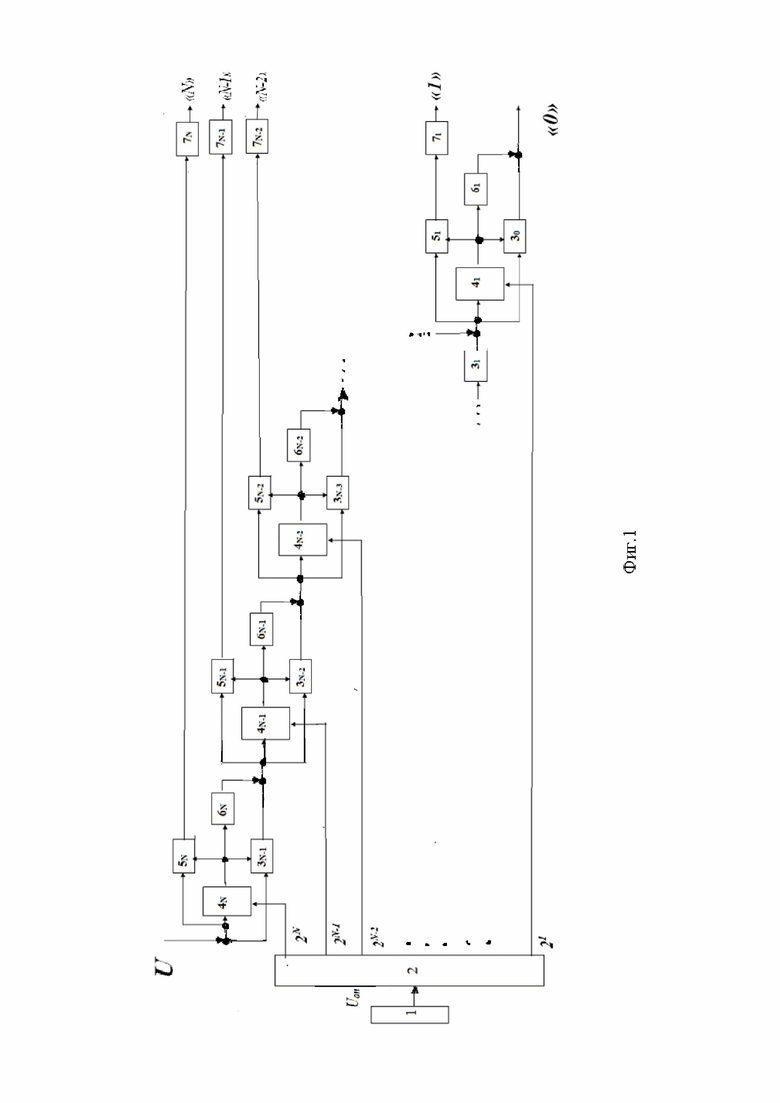

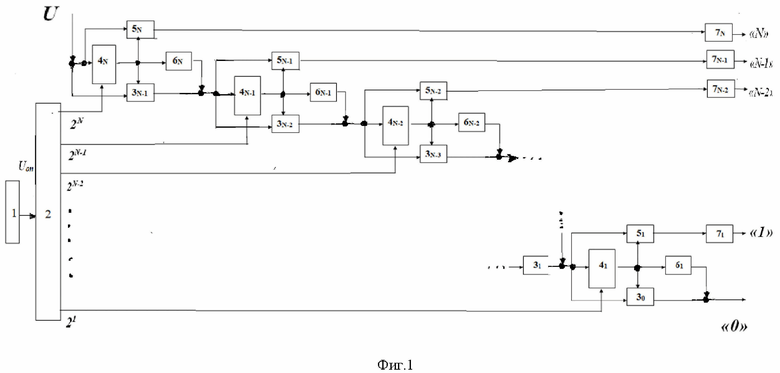

На фиг.1 представлена функциональная схема АЦП.

Устройство содержит источник опорного напряжения 1, N-выходной делитель напряжения 2 и (N+1) разрядных блоков, выходы которых являются выходами (N+1) разрядов АЦП, которые являются соответствующими выходами устройства. Каждый i-й разрядный блок, кроме N-го и нулевого (i=1,2,..., N-1), содержит первый электронный ключ (ЭК) 3i, блок вычитания 4i, второй ЭК 5i, повторитель напряжения (ПН) 6i и компаратор 7i. N-й разрядный блок содержит блок вычитания 4N, второй ЭК 5N, ПН 6N и компаратор 7N, нулевой разрядный блок содержит первый ЭК 30 . Первые ЭК 3N-1,3N-2,...,30 открываются отрицательным напряжением, а вторые ЭК 5N, 5N-1, ..., 51 и ПН 6N, 6N-1, ..., 61 - запираются отрицательным напряжением. Компараторы 7i (i=1,...,N) работают в режиме нуль-индикации.

Выход источника опорного напряжения 1 подключен ко входу делителя напряжения 2, i-й выход которого подключен ко входу вычитаемого блока вычитания 4i i-го разрядного блока (i=1...N). Вход устройства подключен ко входу уменьшаемого блока вычитания 4N N-го разрядного блока. Вход уменьшаемого блока вычитания 4i i-го разрядного блока объединен с информационными входами первого ЭК 3i-1 и второго ЭК 5i i-го разрядного блока. Выход второго ЭК 5i i-го разрядного блока подключен через компаратор 7i к выходу i-го разрядного блока и является соответствующим выходом устройства. Выход блока вычитания 4i i-го разрядного блока подключен к управляющим входам первого ЭК 3i-1 и второго ЭК 5i i-го разрядного блока и входу его ПН 6i, выход которого объединен с выходом первого ЭК 3i-1 (i-1)-го разрядного блока и подключен ко входу уменьшаемого блока вычитания 4i-1 (i-1)-го разрядного блока, кроме выхода ПН 61 первого разрядного блока, объединенного с выходом первого ЭК 30 нулевого разрядного блока и подключенного к выходу нулевого разряда АЦП.

Устройство работает следующим образом.

С момента включения устройства напряжение Uоп с выхода источника опорного напряжения 1 поступает на вход делителя напряжения 2, с i-го выхода которого в течение всего времени работы устройства снимается постоянный сигнал напряжения 2i усл(овных).ед(иниц)., поступающий на вход вычитаемого i-го блока вычитания 4i (i=1...N).

Входной сигнал напряжения U усл.ед., поступая на вход устройства U, поступает одновременно на вход уменьшаемого N-го блока вычитания 4N и информационные входы ЭК 3N-1 и 5N. ЭК 3N-1, 3N-2, ..., 30 открываются только при подаче отрицательного напряжения на их управляющие входы, а ЭК 5N, 5N-1, ..., 51 и ПН 6N, 6N-1, ..., 61 при подаче отрицательного напряжения на их управляющие входы запираются. Поэтому в зависимости от знака формируемой на выходе N-го блока вычитания 4N разности сигналов UN = U-2N усл.ед. открываются:

- или ЭК 5N и ПН 6N (при UN 0) и сигнал со входа уменьшаемого блока вычитания 4N проходит через компаратор 7N на выход N-го разряда устройства, формируя на его выходе «1», при этом разностный сигнал UN поступает через ПН 6N на вход уменьшаемого (N-1)-го блока вычитания 4N-1, - или ЭК 3N-1 (при UN

0) и сигнал со входа уменьшаемого блока вычитания 4N проходит через компаратор 7N на выход N-го разряда устройства, формируя на его выходе «1», при этом разностный сигнал UN поступает через ПН 6N на вход уменьшаемого (N-1)-го блока вычитания 4N-1, - или ЭК 3N-1 (при UN 0) – в этом случае на вход уменьшаемого (N-1)-го блока вычитания 4N-1 проходит сигнал U со входа устройства (со входа уменьшаемого блока вычитания 4N) через ЭК 3N-1 (на выходе N-го разряда устройства при этом формируется «0»). В первом случае (UN

0) – в этом случае на вход уменьшаемого (N-1)-го блока вычитания 4N-1 проходит сигнал U со входа устройства (со входа уменьшаемого блока вычитания 4N) через ЭК 3N-1 (на выходе N-го разряда устройства при этом формируется «0»). В первом случае (UN 0) на выходе блока вычитания 4N-1 формируется разность сигналов UN-1 = UN -2N-1 усл.ед., во втором (UN

0) на выходе блока вычитания 4N-1 формируется разность сигналов UN-1 = UN -2N-1 усл.ед., во втором (UN 0) - UN-1 = U -2N-1 усл.ед. Аналогично работе элементов N-го разряда, знак полученной на выходе блока вычитания 4N-1 разности сигналов UN-1 определяет или формирование «0» на выходе (N-1)-го разряда устройства (UN-1

0) - UN-1 = U -2N-1 усл.ед. Аналогично работе элементов N-го разряда, знак полученной на выходе блока вычитания 4N-1 разности сигналов UN-1 определяет или формирование «0» на выходе (N-1)-го разряда устройства (UN-1 0) и обработку входного сигнала напряжения U в (N-2)-м разряде устройства подобно описанному выше, или формирование «1» на выходе (N-1)-го разряда устройства (UN-1

0) и обработку входного сигнала напряжения U в (N-2)-м разряде устройства подобно описанному выше, или формирование «1» на выходе (N-1)-го разряда устройства (UN-1 0) и аналогичную обработку в (N-2)-м разряде устройства уже сигнала разности UN-1. Работа остальных разрядов устройства, кроме нулевого, совпадает с вышеприведенной. В нулевом разряде «1» формируется или сигналом с выхода ПН 61 (когда на входе уменьшаемого блока вычитания 41 сформирован сигнал 3 усл.ед.) или с выхода ЭК 30 (когда на входе уменьшаемого блока вычитания 41 сформирован сигнал 1 усл.ед.), а «0» формируется при нулевых сигналах с выходов ПН 61 и ЭК 30 (когда на вход уменьшаемого блока вычитания 41 поданы сигналы или 2 усл.ед., или 0 усл.ед.). Различия в напряжениях на выходах ЭК 5i, возникающие в результате поступления на них разных по величине сигналов со входов уменьшаемого блоков вычитания 4i, устраняются прохождением сигналов с выходов ЭК 5i через компараторы 7i, работающие в режиме нуль-индикации и обеспечивающие формирование величины сигнала «1» на выходе i-го разряда АЦП, равной 1 усл.ед.

0) и аналогичную обработку в (N-2)-м разряде устройства уже сигнала разности UN-1. Работа остальных разрядов устройства, кроме нулевого, совпадает с вышеприведенной. В нулевом разряде «1» формируется или сигналом с выхода ПН 61 (когда на входе уменьшаемого блока вычитания 41 сформирован сигнал 3 усл.ед.) или с выхода ЭК 30 (когда на входе уменьшаемого блока вычитания 41 сформирован сигнал 1 усл.ед.), а «0» формируется при нулевых сигналах с выходов ПН 61 и ЭК 30 (когда на вход уменьшаемого блока вычитания 41 поданы сигналы или 2 усл.ед., или 0 усл.ед.). Различия в напряжениях на выходах ЭК 5i, возникающие в результате поступления на них разных по величине сигналов со входов уменьшаемого блоков вычитания 4i, устраняются прохождением сигналов с выходов ЭК 5i через компараторы 7i, работающие в режиме нуль-индикации и обеспечивающие формирование величины сигнала «1» на выходе i-го разряда АЦП, равной 1 усл.ед.

Таким образом, при поступлении на вход устройства сигнала напряжения U усл.ед. на выходах всех N разрядов устройства формируется двоичный код, соответствующий значению U, с быстродействием, определяемым только временем срабатывания N блоков вычитания и N ЭК (или N ПН). С учетом современного быстродействия и тех, и других, общее время срабатывания АЦП даже для 32 разрядов не превышает 40-50 нс, что позволяет проводить обработку сигналов в гигагерцовом диапазоне.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оптический аналого-цифровой преобразователь | 2021 |

|

RU2756462C1 |

| ОПТИЧЕСКИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2008 |

|

RU2361251C1 |

| ОПТИЧЕСКИЙ КОМПАРАТОР | 1995 |

|

RU2106064C1 |

| ДВУХПОРОГОВЫЙ КОМПАРАТОР ДИАПАЗОНА ДВОИЧНЫХ БИТ | 2020 |

|

RU2758205C1 |

| ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДИНАМИЧЕСКОГО ТИПА (ВАРИАНТЫ) | 2008 |

|

RU2389133C1 |

| КРУГОВОЙ АРБИТР ДИСПЕТЧЕРА ЗАДАЧ | 2022 |

|

RU2785771C1 |

| Логарифмический преобразователь напряжения в двоичный код | 1989 |

|

SU1709523A1 |

| Способ управления автономной системой электропитания космического аппарата | 2016 |

|

RU2624447C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2007 |

|

RU2359403C1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании быстродействующих устройств обработки информации. Техническим результатом изобретения является повышение быстродействия преобразования в позиционный двоичный код электрических аналоговых сигналов. Такой результат обеспечивается за счет того, что аналого-цифровой преобразователь состоит из N-выходного делителя напряжения и (N+1) разрядных блоков, выходы которых являются выходами АЦП, при этом N-й разрядный блок содержит электронный ключ, блок вычитания, повторитель напряжения и компаратор в режиме нуль-индикации, а в каждый предшествующий ему разрядный блок введен еще один электронный ключ, при этом нулевой разрядный блок состоит из одного электронного ключа. 1 ил.

Аналого-цифровой преобразователь (АЦП), содержащий источник опорного напряжения, группу компараторов, отличающийся тем, что в него введены N-выходной делитель напряжения и (N+1) разрядных блоков, выходы которых являются выходами (N+1) разрядов АЦП, которые являются соответствующими выходами устройства, каждый j-й разрядный блок (j=1, 2, ..., N-1) содержит первый электронный ключ, блок вычитания, второй электронный ключ, повторитель напряжения, компаратор в режиме нуль-индикации, при этом N-й разрядный блок содержит блок вычитания, второй электронный ключ, повторитель напряжения, компаратор в режиме нуль-индикации, а нулевой разрядный блок содержит первый электронный ключ, выход источника опорного напряжения подключен ко входу делителя напряжения, i-й выход которого подключен ко входу вычитаемого блока вычитания i-го разрядного блока (i=1, ..., N), вход устройства подключен ко входу уменьшаемого блока вычитания N-го разрядного блока, а вход уменьшаемого блока вычитания i-го разрядного блока объединен с информационными входами первого и второго электронных ключей, при этом выход второго электронного ключа i-го разрядного блока подключен через компаратор к выходу i-го разрядного блока и является соответствующим выходом устройства для i-го разряда АЦП, а в i-м разрядном блоке выход блока вычитания подключен к управляющим входам первого и второго электронных ключей и входу повторителя напряжения, выход которого объединен с выходом первого электронного ключа (i-1)-го разрядного блока и подключен ко входу уменьшаемого блока вычитания (i-1)-го разрядного блока, кроме выхода повторителя напряжения первого разрядного блока, объединенного с выходом первого электронного ключа нулевого разрядного блока и подключенного к выходу нулевого разряда АЦП.

| Устройство для учета числа перемещаемых поточно пиломатериалов по длине их | 1932 |

|

SU34830A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

| Бетон с искусственно-приготовленным пористым наполнительным материалом | 1929 |

|

SU18330A1 |

| US 8384571 B2, 26.02.2013 | |||

| US 8604962 B1, 10.12.2013. | |||

Авторы

Даты

2024-07-09—Публикация

2023-10-31—Подача