Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных вычислительных системах для аппаратной реализаций операции деления комплексных чисел, представленных в форме с фиксированной запятой.

Известно устройство для деления, содержащее четыре регистра, восемь сумматоров, четыре сдвигатёля, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. Недостатком известного устройства является низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство для параллельного деления чисел, содержащее в случае трех делимых четыре операционных блока, регистр, блок управления, элементы И. Недостатком данного устройства являются ограниченные функциональные возможности, не позволяющие производить обработку комплексных операндов.

Цель изобретения - расширение функциональных возможностей устройства. ,: Поставленная цель достигается тем, что в устройство, для деления комплексных чисел, содержащее четыре операционных блока, блок управления, первый вход которого является входом запуска устройства, второй вход - тактовым входом устройства, третий и четвертый входы соединены с первыми- выходами второго и первого операционных блоков, соответственно, первый выход является выходом признака ДЕЛЕНИЕ НА НОЛЬ устройства, второй выход соединен с четвертыми входами всех четырех оперэци- . онных блоков и одновременно является выходом признака КОНЕЦ ОПЕРАЦИИ устройства, третий выход соединен с пятыми входами всех четырех операционных блоков, четвертый выход - с первыми входами всех четырех операционных блоков, шестой выход - со вторыми входами первого и третьего операционных блоков, а седьмой выход - со вторыми входами второго и четVI

Ю

ел

Јь

ел о

вертого операционных блоков, дополнительно введены три мультиплексора, вентильная схема и четыре сумматора по модулю два, причем первые входы первого, второго, третьего и четвертого сумматоров по модулю два являются, соответственно, входами ввода мнимой и действительной частей, делителя, и мнимой и действительной частей делимого, а их вторые входы соединены с шиной старшего (нулевого) разряда действительной части делителя, выходы первого, второго, третьего и четвертого сумматоров по модулю два соединены с третьими входами одноименных операционных блоков, соответственно, первые выходы третьего и четвертого операционных блоков являются соответствующими выходами вывода мнимой и действительной частей результата, второй выход третьего операционного блока соединен со вторым информационным входом второго мультиплексора и первым информационным входом третьего мультиплексора, выход которого подключен к шестому входу четвертого операционного блока, второй выход которого соединен со вторым информационным входом третьего мультиплексора и первым информационным входом второго мультиплексора, выход которого подключен к шестому входу третьего операционного блока, а управляющий вход соединен с управляющим входом третьего мультиплексора и с управляющим входом первого мультиплексора, выход которого соединен с шестым входом второго операционного блока, первый информационный вход - со вторым выходом первого операционного блока, а второй информационный вход - со вторым выходом второго операционного блока и вторым входом вентильной схемы, выход которой соединен с шестым входом первого информационного блока, а первый вход - с управляющими входами всех трех мультиплексоров и подключен к пятому выходу блока управления.

Сопоставимый анализ заявляемого решения с прототипом показывает, что заявляемое устройство отличается от известного набором блоков и связями между ними, приводящими к получению положительного эффекта, в силу чего предложенное техническое решение соответствует критерию изобретения новизна.

Заявителям и авторам не известно использование указанной выше совокупности отличительных признаков в других объектах аналогичного назначения, которая в сочетании с совокупностью известных признаков обеспечивает возможность получения положительного эффекта, в силу чего предложенное техническое решение соответствует критерию изобретения техническое решение задачи.

Все элементы заявляемого устройства могут быть выполнены на серийно выпускаемых микросхемах, в силу чего предложенное техническое решение соответствует критерию изобретения техническое решение задачи.

Работа устройства основана на использовании итерационного алгоритма деления комплексных чисел, реализующего мультипликативный метод вычислений.

Предлагаемое устройство производит выполнение операции

,5 Zi/Z2.

О)

в которой операнды Zi Xi+Yn nZ2 X2+Y2i, a также результат Z3 X3+Y3i являются комплексными числами, действительная и мнимая части которых представлены (п+1)-разрядными двоичными дополнительными кодами в формате с фиксированной запятой. Нулевой разряд каждого кода определяет значение знака соответствующего операнда, а разряды с первого по п-ый - соответствующие числовые разряды операндов. Число Z2 является нормализованным, что соответствует условию

тах{ |Х2| , |Y2 } € |,1.

Вычисление значения 2з производится в два этапа. На первом 3raneVk G {1, 2, .... q} вычисления выполняются с использованием рекуррентных соотношений

ak ai -i+Sk bk-i 2 ik(2)

bk bk-l-Sk -an -2 jl (3)

Ck Ck-i+Sk -dk-1 -2-ik(4) .

См -2 ik(5)

где q - число итераций первого этапа: 50 Начальные условия определяются соотношениями.

sgn Х2(6)

-sgnX2. ..- (7)

,5 Xi sgn X2(8)

.5 Yi sgn X2(9)

Значение Sk на первом этапе вычислений определяется знаком операнда Ьы

Sk sgnbk-i 1-2 Ьц(0) (10)

Значение jk на первом этапе вычислений определяется номером старшего числового разряда кода Ьы, имеющего единичное (нулевое) значение при положительном (отрицательном) значении величи- ны Ьы, в соответствии с выражением

JK

jmin{ j 6 N|bk-i Q+1) bk-i(0)} ,nPHbk-l(1)bk.i(0)(11) 15

Первый этап вычислений продолжается до тех пор, пока в результате выполнения очередной S-ой итерации будет выполнено условие20

Ibs ,

(12)

где m - мультипликативная разрядность вычислений ().25

Второй этап вычислений реализует Vke €{q+1, q+2, .... t} преобразование информации согласно рекуррентным соотношениям

ak ak-i+Sk ak-1 (13) 30

Ck-Ck-1+Sk Cj-1 2 jk(14)

dk dk-i+Sk dk-t -2 jk(15)

Значение jk на втором этапе вычислений определяется значением, старшего (нулевого) разряда кода операнда аы в соответствии с выражением

(1-ak-i)1-2 -аы(0) (16)

(При вычислениях аы (0) определяет значение целой части операнда аы).

Значение jk на втором этапе вычисле- 45 ний определяется номером разряда дробной части кода аы, имеющего нулевое (единичное) значение при аы меньшем (большем) единицы в соответствии с выражением50

jk

min{jG Nl ak-1 0+1) ak-1 (0)};

1, при аы(1)аы(0)

(17)

Второй этап вычислений продолжается до тех пор, пока в результате выполнения очередной t-ой итерации будет выполнено условие

1-at

(18)

5

10

15

0

5

0

5

0

5 0

5

По окончании вычислений значения операндов Ct и dz используются в качестве действительной Хз и мнимой Уз частей комплексного результата 2з.

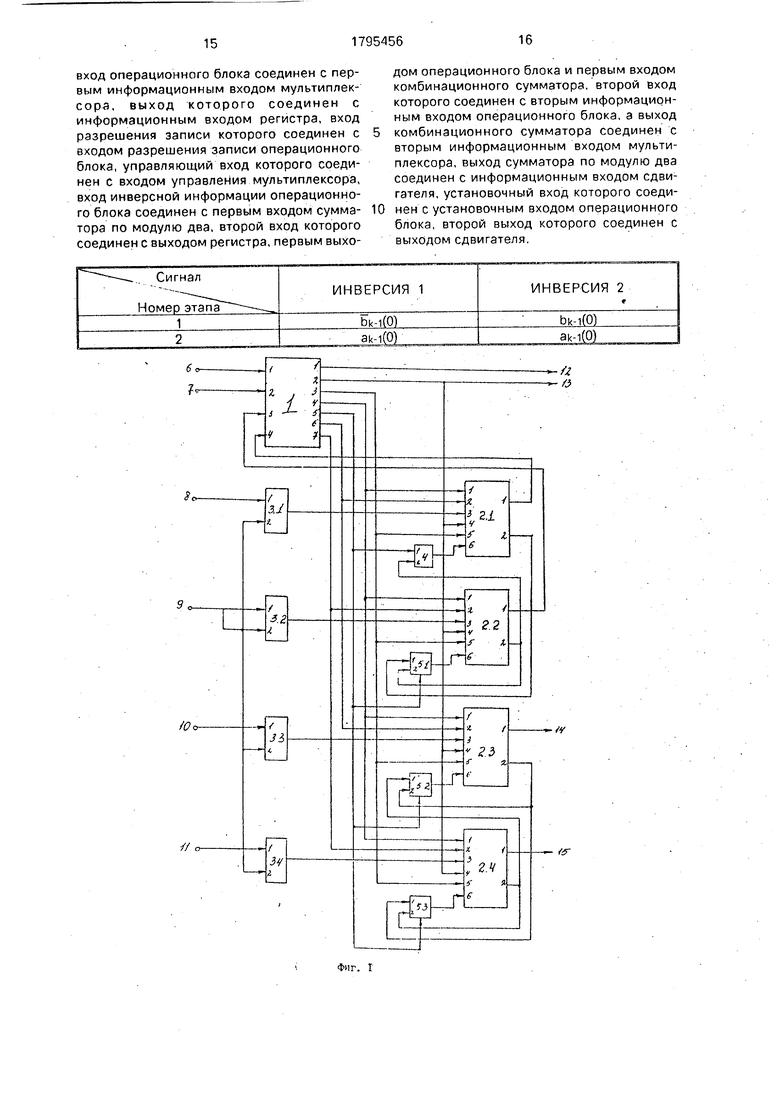

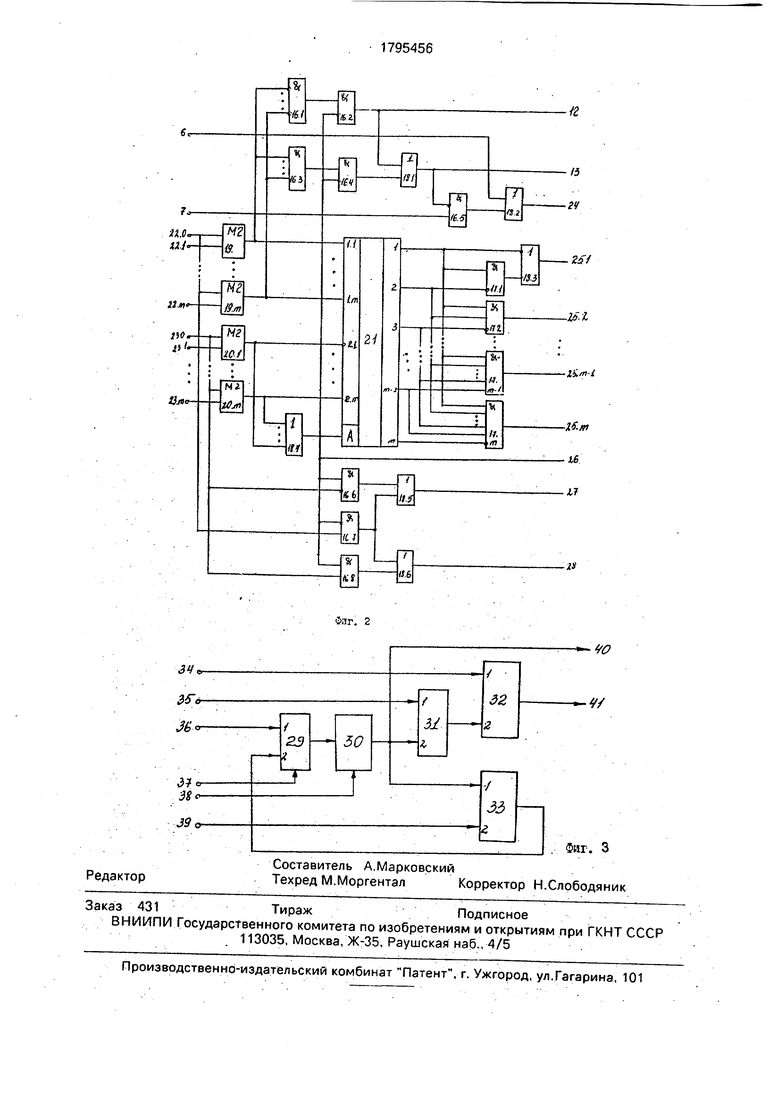

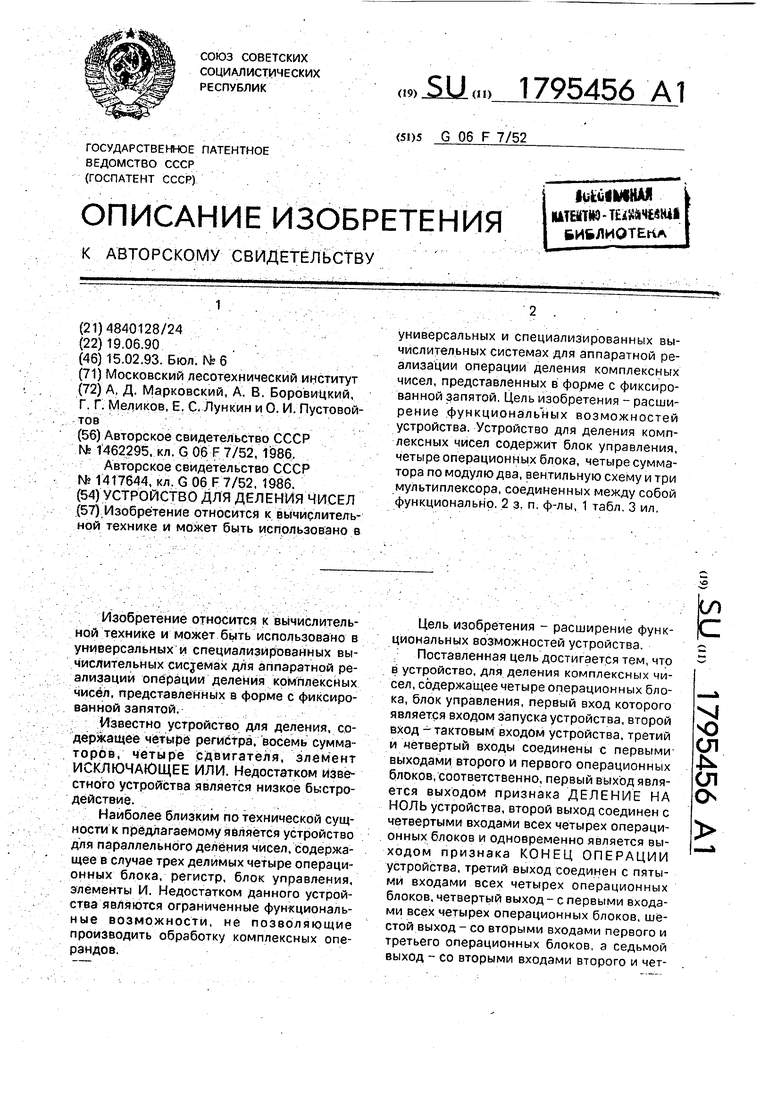

На фиг. 1 представлена структурная схема устройства для деления комплексных чисел; на фиг. 2 - функциональная электрическая схема блока управления; на фиг. 3 - структурная схема операционного блока;

Устройство содержит блок управления 1, четыре операционных блока 2, четыре сумматора по модулю два 3, вентильную схему 4, три мультиплексора 5, имеет шесть входов 6-11 и четыре выхода 12-15.

Блок управления содержит первую группу элементов И 16, включающую восемь элементов, вторую группу элементов И 17, включающую m элементов, шесть элементов ИЛИ 18, первую группу одноразрядных сумматоров по модулю два 19 и вторую группу одноразрядных сумматоров по модулю два 20, содержащие по m одноразрядных сумматоров по модулю два каждая, мультиплексор 21, имеет первый 6, второй 7, третий 22 и четвертый 23 входы, первый 12, второй 13, третий 24, четвертый 25, пятый 26, шестой 27 и седьмой 28 выходы.

Операционный блок содержит мультиплексор 29, регистр 30, сумматор по модулю два 31, сдвигатель 32, сумматор 33, имеет первый 34, второй 35, третий 36, четвертый 37, пятый 38 и шестой 39 входы, первый 40 и второй 41 выходы.

Устройство работает следующим образом.

В исходном состоянии признак КОНЕЦ ОПЕРАЦИИ, поступающий со второго выхода блока управления 1 на второй 13 выход устройства имеет единичное значение. На второй 7 вход устройства непрерывно поступают тактовые импульсы (ТИ). На третий 8, четвертый 9, пятый 10 и шестой 11 входы устройства поступают значения аргументов Y2, Х2, YI и Х{, которые передаются на первые входы первого, второго,третьего и четвертого сумматоров по модулю два 3 соответственно. Коды Yt и Xt поступают на входы соответствующих сумматоров по модулю два 3 со смещением на один разряд в сторону младших разрядов.

На входах сумматоров по модулю два 3 поступающие коды уа, Х2, У1 и хч дополняются нулями до V числовых разрядов (V - вычислительнаяразрядность, обеспечивающая допустимое значение погрешности, возникающей при усечении чисел, сдвигаемых за пределы разрядной сетки, V т).

На вторые входы каждого сумматора по модулю два 3 поступает значение знакового разряда кода Х2, которое поразрядно суммируется по модулю два с кодами, поступившими на второй вход соответствующего сумматора по модулю два. В результате на выходах первого, второго, третьего и четвертого сумматоров по модулю два 3 формируются начальные значения переменных bo, a0,do и Со, которые поступают на третьи входы первого, второго, третьего и четвертого операционных блоков соответственно.

Для начала вычислений синхронно с одним из ТИ на первый 6 вход устройства подается сигнал ПУСК, поступающий на первый вход блока управления 1. Блок управления 1 по сигналу ПУСК формирует на своем третьем выходе сигнал ЗАНЕСЕНИЕ. Единичный уровень признака КОНЕЦ ОПЕРАЦИИ, поступая на четвертые входы операционных блоков 2 со второго выхода блока управления 1, обеспечивает прием операционными блоками 2.1, 2.2, 2.3 и 2.4 начальных значений Ь0, ао, do и со соответственно поступающих на их третьи входы. Сигнал ЗАНЕСЕНИЕ, поступая на пятые входы операционных блоков 2, обеспечивает занесение начальных х значений переменных в регистры блоков 2. С первых выходов блоков 2.1 и 2.2 коды и , содержащие т+1 старших разрядов величин bo и а0, поступают на третий и четвертый входы блока управления 1 соответственно.

Если начальные значения переменных а0 и bo равны нулю, признак КОНЕЦ ОПЕРАЦИИ сохраняет единичное значение и вычисления не проводятся. На первом 12 выходе устройства формируется единичное значение ПР признака ДЕЛЕНИЕ НА НОЛЬ.

При равенстве нулю операнда bo и равенстве единице операнда а0 признак КОНЕЦ ОПЕРАЦИИ сохраняет единичное значение, на выходах 15 и 16 устройства формируются соответственно значения мнимой Уз и действительной Хэ частей результата согласно (1).

При неравенстве нулю операнда а0 и. равенстве нулю операнда Ь0 на пятом выходе блока управления 1 формируется нулевое значение признака НОМЕР ЭТАПА. Признак КОНЕЦ ОПЕРАЦИИ принимает нулевое значение и устройство начинает выполнение вычислений непосредственно со второго этапа.

При отличных от нуля значениях операндов а0 и bo признак НОМЕР ЭТАПА принимает единичное значение, признак

КОНЕЦ ОПЕРАЦИИ принимает нулевое .значение и в устройстве начинается первый этап вычислений. На первом этапе вычислений при выполнении К-ой итерации К G {1,

2, ..;, q} единичный уровень признака НОМЕР ЭТАПА, поступая на первый вход вентильной схемы 4 и управляющие входы мультиплексоров 5, обеспечивает прохождение информации со второго входа на выход вентильной схемы 4, а также с первых информационных входов мультиплексоров 5 на их выходы.

На вторые входы первого и третьего операционного блоков 2 с шестого выхода блока управления 1 и на вторые входы второго и четвертого операционных блоков 2 с седьмого выхода блока управления 1 поступают сигналы ИНВЕРСИЯ 1 и Инверсия 2 соответственно, значения которых определяются таблицей..

На первые входы операционных блоков 2 с четвертого выхода блока управления 1

поступает m-разрядный унитарный двоичный код jk, содержащий единицу в jk-ом разряде, определяемом выражением (11), и нули в остальных разрядах,

В результате операционные блоки 2

производят формирование значений ak, bk, Ck и dk в соответствии с выражениями (2)- (5).

С приходом очередного ТИ на третьем выходе блока управления 1 формируется

единичное значение сигнала ЗАНЕСЕНИЕ, которое, поступая на пятые входы операционных блоков 2, осуществляет занесение вычисленных значений в регистры блоков. Итерационный процесс первого этапа

вычислений продолжается до тех пор, пока в результате выполнения очередной q-ой итерации значения всех m числовых разрядов кода bq, поступающего с первого выхода операционного блока 2.1 на четвертый

вход блока управления 1, станут равными, нулю, либо значения всех m числовых разрядов кода bq станут равными единице. В этом случае признак НОМЕР ЭТАПА на пятом выходе блока управления 1 примет нулевое значение, которое, поступая на управляющие входы мультиплексоров 5, обеспечит прохождение информации со вторых информационных входов мультиплексоров 5 на их выходы. Устройство начнет выполнять второй этап вычислений. На втором этапе вычислений при выполнении К-ой итерации К G {q+1, q-H, ..., t} с четвертого выхода блока управления 1 на первые входы операционных блоков 2 поступает унитарный m-разрядный управляющий код

сдвига Ik, содержащий единицу в jk-м разряде, определяемом выражением 17, и нули в остальных разрядах.

В результате выполнения итерации второй, четвертый и третий операционные блоки 2 формируют согласно выражениям (13)-(15) значения ai, Ck и dk соответственно, которые с приходом очередного ТИ заносятся в регистры операционных блоков. Значение , хранящееся в регистре операционного блока 2.1 на втором этапе вычислений не изменяется.

; Итерационный процесс на втором этапе вычислений продолжается до тех пор, пока в результате выполнения очередной t-рй итерации все m разрядов дробной части кода поступающего с первого выхода операционного блока 2.2 на третий вход блока управления 1 станут равными единице либо все m разрядов дробной части кода станут равными нулю. В этом случае на втором выходе блока управления 1 будет сформировано единичное значение признака КОНЕЦ ОПЕРАЦИИ, которое поступит на второй 13 выход устройства. На третьем 14 и четвертом 15 выходах устройства будут сформированы значения d t и ct, представляющие собой неокругленные значения мнимой Уз и действительной Хз составляющих результата, соответственно.

Блок управления работает следующим образом. В исходном состоянии на входы 22 и 23 блока поступают коды, содержащие только нули или только единицы во всех m числовых разрядах дробной части, на выходе 13 формируется единичный уровень признака КОНЕЦ ОПЕРАЦИИ. Сигнал ПУСК со входа б блока поступает на первый вход элемента ИЛИ 18.2 и затем с выхода элемента ИЛИ 18.2 на выход 24 блока в качестве сигнала ЗАНЕСЕНИЕ. В процессе выполнения операцииУК{0,1,..., t} на входы 22 и 23 блока поступают (т+1)- разрядные коды и . соответственно. Первая группа одноразрядных сумматоров по модулю два 19 инвертирует поступающий на вход 22 код при единичном значении старшего (нулевого) разряда поступающего кода и оставляет поступающий на вход 22 код без изменений при нулевом значении старшего (нулевого) разряда кода, формируя таким образом абсолютное значение величины .

Аналогичные преобразования кода, поступающего на вход 23 выполняет вторая группа одноразрядных сумматоров по модулю два 20, формируя дополнение до двух кода при S1.

Если на выходах первой 19 и второй 20 групп одноразрядных сумматоров по модулю два формируются нулевые коды, на выходе элемента И 16.2 сформируется единичный уровень признака ДЕЛЕНИЕ НА НУЛЬ. Единичное значение признака ДЕЛЕНИЕ НА НУЛЬ, проходя через элемент ИЛИ 18.1 обеспечивает формирование значения признака КОНЕЦ ОПЕРАЦИИ на вы0 ходе 13 блока. Если числовые разряды кода содержит как нули, так и единицы, абсолютное значение кода , поступающее с выходов, второй группы одноразрядных сумматоров по модулю два 20, на вход эле5 мента ИЛИ 18.4, обеспечивает формирование на выходе элемента ИЛИ 18.4, являющемся одновременно выходом 26 блока, единичного значения признака НОМЕР ЭТАПА. Единичное значение признака

0 НОМЕР ЭТАПА, поступая на инверсные входы элементов И 16.2 и И 16.4, обеспечивает формирование нулевого уровня признака КОНЕЦ ОПЕРАЦИИ, на выходе элемента ИЛИ 18.1, который, поступая с выхода эле5 мента ИЛИ 18.1 на инверсный вход элемента И 16.5 разрешает прохождение ТИ со входа 7 блока через элементы И 16.5 и ИЛИ 18.2 на выход 24 блока.

Единичный уровень признака НОМЕР

0 ЭТАПА на выходе элемента ИЛИ 18.4 разрешает прохождение кода с выходов второй группы сумматоров по модулю два 20 через мультиплексор 21 на входы схемы выбора старшего нуля, образованной второй груп5 пой элементов И 17 и элементам ИЛИ 18.3, на выходе которой формируется унитарный код Ik, поступающий на выход 25 блока.

Элементы И 16.6, И 16.7, И 16.8 и элементы ИЛИ 18.5, и ИЛИ 18.6 формируют

0 сигналы ИНВЕРСИЯ 1 и ИНВЕРСИЯ 2 на обоих этапах вычисления в соответствии с приведенной выше таблицей. Сигнал ИНВЕРСИЯ 1 поступает с выхода элемента ИЛИ 18.5 на выход 27 блока. Сигнал ИН5 ВЕРСИЯ 2 поступает с выхода элемента ИЛИ 18.6 на выход 28 блока. При поступлении на вход 23 блока нулевого кода, на выходе элемента ИЛИ 18.4 будет сформировано нулевое значение признака

0 НОМЕР ЭТАПА, определяющее второй этап вычислений. При этом на выход мультиплексора 21 поступит m-разрядный код с выходов первой группы одноразрядных сумматоров по модулю два .19. Формирова5 ние унитарного кода Ik производится в схеме выбора старшего нуля также, как и на первом этапе вычислений.

С появлением на выходах первой группы одноразрядных сумматоров по модулю два 19 кода, все разряды которого одновременно равны единице, на выходе элемента И 16.3 формируется единичное значение сигнала, которое через элементы И 1,6.4 и ИЛИ 18.1 поступает на выход 13 в качестве признака КОНЕЦ ОПЕРАЦИИ. С выхода элемента ИЛИ 18.1 на инверсный вход элемента И 16.5 поступает сигнал единичного уровня, запрещающий прохождение ТИ со входа 7 блока на выход 24 блока. Блок управления прекращает свою работу.Опера- ционный блок работает следующим образом. Признак КОНЕЦ ОПЕРАЦИИ, поступающий с четвертого 37 входа блока на управляющий вход мультиплексора 29, обеспечивает поступление на выход мультиплексора 29 информации с третьего 36 входа блока при занесении начальных .значений и с выхода сумматора 33 при выполнении вычислений. С выхода мультиплексора 29 информация поступает на информационный вход регистра 30, в который заносится при единичном уровне сигнала ЗАНЕСЕНИЕ, поступающего с пятого 38 входа блока на вход занесения регистра 30, С выхода регистра 30 информация поступает на первый 40 выход блока, а также на первый вход сумматора 39 и второй вход сумматора по модулю два 31. Сумматор по модулю два 31 производит поразрядное суммирование по модулю два кода, поступившего на его второй вход со значением сигнала ИНВЕРСИЯ, поступившего на его первый вход со второго 35 входа блока.

Сформированный результат поступает на второй вход сдвигателя 32, на первый вход которого с первого 34 входа блока поступает унитарный m-разрядный код Ik. Сдвигатель 32 производит сдвиг в сторону младших разрядов кода, поступившего на его второй вход на число разрядов, равное номеру единичного разряда в унитарном коде Ik. Полученный в результате сдвига код с выхода сдвигателя 32 поступает на второй 41 выход блока. Сумматор 33 осуществляет суммирование поступившего на его .первый вход кода с кодом, поступившим на его второй вход с шестого 3.9 входа блока.

Таким образом, положительный эффект изобретения заключается в расширении функциональных возможностей устройства. В то же время среднее время выполнения операции деления комплексных чисел составляет п итераций что обеспечивает в среднем двухкратный выигрыш в быстродействии по сравнении с известным устройством, выполняющим аналогичную операцию за 2п+1 итераций. ....:

Формула изобретения

1. Устройство для деления чисел, содержащее первый, второй, третий и четвертый операционные блоки и блок управления, вход запуска которого является входом запуска устройства, первый выход первого операционного блока соединен с первым информационным входом блока управления, первый выход которого является выходом признака деления на ноль устройства,

0 второй выход блока управления является выходом признака конца деления устройства, а четвертый выход блока управления соединен с установочными входами первого, второго, третьего и четвертого операцион5 ных блоков, отличающееся тем, чтр, с целью расширения функциональных воз- можностей за счет деления комплексных чисел, в него введены первый,второй,третий и четвертый сумматоры по модулю два, пер0 вый, второй и третий мультиплексоры и вентильная схема, причем второй выход блока управления соединен с управляющими входами первого, второго, третьего и четвертого операционных блоков, входы

5 разрешения записи которых соединены с третьим выходом блока управления, пятый выход которого соединен с управляющими входами вентильной схемы и первого, второго и третьего мультиплексоров, шестой

0 выход блока управления соединен с входами инверсной информации первого и третьего операционных блоков, седьмой выход блока управления соединен с входами инверсной информации второго и четвертого

5 операционных блоков, первый выход второго операционного блока соединен с вторым информационным входом блока управления, тактовый вход которого является тактовым входом устройства, входы ввода

0 действительной и мнимой частей делителя и . действительной и мнимой частей делимого которого соединены соответственно с первыми входами первого, второго, третьего и четвертого сумматоров по модулю два, вто5 рые входы которых соединены со старшим, разрядом ввода действительной части делителя устройства, выход первого сумматора по модулю два соединен с первым информационным входом первого операционного

0 блока/выход второго сумматора по модулю два соединен с первым информационным входом второго операционного блока, выход третьего сумматора по модулю два соединен с первым информационным входом

5 третьего операционного блока, выход четвертого сумматора по модулю два соединен с первым информационным входом четвертого операционного блока, второй выход первого операционного блока соединен с первым информационным входом первого

мультиплексора, второй информационный вход которого соединен с вторым выходом второго операционного блока и с информационным входом вентильной схемы, первые выходы третьего и четвертого операционных блоков является соответственно выходами действительной и мнимой части результата устройства, второй выход третьего операционного блока соединен с первым информационным входом третьего мультиплексора и с вторым информационным входом второго мультиплексора, первый информационный вход которого соединен с вторым информационным входом третьего мультиплексора и с вторым выходом четвертого операционного блока, выход вентильной схемы соединен с вторым информационным вх.одом первого операционного блока, выход первого мультиплексора соединен с вторым информационным входом второго операционного блока, вы- хбд второго мультиплексора соединён с вторым информационным входом третьего операционного блока, выход третьего мультиплексора соединен с вторым информационным входом четвертого операционного блока.

2. Устройство поп. 1,отличающее- с я тем, что блок управления содержит первую группу из восьми элементов И, вторую группу из m элементов И. группу из шести элементов ИЛИ, первую группу из m сумматоров по модулю два, вторую, группу из m сумматоров по модулю два, где m - мультипликативная разрядность вычислений, и мультиплексор, причем первые входы m сумматоров по модулю два первой группы соединены соответственно с m разрядами первого информационного входа блока управления, (т+1)-й разряд которого соединен с вторыми входами сумматоров по модулю два первой группы, выходы которых соединены соответственно с инверсными входами первого элемента И первой группы, с прямыми входами третьего элемента И первой группы и с входами первой группы мультиплексора, первые входы m сумматоров по модулю два второй группы соединены соответственно с m разрядами второго информационного входа блока управления, (т+1)-й разряд которого соединен с вторыми входами сумматоров по модулю два второй группы, выходы которых соединены соответственно с входами четвертого элемента ИЛИ группы, выход которого соединен с управляющим входом мультиплексора, с первыми (инверсными) входами второго, четвертого и седьмого элементов И первой группы и с первыми (пря- мыми) входами шестого и восьмого

элемента И первой группы, вторые (прямые) входы второго и четвертого элементов И первой группы соединены соответственно с выходами первого и третьего элементов И первой группы, второй (прямой) вход седьмого элемента И первой группы соединен с (т+1)-м разрядом первого информационного входа блока управления, второй (инверсный) вход шестого элемента И первой

0 группы соединен с вторым (прямым) входом восьмого элемента И первой группы и с (т+1)-м разрядом второго информационного входа блока управления, выход второго элемента И первой группы является первым

5 выходом блока управления и соединен с первым (прямым) входом первого элемента ИЛИ группы, второй вход (прямой) которого соединен с выходом четвертого элемента И первой группы, выход первого элемента

0 ИЛИ группы является вторым выходом блока управления и соединен с первым (инверсным) входом пятого элемента И первой группы, второй (прямой) вход которого соединен с тактовым входом блока управления,

5 выход пятого элемента И первой группы соединен с первым входом второго элемента ИЛИ группы, выход которого является третьим выходом блока управления, первый выход мультиплексора соединен с первым

0 (инверсным) входом третьего элемента ИЛИ группы и с первыми (прямыми) входами m элементов И второй группы, выход первого элемента И которой соединен с вторым (прямым) входом третьего элемента ИЛИ

5 группы, 1-й выход мультиплексора, где , т, соединен с вторым (инверсным) входом 1-го элемента И второй группы и j-м входом (прямым) , m-1) (i+1)-ro элемента И второй группы, выходы третьего элемента ИЛИ

0 группы и элементов И второй группы с второго по m-й составляют m разрядов четвертого выхода блока управления, выход четвертого элемента ИЛИ группы является пятым выходом блока управления, выход

5 шестого элемента И первой группы соединен с первым (прямым) входом пятого элемента ИЛИ группы, второй (прямой) вход которого соединен с выходом седьмого элемента И первой группы и с первым (прямым)

0 входом шестого элемента ИЛИ группы, второй (прямой) вход которого соединен с выходом восьмого элемента И первой группы, выходы пятого и шестого элементов ИЛИ группы являются соответственно шестым и

5 седьмым выходами блока управления.

3. Устройство поп, 1,отличающее- с я тем, что операционный блок содержит мультиплексор, регистр, сумматор по модулю два, сдвигатель и комбинационный сумматор, причем первый информационных

вход операционного блока соединен с первым информационным входом мультиплексора, выход которого соединен с информационным входом регистра, вход разрешения записи которого соединен с входом разрешения записи операционного блока, управляющий вход которого соединен с входом управления мультиплексора, вход инверсной информации операционного блока соединен с первым входом сумматора по модулю два, второй вход которого соединен с выходом регистра, первым выхо0

дом операционного блока и первым входом комбинационного сумматора, второй вход которого соединен с вторым информационным входом операционного блока, а выход комбинационного сумматора соединен с вторым информационным входом мультиплексора, выход сумматора по модулю два соединен с информационным входом сдви- гателя, установочный вход которого соединен с установочным входом операционного блока, второй выход которого соединен с выходом сдвигателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1718215A1 |

| Устройство для вычисления квадратного корня из суммы квадратов | 1990 |

|

SU1751751A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1728861A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАТУРАЛЬНОГО ЛОГАРИФМА КОМПЛЕКСНОГО ЧИСЛА | 1991 |

|

RU2010312C1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОГО ДЕЛЕНИЯ ЧИСЕЛ | 1991 |

|

RU2010311C1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Секционный микропроцессор | 1982 |

|

SU1062711A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Процессорный модуль | 1985 |

|

SU1343421A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

Изобретение относится к вычислитеяь- ной технике и может быть использовано в 2 универсальных и специализированных вычислительных системах для аппаратной реализации операции деления комплексных чисел, представленных в форме с фиксированной запятой. Цель изобретения - расширение функциональных возможностей устройства. Устройство для деления комплексных чисел содержит блок управления, четыре операционных блока, четыре сумматора по модулю два, вентильную схему и три мультиплексора, соединенных между собой функционально. 2 з, п. ф-лы, 1 табл. 3 ил.

| Устройство для деления | 1986 |

|

SU1462295A1 |

| кл | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Авторское свидетельство СССР № 1417644, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-02-15—Публикация

1990-06-19—Подача