Перекрестная ссылка на связанные заявки

Настоящее изобретение испрашивает приоритет по китайской патентной заявке №202210028112.2, озаглавленной «КОНСТРУКЦИЯ С СИГНАЛЬНЫМИ ЛИНИЯМИ, СПОСОБ ВОЗБУЖДЕНИЯ СИГНАЛЬНОЙ ЛИНИИ И СХЕМА СИГНАЛЬНОЙ ЛИНИИ», поданной 11 января 2022 г., которая полностью включена в настоящий документ посредством ссылки.

Область техники

Настоящее изобретение относится к технической области производства интегральных схем и, в частности, к конструкции с сигнальными линиями, способу возбуждения сигнальной линии и схеме сигнальной линии.

Уровень техники

Поскольку в общем тракте передачи данных направление передачи данных является случайным, между разными параллельными смежными сигнальными линиями возникают перекрестные помехи, которые влияют на синхронизацию данных. В некоторых случаях для обеспечения изоляции вводят заземленный провод, чтобы обеспечить постоянство синхронизации во время передачи данных. Кроме того, для уменьшения влияния перекрестных помех между сигнальными линиями требуется средство хранения информации о состоянии. Как для изолирующего провода, так и для средства хранения информации о состоянии потребуются дополнительные линии и площадь разводки, что приведет к увеличению площади разводки для сигнальных линий.

Следует отметить, что информация, раскрытая выше, предназначена только для облегчения понимания предпосылок настоящего изобретения и, следовательно, может включать информацию, которая не составляет предшествующий уровень техники, известный специалистам в данной области техники.

Раскрытие сущности изобретения

Задача настоящего изобретения состоит в представлении конструкции с сигнальными линиями, способа возбуждения сигнальной линии и схемы сигнальной линии для улучшения качества сигнала в сигнальных линиях, по меньшей мере до определенной степени, и экономии площади разводки параллельных сигнальных линий.

Согласно первому аспекту настоящего изобретения предложена конструкция с сигнальными линиями, включающая в себя множество параллельных сигнальных линий, причем каждая из сигнальных линий поддерживается в состоянии возбуждения в любой момент времени.

Согласно второму аспекту настоящего изобретения предложен способ возбуждения сигнальной линии, применяемый к конструкции с сигнальными линиями, описанной выше и включающий в себя: управление множеством параллельных сигнальных линий, которые необходимо поддерживать в состоянии возбуждения в любой момент времени.

Согласно третьему аспекту настоящего изобретения предложена схема сигнальной линии, включающая в себя: первый драйвер, снабженный входным выводом для приема первого входного сигнала, разрешающим выводом, соединенным с первым узлом, и выходным выводом, соединенным с сигнальной линией; второй драйвер, снабженный входным выводом для приема второго входного сигнала, разрешающим выводом, соединенным со вторым узлом, и выходным выводом, соединенным с сигнальной линией; и инвертор, снабженный входным выводом, соединенным с первым узлом, и выходным выводом, соединенным со вторым узлом, причем первый узел выполнен с возможностью приема разрешающего сигнала драйвера, который имеет первый уровень, сконфигурированный для управления первым драйвером, который необходимо поддерживать в состоянии возбуждения, и вторым драйвером, который необходимо поддерживать в высокоимпедансном состоянии, и второй уровень, сконфигурированный для управления вторым драйвером, который необходимо поддерживать в состоянии возбуждения, и первым драйвером, который необходимо поддерживать в высокоимпедансном состоянии.

Согласно вариантам осуществления настоящего изобретения путем конфигурирования сигнальных линий, которые необходимо поддерживать в состоянии возбуждения, когда множество сигнальных линий расположены параллельно, можно предотвратить перекрестные помехи между сигнальными линиями, вызывающие ошибки в передаваемых данных, при этом отсутствует необходимость в изолирующем проводе и средстве хранения информации о состоянии, что позволяет значительно сэкономить площадь разводки сигнальных линий.

Следует понимать, что приведенное выше общее описание и нижеследующее подробное описание являются лишь иллюстративными и пояснительными, и их не следует рассматривать как ограничение настоящего изобретения.

Краткое описание чертежей

Прилагаемые чертежи, включенные в описание и составляющие часть описания, иллюстрируют варианты осуществления настоящего изобретения и служат вместе с описанием для пояснения принципов настоящего изобретения. Очевидно, что на чертежах в нижеследующем описании показаны лишь некоторые варианты осуществления настоящего изобретения, и специалисты в данной области техники на основании этих чертежей могут получить другие чертежи, не затрачивая творческих усилий.

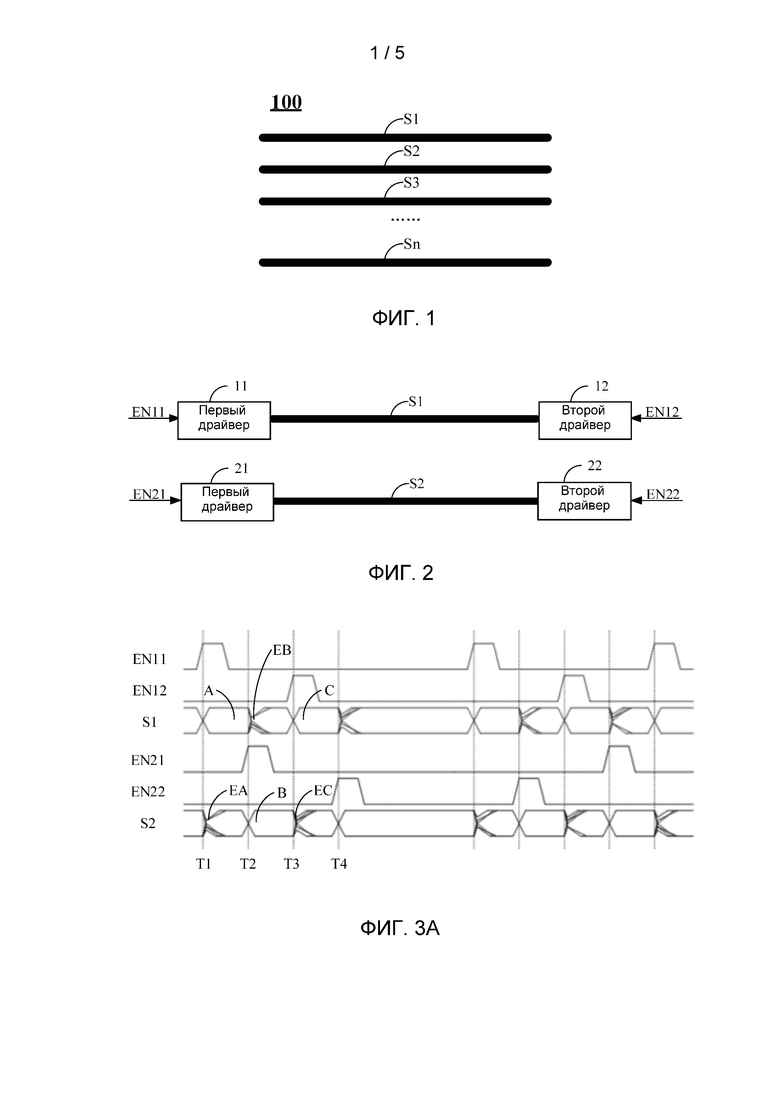

На фиг. 1 представлена принципиальная схема конструкции с сигнальными линиями согласно одному приведенному для примера варианту осуществления настоящего изобретения.

На фиг. 2 представлена принципиальная схема режима возбуждения сигнальных линий согласно одному варианту осуществления настоящего изобретения.

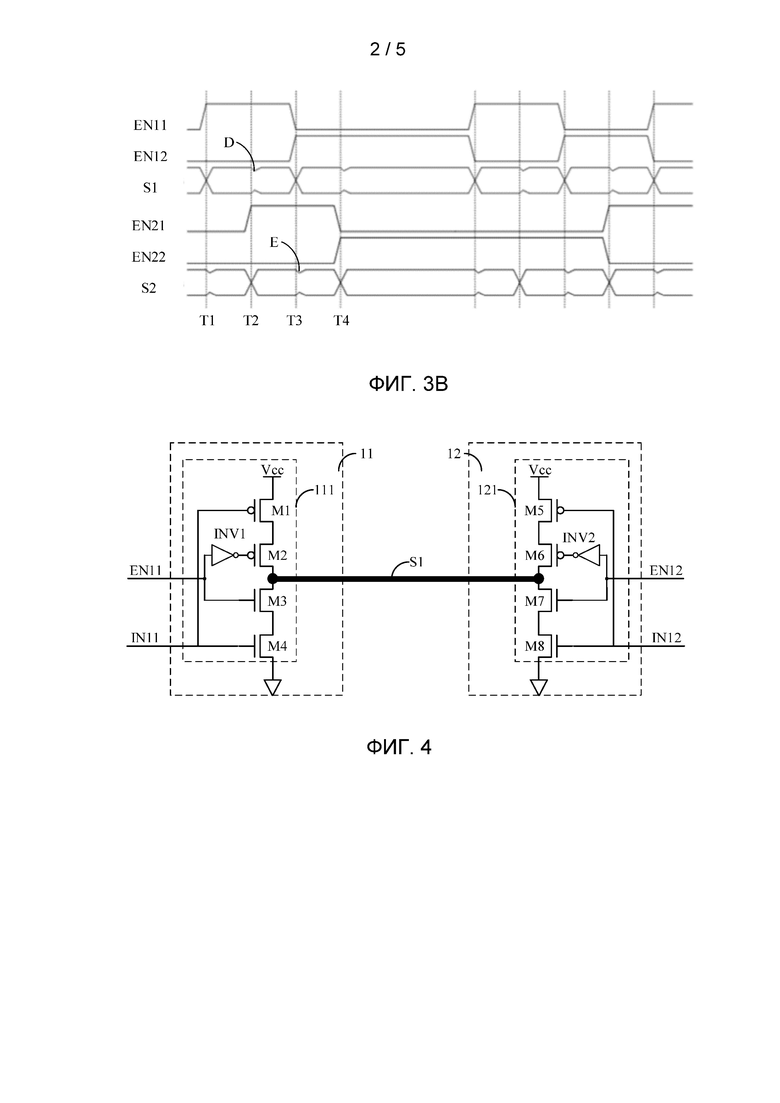

На фиг. 3A представлена принципиальная схема перекрестных помех между двумя смежными сигнальными линиями согласно предшествующему уровню техники.

На фиг. 3B представлена принципиальная схема перекрестных помех между двумя смежными сигнальными линиями согласно одному варианту осуществления настоящего изобретения.

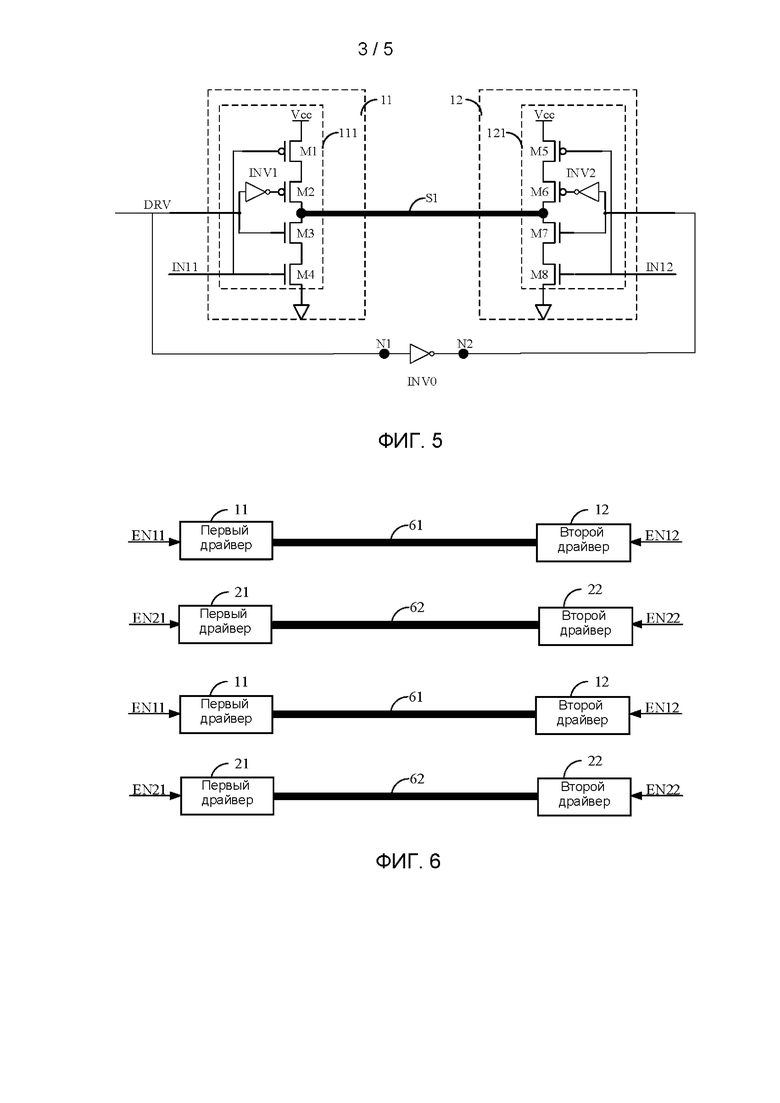

На фиг. 4 представлены принципиальные схемы первого драйвера и второго драйвера сигнальной линии согласно одному варианту осуществления настоящего изобретения.

На фиг. 5 представлена принципиальная схема взаимосвязи между первым разрешающим сигналом и вторым разрешающим сигналом, показанными на фиг. 4, согласно одному варианту осуществления настоящего изобретения.

На фиг. 6 представлена принципиальная схема установки сигнальных линий согласно одному варианту осуществления настоящего изобретения.

На фиг. 7 представлена схема синхронизации сигнала, соответствующая режиму установки сигнальных линий, показанному на фиг. 6.

На фиг. 8 представлена принципиальная схема способа возбуждения сигнальной линии согласно одному варианту осуществления настоящего изобретения.

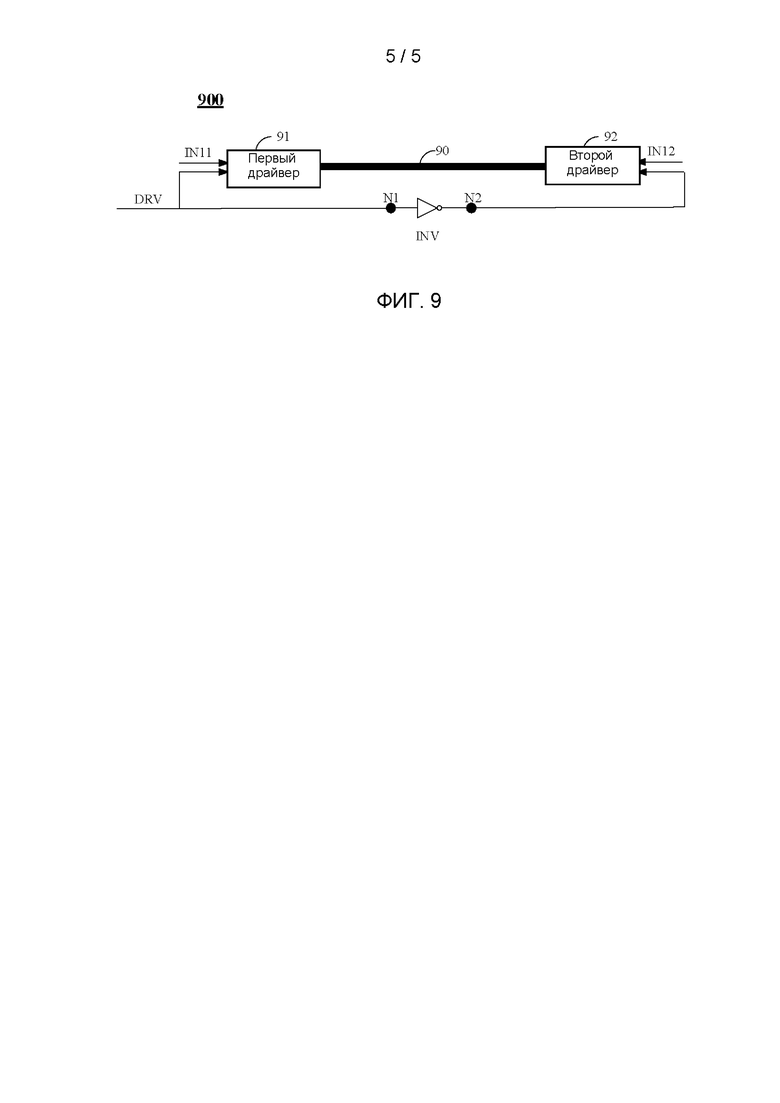

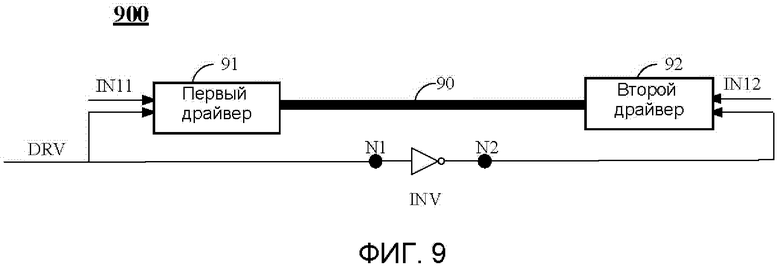

На фиг. 9 представлена принципиальная схема сигнальной линии согласно одному приведенному для примера варианту осуществления настоящего изобретения.

Осуществление изобретения

Ниже более подробно описаны приведенные для примера варианты реализации со ссылкой на прилагаемые чертежи. Однако приведенные для примера варианты реализации могут быть осуществлены в различных формах и их не следует рассматривать как ограничивающиеся описанными в настоящем документе примерами. Напротив, эти варианты реализации представлены таким образом, чтобы настоящее раскрытие было более широким и полным, и полностью передавало концепцию приведенных для примера вариантов реализации для специалистов в данной области техники. Описанные признаки, структуры или характеристики могут быть включены в один или более вариантов реализации любым подходящим образом. В нижеследующем описании представлено множество конкретных подробностей для обеспечения полного понимания вариантов реализации настоящего изобретения. Однако для специалистов в данной области техники очевидно, что технические решения настоящего изобретения могут быть осуществлены на практике без одной или более конкретных деталей или могут быть использованы другие способы, компоненты, аппараты, этапы и т.п. В других случаях общеизвестные технические решения не проиллюстрированы и не описаны подробно, чтобы избежать затруднения понимания различных аспектов настоящего изобретения.

Кроме того, прилагаемые чертежи представляют собой просто принципиальные схемы настоящего изобретения и одинаковые номера позиций на прилагаемых чертежах обозначают идентичные или подобные части. Поэтому их повторное описание будет опущено. Некоторые блок-схемы, показанные на прилагаемых чертежах, являются функциональными объектами и не обязательно соответствуют физически или логически независимым объектам. Эти функциональные объекты могут быть реализованы в виде программного обеспечения или могут быть реализованы в одном или более аппаратных модулях или интегральных схемах, либо могут быть реализованы в различных сетях и/или процессорных аппаратах и/или микроконтроллерных аппаратах.

Далее подробно описаны приведенные для примера варианты реализации настоящего изобретения со ссылкой на прилагаемые чертежи.

На фиг. 1 представлена принципиальная схема конструкции с сигнальными линиями согласно одному приведенному для примера варианту осуществления настоящего изобретения.

Со ссылкой на фиг. 1, конструкция 100 с сигнальными линиями может включать в себя:

множество параллельных сигнальных линий S1-Sn, причем каждая из сигнальных линий поддерживается в состоянии возбуждения в любой момент времени.

По сравнению с предшествующим уровнем техники нет необходимости в обеспечении изолирующей линии между каждыми двумя из множества параллельных сигнальных линий S1-Sn и нет необходимости в обеспечении средства хранения информации о состоянии после передачи сигнала, что позволяет эффективно сэкономить площадь проводной разводки. Поскольку каждую из сигнальных линий поддерживают в состоянии возбуждения в любой момент времени, перекрестные помехи между параллельными сигнальными линиями не будут приводить к сигнальному переходу в сигнальных линиях, что позволяет эффективно повысить стабильность сигнала, а также избежать усиления перекрестных помех, сигнального перехода в сигнальных линиях и возникновения ошибок передачи, вызванных проводной разводкой высокой плотности. Следовательно, варианты осуществления настоящего изобретения позволяют повысить стабильность сигнала при уменьшении площади проводной разводки высокой плотности.

Могут быть применены различные способы управления каждой из сигнальных линий, которые необходимо поддерживать в состоянии возбуждения в любой момент времени, и некоторые варианты осуществления будут описаны ниже со ссылкой на прилагаемые чертежи.

На фиг. 2 представлена принципиальная схема режима возбуждения сигнальных линий согласно одному варианту осуществления настоящего изобретения.

Со ссылкой на фиг. 2, в одном приведенном для примера варианте осуществления настоящего изобретения два конца сигнальной линии S1, соответственно, соединены с первым драйвером 11 и вторым драйвером 12, при этом один и тот же момент времени только один из первого драйвера 11 и второго драйвера 12 сигнальной линии S1 поддерживается в состоянии возбуждения. Сигнальная линия S2 параллельна и смежна сигнальной линии S1, причем два конца сигнальной линии S2, соответственно, соединены с первым драйвером 21 и вторым драйвером 22, при этом в один и тот же момент времени только один из первого драйвера 21 и второго драйвера 22 сигнальной линии S2 поддерживается в состоянии возбуждения.

Также со ссылкой на фиг. 2, в одном варианте осуществления первый драйвер 11 сигнальной линии S1 поддерживается в состоянии возбуждения, когда первый разрешающий сигнал EN11 находится на первом уровне, и поддерживается в высокоимпедансном состоянии, когда первый разрешающий сигнал EN11 находится на втором уровне; а второй драйвер 12 поддерживается в состоянии возбуждения, когда второй разрешающий сигнал EN12 находится на первом уровне, и поддерживается в высокоимпедансном состоянии, когда второй разрешающий сигнал EN12 находится на втором уровне. Когда первым разрешающим сигналом EN11 и вторым разрешающим сигналом EN12 управляют с помощью двух уровней, первый уровень является, например, высоким уровнем, а второй уровень является, например, низким уровнем. Или первый уровень является, например, низким уровнем, а второй уровень является, например, высоким уровнем. Высокий уровень представляет собой, например, состояние равенства напряжению питания или больше его, а низкий уровень представляет собой, например, состояние равенства напряжению земли или меньше его. В данном случае высокий уровень и низкий уровень являются относительными, и конкретный используемый диапазон напряжения должен быть определен в соответствии с конкретным устройством. Например, для полевого транзистора N-типа высокий уровень относится к диапазону напряжения затвора, в котором полевой транзистор N-типа может быть включен, а низкий уровень относится к диапазону напряжения затвора, в котором полевой транзистор N-типа может быть выключен; и для полевого транзистора P-типа низкий уровень относится к диапазону напряжения затвора, в котором полевой транзистор P-типа может быть включен, а высокий уровень относится к диапазону напряжения затвора, в котором полевой транзистор P-типа может быть выключен.

Соответственно, первый драйвер 21 сигнальной линии S2 поддерживается в состоянии возбуждения, когда первый разрешающий сигнал EN21 находится на первом уровне, и поддерживается в высокоимпедансном состоянии, когда первый разрешающий сигнал EN21 находится на втором уровне; а второй драйвер 22 поддерживается в состоянии возбуждения, когда второй разрешающий сигнал EN22 находится на первом уровне, и поддерживается в высокоимпедансном состоянии, когда второй разрешающий сигнал EN22 находится на втором уровне.

На фиг. 3A представлена принципиальная схема перекрестных помех между двумя смежными сигнальными линиями согласно предшествующему уровню техники.

На фиг. 3B представлена принципиальная схема перекрестных помех между двумя смежными сигнальными линиями согласно одному варианту осуществления настоящего изобретения.

На фиг. 3A и фиг. 3B сигнальная линия S1 и сигнальная линия S2 показаны как две параллельные смежные сигнальные линии. Для сигнальной линии S1 первым разрешающим сигналом является EN11, а вторым разрешающим сигналом является EN12; и, для сигнальной линии S2, первым разрешающим сигналом является EN21, а вторым разрешающим сигналом является EN22.

Со ссылкой на фиг. 3A, в предшествующем уровне техники в первый момент времени T1 импульс высокого уровня появляется в первом разрешающем сигнале EN11, соответствующем сигнальной линии S1, и сигнальная линия S1 возбуждается первым драйвером 11 с генерацией сигнала A. В тот же момент времени первый драйвер 21 и второй драйвер 22, расположенные на двух концах сигнальной линии S2, смежной и параллельной сигнальной линии S1, находятся в высокоимпедансном состоянии и не могут возбуждать сигнальную линию S2. Под воздействием сигнала A в сигнальной линии S2 возникает ошибка EA перекрестных помех. Во второй момент времени T2 импульс высокого уровня появляется в первом разрешающем сигнале EN21, соответствующем сигнальной линии S2, и сигнальная линия S2 возбуждается первым драйвером 21 с генерацией сигнала A. В тот же момент времени первый драйвер 11 и второй драйвер 12, расположенные на двух концах сигнальной линии S1, смежной и параллельной сигнальной линии S2, находятся в высокоимпедансном состоянии и не могут возбуждать сигнальную линию S1. Под воздействием сигнала B в сигнальной линии S1 возникает ошибка EB перекрестных помех.

Аналогичным образом, в третий момент времени T3, когда импульс высокого уровня появляется во втором разрешающий сигнале EN12, соответствующем сигнальной линии S1, сигнальная линия S1 возбуждается вторым драйвером 12 с генерацией сигнального перехода (сигнала C), который влияет на состояние сигнала B в сигнальной линии S2, и в сигнальной линии S2 возникает ошибка перекрестных помех EC. В четвертый момент времени T4, когда импульс высокого уровня появляется во втором разрешающий сигнале EN22, соответствующем сигнальной линии S2, сигнальная линия S2 возбуждается вторым драйвером 22 с генерацией сигнального перехода, который влияет на состояние сигнала C в сигнальной линии S1, и также возникает ошибка перекрестных помех.

Следовательно, в предшествующем уровне техники перекрестные помехи, вероятно, возникают между двумя параллельными смежными сигнальными линиями, что приводит к ошибкам при передаче данных.

Со ссылкой на фиг. 3B, в одном варианте осуществления настоящего изобретения в один и тот же момент времени только один из первого разрешающего сигнала EN11 и второго разрешающего сигнала EN12 сигнальной линии S1 находится на высоком уровне, и в один и тот же момент времени только один из первого разрешающего сигнала EN21 и второго разрешающего сигнала EN22 сигнальной линии S2 находятся на высоком уровне.

Во второй момент времени T2 уровень первого разрешающего сигнала EN21 сигнальной линии S2 изменяется на высокий уровень, первый драйвер 21 сигнальной линии S2 переходит в состояние возбуждения и по сигнальной линии S2 происходит передача данных. Поскольку первый разрешающий сигнал EN11 сигнальной линии S1 также находится на высоком уровне и первый драйвер 11 сигнальной линии S1 также находится в состоянии возбуждения, сигнал данных в сигнальной линии S1 менее подвержен влиянию перекрестных помех (точка D). В третий момент времени T3 уровень второго разрешающего сигнала EN12 сигнальной линии S1 изменяется на высокий уровень, второй драйвер 12 сигнальной линии S1 переходит в состояние возбуждения и по сигнальной линии S1 происходит передача данных. Поскольку первый разрешающий сигнал EN21 сигнальной линии S2 также находится на высоком уровне и первый драйвер 21 сигнальной линии S2 также находится в состоянии возбуждения, сигнал данных в сигнальной линии S2 менее подвержен влиянию перекрестных помех (точка E). Аналогичным образом можно сделать вывод о том, что в первый момент времени T1 и в четвертый момент времени T4 сигналы данных в сигнальной линии S1 и сигнальной линии S2 также менее подвержены влиянию перекрестных помех.

Следовательно, поддерживая только один из драйверов на двух концах сигнальной линии в состоянии возбуждения в любой момент времени, можно уменьшить влияние передачи данных на сигнал в сигнальной линии и перекрестных помех в сигнальной линии, параллельной и смежной указанной сигнальной линии, и можно поддерживать стабильность сигнала. Другими словами, используя способ, предложенный в варианте осуществления настоящего изобретения, для управления драйвером сигнальной линии, можно поддерживать стабильность сигнала без обеспечения изолирующей линии и средства хранения информации о состоянии между сигнальными линиями, и значительно сэкономить площадь проводной разводки.

На фиг. 4 представлены принципиальные схемы первого драйвера и второго драйвера сигнальной линии согласно одному варианту осуществления настоящего изобретения.

Со ссылкой на фиг. 4, в одном варианте осуществления настоящего изобретения первый драйвер 11 и второй драйвер 12 сигнальной линии S1 включают в себя по меньшей мере один стробирующий инвертор.

В варианте осуществления, показанном на фиг. 4, первый стробирующий инвертор 111 в первом драйвере 11 снабжен входным выводом, электрически соединенным с первым входным сигналом IN11, разрешающим выводом, соединенным с первым разрешающим сигналом EN11, и выходным выводом, электрически соединенным с сигнальной линией S1. Второй стробирующий инвертор 121 во втором драйвере 12 снабжен входным выводом, электрически соединенным со вторым входным сигналом IN12, разрешающим выводом, соединенным со вторым разрешающим сигналом EN12, и выходным выводом, электрически соединенным с сигнальной линией S1.

Первый стробирующий инвертор 111 включает в себя первый транзистор M1, второй транзистор M2, третий транзистор M3 и четвертый транзистор M4, соединенные последовательно. Первый транзистор M1 и второй транзистор M2 являются транзисторами P-типа, и исток первого транзистора M1 подключен к напряжению Vcc питания. Третий транзистор M3 и четвертый транзистор M4 являются транзисторами N-типа, и исток четвертого транзистора M4 заземлен. Затвор первого транзистора M1 и затвор четвертого транзистора M4 соединены, образуя входной вывод первого стробирующего инвертора 111, и электрически соединены с первым входным сигналом IN11. Затвор второго транзистора M2 соединен с выходным выводом инвертора INV1, входной вывод инвертора INV1 соединен с затвором третьего транзистора M3, а затвор третьего транзистора M3 используется в качестве разрешающего вывода первого стробирующего инвертора 111 и соединен с первым разрешающим сигналом EN11.

Второй стробирующий инвертор 121 включает в себя пятый транзистор M5, шестой транзистор M6, седьмой транзистор M7 и восьмой транзистор M8, соединенные последовательно. Пятый транзистор M5 и шестой транзистор M6 являются транзисторами P-типа, и исток пятого транзистора M5 подключен к напряжению Vcc питания. Седьмой транзистор M7 и восьмой транзистор M8 являются транзисторами N-типа, и исток восьмого транзистора M8 заземлен. Затвор пятого транзистора M5 и затвор восьмого транзистора M8 соединены, образуя входной вывод второго стробирующего инвертора 121, и электрически соединены с первым входным сигналом IN11. Затвор шестого транзистора M6 соединен с выходным выводом инвертора INV2, входной вывод инвертора INV2 соединен с затвором седьмого транзистора M7, а затвор седьмого транзистора M7 используется в качестве разрешающего вывода первого стробирующего инвертора 121 и соединен со вторым разрешающим сигналом EN12.

Когда первый разрешающий сигнал EN11 находится на высоком уровне, второй транзистор M2 и третий транзистор M3 в первом стробирующем инверторе 111 включены, первый стробирующий инвертор 111 находится в состоянии возбуждения и сигнал в сигнальной линии S1 изменяется в соответствии с первым входным сигналом IN11. Когда первый разрешающий сигнал EN11 находится на низком уровне, второй транзистор M2 и третий транзистор M3 в первом стробирующем инверторе 111 выключены, первый стробирующий инвертор 111 находится в высокоимпедансном состоянии и сигнал в сигнальной линии S1 не изменяется в соответствии с первым входным сигналом IN11.

Аналогичным образом, когда второй разрешающий сигнал EN12 находится на высоком уровне, шестой транзистор M6 и седьмой транзистор M7 во втором стробирующем инверторе 121 включены, второй стробирующий инвертор 121 находится в состоянии возбуждения и сигнал в сигнальной линии S1 изменяется в соответствии со вторым входным сигналом IN12. Аналогичным образом, когда второй разрешающий сигнал EN12 находится на низком уровне, шестой транзистор M6 и седьмой транзистор M7 во втором стробирующем инверторе 121 выключены, второй стробирующий инвертор 121 находится в высокоимпедансном состоянии и сигнал в сигнальной линии S1 не изменяется в соответствии со вторым входным сигналом IN12.

Когда только один из первого драйвера 11 и второго драйвера 12 выполнен с возможностью его поддержания в состоянии возбуждения в один и тот же момент времени, только один из первого разрешающего сигнала EN11 и второго разрешающего сигнала EN12 может быть установлен на высокий уровень, как показано на фиг. 3B. В одном приведенном для примера варианте осуществления настоящего изобретения второй разрешающий сигнал EN12 может быть получен путем инвертирования первого разрешающего сигнала EN11 с помощью инвертора.

Как первый драйвер 11, так и второй драйвер 12 могут включать в себя один или более стробирующих инверторов, и фиг. 4 является лишь примером, которым конкретно не ограничивается настоящее изобретение.

На фиг. 5 представлена принципиальная схема взаимосвязи между первым разрешающим сигналом и вторым разрешающим сигналом, показанными на фиг. 4, согласно одному варианту осуществления настоящего изобретения.

Со ссылкой на фиг. 5, в одном приведенном для примера варианте осуществления настоящего изобретения первый драйвер 11 снабжен входным выводом для приема первого входного сигнала IN11, разрешающим выводом, соединенным с первым узлом N1, и выходным выводом, соединенным с сигнальной линией S1. Второй драйвер 12 снабжен входным выводом для приема второго входного сигнала IN12, разрешающим выводом, соединенным со вторым узлом N2, и выходным выводом, соединенным с сигнальной линией S1. Первый узел N1 выполнен с возможностью приема разрешающего сигнала DRV драйвера. Второй узел N2 и первый узел N1 соединены посредством нечетного количества инверторов INV0 (на фиг. 5 показан только один из них).

В варианте осуществления, показанном на фиг. 5, разрешающий сигнал DRV драйвера выполнен с возможностью управления в один и тот же момент времени, независимо от того, находится ли он в состоянии высокого уровня или в состоянии низкого уровня, только одним из первого драйвера 11 и второго драйвера 12, который необходимо поддерживать в состоянии возбуждения.

На фиг. 6 представлена принципиальная схема установки сигнальных линий согласно одному варианту осуществления настоящего изобретения.

Со ссылкой на фиг. 6, в одном приведенном для примера варианте осуществления настоящего изобретения множество параллельных сигнальных линий включают в себя линии 61 нечетных данных и линии 62 четных данных, расположенные попеременно. Линии 61 нечетных данных выполнены с возможностью передачи нечетных сигналов, полученных путем дискретизации нечетных синхронизирующих тактовых импульсов, линии 62 четных данных выполнены с возможностью передачи четных сигналов, полученных путем дискретизации четных синхронизирующих тактовых импульсов, и разность фаз между нечетными синхронизирующими тактовыми импульсами и четными синхронизирующими тактовыми импульсами составляет 180 градусов. Первый разрешающий сигнал EN11, соответствующий линиям 61 нечетных данных, и первый разрешающий сигнал EN21, соответствующий линиям 62 четных данных, имеют разные фазы, и второй разрешающий сигнал EN12, соответствующий линиям 61 нечетных данных, и второй разрешающий сигнал EN22, соответствующий линиям 62 четных данных, имеют разные фазы.

На фиг. 7 представлена схема синхронизации сигнала, соответствующая режиму установки сигнальных линий, показанному на фиг. 6.

Со ссылкой на фиг. 7, в одном приведенном для примера варианте осуществления настоящего изобретения цикл передачи нечетных данных и цикл передачи четных данных равны T, а интервал передачи между нечетными данными и четными данными равен T/2, т.е. между нечетными данными и четными данными существует разность фаз 180 градусов.

В первый момент T1, когда первый разрешающий сигнал EN11, соответствующий линии 61 нечетных данных, имеет нарастающий фронт, второй разрешающий сигнал EN12, соответствующий линии 61 нечетных данных, имеет спадающий фронт, первый драйвер 11, соответствующий линии 61 нечетных данных, переходит в состояние возбуждения, второй драйвер 12 переходит в высокоимпедансное состояние, а сигнал в линии 61 нечетных данных управляется входным сигналом первого драйвера 11. В третий момент T3, когда второй разрешающий сигнал EN12, соответствующий линии 61 нечетных данных, имеет нарастающий фронт, первый разрешающий сигнал EN11, соответствующий линии 61 нечетных данных, имеет спадающий фронт, второй драйвер 12, соответствующий линии 61 нечетных данных, переходит в состояние возбуждения, первый драйвер 11 переходит в высокоимпедансное состояние, а сигнал в линии 61 нечетных данных управляется входным сигналом второго драйвера 12. Во второй момент T2, когда первый разрешающий сигнал EN21, соответствующий линии 62 четных данных, имеет нарастающий фронт, второй разрешающий сигнал EN22, соответствующий линии 62 четных данных, имеет спадающий фронт, первый драйвер 21, соответствующий линии 62 четных данных, переходит в состояние возбуждения, второй драйвер 22 переходит в высокоимпедансное состояние, а сигнал в линии 62 четных данных управляется входным сигналом первого драйвера 21. В четвертый момент T4, когда второй разрешающий сигнал EN22, соответствующий линии 62 четных данных, имеет нарастающий фронт, первый разрешающий сигнал EN21, соответствующий линии 62 четных данных, имеет спадающий фронт, второй драйвер 22, соответствующий линии 62 четных данных, переходит в состояние возбуждения, первый драйвер 21 переходит в высокоимпедансное состояние, а сигнал в линии 62 четных данных управляется входным сигналом второго драйвера 22.

Между первым разрешающим сигналом EN11, соответствующим линии 61 нечетных данных, и первым разрешающим сигналом EN21, соответствующим линии 62 четных данных, существует разность фаз, равная 180 градусов (T/2), и между вторым разрешающим сигналом EN12, соответствующим линии 61 нечетных данных, и вторым разрешающим сигналом EN22, соответствующим линии 62 четных данных, существует разность фаз, равная 180 градусов (T/2). В один и тот же момент времени только один из первого разрешающего сигнала EN11 и второго разрешающего сигнала EN12, соответствующих линии 61 нечетных данных, поддерживается на высоком уровне и только один из первого разрешающего сигнала EN21 и второго разрешающего сигнала EN22, соответствующих линии 62 четных данных, поддерживается на высоком уровне.

Управляя как линией 61 нечетных данных, так и линией 62 четных данных, которые необходимо поддерживать в состоянии возбуждения в любой момент времени, можно избежать взаимного влияния между попеременно передаваемыми нечетными данными и четными данными, и повысить надежность передачи данных.

На фиг. 8 представлена принципиальная схема способа возбуждения сигнальной линии согласно одному варианту осуществления настоящего изобретения.

Способ 800 возбуждения сигнальной линии может быть применен к конструкции с сигнальными линиями, показанной в любом из представленных выше вариантов осуществления.

Со ссылкой на фиг. 8, способ 800 возбуждения сигнальной линии может включать: этап S10, управление множеством параллельных сигнальных линий, которые необходимо поддерживать в состоянии возбуждения в любой момент времени.

В одном приведенном для примера варианте осуществления настоящего изобретения два конца каждой из сигнальных линий, соответственно, снабжены первым драйвером и вторым драйвером. Управление параллельными сигнальными линиями, которые необходимо поддерживать в состоянии возбуждения в любой момент времени, включает: управление в один и тот же момент времени только одним из первого драйвера и второго драйвера одной и той же сигнальной линии, которую необходимо поддерживать в состоянии возбуждения.

В одном приведенном для примера варианте осуществления настоящего изобретения первый драйвер или второй драйвер включают в себя по меньшей мере один стробирующий инвертор. Стробирующий инвертор снабжен входным выводом, электрически соединенным со входным сигналом, разрешающим выводом, соединенным с первым разрешающим сигналом или вторым разрешающим сигналом, и выходным выводом, электрически соединенным с сигнальной линией. Управление в один и тот же момент времени только одним из первого драйвера и второго драйвера одной и той же сигнальной линии, которую необходимо поддерживать в состоянии возбуждения, включает: подачу первого разрешающего сигнала с первым уровнем на разрешающий вывод первого драйвера таким образом, чтобы обеспечить поддержание первого драйвера в состоянии возбуждения, и, в тот же момент времени, подачу второго разрешающего сигнала со вторым уровнем на разрешающий вывод второго драйвера таким образом, чтобы обеспечить поддержание второго драйвера в высокоимпедансном состоянии; или подачу первого разрешающего сигнала со вторым уровнем на разрешающий вывод первого драйвера таким образом, чтобы обеспечить поддержание первого драйвера в высокоимпедансном состоянии, и, в тот же момент времени, подачу второго разрешающего сигнала с первым уровнем на разрешающий вывод второго драйвера таким образом, чтобы обеспечить поддержание второго драйвера в состоянии возбуждения.

В одном приведенном для примера варианте осуществления настоящего изобретения первый драйвер снабжен входным выводом для приема первого входного сигнала, разрешающим выводом, соединенным с первым узлом, и выходным выводом, соединенным с сигнальной линией. Второй драйвер снабжен входным выводом для приема второго входного сигнала, разрешающим выводом, соединенным со вторым узлом, и выходным выводом, соединенным с сигнальной линией. Первый узел выполнен с возможностью приема разрешающего сигнала драйвера. Второй узел и первый узел соединены посредством нечетного количества инверторов. Управление в один и тот же момент времени только одним из первого драйвера и второго драйвера, который необходимо поддерживать в состоянии возбуждения, включает: установку, в ответ на сообщение о поступлении первого входного сигнала, разрешающего сигнала драйвера на первый уровень таким образом, чтобы поддерживать первый драйвер в состоянии возбуждения и поддерживать второй драйвер в высокоимпедансном состоянии; и установку, в ответ на сообщение о поступлении второго входного сигнала, разрешающего сигнала драйвера на второй уровень таким образом, чтобы поддерживать второй драйвер в состоянии возбуждения и поддерживать первый драйвер в высокоимпедансном состоянии. В одном приведенном для примера варианте осуществления настоящего изобретения первый уровень является, например, высоким уровнем, а второй уровень является, например, низким уровнем.

В одном приведенном для примера варианте осуществления настоящего изобретения два конца каждой из сигнальных линий, соответственно, снабжены первым драйвером и вторым драйвером. Множество сигнальных линий включают в себя линии нечетных данных и линии четных данных. Управление параллельными сигнальными линиями, которые необходимо поддерживать в состоянии возбуждения в любой момент времени, включает: для одной и той же линии нечетных данных подачу первого разрешающего сигнала с первым уровнем в первый драйвер и подачу второго разрешающего сигнала со вторым уровнем во второй драйвер таким образом, чтобы обеспечить поддержание линии нечетных данных в состоянии возбуждения; или для одной и той же линии нечетных данных подачу первого разрешающего сигнала со вторым уровнем в первый драйвер и подачу второго разрешающего сигнала с первым уровнем во второй драйвер таким образом, чтобы обеспечить поддержание линии нечетных данных в состоянии возбуждения; и для одной и той же линии четных данных подачу первого разрешающего сигнала с первым уровнем в первый драйвер и подачу второго разрешающего сигнала со вторым уровнем во второй драйвер таким образом, чтобы обеспечить поддержание линии четных данных в состоянии возбуждения; или для одной и той же линии четных данных подачу первого разрешающего сигнала со вторым уровнем в первый драйвер и подачу второго разрешающего сигнала с первым уровнем во второй драйвер таким образом, чтобы обеспечить поддержание линии четных данных в состоянии возбуждения. Первый разрешающий сигнал, соответствующий линиям нечетных данных, и первый разрешающий сигнал, соответствующий линиям четных данных, имеют разные фазы, и второй разрешающий сигнал, соответствующий линиям нечетных данных, и второй разрешающий сигнал, соответствующий линиям четных данных, имеют разные фазы.

Соответствующие принципы способа 800 возбуждения сигнальной линии были объяснены в вариантах осуществления, показанных на фиг. 1-7. Их подробное описание в настоящем раскрытии не будет повторено.

На фиг. 9 представлена принципиальная схема сигнальной линии согласно одному приведенному для примера варианту осуществления настоящего изобретения.

Со ссылкой на фиг. 9, схема 900 сигнальной линии включает в себя:

- первый драйвер 91, снабженный входным выводом для приема первого входного сигнала IN11, разрешающим выводом, соединенным с первым узлом N1, и выходным выводом, соединенным с сигнальной линией 90;

- второй драйвер 92, снабженный входным выводом для приема второго входного сигнала IN12, разрешающим выводом, соединенным со вторым узлом N2, и выходным выводом, соединенным с сигнальной линией 90; и

- инвертор INV, снабженный входным выводом, соединенным с первым узлом N1, и выходным выводом, соединенным со вторым узлом N2, причем первый узел выполнен с возможностью приема разрешающего сигнала DRV драйвера, а разрешающий сигнал DRV драйвера имеет первый уровень, сконфигурированный для управления первым драйвером 11, который необходимо поддерживать в состоянии возбуждения, и вторым драйвером 12, который необходимо поддерживать в высокоимпедансном состоянии, и второй уровень, сконфигурированный для управления вторым драйвером 12, который необходимо поддерживать в состоянии возбуждения, и первым драйвером 11, который необходимо поддерживать в высокоимпедансном состоянии.

Схема 900 сигнальной линии, показанная на фиг. 9, позволяет обеспечить поддержание с помощью разрешающего сигнала DRV драйвера, независимо от того, находится ли он в состоянии высокого уровня или в состоянии низкого уровня, только одного из первого драйвера 91 и второго драйвера 92 в состоянии возбуждения. Следовательно, отсутствует необходимость в обеспечении изолирующей линии и средства хранения информации о состоянии для сигнальной линии 90, и также при переходе уровня может быть предотвращено влияние сигнальной линии 90 на сигнальную линию, параллельную и смежную с сигнальной линией 90. Следовательно, схема 900 сигнальной линии имеет меньшую площадь проводной разводки.

Следует отметить, что хотя в приведенном выше подробном описании указан ряд модулей или блоков устройства для выполнения, указанное разделение не является обязательным. На практике в соответствии с вариантами реализации настоящего изобретения признаки и функции двух или более модулей или блоков, описанных выше, могут быть осуществлены в одном модуле или блоке. Соответственно, признаки и функции модуля или блока, описанных выше, могут быть дополнительно разделены на множество модулей или блоков, подлежащих осуществлению.

Для специалистов в данной области техники после ознакомления с описанием и практического применения раскрытой в настоящем документе заявки будут очевидны другие варианты реализации настоящего изобретения. Эта заявка охватывает любые варианты, задачи или адаптивные изменения настоящего изобретения. Такие варианты, задачи или применимые изменения соответствуют общему принципу настоящего изобретения и включают в себя общеизвестные или обычные технические средства в данной области техники, которые не раскрыты в настоящем изобретении. Описание и варианты осуществления следует рассматривать исключительно как иллюстративные, а реальный объем и концепция настоящего изобретения определяются прилагаемой формулой изобретения.

Промышленная применимость

Согласно вариантам осуществления настоящего изобретения путем конфигурирования сигнальных линий, которые необходимо поддерживать в состоянии возбуждения, когда множество сигнальных линий расположены параллельно, можно предотвратить перекрестные помехи между сигнальными линиями, вызывающие ошибки в передаваемых данных, при этом отсутствует необходимость в изолирующем проводе и средстве хранения информации о состоянии, что позволяет значительно сэкономить площадь разводки сигнальных линий.

| название | год | авторы | номер документа |

|---|---|---|---|

| СХЕМА ПИКСЕЛЯ И УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2010 |

|

RU2504022C1 |

| СХЕМА ВОЗБУЖДЕНИЯ ДЛЯ ЛИНИЙ СКАНИРУЮЩЕГО СИГНАЛА, СДВИГОВЫЙ РЕГИСТР И СПОСОБ ВОЗБУЖДЕНИЯ СДВИГОВОГО РЕГИСТРА | 2009 |

|

RU2473977C1 |

| СДВИГОВЫЙ РЕГИСТР, ВОЗБУЖДАЮЩАЯ СХЕМА ЛИНИИ СИГНАЛОВ СКАНИРОВАНИЯ, СОДЕРЖАЩАЯ ЕГО, УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2010 |

|

RU2543312C2 |

| СХЕМА ДЛЯ ПЕРЕДАЧИ ВИДЕОДАННЫХ НА ДИСПЛЕЙ | 1994 |

|

RU2126177C1 |

| ДИСПЛЕЙНОЕ УСТРОЙСТВО И СПОСОБ ДЛЯ ВОЗБУЖДЕНИЯ ДИСПЛЕЙНОГО УСТРОЙСТВА | 2008 |

|

RU2443071C1 |

| СХЕМА ВОЗБУЖДЕНИЯ ЛИНИЙ СИГНАЛА СКАНИРОВАНИЯ И УСТРОЙСТВО ОТОБРАЖЕНИЯ, ВКЛЮЧАЮЩЕЕ В СЕБЯ ДАННУЮ СХЕМУ | 2010 |

|

RU2514903C2 |

| ЖИДКОКРИСТАЛЛИЧЕСКОЕ УСТРОЙСТВО ОТОБРАЖЕНИЯ И СПОСОБ ЕГО ВОЗБУЖДЕНИЯ | 2010 |

|

RU2496153C1 |

| ДИСПЛЕЙ | 1993 |

|

RU2160933C2 |

| ДИСПЛЕЙНОЕ УСТРОЙСТВО И СПОСОБ ДЛЯ ВОЗБУЖДЕНИЯ ДИСПЛЕЙНОГО УСТРОЙСТВА | 2008 |

|

RU2452038C2 |

| ДИСПЛЕЙНЫЙ МОДУЛЬ И ЭЛЕКТРОННОЕ УСТРОЙСТВО | 2020 |

|

RU2800491C1 |

Изобретение относится к конструкции с сигнальными линиями. Технический результат - улучшение качества сигнала в сигнальных линиях и экономия площади разводки параллельных сигнальных линий. Он достигается тем, что в настоящем изобретении предложена конструкция с сигнальными линиями, способ возбуждения сигнальной линии и схема сигнальной линии. Конструкция с сигнальными линиями включает в себя множество параллельных сигнальных линий, причем каждая из сигнальных линий поддерживается в состоянии возбуждения в любой момент времени. 3 н. и 4 з.п. ф-лы, 10 ил.

1. Конструкция с сигнальными линиями, содержащая:

множество параллельных сигнальных линий, причем каждая из сигнальных линий поддерживается в состоянии возбуждения в любой момент времени,

причем два конца каждой из сигнальных линий, соответственно, соединены с первым драйвером и вторым драйвером, при этом в один и тот же момент времени только один из первого драйвера и второго драйвера одной и той же сигнальной линии поддерживается в состоянии возбуждения,

первый драйвер поддерживается в состоянии возбуждения, когда первый разрешающий сигнал находится на первом уровне, и поддерживается в высокоимпедансном состоянии, когда первый разрешающий сигнал находится на втором уровне; а второй драйвер поддерживается в состоянии возбуждения, когда второй разрешающий сигнал находится на первом уровне, и поддерживается в высокоимпедансном состоянии, когда второй разрешающий сигнал находится на втором уровне,

причем первый драйвер или второй драйвер содержит по меньшей мере один стробирующий инвертор, при этом стробирующий инвертор снабжен входным выводом, электрически соединенным с входным сигналом, разрешающим выводом, соединенным с первым разрешающим сигналом или вторым разрешающим сигналом, и выходным выводом, электрически соединенным с сигнальной линией.

2. Конструкция с сигнальными линиями по п. 1, в которой

первый уровень является высоким уровнем, а второй уровень является низким уровнем, и/или

второй разрешающий сигнал получен путем инвертирования первого разрешающего сигнала с помощью инвертора.

3. Конструкция с сигнальными линиями по п. 1, в которой множество параллельных сигнальных линий содержат линии нечетных данных и линии четных данных, расположенные попеременно, причем линии нечетных данных выполнены с возможностью передачи нечетных сигналов, полученных путем дискретизации нечетных синхронизирующих тактовых импульсов, линии четных данных выполнены с возможностью передачи четных сигналов, полученных путем дискретизации четных синхронизирующих тактовых импульсов, и разность фаз между нечетными синхронизирующими тактовыми импульсами и четными синхронизирующими тактовыми импульсами составляет 180 градусов; и первый разрешающий сигнал, соответствующий линиям нечетных данных, и первый разрешающий сигнал, соответствующий линиям четных данных, имеют разные фазы, и второй разрешающий сигнал, соответствующий линиям нечетных данных, и второй разрешающий сигнал, соответствующий линиям четных данных, имеют разные фазы, причем

между первым разрешающим сигналом, соответствующим линиям нечетных данных, и первым разрешающим сигналом, соответствующим линиям четных данных, существует разность фаз, равная 180 градусам, и между вторым разрешающим сигналом, соответствующим линиям нечетных данных, и вторым разрешающим сигналом, соответствующим линиям четных данных, существует разность фаз, равная 180 градусам.

4. Способ возбуждения сигнальной линии, применяемый к конструкции с сигнальными линиями по любому из пп. 1-3, причем способ возбуждения сигнальной линии включает:

управление множеством параллельных сигнальных линий, которые необходимо поддерживать в состоянии возбуждения в любой момент времени,

причем два конца каждой из сигнальных линий снабжены, соответственно, первым драйвером и вторым драйвером; и управление множеством параллельных сигнальных линий, которые необходимо поддерживать в состоянии возбуждения в любой момент времени, включает:

управление в один и тот же момент времени только одним из первого драйвера и второго драйвера одной и той же сигнальной линии, которую необходимо поддерживать в состоянии возбуждения, при этом

первый драйвер или второй драйвер содержит по меньшей мере один стробирующий инвертор, который снабжен входным выводом, электрически соединенным с входным сигналом, разрешающим выводом, соединенным с первым разрешающим сигналом или вторым разрешающим сигналом, и выходным выводом, электрически соединенным с сигнальной линией; а управление в один и тот же момент времени только одним из первого драйвера и второго драйвера одной и той же сигнальной линии, которую необходимо поддерживать в состоянии возбуждения, включает: подачу первого разрешающего сигнала с первым уровнем на разрешающий вывод первого драйвера таким образом, чтобы обеспечить поддержание первого драйвера в состоянии возбуждения, и в тот же момент времени подачу второго разрешающего сигнала со вторым уровнем на разрешающий вывод второго драйвера таким образом, чтобы обеспечить поддержание второго драйвера в высокоимпедансном состоянии; или подачу первого разрешающего сигнала со вторым уровнем на разрешающий вывод первого драйвера таким образом, чтобы обеспечить поддержание первого драйвера в высокоимпедансном состоянии, и в тот же момент времени подачу второго разрешающего сигнала с первым уровнем на разрешающий вывод второго драйвера таким образом, чтобы обеспечить поддержание второго драйвера в состоянии возбуждения.

5. Способ возбуждения сигнальной линии по п. 4, согласно которому первый драйвер снабжен входным выводом для приема первого входного сигнала, разрешающим выводом, соединенным с первым узлом, и выходным выводом, соединенным с сигнальной линией; второй драйвер снабжен входным выводом для приема второго входного сигнала, разрешающим выводом, соединенным со вторым узлом, и выходным выводом, соединенным с сигнальной линией; первый узел выполнен с возможностью приема разрешающего сигнала драйвера; второй узел и первый узел соединены посредством нечетного количества инверторов; а управление в один и тот же момент времени только одним из первого драйвера и второго драйвера одной и той же сигнальной линии, который необходимо поддерживать в состоянии возбуждения, включает:

установку, в ответ на сообщение о поступлении первого входного сигнала, разрешающего сигнала драйвера на первый уровень таким образом, чтобы поддерживать первый драйвер в состоянии возбуждения и поддерживать второй драйвер в высокоимпедансном состоянии; и

установку, в ответ на сообщение о поступлении второго входного сигнала, разрешающего сигнала драйвера на второй уровень таким образом, чтобы поддерживать второй драйвер в состоянии возбуждения и поддерживать первый драйвер в высокоимпедансном состоянии,

причем первый уровень является высоким уровнем, а второй уровень является низким уровнем.

6. Способ возбуждения сигнальной линии по п. 4, согласно которому множество сигнальных линий содержат линии нечетных данных и линии четных данных; управление множеством параллельных сигнальных линий, которые необходимо поддерживать в состоянии возбуждения в любой момент времени, включает:

для одной и той же линии нечетных данных подачу первого разрешающего сигнала с первым уровнем в первый драйвер и подачу второго разрешающего сигнала со вторым уровнем во второй драйвер таким образом, чтобы обеспечить поддержание линии нечетных данных в состоянии возбуждения; или для одной и той же линии нечетных данных подачу первого разрешающего сигнала со вторым уровнем в первый драйвер и подачу второго разрешающего сигнала с первым уровнем во второй драйвер таким образом, чтобы обеспечить поддержание линии нечетных данных в состоянии возбуждения; и

для одной и той же линии четных данных подачу первого разрешающего сигнала с первым уровнем в первый драйвер и подачу второго разрешающего сигнала со вторым уровнем во второй драйвер таким образом, чтобы обеспечить поддержание линии четных данных в состоянии возбуждения; или для одной и той же линии четных данных подачу первого разрешающего сигнала со вторым уровнем в первый драйвер и подачу второго разрешающего сигнала с первым уровнем во второй драйвер таким образом, чтобы обеспечить поддержание линии четных данных в состоянии возбуждения; причем

первый разрешающий сигнал, соответствующий линиям нечетных данных, и первый разрешающий сигнал, соответствующий линиям четных данных, имеют разные фазы, и второй разрешающий сигнал, соответствующий линиям нечетных данных, и второй разрешающий сигнал, соответствующий линиям четных данных, имеют разные фазы.

7. Схема сигнальной линии, содержащая:

первый драйвер, снабженный входным выводом для приема первого входного сигнала, разрешающим выводом, соединенным с первым узлом, и выходным выводом, соединенным с сигнальной линией;

второй драйвер, снабженный входным выводом для приема второго входного сигнала, разрешающим выводом, соединенным со вторым узлом, и выходным выводом, соединенный с сигнальной линией; и

инвертор, снабженный входным выводом, соединенным с первым узлом, и выходным выводом, соединенным со вторым узлом, причем первый узел выполнен с возможностью приема разрешающего сигнала драйвера, который имеет первый уровень, сконфигурированный для управления первым драйвером, который необходимо поддерживать в состоянии возбуждения, и вторым драйвером, который необходимо поддерживать в высокоимпедансном состоянии, и второй уровень, сконфигурированный для управления вторым драйвером, который необходимо поддерживать в состоянии возбуждения, и первым драйвером, который необходимо поддерживать в высокоимпедансном состоянии.

| JP 2003023086 A, 24.01.2003 | |||

| US 20110069782 A1, 24.03.2011 | |||

| US 20050018596 A1, 27.01.2005 | |||

| US 7477300 B2, 13.01.2009 | |||

| СПОСОБ СНИЖЕНИЯ ПЕРЕКРЕСТНЫХ ПОМЕХ В ЧЕТЫРЕХПРОВОДНЫХ ЭЛЕКТРИЧЕСКИХ ЛИНИЯХ ПЕРЕДАЧИ ДАННЫХ | 2009 |

|

RU2419969C2 |

Авторы

Даты

2024-08-01—Публикация

2022-04-18—Подача