Область техники, к которой относится изобретение

Настоящее изобретение имеет отношение к схеме возбуждения и к способу возбуждения для устройства отображения с активной матрицей. Конкретнее, изобретение имеет отношение к сдвиговому регистру в схеме возбуждения для линий сканирующего сигнала, который возбуждает линии сканирующего сигнала, размещенные на участке отображения в устройстве отображения с активной матрицей, и к способу его возбуждения.

Уровень техники

Жидкокристаллические устройства отображения, использующие тонкопленочные транзисторы на основе аморфного кремния (a-Si) (именуемые в дальнейшем “a-Si TFT” - amorphous silicon thin film transistor) в качестве элементов возбудителя, известны достаточно хорошо. В последние годы на первый план выдвигается развитие жидкокристаллических устройств отображения, использующих тонкопленочные транзисторы на основе микрокристаллического кремния (именуемые в дальнейшем “µc-Si TFT”) в качестве элементов возбудителя. Подвижность микрокристаллического кремния больше, чем подвижность аморфного кремния, и µc-Si TFT могут формироваться посредством технологического процесса, подобного технологическому процессу для a-Si TFT. По этой причине, можно рассчитывать, что применение µc-Si TFT в качестве элементов возбудителя принесет, например, снижение затрат за счет сокращения площади кадра и уменьшения числа кристаллов в ИС возбудителя, повышение монтажной производительности, а также увеличение размеров устройств отображения. Дополнительно, µc-Si TFT обладают такой характерной особенностью, что пороговый сдвиг (изменение порогового напряжения), когда напряжение прикладывается к электроду затвора в течение длительного периода времени, меньше порогового сдвига для a-Si TFT. Другими словами, µc-Si TFT надежнее, чем a-Si TFT, в том смысле, что µc-Si TFT невосприимчивы к деградации.

Между прочим, модуль отображения жидкокристаллического устройства отображения с активной матрицей включает в себя множество линий шин истоков (линий видеосигнала), множество линий шин затворов (линий сканирующего сигнала), а также множество участков формирования элементов изображения, соответственно, предусмотренных на пересечениях множества линий шин истоков и множества линий шин затворов. Эти участки формирования элементов изображения размещаются в матрице для создания массива элементов изображения. Каждый участок формирования элементов изображения включает в себя, например, тонкопленочный транзистор в качестве переключающего элемента, чей контакт затвора подключается к линии шины затвора, которая проходит через соответствующее пересечение, и чей контакт истока подключается к линии шины истока, которая проходит через соответствующее пересечение, и емкость элемента изображения для хранения значения элемента изображения. Дополнительно, такое жидкокристаллическое устройство отображения с активной матрицей снабжается возбудителем истоков (схемой возбуждения для линий видеосигнала) для возбуждения множества линий шин истоков и возбудителем затворов (схемой возбуждения для линий сканирующего сигнала) для возбуждения множества линий шин затворов.

Видеосигналы, указывающие значения элементов изображения, переносятся по линиям шин истоков. Однако невозможно одновременно (вместе) перенести видеосигналы, указывающие значения элементов изображения, для множества линий через единственную линию шины истока. По этой причине, видеосигналы записываются в емкости элементов изображения в участках формирования элементов изображения, размещенных в матрице последовательно построчно. Следовательно, возбудитель затвора конфигурируется сдвиговым регистром с множеством каскадов так, чтобы множество линий шин затворов последовательно выбирались в течение предварительно заданного периода.

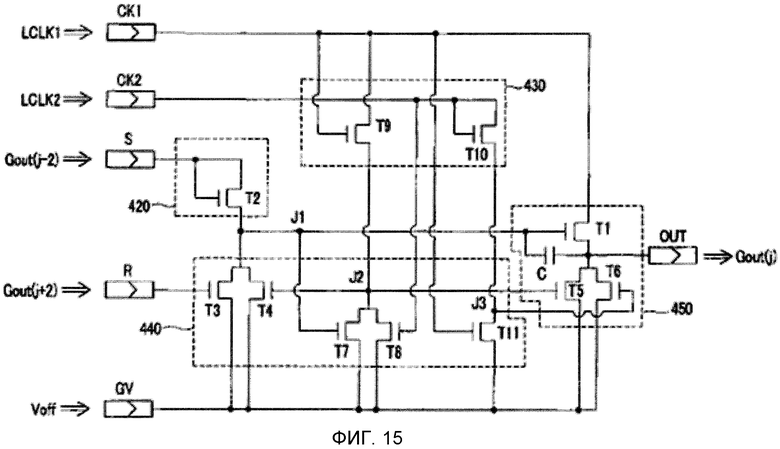

Желательно, чтобы каждая линия шины затвора приводилась в выбранное состояние только один раз в одном кадровом периоде (в одном периоде горизонтального сканирования). Следовательно, предпочтительно, чтобы сканирующий сигнал, который прикладывается к каждой линии шины затвора, был с потенциалом на Высоком уровне только в течение периода, в котором каждая линия шины затвора будет установлена в выбранное состояние (в дальнейшем, именуется как “период с выбором”), и с заданным потенциалом на Низком уровне в период, отличный от периода с выбором (в дальнейшем, именуется как “период без выбора”). Однако потенциал сканирующего сигнала иногда изменяется в положительную сторону от потенциала на Низком уровне в периоде без выбора под влиянием паразитной емкости, образуемой на схеме, которая формирует сдвиговый регистр. Так, например, Выложенная Заявка на Патент Японии Номер 2006-351171 раскрывает изобретение, касающееся сдвигового регистра с возможностью снижения влияния, обусловленного паразитной емкостью, по сравнению с традиционным случаем. Фиг.15 является принципиальной схемой, демонстрирующей конфигурацию, соответствующую одному каскаду в сдвиговом регистре, раскрытом в Выложенной Заявке на Патент Японии Номер 2006-351171. В соответствии с этой схемой, на протяжении периода без выбора, линия шины затвора не переходит в высокоимпедансное состояние, а запирающее напряжение всегда подается на линию шины затвора. Считается, что это позволяет подавлять влияние, обусловленное паразитной емкостью.

ДОКУМЕНТ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

ПАТЕНТНЫЙ ДОКУМЕНТ

[Патентный документ 1] Выложенная Заявка на Патент Японии Номер 2006-351171

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Задачи, решаемые изобретением

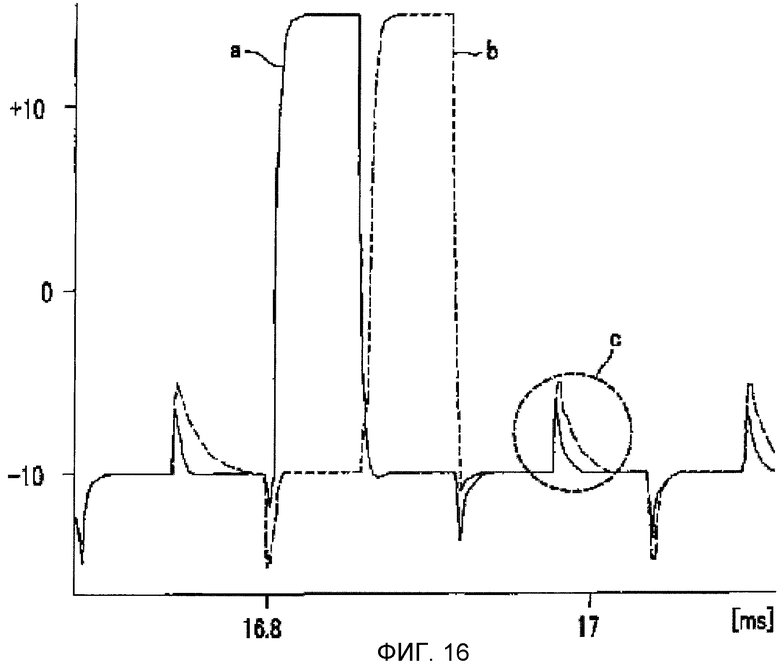

При конфигурации, описанной выше, однако, как показано условным обозначением “c” на Фиг.16 (Фиг.9 в Выложенной Заявке на Патент Японии Номер 2006-351171), в периоде без выбора, потенциал сканирующего сигнала изменяется в положительную сторону от потенциала на Низком уровне из-за влияния паразитной емкости. В качестве причины этого рассматривается следующее. В Выложенной Заявке на Патент Японии Номер 2006-351171, внимание сосредоточено на паразитной емкости между линией шины затвора и общим электродом. Однако подобная паразитная емкость образуется также между электродами тонкопленочного транзистора в схеме, которая формирует сдвиговый регистр. Например, паразитная емкость образуется между затвором и истоком тонкопленочного транзистора, показанного условным обозначением T1 на Фиг.15. Поэтому, когда потенциал синхроимпульса LCLK1 изменяется с Низкого уровня на Высокий уровень, потенциал контакта затвора тонкопленочного транзистора T1 повышается вследствие паразитной емкости. В результате, ток утечки протекает через тонкопленочный транзистор T1, так что потенциал сканирующего сигнала изменяется. В данном документе, поскольку синхроимпульс LCLK1 устанавливается в состояние Высокого уровня в предварительно заданном цикле, даже в периоде без выбора, потенциал сканирующего сигнала изменяется в этом предварительно заданном цикле.

Как описано выше, когда потенциал сканирующего сигнала в периоде без выбора изменяется, излишний электрический ток протекает через линию шины затвора для передачи сканирующего сигнала. Например, в случае устройства отображения, на котором применяется панель WXGA, в каждый момент времени, только одна из 768 линий шин затворов будет установлена в выбранное состояние, а каждая из остальных 767 линий шин затворов будет установлена в невыбранное состояние. Другими словами, сканирующий сигнал, который прикладывается к каждой из этих 767 линий шин затворов, должен быть установлен на Низкий уровень. Однако, если ток утечки, описанный выше, генерируется в каждом каскаде сдвигового регистра, излишние электрические токи, соответствующие 767 линиям шин затвора, протекают через все устройство отображения. Следовательно, происходит излишнее потребление электроэнергии.

Более того, описанный выше µc-Si TFT имеет большую, чем a-Si TFT, утечку в закрытом состоянии (ток утечки, генерируемый в Закрытом состоянии). Таким образом, в случае применения µc-Si TFT для схемы, которая формирует сдвиговый регистр, излишнее потребление мощности из-за тока утечки становится большим, по сравнению со случаем применения a-Si TFT.

Задачей настоящего изобретения является реализация схемы возбуждения для линий сканирующего сигнала (в устройстве отображения), способной, даже в случае, когда схема в сдвиговом регистре формируется с использованием тонкопленочного транзистора, который имеет относительно большую утечку в закрытом состоянии, подавлять излишнее потребление мощности из-за тока утечки в тонкопленочном транзисторе.

Средство для решения задач

Первый аспект настоящего изобретения направлен на схему возбуждения для линий сканирующего сигнала устройства отображения, которая возбуждает множество линий сканирующего сигнала, размещенных на участке отображения, причем схема возбуждения для линий сканирующего сигнала содержит:

сдвиговый регистр, включающий в себя множество бистабильных схем, каждая из которых обладает первым состоянием и вторым состоянием и подключается последовательно одна к другой, причем сдвиговый регистр устанавливает множество бистабильных схем последовательно в первое состояние, основываясь на четырехфазных сигналах синхронизации, которые вводятся извне и подаются в качестве первого, второго, третьего и четвертого сигналов синхронизации на соответствующие бистабильные схемы, при этом каждый из четырехфазных сигналов синхронизации циклически воспроизводит потенциал на Высоком уровне и потенциал на Низком уровне, причем

каждая бистабильная схема включает в себя:

зарядный участок выходной узловой точки, включающий в себя первый переключающий элемент, имеющий второй электрод, по которому подается первый сигнал синхронизации, и третий электрод, подключенный к выходной узловой точке, которая является узловой точкой для вывода сигнала состояния, указывающего либо первое состояние, либо второе состояние, и которая является узловой точкой, подключенной к линии сканирующего сигнала, причем этот зарядный участок выходной узловой точки устанавливает состояние, указанное сигналом состояния, в первое состояние;

разрядный участок выходной узловой точки для установки состояния, указанного сигналом состояния, во второе состояние;

зарядный участок первой узловой точки для зарядки первой узловой точки, подключенной к первому электроду первого переключающего элемента, на основании предварительно заданного установочного сигнала;

первый разрядный участок первой узловой точки для разрядки первой узловой точки, причем этот первый разрядный участок первой узловой точки включает в себя второй переключающий элемент, имеющий второй электрод, подключенный к первой узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал;

зарядный участок второй узловой точки для зарядки второй узловой точки, подключенной к первому электроду второго переключающего элемента, на основании третьего сигнала синхронизации; и

первый разрядный участок второй узловой точки для разрядки второй узловой точки, на основании четвертого сигнала синхронизации,

коэффициент заполнения, который является отношением периода, в течение которого поддерживается потенциал на Высоком уровне, к циклу, в котором потенциал на Высоком уровне и потенциал на Низком уровне повторяются в отношении каждого из четырехфазных сигналов синхронизации, устанавливается равным одной второй,

первый сигнал синхронизации и второй сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу,

третий сигнал синхронизации и четвертый сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу, и

третий сигнал синхронизации опережает по фазе первый сигнал синхронизации.

Согласно второму аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

в каждой бистабильной схеме,

зарядный участок второй узловой точки включает в себя третий переключающий элемент, имеющий первый электрод и второй электрод, на каждый из которых подается третий сигнал синхронизации, и третий электрод, подключенный ко второй узловой точке,

первый разрядный участок второй узловой точки включает в себя четвертый переключающий элемент, имеющий первый электрод, на который подается четвертый сигнал синхронизации, второй электрод, подключенный ко второй узловой точке, и третий электрод, на который подается предварительно заданный низкий потенциал, и

зарядный участок первой узловой точки включает в себя пятый переключающий элемент, имеющий первый электрод и третий электрод, на каждый из которых подается установочный сигнал, и второй электрод, подключенный к первой узловой точке.

Согласно третьему аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

каждая бистабильная схема дополнительно включает в себя:

второй разрядный участок второй узловой точки для разрядки второй узловой точки на основании зарядного напряжения первой узловой точки, причем этот второй разрядный участок второй узловой точки включает в себя шестой переключающий элемент, имеющий первый электрод, подключенный к первой узловой точке, второй электрод, подключенный ко второй узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал; и

второй разрядный участок первой узловой точки для разрядки первой узловой точки на основании предварительно заданного сигнала сброса, причем этот второй разрядный участок первой узловой точки включает в себя седьмой переключающий элемент, имеющий первый электрод, по которому подается сигнал сброса, второй электрод, подключенный к первой узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал.

Согласно четвертому аспекту настоящего изобретения, в третьем аспекте настоящего изобретения,

четырехфазные сигналы синхронизации формируются первой группой сигналов синхронизации, включающей в себя двухфазные сигналы синхронизации, которые подаются в качестве первого и второго сигналов синхронизации на каждую бистабильную схему, и второй группой сигналов синхронизации, включающей в себя двухфазные сигналы синхронизации, которые подаются в качестве третьего и четвертого сигналов синхронизации на каждую бистабильную схему, и

когда две соседние бистабильные схемы определяются как первая и вторая бистабильные схемы,

на первую бистабильную схему подается, в качестве первого сигнала синхронизации, один из двухфазных сигналов синхронизации, входящих в состав первой группы сигналов синхронизации, подается, в качестве второго сигнала синхронизации, другой из двухфазных сигналов синхронизации, входящих в состав первой группы сигналов синхронизации, подается, в качестве третьего сигнала синхронизации, один из двухфазных сигналов синхронизации, входящих в состав второй группы сигналов синхронизации, подается, в качестве четвертого сигнала синхронизации, другой из двухфазных сигналов синхронизации, входящих в состав второй группы сигналов синхронизации, и подается, в качестве сигнала сброса, сигнал состояния, выводимый от второй бистабильной схемы, и

на вторую бистабильную схему подается, в качестве первого сигнала синхронизации, сигнал, который подается в качестве второго сигнала синхронизации на первую бистабильную схему, подается, в качестве второго сигнала синхронизации, сигнал, который подается в качестве первого сигнала синхронизации на первую бистабильную схему, подается, в качестве третьего сигнала синхронизации, сигнал, который подается в качестве четвертого сигнала синхронизации на первую бистабильную схему, подается, в качестве четвертого сигнала синхронизации, сигнал, который подается в качестве третьего сигнала синхронизации на первую бистабильную схему, и подается, в качестве установочного сигнала, сигнал состояния, выводимый от первой бистабильной схемы.

Согласно пятому аспекту настоящего изобретения, в четвертом аспекте настоящего изобретения,

сигнальная линия, передающая первую группу сигналов синхронизации, является большей по ширине, чем сигнальная линия, передающая вторую группу сигналов синхронизации.

Согласно шестому аспекту настоящего изобретения, в третьем аспекте настоящего изобретения,

четырехфазные сигналы синхронизации формируются первым набором сигналов синхронизации и вторым набором сигналов синхронизации, каждый из которых включает в себя двухфазные сигналы синхронизации, сдвинутые по фазе на 180 градусов по отношению друг к другу, и

когда бистабильная схема, предшествующая некоторой одной из множества бистабильных схем, определяется как первая бистабильная схема, а бистабильная схема, следующая за этой некоторой бистабильной схемой, определяется как вторая бистабильная схема,

на первую бистабильную схему подается, в качестве первого сигнала синхронизации, один из двухфазных сигналов синхронизации, входящих в состав первого набора сигналов синхронизации, подается, в качестве второго сигнала синхронизации, другой из двухфазных сигналов синхронизации, входящих в состав первого набора сигналов синхронизации, подается, в качестве третьего сигнала синхронизации, один из двухфазных сигналов синхронизации, входящих в состав второго набора сигналов синхронизации, подается, в качестве четвертого сигнала синхронизации, другой из двухфазных сигналов синхронизации, входящих в состав второго набора сигналов синхронизации, и подается, в качестве сигнала сброса, сигнал состояния, выводимый от второй бистабильной схемы, и

на вторую бистабильную схему подается, в качестве первого сигнала синхронизации, сигнал, который подается в качестве второго сигнала синхронизации на первую бистабильную схему, подается, в качестве второго сигнала синхронизации, сигнал, который подается в качестве первого сигнала синхронизации на первую бистабильную схему, подается, в качестве третьего сигнала синхронизации, сигнал, который подается в качестве четвертого сигнала синхронизации на первую бистабильную схему, подается, в качестве четвертого сигнала синхронизации, сигнал, который подается в качестве третьего сигнала синхронизации на первую бистабильную схему, и подается, в качестве установочного сигнала, сигнал состояния, выводимый от первой бистабильной схемы.

Согласно седьмому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

разрядный участок выходной узловой точки включает в себя:

первый разрядный участок выходной узловой точки для установки состояния, указанного сигналом состояния, во второе состояние, на основании сигнала сброса, причем этот первый разрядный участок выходной узловой точки включает в себя восьмой переключающий элемент, имеющий первый электрод, на который подается сигналом сброса, второй электрод, подключенный к выходной узловой точке, и третий электрод, на который подается предварительно заданный низкий потенциал; и

второй разрядный участок выходной узловой точки для установки состояния, указанного сигналом состояния, во второе состояние, на основании второго сигнала синхронизации, причем этот второй разрядный участок выходной узловой точки включает в себя девятый переключающий элемент, имеющий первый электрод, на который подается второй сигнал синхронизации, второй электрод, подключенный к выходной узловой точке, и третий электрод, на который подается предварительно заданный низкий потенциал.

Согласно восьмому аспекту настоящего изобретения, в седьмом аспекте настоящего изобретения,

разрядный участок выходной узловой точки дополнительно включает в себя третий разрядный участок выходной узловой точки для установки состояния, указанного сигналом состояния, во второе состояние, на основании зарядного напряжения второй узловой точки, причем этот третий разрядный участок выходной узловой точки включает в себя десятый переключающий элемент, имеющий первый электрод, подключенный ко второй узловой точке, второй электрод, подключенный к выходной узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал.

Согласно девятому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

каждая бистабильная схема дополнительно включает в себя конденсатор с одним концом, подключенным к первой узловой точке, и другим концом, подключенным к выходной узловой точке.

Согласно десятому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

третий сигнал синхронизации опережает по фазе на 90 градусов первый сигнал синхронизации.

Согласно одиннадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

схема возбуждения для линий сканирующего сигнала включает в себя

первую схему возбуждения для линий сканирующего сигнала для подачи сигнала состояния от одних концов на другие концы множества линий сканирующего сигнала, и

вторую схему возбуждения для линий сканирующего сигнала для подачи сигнала состояния от этих других концов на эти первые концы множества линий сканирующего сигнала.

Согласно двенадцатому аспекту настоящего изобретения, в одиннадцатом аспекте настоящего изобретения,

первая схема возбуждения для линий сканирующего сигнала подает сигнал состояния или на множество линий сканирующего сигнала на нечетных строках, или на множество линий сканирующего сигнала на четных строках, и

вторая схема возбуждения для линий сканирующего сигнала подает сигнал состояния на иное или множество линий сканирующего сигнала на нечетных строках, или множество линий сканирующего сигнала на четных строках.

Согласно тринадцатому аспекту настоящего изобретения, в одиннадцатом аспекте настоящего изобретения,

на каждую линию сканирующего сигнала подается сигнал состояния и от первой схемы возбуждения для линий сканирующего сигнала и от второй схемы возбуждения для линий сканирующего сигнала.

Согласно четырнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

переключающие элементы, входящие в состав каждой бистабильной схемы, представляют собой тонкопленочные транзисторы, сделанные из микрокристаллического кремния.

Согласно пятнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

переключающие элементы, входящие в состав каждой бистабильной схемы, представляют собой тонкопленочные транзисторы, сделанные из аморфного кремния.

Согласно шестнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

по меньшей мере, один из переключающих элементов, каждый из которых имеет второй электрод, подключенный к первой узловой точке, представляет собой тонкопленочный транзистор с многоканальной структурой.

Семнадцатый аспект настоящего изобретения направлен на устройство отображения, которое содержит:

участок отображения; и

схему возбуждения для линий сканирующего сигнала, которая возбуждает множество линий сканирующего сигнала, размещенных на участке отображения, при этом

схема возбуждения для линий сканирующего сигнала включает в себя сдвиговый регистр, включающий в себя множество бистабильных схем, каждая из которых обладает первым состоянием и вторым состоянием и подключается последовательно одна к другой, причем сдвиговый регистр устанавливает множество бистабильных схем последовательно в первое состояние, основываясь на четырехфазных сигналах синхронизации, которые вводятся извне и подаются в качестве первого, второго, третьего и четвертого сигналов синхронизации на соответствующие бистабильные схемы, при этом каждый из четырехфазных сигналов синхронизации циклически воспроизводит потенциал на Высоком уровне и потенциал на Низком уровне,

каждая бистабильная схема включает в себя:

зарядный участок выходной узловой точки, включающий в себя первый переключающий элемент, имеющий второй электрод, по которому подается первый сигнал синхронизации, и третий электрод, подключенный к выходной узловой точке, которая является узловой точкой для вывода сигнала состояния, указывающего либо первое состояние, либо второе состояние, и которая является узловой точкой, подключенной к линии сканирующего сигнала, причем этот зарядный участок выходной узловой точки устанавливает состояние, указанное сигналом состояния, в первое состояние;

разрядный участок выходной узловой точки для установки состояния, указанного сигналом состояния, во второе состояние;

зарядный участок первой узловой точки для зарядки первой узловой точки, подключенной к первому электроду первого переключающего элемента, на основании предварительно заданного установочного сигнала;

первый разрядный участок первой узловой точки для разрядки первой узловой точки, причем этот первый разрядный участок первой узловой точки включает в себя второй переключающий элемент, имеющий второй электрод, подключенный к первой узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал;

зарядный участок второй узловой точки для зарядки второй узловой точки, подключенной к первому электроду второго переключающего элемента, на основании третьего сигнала синхронизации; и

первый разрядный участок второй узловой точки для разрядки второй узловой точки, на основании четвертого сигнала синхронизации,

коэффициент заполнения, который является отношением периода, в течение которого поддерживается потенциал на Высоком уровне, к циклу, в котором потенциал на Высоком уровне и потенциал на Низком уровне повторяются в отношении каждого из четырехфазных сигналов синхронизации, устанавливается равным одной второй,

первый сигнал синхронизации и второй сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу,

третий сигнал синхронизации и четвертый сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу, и

третий сигнал синхронизации опережает по фазе первый сигнал синхронизации.

Согласно восемнадцатому аспекту настоящего изобретения, в семнадцатом аспекте настоящего изобретения,

устройство отображения является возбудителем монолитного типа, в котором участок отображения и схема возбуждения для линий сканирующего сигнала формируются на единой подложке.

Девятнадцатый аспект настоящего изобретения направлен на сдвиговый регистр для возбуждения множества линий сканирующего сигнала, размещенных на участке отображения в устройстве отображения, при этом сдвиговый регистр содержит множество бистабильных схем, каждая из которых обладает первым состоянием и вторым состоянием и подключается последовательно одна к другой, причем сдвиговый регистр устанавливает множество бистабильных схем последовательно в первое состояние, основываясь на четырехфазных сигналах синхронизации, которые вводятся извне и подаются в качестве первого, второго, третьего и четвертого сигналов синхронизации на соответствующие бистабильные схемы, при этом каждый из четырехфазных сигналов синхронизации циклически воспроизводит потенциал на Высоком уровне и потенциал на Низком уровне, причем

каждая бистабильная схема включает в себя:

зарядный участок выходной узловой точки, включающий в себя первый переключающий элемент, имеющий второй электрод, по которому подается первый сигнал синхронизации, и третий электрод, подключенный к выходной узловой точке, которая является узловой точкой для вывода сигнала состояния, указывающего либо первое состояние, либо второе состояние, и которая является узловой точкой, подключенной к линии сканирующего сигнала, причем этот зарядный участок выходной узловой точки устанавливает состояние, указанное сигналом состояния, в первое состояние;

разрядный участок выходной узловой точки для установки состояния, указанного сигналом состояния, во второе состояние;

зарядный участок первой узловой точки для зарядки первой узловой точки, подключенной к первому электроду первого переключающего элемента, на основании предварительно заданного установочного сигнала;

первый разрядный участок первой узловой точки для разрядки первой узловой точки, причем этот первый разрядный участок первой узловой точки включает в себя второй переключающий элемент, имеющий второй электрод, подключенный к первой узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал;

зарядный участок второй узловой точки для зарядки второй узловой точки, подключенной к первому электроду второго переключающего элемента, на основании третьего сигнала синхронизации; и

первый разрядный участок второй узловой точки для разрядки второй узловой точки, на основании четвертого сигнала синхронизации,

коэффициент заполнения, который является отношением периода, в течение которого поддерживается потенциал на Высоком уровне, к циклу, в котором потенциал на Высоком уровне и потенциал на Низком уровне повторяются в отношении каждого из четырехфазных сигналов синхронизации, устанавливается равным одной второй,

первый сигнал синхронизации и второй сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу,

третий сигнал синхронизации и четвертый сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу, и

третий сигнал синхронизации опережает по фазе первый сигнал синхронизации.

Двадцатый аспект настоящего изобретения направлен на способ возбуждения для сдвигового регистра, для возбуждения множества линий сканирующего сигнала, размещенных на участке отображения в устройстве отображения, при этом сдвиговый регистр включает в себя множество бистабильных схем, каждая из которых обладает первым состоянием и вторым состоянием и подключается последовательно одна к другой, причем сдвиговый регистр устанавливает множество бистабильных схем последовательно в первое состояние, основываясь на четырехфазных сигналах синхронизации, которые вводятся извне и подаются в качестве первого, второго, третьего и четвертого сигналов синхронизации на соответствующие бистабильные схемы, при этом каждый из четырехфазных сигналов синхронизации циклически воспроизводит потенциал на Высоком уровне и потенциал на Низком уровне,

способ возбуждения содержит:

первый этап возбуждения, на котором переводят каждую бистабильную схему из второго состояния в первое состояние, поддерживают каждую бистабильную схему в первом состоянии в течение предварительно заданного периода, а затем переводят каждую бистабильную схему во второе состояние; и

второй этап возбуждения, на котором поддерживают каждую бистабильную схему во втором состоянии, и при этом

каждая бистабильная схема включает в себя:

выходную узловую точку, которая является узловой точкой для вывода сигнала состояния, указывающего либо первое состояние, либо второе состояние, и которая является узловой точкой, подключенной к линии сканирующего сигнала;

первый переключающий элемент, имеющий второй электрод, по которому подается первый сигнал синхронизации, и третий электрод, подключенный к выходной узловой точке;

первую узловую точку, подключенную к первому электроду первого переключающего элемента;

второй переключающий элемент, имеющий второй электрод, подключенный к первой узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал; и

вторую узловую точку, подключенную к первому электроду второго переключающего элемента,

первый этап возбуждения включает в себя:

этап зарядки первой узловой точки, на котором заряжают первую узловую точку, подавая предварительно заданный установочный сигнал на каждую бистабильную схему;

этап зарядки выходной узловой точки, на котором переводят состояние, указанное сигналом состояния, из второго состояния в первое состояние, изменяя потенциал первого сигнала синхронизации с Низкого уровня на Высокий уровень; и

первый этап разрядки выходной узловой точки, на котором переводят состояние, указанное сигналом состояния, из первого состояния во второе состояние, подавая предварительно заданный сигнал сброса на каждую бистабильную схему,

второй этап возбуждения включает в себя:

этап зарядки второй узловой точки, на котором заряжают вторую узловую точку, изменяя потенциал третьего сигнала синхронизации с Низкого уровня на Высокий уровень; и

первый этап разрядки второй узловой точки, на котором разряжают вторую узловую точку, изменяя потенциал четвертого сигнала синхронизации с Низкого уровня на Высокий уровень,

коэффициент заполнения, который является отношением периода, в течение которого поддерживается потенциал на Высоком уровне, к циклу, в котором потенциал на Высоком уровне и потенциал на Низком уровне повторяются в отношении каждого из четырехфазных сигналов синхронизации, устанавливается равным одной второй,

первый сигнал синхронизации и второй сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу,

третий сигнал синхронизации и четвертый сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу, и

третий сигнал синхронизации опережает по фазе первый сигнал синхронизации.

Согласно двадцать первому аспекту настоящего изобретения, в двадцатом аспекте настоящего изобретения,

каждая бистабильная схема дополнительно включает в себя:

третий переключающий элемент, имеющий первый электрод и второй электрод, на каждый из которых подается третий сигнал синхронизации, и третий электрод, подключенный ко второй узловой точке;

четвертый переключающий элемент, имеющий первый электрод, по которому подается четвертый сигнал синхронизации, второй электрод, подключенный ко второй узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал; и

пятый переключающий элемент, имеющий первый электрод и третий электрод, на каждый из которых подается установочный сигнал, и второй электрод, подключенный к первой узловой точке,

на этапе зарядки второй узловой точки, вторая узловая точка заряжается таким образом, что третий переключающий элемент устанавливается в Открытое состояние, на основании третьего сигнала синхронизации,

на первом этапе разрядки второй узловой точки, вторая узловая точка разряжается таким образом, что четвертый переключающий элемент устанавливается в Открытое состояние, на основании четвертого сигнала синхронизации, и

на этапе зарядки первой узловой точки, первая узловая точка заряжается таким образом, что пятый переключающий элемент устанавливается в Открытое состояние, на основании установочного сигнала.

Согласно двадцать второму аспекту настоящего изобретения, в двадцатом аспекте настоящего изобретения,

первый этап возбуждения дополнительно включает в себя:

второй этап разрядки второй узловой точки, на котором разряжают вторую узловую точку, на основании зарядного напряжения первой узловой точки; и

второй этап разрядки первой узловой точки, на котором разряжают первую узловую точку, на основании сигнала сброса,

каждая бистабильная схема дополнительно включает в себя:

шестой переключающий элемент, имеющий первый электрод, подключенный к первой узловой точке, второй электрод, подключенный ко второй узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал; и

седьмой переключающий элемент, имеющий первый электрод, по которому подается сигнал сброса, второй электрод, подключенный к первой узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал,

на втором этапе разрядки второй узловой точки, вторая узловая точка разряжается таким образом, что шестой переключающий элемент устанавливается в Открытое состояние, на основании зарядного напряжения первой узловой точки, и

на втором этапе разрядки первой узловой точки, первая узловая точка разряжается таким образом, что седьмой переключающий элемент устанавливается в Открытое состояние, на основании сигнала сброса.

Согласно двадцать третьему аспекту настоящего изобретения, в двадцатом аспекте настоящего изобретения,

четырехфазные сигналы синхронизации формируются первой группой сигналов синхронизации, включающей в себя двухфазные сигналы синхронизации, которые подаются в качестве первого и второго сигналов синхронизации на каждую бистабильную схему, и второй группой сигналов синхронизации, включающей в себя двухфазные сигналы синхронизации, которые подаются в качестве третьего и четвертого сигналов синхронизации на каждую бистабильную схему, и

когда две соседние бистабильные схемы определяются как первая и вторая бистабильные схемы,

на первую бистабильную схему подается, в качестве первого сигнала синхронизации, один из двухфазных сигналов синхронизации, входящих в состав первой группы сигналов синхронизации, подается, в качестве второго сигнала синхронизации, другой из двухфазных сигналов синхронизации, входящих в состав первой группы сигналов синхронизации, подается, в качестве третьего сигнала синхронизации, один из двухфазных сигналов синхронизации, входящих в состав второй группы сигналов синхронизации, подается, в качестве четвертого сигнала синхронизации, другой из двухфазных сигналов синхронизации, входящих в состав второй группы сигналов синхронизации, и подается, в качестве сигнала сброса, сигнал состояния, выводимый от второй бистабильной схемы, и

на вторую бистабильную схему подается, в качестве первого сигнала синхронизации, сигнал, который подается в качестве второго сигнала синхронизации на первую бистабильную схему, подается, в качестве второго сигнала синхронизации, сигнал, который подается в качестве первого сигнала синхронизации на первую бистабильную схему, подается, в качестве третьего сигнала синхронизации, сигнал, который подается в качестве четвертого сигнала синхронизации на первую бистабильную схему, подается, в качестве четвертого сигнала синхронизации, сигнал, который подается в качестве третьего сигнала синхронизации на первую бистабильную схему, и подается, в качестве установочного сигнала, сигнал состояния, выводимый от первой бистабильной схемы.

Согласно двадцать четвертому аспекту настоящего изобретения, в двадцатом аспекте настоящего изобретения,

четырехфазные сигналы синхронизации формируются первым набором сигналов синхронизации и вторым набором сигналов синхронизации, каждый из которых включает в себя двухфазные сигналы синхронизации, сдвинутые по фазе на 180 градусов по отношению друг к другу, и

когда бистабильная схема, предшествующая некоторой одной из множества бистабильных схем, определяется как первая бистабильная схема, а бистабильная схема, следующая за этой некоторой бистабильной схемой, определяется как вторая бистабильная схема,

на первую бистабильную схему подается, в качестве первого сигнала синхронизации, один из двухфазных сигналов синхронизации, входящих в состав первого набора сигналов синхронизации, подается, в качестве второго сигнала синхронизации, другой из двухфазных сигналов синхронизации, входящих в состав первого набора сигналов синхронизации, подается, в качестве третьего сигнала синхронизации, один из двухфазных сигналов синхронизации, входящих в состав второго набора сигналов синхронизации, подается, в качестве четвертого сигнала синхронизации, другой из двухфазных сигналов синхронизации, входящих в состав второго набора сигналов синхронизации, и подается, в качестве сигнала сброса, сигнал состояния, выводимый от второй бистабильной схемы, и

на вторую бистабильную схему подается, в качестве первого сигнала синхронизации, сигнал, который подается в качестве второго сигнала синхронизации на первую бистабильную схему, подается, в качестве второго сигнала синхронизации, сигнал, который подается в качестве первого сигнала синхронизации на первую бистабильную схему, подается, в качестве третьего сигнала синхронизации, сигнал, который подается в качестве четвертого сигнала синхронизации на первую бистабильную схему, подается, в качестве четвертого сигнала синхронизации, сигнал, который подается в качестве третьего сигнала синхронизации на первую бистабильную схему, и подается, в качестве установочного сигнала, сигнал состояния, выводимый от первой бистабильной схемы.

Согласно двадцать пятому аспекту настоящего изобретения, в двадцатом аспекте настоящего изобретения,

третий сигнал синхронизации опережает по фазе на 90 градусов первый сигнал синхронизации.

Согласно двадцать шестому аспекту настоящего изобретения, в двадцатом аспекте настоящего изобретения,

каждая бистабильная схема дополнительно включает в себя:

восьмой переключающий элемент, имеющий первый электрод, по которому подается сигнал сброса, второй электрод, подключенный к выходной узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал; и

девятый переключающий элемент, имеющий первый электрод, по которому подается второй сигнал синхронизации, второй электрод, подключенный к выходной узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал,

и первый этап возбуждения, и второй этап возбуждения дополнительно включают в себя второй этап разрядки выходной узловой точки, на котором подают второй сигнал синхронизации на девятый переключающий элемент, чтобы поддерживать состояние, указанное сигналом состояния, во втором состоянии,

на первом этапе разрядки выходной узловой точки, состояние, указанное сигналом состояния, переводится из первого состояния во второе состояние таким образом, что восьмой переключающий элемент устанавливается в Открытое состояние, на основании сигнала сброса, и

на втором этапе разрядки выходной узловой точки, состояние, указанное сигналом состояния, поддерживается во втором состоянии таким образом, что девятый переключающий элемент устанавливается в Открытое состояние, на основании второго сигнала синхронизации.

Согласно двадцать седьмому аспекту настоящего изобретения, в двадцать шестом аспекте настоящего изобретения,

каждая бистабильная схема дополнительно включает в себя:

десятый переключающий элемент, имеющий первый электрод, подключенный ко второй узловой точке, второй электрод, подключенный к выходной узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал,

и первый этап возбуждения, и второй этап возбуждения дополнительно включают в себя третий этап разрядки выходной узловой точки, на котором поддерживают состояние, указанное сигналом состояния, во втором состоянии, на основании зарядного напряжения второй узловой точки, и

на третьем этапе разрядки выходной узловой точки, состояние, указанное сигналом состояния, поддерживается во втором состоянии таким образом, что десятый переключающий элемент устанавливается в Открытое состояние, на основании зарядного напряжения второй узловой точки.

Результаты изобретения

Согласно первому аспекту настоящего изобретения, в каждой бистабильной схеме, которая формирует сдвиговый регистр в схеме возбуждения для линий сканирующего сигнала устройства отображения, первый переключающий элемент имеет конфигурацию, в которой первый электрод подключается к первой узловой точке, по второму электроду подается первый сигнал синхронизации, а третий электрод подключается к выходной узловой точке. Таким образом, когда потенциал первой узловой точки повышается, на основании предварительно заданного установочного сигнала, а затем первый сигнал синхронизации изменяется с Низкого уровня на Высокий уровень, потенциал первой узловой точки дополнительно повышается из-за паразитной емкости между первым электродом и вторым электродом первого переключающего элемента, так что первый переключающий элемент переходит в Открытое состояние. В результате, потенциал выходной узловой точки повышается, и сигнал состояния, указывающий первое состояние, выводится от выходной узловой точки. Разрядный участок выходной узловой точки устанавливает состояние, указанное сигналом состояния, во второе состояние. С другой стороны, если первый сигнал синхронизации изменяется с Низкого уровня на Высокий уровень в том случае, когда первая узловая точка не заряжается, потенциал первой узловой точки повышается незначительно вследствие паразитной емкости между первым электродом и вторым электродом первого переключающего элемента. Каждая бистабильная схема включает в себя первый разрядный участок первой узловой точки для разрядки первой узловой точки. Вторая узловая точка, подключенная к первому электроду второго переключающего элемента, входящего в состав первого разрядного участка первой узловой точки, заряжается на основании третьего сигнала синхронизации и разряжается на основании четвертого сигнала синхронизации. В данном документе, третий сигнал синхронизации опережает по фазе первый сигнал синхронизации. Таким образом, если первый сигнал синхронизации изменяется с Низкого уровня на Высокий уровень в периоде без выбора так, что потенциал первой узловой точки повышается незначительно, второй переключающий элемент, входящий в состав первого разрядного участка первой узловой точки, уже находится в Открытом состоянии. Соответственно, в периоде без выбора, даже если потенциал первой узловой точки повышается, потенциал быстро падает. Следовательно, ток утечки в переключающем элементе, подключенном к выходной узловой точке, становится меньшим, чем в традиционном случае. Таким образом, создается препятствие для того, чтобы излишний электрический ток протекал через линию сканирующего сигнала, что приводит к снижению потребляемой мощности.

Более того, когда первый сигнал синхронизации изменяется с Высокого уровня на Низкий уровень в периоде без выбора, потенциал первой узловой точки падает до потенциала, который ниже, чем потенциал (отрицательного) напряжения источника питания. В данном документе, поскольку время изменения четвертого сигнала синхронизации с Низкого уровня на Высокий уровень, является более ранним, чем время изменения первого сигнала синхронизации с Высокого уровня на Низкий уровень, вторая узловая точка находится в разряженном состоянии, а второй переключающий элемент находится в Закрытом состоянии на момент времени, когда потенциал первой узловой точки падает до потенциала, который ниже, чем потенциал напряжения источника питания. Таким образом, потенциал первой узловой точки не повышается быстро до потенциала напряжения источника питания, а повышается постепенно до потенциала напряжения источника питания. В результате, отрицательное напряжение смещения удовлетворительно прикладывается к первому электроду первого переключающего элемента в дополнение к положительному напряжению смещения в течение периода работы устройства отображения. Следовательно, пороговый сдвиг в первом переключающем элементе становится меньше, чем в традиционном случае. Соответственно, можно сократить размер первого переключающего элемента по сравнению с традиционным случаем, что дает возможность уменьшения размеров в устройстве отображения.

Дополнительно, поскольку четвертый сигнал синхронизации запаздывает по фазе относительно первого сигнала синхронизации, в периоде с выбором, четвертый сигнал синхронизации изменяется с Низкого уровня на Высокий уровень, так что вторая узловая точка разряжается. В данном документе, вторая узловая точка подключается к первому электроду второго переключающего элемента, имеющего второй электрод, подключенный к первой узловой точке. Как описано выше, поскольку период, в котором второй переключающий элемент установлен в Закрытое состояние в периоде с выбором, становится более продолжительным, чем в традиционном случае, создается препятствие для того, чтобы потенциал первой узловой точки падал в период с выбором. Если потенциал первой узловой точки падает в период с выбором, падение сканирующего сигнала задерживается во время перехода от периода с выбором к периоду без выбора. Согласно первому аспекту настоящего изобретения, однако, так как падение потенциала первой узловой точки в периоде с выбором подавляется, сканирующий сигнал падает быстро во время перехода от периода с выбором к периоду без выбора. Таким образом, создается препятствие для появления дефекта отображения из-за того, что падение сканирующего сигнала становится медленным.

Согласно второму аспекту настоящего изобретения, те же самые результаты, что и для первого аспекта настоящего изобретения, могут быть получены при конфигурации, в которой каждый из разрядного участка второй узловой точки, разрядного участка первой узловой точки и зарядного участка первой узловой точки включает в себя переключающий элемент.

Согласно третьему аспекту настоящего изобретения, поскольку вторая узловая точка разряжается в течение периода с выбором, предотвращается падение потенциала первой узловой точки в периоде с выбором. Более того, благодаря разрядке первой узловой точки после окончания периода с выбором, создается препятствие для того, чтобы ток утечки генерировался в первом переключающем элементе после окончания периода с выбором.

Согласно четвертому аспекту настоящего изобретения, схема возбуждения для линий сканирующего сигнала, дающая результаты, которые подобны результатам согласно третьему аспекту настоящего изобретения, реализуется посредством конфигурации, в которой сигналы состояния, выводящиеся от соответствующих бистабильных схем, используются в качестве сигнала сброса на предыдущем каскаде и в качестве установочного сигнала на последующем каскаде.

Согласно пятому аспекту настоящего изобретения, относительно толстая сигнальная линия используется в качестве сигнальной линии, передающей сигнал синхронизации, непосредственно способствующий установке состояния, указанного сигналом состояния, в первое состояние, и относительно тонкая сигнальная линия используется в качестве сигнальной линии, передающей сигнал синхронизации для управления второй узловой точкой. Таким образом, можно уменьшить площадь схемы при сохранении функционирования сдвигового регистра в нормальном режиме.

Согласно шестому аспекту настоящего изобретения, схема возбуждения для линий сканирующего сигнала, дающая результаты, которые подобны результатам согласно третьему аспекту настоящего изобретения, реализуется посредством конфигурации, в которой сигналы состояния, выводящиеся от соответствующих бистабильных схем, используются в качестве сигнала сброса на двух предыдущих каскадах и в качестве установочного сигнала на двух последующих каскадах.

Согласно седьмому аспекту настоящего изобретения, состояние, указанное сигналом состояния, устанавливается во второе состояние на основании сигнала сброса и второго сигнала синхронизации. Таким образом, можно в любое время установить состояние, указанное сигналом состояния, во второе состояние.

Согласно восьмому аспекту настоящего изобретения, состояние, указанное сигналом состояния, дополнительно устанавливается во второе состояние на основании зарядного напряжения второй узловой точки. Таким образом, в периоде без выбора можно надежно поддерживать состояние, указанное сигналом состояния, во втором состоянии.

Согласно девятому аспекту настоящего изобретения, потенциал первой узловой точки поддерживается на Высоком уровне в течение периода с выбором. Таким образом, создается препятствие для того, чтобы потенциал сканирующего сигнала падал в периоде с выбором.

Согласно десятому аспекту настоящего изобретения, с первого по четвертый сигналы синхронизации генерируются относительно просто.

Согласно одиннадцатому аспекту настоящего изобретения, схема возбуждения для линий сканирующего сигнала, дающая результаты, которые подобны результатам согласно первому аспекту настоящего изобретения, реализуется посредством конфигурации, в которой предусматривается две схемы возбуждения для линий сканирующего сигнала.

Согласно двенадцатому аспекту настоящего изобретения, те же самые результаты, что и для одиннадцатого аспекта настоящего изобретения, могут быть получены при конфигурации, в которой нечетные линии сканирующего сигнала и четные линии сканирующего сигнала возбуждаются разными схемами возбуждения для линий сканирующего сигнала.

Согласно тринадцатому аспекту настоящего изобретения, те же самые результаты, что и для одиннадцатого аспекта настоящего изобретения, могут быть получены при конфигурации, в которой каждая линия сканирующего сигнала возбуждается двумя схемами возбуждения для линий сканирующего сигнала.

Согласно четырнадцатому аспекту настоящего изобретения, поскольку в качестве переключающего элемента применяются тонкопленочные транзисторы, сделанные из микрокристаллического кремния, который является относительно невосприимчивым к деградации, можно повысить надежность функционирования сдвигового регистра.

Согласно пятнадцатому аспекту настоящего изобретения, в конфигурации, в которой в качестве переключающего элемента применяются тонкопленочные транзисторы, сделанные из аморфного кремния, ток утечки в первом переключающем элементе становится намного меньше, и подавляется излишнее потребление мощности.

Согласно шестнадцатому аспекту настоящего изобретения, поскольку переключающий элемент (второй переключающий элемент, седьмой переключающий элемент) для разрядки первой узловой точки формируется с использованием тонкопленочного транзистора, имеющего многоканальную структуру, можно предотвратить снижение потенциала первой узловой точки из-за тока утечки в этих переключающих элементах при повышении потенциала первой узловой точки.

Согласно семнадцатому аспекту настоящего изобретения, реализуется устройство отображения, включающее в себя схему возбуждения для линий сканирующего сигнала, дающей результаты, подобные результатам согласно первому аспекту настоящего изобретения.

Согласно восемнадцатому аспекту настоящего изобретения, устройство отображения, дающее результаты, подобные результатам согласно семнадцатому аспекту настоящего изобретения, реализуется при обеспечении уменьшения размера устройства.

Согласно девятнадцатому аспекту настоящего изобретения, реализуется сдвиговый регистр, дающий результаты, подобные результатам согласно первому аспекту настоящего изобретения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

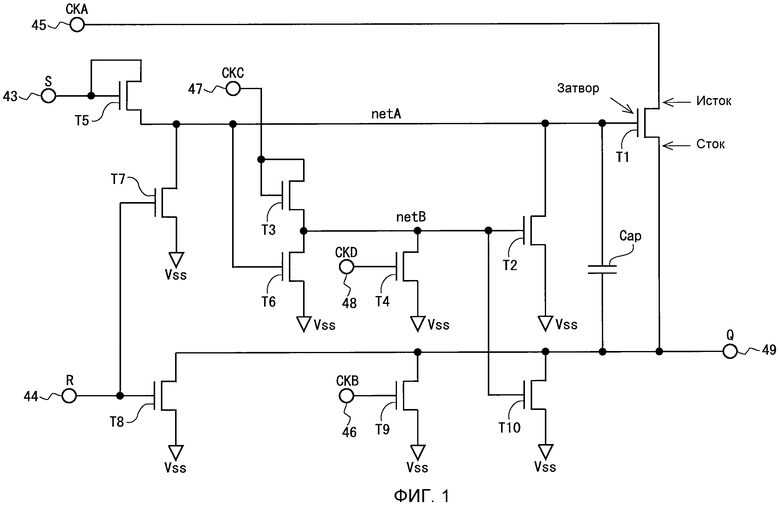

Фиг.1 является принципиальной схемой, демонстрирующей конфигурацию бистабильной схемы, входящей в состав сдвигового регистра в возбудителе затворов жидкокристаллического устройства отображения согласно одному варианту осуществления настоящего изобретения.

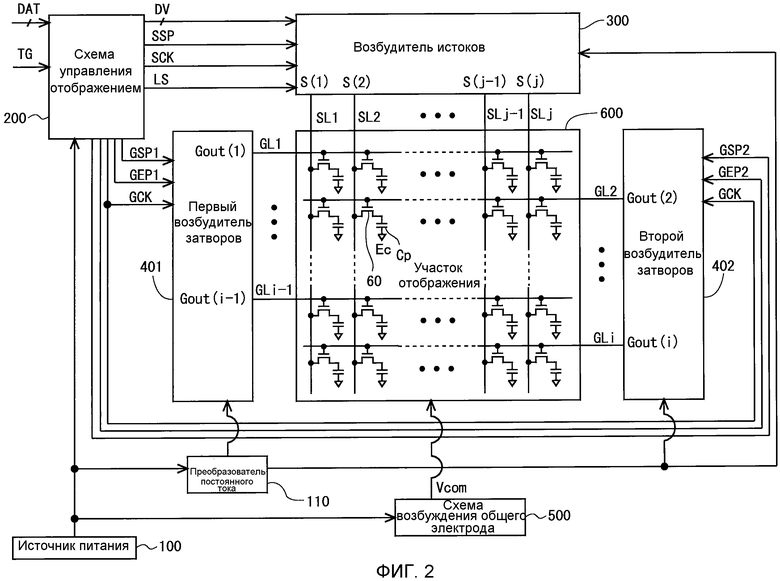

Фиг.2 является структурной схемой, демонстрирующей общую конфигурацию жидкокристаллического устройства отображения согласно варианту осуществления.

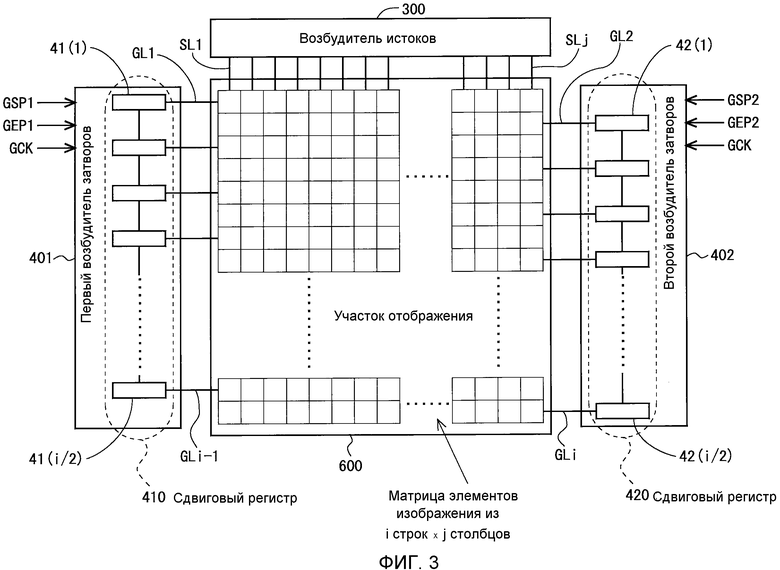

Фиг.3 является структурной схемой для пояснения конфигурации возбудителя затворов, в варианте осуществления.

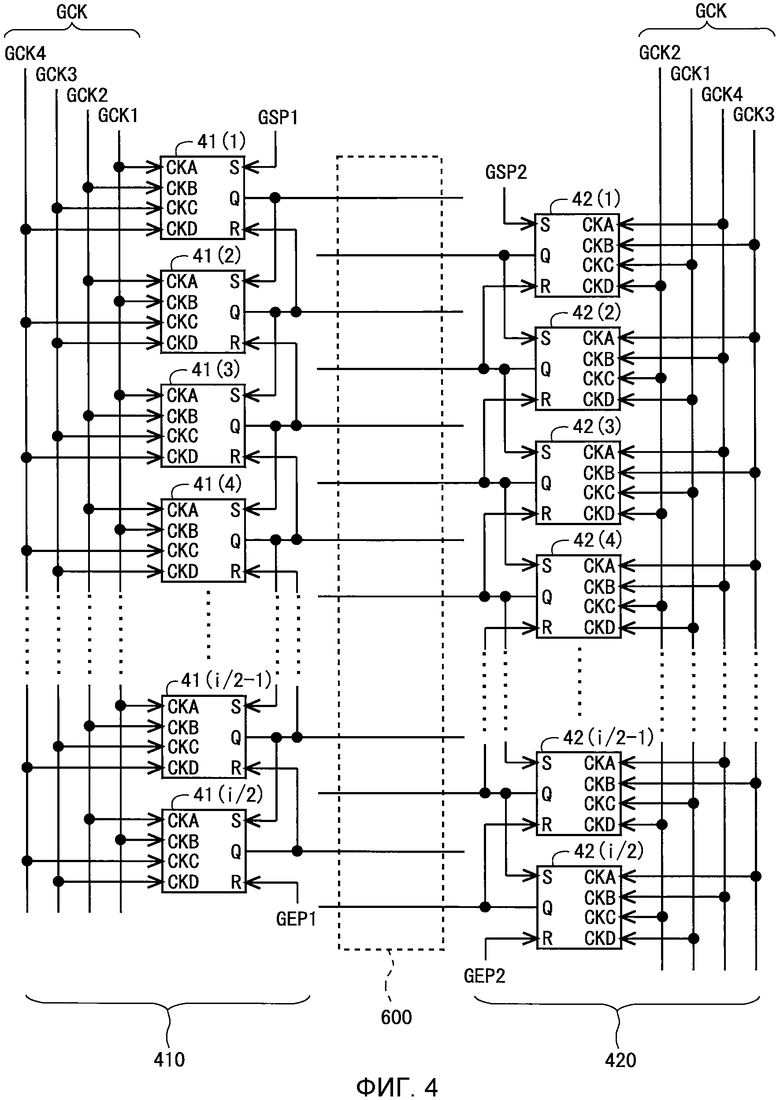

Фиг.4 является структурной схемой, демонстрирующей конфигурацию сдвигового регистра в возбудителе затворов, в варианте осуществления.

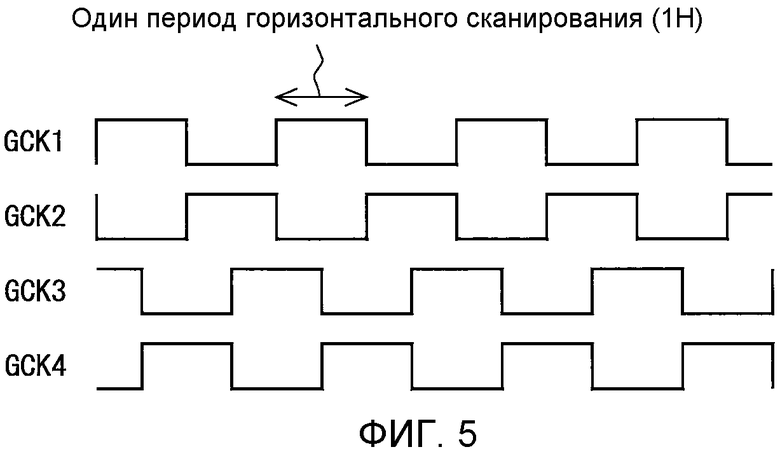

Фиг.5 является диаграммой форм колебаний сигнала, демонстрирующей формы колебаний первого - четвертого сигналов синхронизации затвора, в варианте осуществления.

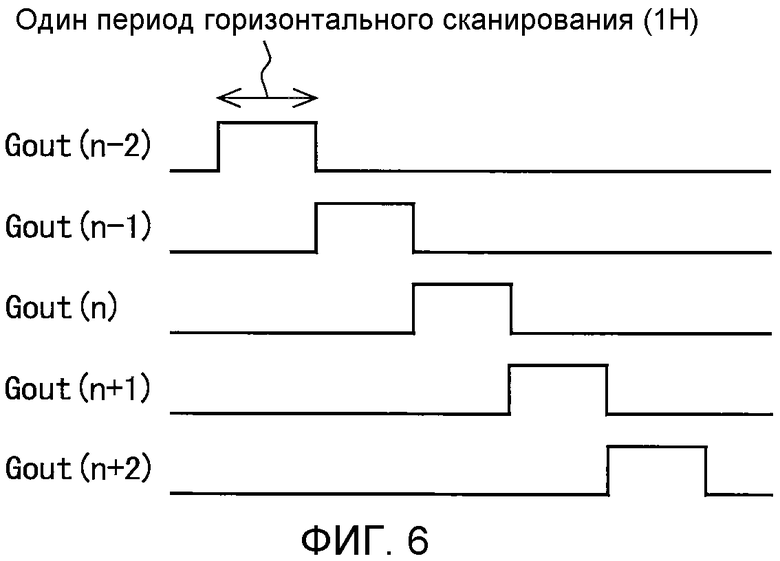

Фиг.6 является диаграммой форм колебаний сигнала, демонстрирующей формы колебаний сканирующих сигналов, в варианте осуществления.

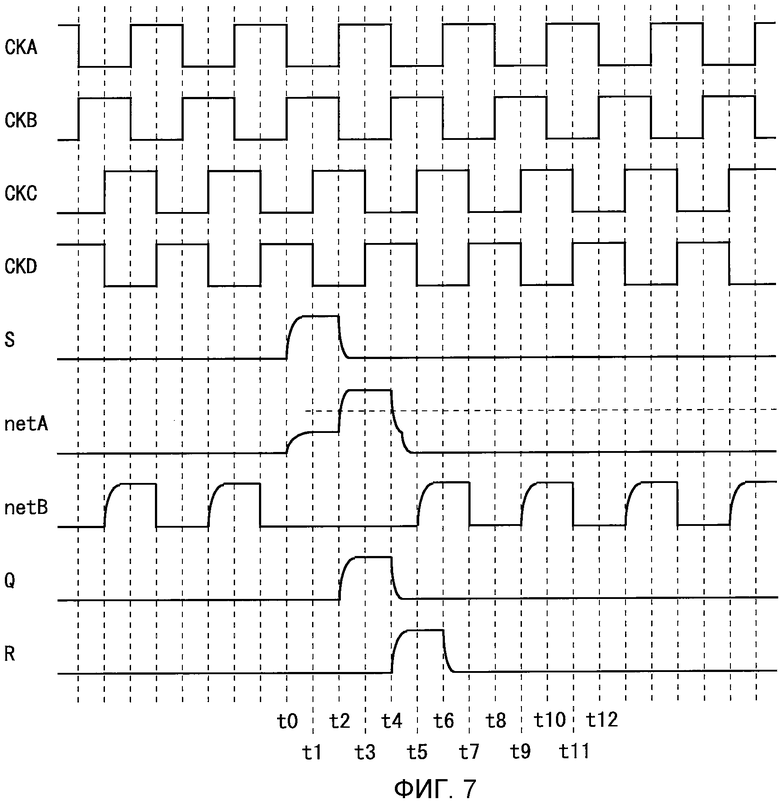

Фиг.7 является диаграммой форм колебаний для пояснения функционирования бистабильной схемы, в варианте осуществления.

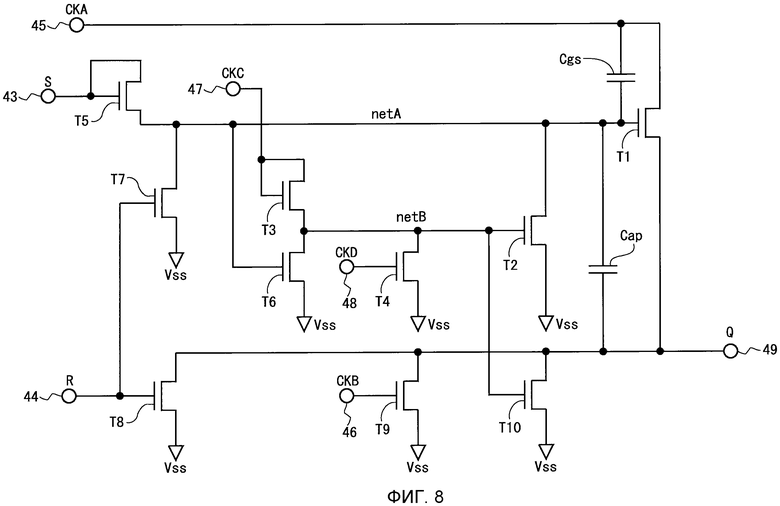

Фиг.8 является принципиальной схемой с учетом паразитной емкостью между затвором и истоком тонкопленочного транзистора T1, в варианте осуществления.

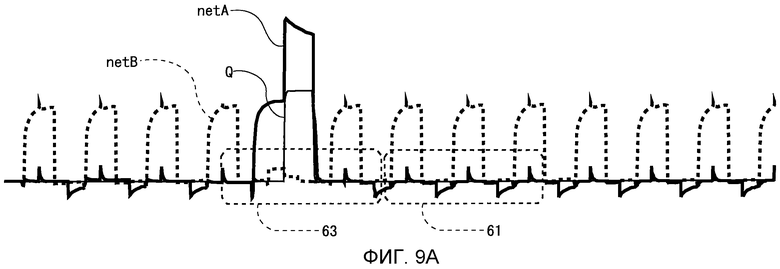

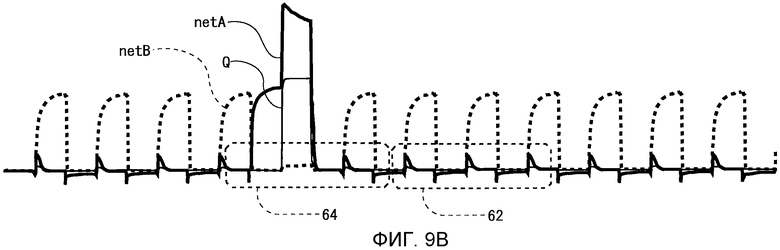

Фиг.9A является диаграммой форм колебаний, демонстрирующей результат моделирования с использованием конфигурации согласно варианту осуществления. Фиг.9B является диаграммой форм колебаний, демонстрирующей результат моделирования с использованием конфигурации согласно традиционному примеру.

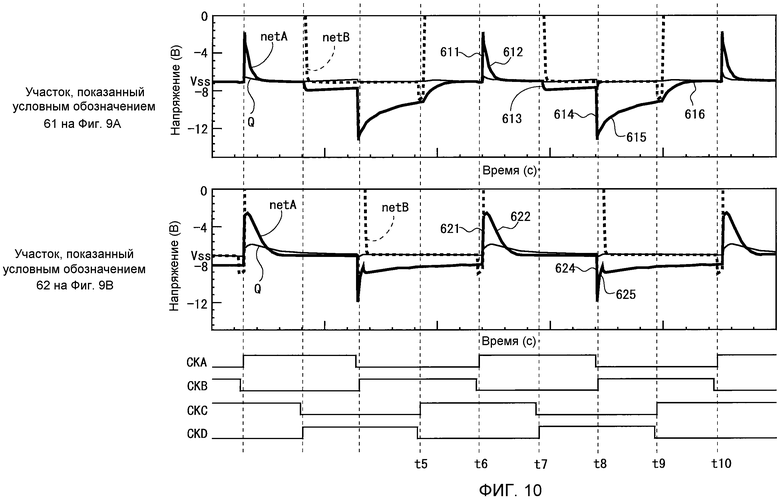

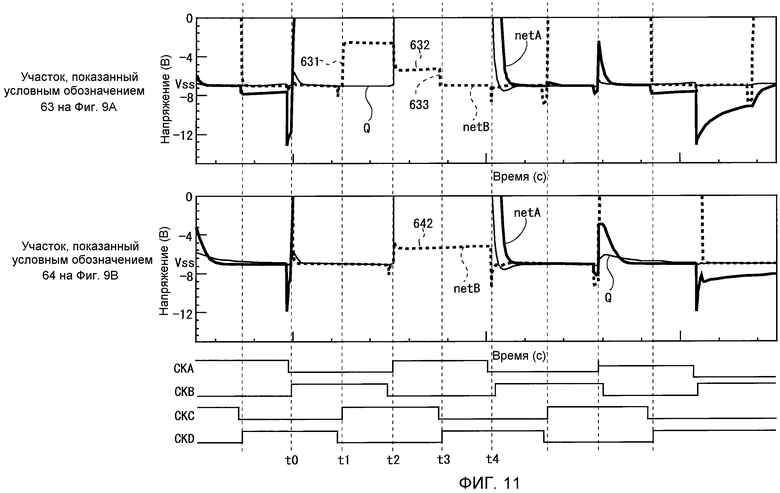

Фиг.10 является частично увеличенным графическим изображением результатов моделирования.

Фиг.11 является частично увеличенным графическим изображением результатов моделирования.

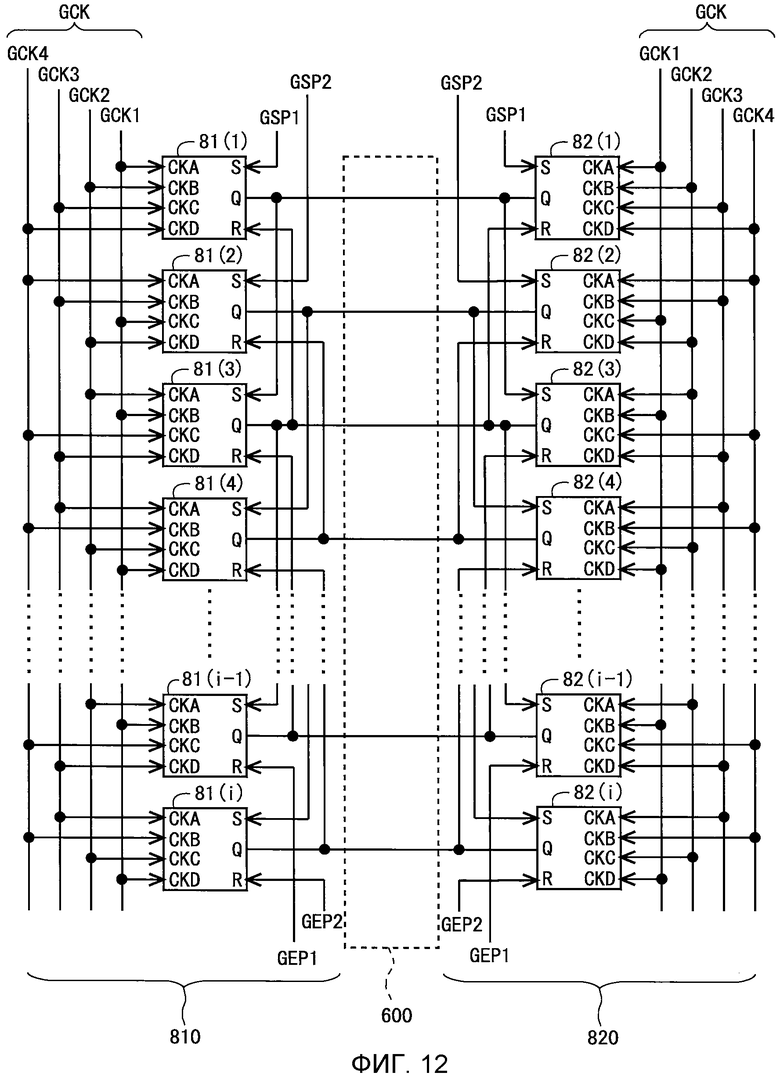

Фиг.12 является структурной схемой, демонстрирующей конфигурацию сдвигового регистра в возбудителе затворов, в модифицированном варианте осуществления.

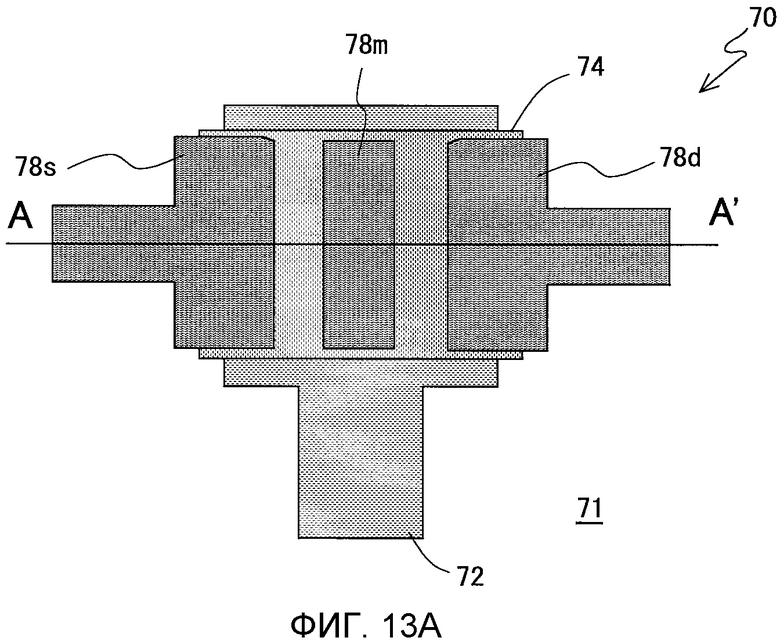

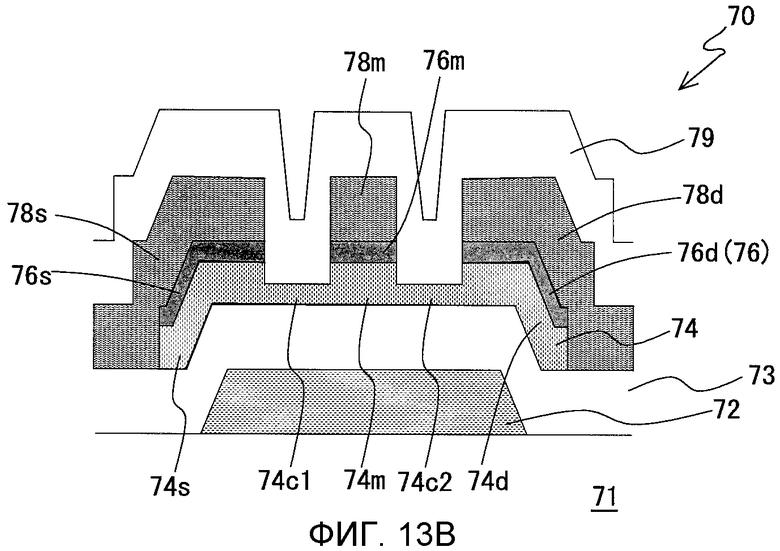

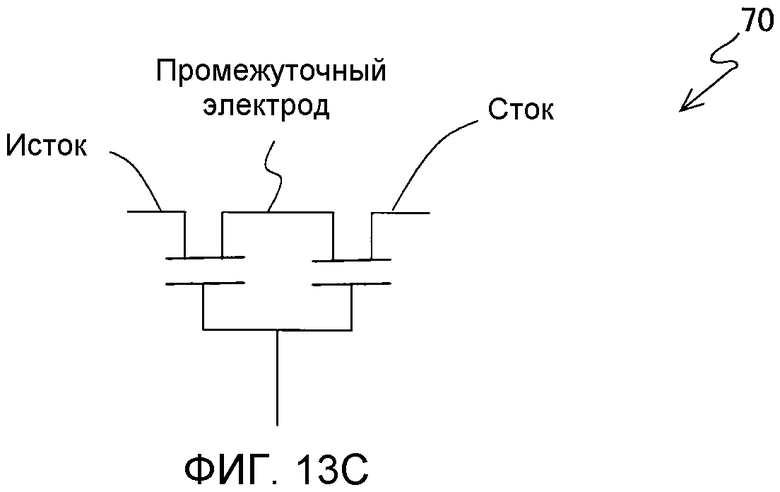

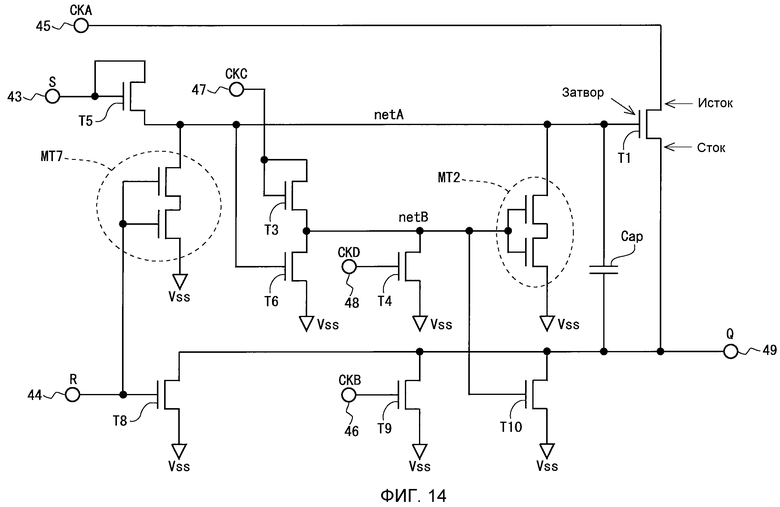

Фиг.13A-13C являются графическими изображениями для пояснения многоканального TFT.

Фиг.14 является принципиальной схемой конфигурации, в которой бистабильная схема согласно варианту осуществления формируется с использованием многоканального TFT.

Фиг.15 является принципиальной схемой, демонстрирующей пример конфигурации, соответствующий одному каскаду в сдвиговом регистре, входящем в состав традиционного возбудителя затворов.

Фиг.16 является диаграммой форм колебаний, демонстрирующей функционирование в традиционном примере.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Ниже будет описан один вариант осуществления настоящего изобретения со ссылкой на прилагаемые чертежи. В последующем описании, в отношении тонкопленочного транзистора, контакт затвора (электрод затвора) соответствует первому электроду, контакт истока (электрод истока) соответствует второму электроду, и контакт стока (электрод стока) соответствует третьему электроду.

<1. Общая Конфигурация и Функционирование>

Фиг.2 является структурной схемой, демонстрирующей общую конфигурацию жидкокристаллического устройства отображения с активной матрицей согласно одному варианту осуществления настоящего изобретения. Как показано на Фиг.2, это жидкокристаллическое устройство отображения включает в себя источник 100 питания, преобразователь 110 постоянного тока, схему 200 управления отображением, возбудитель 300 истоков (схему возбуждения для линий видеосигнала), первый возбудитель 401 затворов (первую схему возбуждения для линий сканирующего сигнала), второй возбудитель 402 затворов (вторую схему возбуждения для линий сканирующего сигнала), схему 500 возбуждения общего электрода и участок 600 отображения. Как правило, участок 600 отображения, а также первый и второй возбудитель 401 и 402 затворов, каждый из которых представляет собой схему возбуждения, формируются на единой подложке, то есть формируются монолитно.

Участок 600 отображения включает в себя множество (j) линий шин истоков (линий видеосигналов) SL1-SLj, множество (i) линий шин затворов (линий сканирующего сигнала) GL1-GLi и множество (i×j) участков формирования элементов изображения, предоставленных в соответствии с пересечениями между линиями SL1-SLj шин истоков и линиями GL1-GLi шин затворов, соответственно. Среди "i" линий GL1-GLi шин затворов, нечетные линии GL1, GL3, … и GLi-1 шин затворов распространяются от первого возбудителя 401 затворов, а четные линии GL2, GL4, …, и GLi шин затворов распространяются от второго возбудителя 402 затворов.

Множество участков формирования элементов изображения располагаются в форме матрицы для формирования массива элементов изображения. Каждый участок формирования элементов изображения включает в себя тонкопленочный транзистор (TFT) 60, который представляет собой переключающий элемент, имеющий контакт затвора, подключенный к линии шины затвора, проходящей через соответствующее пересечение, и контакт истока, подключенный к линии шины истока, проходящей через это пересечение, электрод элемента изображения, подключенный к контакту стока тонкопленочного транзистора 60, общий электрод Ec, который является противоэлектродом, предоставленный в совместное пользование для множества участков формирования элементов изображения, и жидкокристаллический слой, предоставленный в совместное пользование для множества участков формирования элементов изображения и удерживаемый между электродом элемента изображения и общим электродом Ec. Емкость жидких кристаллов, которая будет образовываться электродом элемента изображения и общим электродом Ec, формирует емкость Cp элемента изображения. Обычно, предусматривается вспомогательная емкость параллельно емкости жидких кристаллов, чтобы емкость Cp элемента изображения надежно удерживала напряжение. Однако, поскольку вспомогательная емкость не связана непосредственно с настоящим изобретением, его описание и иллюстрация приводиться не будет.

Источник 100 питания подает предварительно заданное напряжение источника питания на преобразователь 110 постоянного тока, на схему 200 управления отображением и на схему 500 возбуждения общего электрода. Преобразователь 110 постоянного тока генерирует предварительно заданное напряжение постоянного тока из напряжения источника питания для того, чтобы работали возбудитель 300 истоков, первый возбудитель 401 затворов и второй возбудитель 402 затворов, и подает это напряжение постоянного тока на возбудитель 300 истоков, на первый возбудитель 401 затворов и на второй возбудитель 402 затворов. Схема 500 возбуждения общего электрода подает предварительно заданный потенциал Vcom на общий электрод Ec.

Схема 200 управления отображением принимает передаваемый извне сигнал DAT изображения и передаваемую извне группу TG сигналов синхронизации, как, например, сигнал строчной синхронизации, сигнал кадровой синхронизации и т.п., и выводит цифровой видеосигнал DV, а также сигнал SSP пускового импульса истока, сигнал SCK синхронизации истока, стробирующий сигнал LS фиксации, первый сигнал GSP1 пускового импульса затвора, первый сигнал GEP1 конечного импульса затвора, второй сигнал GSP2 пускового импульса затвора, второй сигнал GEP2 конечного импульса затвора и сигнал GCK синхронизации затвора, которые предназначены для управления отображением изображения на участке 600 отображения.

Возбудитель 300 истоков принимает цифровой видеосигнал DV, сигнал SSP пускового импульса истока, сигнал SCK синхронизации истока и стробирующий сигнал LS фиксации, каждый из которых выводится от схемы 200 управления отображением, и прикладывает видеосигналы S(1)-S(j) возбуждения к линиям SL1-SLj шин истоков, соответственно.

В этом варианте осуществления, возбудитель затворов разделяется на первый возбудитель 401 затворов для возбуждения нечетных линий GL1, GL3, …, и GLi-1 шин затворов, и второй возбудитель 402 затворов для возбуждения четных линий GL2, GL4, …, и GLi шин затворов. Первый возбудитель 401 затворов неоднократно прикладывает активные сканирующие сигналы Gout(1), Gout(3), …, и Gout(i-1) к нечетным линиям GL1, GL3, … и GLi-1 шин затворов, на основании первого сигнала GSP1 пускового импульса затвора, первого сигнала GEP1 конечного импульса затвора и сигнала GCK синхронизации затвора, каждый из которых выводится от схемы 200 управления отображением, для одного периода вертикального сканирования, определяемого как цикл. Аналогично, второй возбудитель 402 затворов неоднократно прикладывает активные сканирующие сигналы Gout(2), Gout(4), …, и Gout(i) к четным линиям GL2, GL4, …, и GLi шин затворов, на основании второго сигнала GSP2 пускового импульса затвора, второго сигнала GEP2 конечного импульса затвора и сигнала GCK синхронизации затвора, каждый из которых выводится от схемы 200 управления отображением, для одного периода вертикального сканирования, определяемого как цикл. Подробное описание этих возбудителей затворов будет дано позже.

Как описано выше, видеосигналы S(1)-S(j) возбуждения прикладываются к линиям SL1-SLj шин истоков, соответственно, а сканирующие сигналы Gout(1)-Gout(i) прикладываются к линиям GL1-GLi шин затворов, соответственно, так что изображение, основанное на передаваемом извне сигнале DAT изображения, отображается на участке 600 отображения.

<2. Конфигурация и Функционирование Возбудителя Затворов>

Что касается конфигурации и функционирования возбудителя затворов в этом варианте осуществления, далее будут описаны общие принципы, со ссылкой на Фиг.3 - Фиг.6. Как показано на Фиг.3, первый возбудитель 401 затворов формируется с использованием многокаскадного сдвигового регистра 410, а второй возбудитель 402 затворов формируется с использованием многокаскадного сдвигового регистра 420. Матрица элементов изображения (“i” строк × “j” столбцов) формируется на участке 600 отображения. Соответствующие каскады сдвигового регистра 410 находятся во взаимно-однозначном соответствии с нечетными строками в матрице элементов изображения, а соответствующие каскады сдвигового регистра 420 находятся во взаимно-однозначном соответствии с четными строками в матрице элементов изображения. Более того, каждый из каскадов сдвиговых регистров 410 и 420 представляет собой бистабильную схему, которая переходит в одно из двух состояний (первое состояние и второе состояние) в каждый момент времени, и выводит сигнал, указывающий соответствующее состояние (в дальнейшем, именуется как “сигнал состояния”). Таким образом, сдвиговый регистр 410 формируется с использованием “i/2” бистабильных схем 41(1)-41(i/2), а сдвиговый регистр 420 формируется с использованием “i/2” бистабильных схем 42(1)-42(i/2). В этом варианте осуществления, когда бистабильная схема находится в первом состоянии, от бистабильной схемы выводится сигнал состояния на Высоком уровне (уровень H). С другой стороны, когда бистабильная схема находится во втором состоянии, от бистабильной схемы выводится сигнал состояния на Низком уровне (уровень L).

Фиг.4 является структурной схемой, демонстрирующей конфигурацию сдвиговых регистров 410 и 420 в возбудителе затворов. Как описано выше, сдвиговый регистр 410 формируется с использованием “i/2” бистабильных схем 41(1)-41(i/2), а сдвиговый регистр 420 формируется с использованием “i/2” бистабильных схем 42(1)-42(i/2). Каждая бистабильная схема обеспечивается входными контактами для приема четырех сигналов синхронизации, CKA (в дальнейшем, именуется как “первый синхроимпульс”), CKB (в дальнейшем, именуется как “второй синхроимпульс”), CKC (в дальнейшем, именуется как “третий синхроимпульс”) и CKD (в дальнейшем, именуется как “четвертый синхроимпульс”), входным контактом для приема установочного сигнала S, вводом для приема сигнала R сброса и выходным контактом для вывода сигнала Q состояния.

На сдвиговый регистр 410 в первом возбудителе 401 затворов подаются, от схемы 200 управления отображением, четыре сигнала синхронизации, GCK1 (в дальнейшем, именуется как “первый сигнал синхронизации возбудителя”), GCK2 (в дальнейшем, именуется как “второй сигнал синхронизации возбудителя”), GCK3 (в дальнейшем, именуется как “третий сигнал синхронизации возбудителя”) и GCK4 (в дальнейшем, именуется как “четвертый сигнал синхронизации возбудителя”), каждый из которых выполняет функции сигнала GCK синхронизации затвора, первый сигнал GSP1 пускового импульса затвора, и первый сигнал GEP1 конечного импульса затвора. На сдвиговый регистр 420 во втором возбудителе 402 затворов подаются, от схемы 200 управления отображением, первый сигнал GCK1 синхронизации возбудителя, второй сигнал GCK2 синхронизации возбудителя, третий сигнал GCK3 синхронизации возбудителя, четвертый сигнал GCK4 синхронизации возбудителя, второй сигнал GSP2 пускового импульса затвора и второй сигнал GEP2 конечного импульса затвора.

Как показано на Фиг.5, первый сигнал GCK1 синхронизации возбудителя и второй сигнал GCK2 синхронизации возбудителя сдвинуты по фазе на 180 градусов (период, соответствующий одному периоду горизонтального сканирования) по отношению друг к другу, а также третий сигнал GCK3 синхронизации возбудителя и четвертый сигнал GCK4 синхронизации возбудителя сдвинуты по фазе на 180 градусов по отношению друг к другу. Третий сигнал GCK3 синхронизации возбудителя опережает по фазе на 90 градусов первый сигнал GCK1 синхронизации возбудителя. Каждый, с первого по четвертый, сигнал GCK1-4 синхронизации возбудителя, переходит в состояние Высокого уровня (уровень H) в каждом периоде горизонтального сканирования.

В этом варианте осуществления, сигналами, которые подаются на входные контакты каждого каскада (каждой бистабильной схемы) в сдвиговом регистре 410, являются следующие. В первом каскаде 41(1), первый сигнал GCK1 синхронизации возбудителя подается в качестве первого синхроимпульса CKA, второй сигнал GCK2 синхронизации возбудителя подается в качестве второго синхроимпульса CKB, третий сигнал GCK3 синхронизации возбудителя подается в качестве третьего синхроимпульса CKC и четвертый сигнал GCK4 синхронизации возбудителя подается в качестве четвертого синхроимпульса CKD. Во втором каскаде 41(2), второй сигнал GCK2 синхронизации возбудителя подается в качестве первого синхроимпульса CKA, первый сигнал GCK1 синхронизации возбудителя подается в качестве второго синхроимпульса CKB, четвертый сигнал GCK4 синхронизации возбудителя подается в качестве третьего синхроимпульса CKC и третий сигнал GCK3 синхронизации возбудителя подается в качестве четвертого синхроимпульса CKD. В третьем каскаде и в последующих каскадах, конфигурации, аналогичные конфигурациям от первого каскада до второго каскада, повторяются каждые два каскада. В первом каскаде 41(1), кроме того, первый сигнал GSP1 пускового импульса затвора подается в качестве установочного сигнала S. Во втором каскаде 41(2) и в последующих каскадах, сигнал Q состояния на предыдущем каскаде подается в качестве установочного сигнала S. В каскадах от первого до (i/2-1)-го, дополнительно, сигнал Q состояния на последующем каскаде подается в качестве сигнала R сброса. В (i/2)-м каскаде, первый сигнал GEP1 конечного импульса затвора подается в качестве сигнала R сброса.

Сигналами, которые подаются на входные контакты каждого каскада (каждой бистабильной схемы) в сдвиговом регистре 420, являются следующие. В первом каскаде 42(1), четвертый сигнал GCK4 синхронизации возбудителя подается в качестве первого синхроимпульса CKA, третий сигнал GCK3 синхронизации возбудителя подается в качестве второго синхроимпульса CKB, первый сигнал GCK1 синхронизации возбудителя подается в качестве третьего синхроимпульса CKC и второй сигнал GCK2 синхронизации возбудителя подается в качестве четвертого синхроимпульса CKD. Во втором каскаде 42(2), третий сигнал GCK3 синхронизации возбудителя подается в качестве первого синхроимпульса CKA, четвертый сигнал GCK4 синхронизации возбудителя подается в качестве второго синхроимпульса CKB, второй сигнал GCK2 синхронизации возбудителя подается в качестве третьего синхроимпульса CKC, и первый сигнал GCK1 синхронизации возбудителя подается в качестве четвертого синхроимпульса CKD. В третьем каскаде и в последующих каскадах, конфигурации, аналогичные конфигурациям от первого каскада до второго каскада, повторяются каждые два каскада. В первом каскаде 42(1), кроме того, второй сигнал GSP2 пускового импульса затвора подается в качестве установочного сигнала S. Во втором каскаде 42(2) и в последующих каскадах, сигнал Q состояния на предыдущем каскаде подается в качестве установочного сигнала S. В каскадах от первого до (i/2-1)-го, дополнительно, сигнал Q состояния на последующем каскаде подается в качестве сигнала R сброса. В (i/2)-м каскаде, второй сигнал GEP2 конечного импульса затвора подается в качестве сигнала R сброса.

Когда первый сигнал GSP1 пускового импульса затвора подается в качестве установочного сигнала S на первый каскад 41(1) в сдвиговом регистре 410, импульс, содержащийся в первом сигнале GSP1 пускового импульса затвора (этот импульс содержится в сигнале Q состояния, выводимом от каждого каскада), переносится последовательно от первого каскада 41(1) до (i/2)-ого каскада 41(i/2), на основании от первого до четвертого сигналов GCK1-4 синхронизации возбудителя. Затем, в ответ на передачу этого импульса, сигнал Q состояния, выводимый от соответствующих каскадов 41(1)-(i/2) последовательно переходит на Высокий уровень. Далее, сигналы Q состояния, выводимые от соответствующих каскадов 41(1)-(i/2), подаются в качестве сканирующих сигналов на нечетные линии GL1, GL3, … и GLi-1 шин затворов, соответственно.

Когда второй сигнал GSP2 пускового импульса затвора подается в качестве установочного сигнала S на первый каскад 42(1) в сдвиговом регистре 420, импульс, содержащийся во втором сигнале GSP2 пускового импульса затвора, переносится последовательно от первого каскада 42(1) (i/2)-ого каскада 42(i/2), на основании от первого до четвертого сигналов GCK1-4 синхронизации возбудителя. Затем, в ответ на передачу этого импульса, сигнал Q состояния, выводимый от соответствующих каскадов 42(1)-(i/2), последовательно переходит на Высокий уровень. Далее, сигналы Q состояния, выводимые от соответствующих каскадов 42(1)-(i/2), подаются в качестве сканирующих сигналов на четные линии GL2, GL4, …, и GLi шин затворов, соответственно.

Как показано на Фиг.6, сканирующие сигналы, которые последовательно переходят на Высокий уровень каждый период горизонтального сканирования, подаются на линии шин затворов на участке 600 отображения, как описано выше.

Что касается конфигурации сдвигового регистра 410, показанного на Фиг.4, относительно толстая сигнальная линия используется в качестве сигнальной линии, передающей первый сигнал GCK1 синхронизации возбудителя, и сигнальной линии, передающей второй сигнал GCK2 синхронизации возбудителя, и относительно тонкая сигнальная линия используется в качестве каждой сигнальной линии, передающей третий сигнал GCK3 синхронизации возбудителя, и сигнальной линии, передающей четвертый сигнал GCK4 синхронизации возбудителя. Кроме того, что касается конфигурации сдвигового регистра 420, показанного на Фиг.4, относительно толстая сигнальная линия используется в качестве сигнальной линии, передающей третий сигнал GCK3 синхронизации возбудителя, и сигнальной линии, передающей четвертый сигнал GCK4 синхронизации возбудителя, и относительно тонкая сигнальная линия используется в качестве каждой сигнальной линии, передающей первый сигнал GCK1 синхронизации возбудителя, и сигнальной линии, передающей второй сигнал GCK2 синхронизации возбудителя. Другими словами, относительно толстая сигнальная линия используется в качестве сигнальной линии, передающей сигнал синхронизации, непосредственно способствующий повышению потенциала сканирующего сигнала, и относительно тонкая сигнальная линия используется в качестве сигнальной линии, передающей сигнал синхронизации для управления функционированием упоминаемого позднее тонкопленочного транзистора (который будет описан ниже), входящим в состав каждой бистабильной схемы.

<3. Конфигурация Бистабильной Схемы>

Фиг.1 является принципиальной схемой, демонстрирующей конфигурацию бистабильной схемы, входящей в состав каждого из описанных выше сдвиговых регистров 410 и 420 (конфигурацию, соответствующую одному каскаду в каждом из сдвиговых регистров 410 и 420). Как показано на Фиг.1, бистабильная схема включает в себя 10 тонкопленочных транзисторов T1 (первый переключающий элемент), T2 (второй переключающий элемент), T3 (третий переключающий элемент), T4 (четвертый переключающий элемент), T5 (пятый переключающий элемент), T6 (шестой переключающий элемент), T7 (седьмой переключающий элемент), T8 (восьмой переключающий элемент), T9 (девятый переключающий элемент) и T10 (десятый переключающий элемент), и конденсатор Cap. Кроме того, бистабильная схема имеет шесть входных контактов 43-48, и один выходной контакт (выходную узловую точку) 49. В данном документе, входной контакт, который принимает установочный сигнал S, обозначен условным обозначением 43, входной контакт, который принимает сигнал R сброса, обозначен условным обозначением 44, входной контакт, который принимает первый синхроимпульс CKA, обозначен условным обозначением 45, входной контакт, который принимает второй синхроимпульс CKB, обозначен условным обозначением 46, входной контакт, который принимает третий синхроимпульс CKC, обозначен условным обозначением 47, входной контакт, который принимает четвертый синхроимпульс CKD, обозначен условным обозначением 48, и выходной контакт, который выводит сигнал Q состояния, обозначен условным обозначением 49. В последующем описании приводится взаимосвязь соединений между составляющими элементами в бистабильной схеме.

Контакт затвора тонкопленочного транзистора T1, контакт истока тонкопленочного транзистора T2, контакт истока тонкопленочного транзистора T5, контакт затвора тонкопленочного транзистора T6, и контакт истока тонкопленочного транзистора T7 соединяются друг с другом. В данном документе, область (монтажной схемы), где эти элементы соединяются друг с другом, именуется как “netA” (первая узловая точка), для удобства описания.

Контакт затвора тонкопленочного транзистора T2, контакт стока тонкопленочного транзистора T3, контакт истока тонкопленочного транзистора T4, контакт истока тонкопленочного транзистора T6 и контакт затвора тонкопленочного транзистора T10 соединяются друг с другом. В данном документе, область (монтажной схемы), где эти элементы соединяются друг с другом, именуется как “netB” (вторая узловая точка), для удобства описания.

В тонкопленочном транзисторе T1, контакт затвора подключается к netA, контакт истока подключается к входному контакту 45, и контакт стока подключается к выходному контакту 49. В тонкопленочном транзисторе T2, контакт затвора подключается к netB, контакт истока подключается к netA, и контакт стока подключается к напряжению Vss источника питания. В тонкопленочном транзисторе T3, контакт затвора и контакт истока подключаются к входному контакту 47, и контакт стока подключается к netB. В тонкопленочном транзисторе T4, контакт затвора подключается к входному контакту 48, контакт истока подключается к netB, и контакт стока подключается к напряжению Vss источника питания. В тонкопленочном транзисторе T5, контакт затвора и контакт стока подключаются к входному контакту 43 (т.е., устанавливают диодное соединение), и контакт истока подключается к netA.

В тонкопленочном транзисторе T6, контакт затвора подключается к netA, контакт истока подключается к netB, и контакт стока подключается к напряжению Vss источника питания. В тонкопленочном транзисторе T7, контакт затвора подключается к входному контакту 44, контакт истока подключается к netA, и контакт стока подключается к напряжению Vss источника питания. В тонкопленочном транзисторе T8, контакт затвора подключается к входному контакту 44, контакт истока подключается к выходному контакту 49, и контакт стока подключается к напряжению Vss источника питания. В тонкопленочном транзисторе T9, контакт затвора подключается к входному контакту 46, контакт истока подключается к выходному контакту 49, и контакт стока подключается к напряжению Vss источника питания. В тонкопленочном транзисторе T10, контакт затвора подключается к netB, контакт истока подключается к выходному контакту 49, и контакт стока подключается к напряжению Vss источника питания. В конденсаторе Cap, один конец подключается к netA, а другой конец подключается к выходному контакту 49.

В последующем описании приводятся функции соответствующих составляющих элементов в бистабильной схеме. Тонкопленочный транзистор T1 подает потенциал первого синхроимпульса CKA на выходной контакт 49, когда потенциал netA находится на Высоком уровне. Тонкопленочный транзистор T2 устанавливает потенциал netA на Низкий уровень, когда потенциал netB находится на Высоком уровне. Тонкопленочный транзистор T3 устанавливает потенциал netB на Высокий уровень, когда третий синхроимпульс CKC находится на Высоком уровне. Тонкопленочный транзистор T4 устанавливает потенциал netB на Низкий уровень, когда четвертый синхроимпульс CKD находится на Высоком уровне. При этом, благодаря установке потенциала netB на Низкий уровень посредством тонкопленочного транзистора T4, предотвращается приложение напряжения смещения к каждому из тонкопленочных транзисторов T2 и T10 в течение длительного периода времени. В результате, предотвращается сбой выполнения тонкопленочными транзисторами T2 и T10 функций переключателя из-за повышения порогового напряжения тонкопленочного транзистора. Тонкопленочный транзистор T5 повышает потенциал netA при поступлении установочного сигнала S на Высоком уровне.