(54) КОММУТАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная стабилизирующая система электропитания | 1987 |

|

SU1444736A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| Устройство для сопряжения ЭВМ с каналом передачи данных | 1989 |

|

SU1647580A1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| Устройство для контроля каналов записи аппарата магнитной записи | 1986 |

|

SU1411818A1 |

| Многоканальный коммутатор аналоговых сигналов | 1988 |

|

SU1598149A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Цифровой измеритель отношения временных интервалов | 1987 |

|

SU1442970A1 |

| Устройство для приема информации | 1988 |

|

SU1552216A1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

Иэобретенле относится к коммута ционной технике.

Известны коммутаторы, содержащие счетчики, дешифратор, генераторы, триггер, блок сравнения и элемент задержки 1.

К недостаткам известных устройств относится низкое быстродействие.

Наиболее близким техническим решением к предлагаемому является коммутатор, содержащий счетчик каналов, счетный вход которого соединен с выходом тактового генератора, информационные входы подключены к входным шинам, а выходы соединены через дешифратор с группой выходных шин и непосредственно с первыми входами блока сравнения, вторые входы которого подключены к выходам счетчика импульсов, а также элемент задержки И триггер, единичный выход которого соединен с входом запуска высокочастотного генератора 2.

К недостаткам известного устройства относится низкое быстродействие,

Цель изобретения - повышение быстродействия коммутатора.

Указанная, цель достигается тем, что в коммутатор, содержащий счетчик каналов, счетный вход которого соединен с выходом тактового генератора, информационные входы подключены к входным шинам, а выходы соединены через дешифратор с группой выходных шин и непосредственно с первыми входами блока сравнения, вторые входы которого подключены к выходам счетчика импульсов, а также элемент задержки и триггер, единичный выход

10 которого соединен с входом запуска высокочастотного генератора, введены два формирователя, два элемента ИЛИ, четыре элемента Н и инвертор, вход которого соединен х; выходом нулево15го канала дешифратора и первым входом первого элемента И, а выход подключен к первому входу второго элемента И, второй вход которого соединен с выходом тактового генератора,

20 вторым входом первого элемента И и первым входом первого элемента ИЛИ, третий вход - с третьим входом первого элемента И, первым выходом блока сравнения и нулевым входом триг25 гера, а выход подключен к первому входу второго элемента ИЛИ, второй вход которого через первый формирователь соединен с выходом первого элемента И, первой выходной шиной и

30 входом сброса счетчика импульсов.

а выход подключен к единичному входу триггера, нулевой выход которого соединен с вторым входом первого элемента ИЛИ, выход которого через второй формирователь подключен к входу элемента задержки, выход которого соединен с второй выходной шиной, при этом второй и третий выходы блока сравнения подключены к первым входам соответственно третьего и четвертого элементов И, вторые входы которых объединены и соединены с выходом высокочастотного генератора, выход третьего элемента И подключен к третьей выходной шине и вычитающему входу счетчика импульсов, а выход четвертого элемента И - к четвертой выходной шине и суммирующему входу счетчика импульсов.

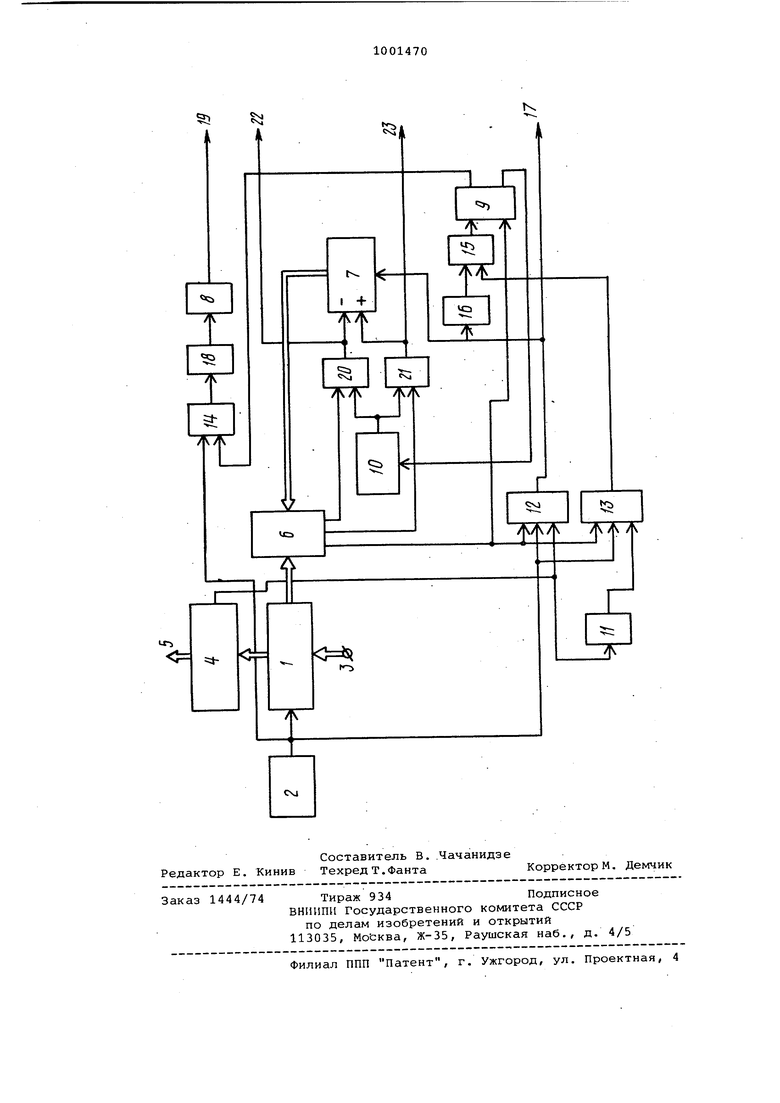

На чертеже представлена функциональная схема коммутатора.

Коммутатор содержит счетчик 1 каналов, счетный вход которого соединен с выходом тактового генератора 2, информационные входы подключены к входным шинам 3, а выходы соединены через дешифратор 4 с группой выходных шин 5 и непосредственно с первыми входами блока б сравнения, вторые входы которого подключены к выходам счетчика 7 импульсов, элемент 8 задержки, триггер 9, единичный выход которого соединен с входом запуска высокочастотного генератора 10,инвертор 11, вход которого соединен с выходом нулевого канала дешифратора 4 и первым входом элемента Н 12, а выход подключен к первому входу элемента И 13, второй вход которого соединен с выходом тактового генератора 2, вторым входом элемента И 12 и первым входом элемента ИЛИ 14, третий вход - с третьим входом элемента И 12, первым выходом блока б сравнения и нулевым входом триггера.9, а выход подключен к первому входу элемента ИЛИ 15, второй вход которого через формирователь 16 соединен с выходом элемента И 12, выходной шиной 17 и входом сброса счетчика 7 импульсов, а выход подключен к единичному входу триггера 9, нулевой выход которого соединен с вторым входом элемента ИЛИ 14, -выход которого через формирователь 18 подключен к входу элемента В задержки, выход которого соединен с выходной шиной 19, второй и третий выходы блока б сравнения подключены к первым входам соответственно элементов И 20 и 21,вторые входы которых объединены и соединены с выходом высокочастотного генератора 10, выход эле-, мента И 20 подключен к выходной шине 22 и вычитающему входу счетчика 7 импульсов, а выход элемента И 21 к ВЫХОДНОЙ шине 23 и суммирующему входу счетчика 7 импульсов.

Коммутатор работает следующим oб разом.

При централизованной и выносной коммутации обеспечиваются адресный и циклический режимы работы. Перед началом работы производится начальная установка счетчика 1 каналов в положение, соответствующее первому номеру канала в цикле или выбранному номеру канала в адресном режиме. Дешифратор 4 преобразует код счетчика 1 каналов Ъ управляющие сигналы на включение определенного канала при централизованной коммутации. Переключение каналов осуществляется по импульсам тактового генератора 2, поступающим на счетный вход счетчика 1 каналов. При выносной коммутации выходной код счетчика 1 каналов преобразуется в число-импульсный и с выхода высокочастотного генератора 10 определенное число импульсов поступает в выносной коммутатор, где устанавливает его счетчик каналов в положение, соответствующее, номеру выбранного канала, коммутатор вырабатывает сигнал Сброс, производящи сброс счетчика 7 импульсов и одновременно поступающий в выносной коммутатор для сброса его счетчика каналов , что обеспечивает синхронную работу этих устройств. При работе выносного коммутатора сигнал Сброс возникает при включении питания для обеспечения синхронизации в начале работы, а затем в процессе работы при выборе каждого нулевого канала. Общее число каналов коммутации, как правило, разбито на группы по 10 каналов в каждой. В таком случае сброс происходит на одном нулевом канале в каждом десятке. При работе в циклическом режиме последующий номер включенного канала отличается от предыдущего всегда на единицу, и при отсутствии сброса счетчика 7 импульсов в начале преобразования число импульсов, вырабатываемых высокочастотным генератором 10, всегда равно 1.

Таким образом, -в циклическом режиме работы время преобразования кода является постоянным, независимым от номера включенного канала и минимальным по величине временем выдачи одного импульса высокочастотног генератора 10. Счетчик 7 импульсов реверсивный, позволяющий производить как сложение, так и вычитание. При разбиении каналов на группы по 10 целесообразно использовать двоичнодесятичный счетчик. БЛОК б сравнения производит сравнение кодов счетчика 1 каналов-и счетчика 7 импульсо с выдачей выходного сигнала Равенство, при равенстве этих кодов, что определяет момент коЬца преобразования. Креме того, блок б сравнения

производит поразрядное сравнение старших двух разрядов кодов, что позволяет Определить разницу между ними. При работе счетчика 7 импульсов в двоично-десятичном коде это позволяет определить, превышает или нет разница четыре. Если разница между кодами больше четырех, а новый исходный код счетчика 1 каналов больше предыдущего или разница меньше четырех, а новый исходный код меньше предыдущего, блок б сравнения вырабатывает выходной сигнал, определяющий работу счетчика 7 импульсов в режиме вычитание если разница кодов меньше четырех, а новый исходный код больше предыдущего или разница больше четырех, а новый исходный код меньше предыдущего,блок б сравнения вырабатывает выходной сигнал, определяющий работу счетчика 7 импульсов в режиме сложение. В зависимости от выходных сигналов блока б сравнения импульсы высокочастотного генератора 10 проходят либо через элемент И 20, либо через элемент И 21 на вычитающий или суммирую11а1й входы счетчика 7 импульсов и по соответствующей шине 22 или 23 поступают в выносной коммутатор. В адресном режиме при любой комбинации предыдущего и последующего исходных кодов число импульсов преобразованного кода не превышает пяти. При поступлении очередного импульса тактового генератора 2 происходит изменение состояния счетчика 1 каналов и возникает сигнал на одном из элементов И 12 или 13 в зависимости от того, требуется ли сброс в начале преобразования. Если преобразование идет с начальным сбросом, то выдается импульс сброса в выносной коммутатор с выхода элемента и 12. В этом случае включение высокочастотного генератора 10 осуществляется после прохождения импульса сброса в выносной коммутатор, т.е. по его заднему фронту. Выходной сигнал элемента И 12 поступает на формирователь 16, выходной импульс которого проходит через элемент ИЛИ 15 на единичный вход триггера 9. Триггер 9 устанавливается в единичное.состояние и его единичный выходной сигнал включает высокочастотный генератор 10, начинается работа счетчика 7 импульсов и выдача необходимого числа импульсов в выносной коммутатор, котррые устанавливают его счетчик в положение , соответствующее номеру включенного канала. Работа высокочастотного генератора 10 продолжается до момента, когда блок 6 сравнения вырабатывает сигнал, соответствующий признаку равенство. Этот выходной сигнал сбрасывает триггер 9 и высокочастотный генератор 10 выключается до прихода следующего тактового импульса генератора 2. При отсутствии импульса сброса в начале преобразования тактоцые импульсы генератора 2 проходят через элементы и 13 и ИЛИ 15, и установка триггера 9 в единичное состояние, включение высокочастотного генератора 10 и выдача импульсов в выносной коммутатор происходят по переднему фронту 0 тактовых импульсов генератора 2.

Сброс триггера 9 и выключение высокочастотного генератора 10 также производится по выходному сигнешу блока б сравнения, соответствующего 5 признаку равенство.

Таким образом, триггер 9 устанавливается в единичное состояние по переднему или заднему фронту тактовых импульсов в зависимости от нали-i 0 чия импульса сброса в начале преобразования, что соответствует моменту начала преобразования, и сбрасывается сигналом признака равенство, что соответствует моменту конца пре5 образования. Время, в течение которого триггер 9 находится в единичном состоянии, соответствует интервалу преобразования кода. Нулевой выходной сигнал триггера 9 поступает на вход элемента ИЛИ 14. На первый вход

0 элемента ИЛИ 14 поступают тактовые импульсы генератора 2; Если коды равны и время на преобразовгдаие кода не требуется, например, при многократных измерениях по одному адресу, 5 триггер 9 находится в сброшенном

состоянии, его нулевой выходной сигнал пропускает тактовые импульсы генератора 2 через элемент ИЛИ 14 на формирователь 18, который по задне0 му фронту тактовых импульсов формирует импульс Конец операции. Если коды неравны, то триггер 9 устанавливается в единичное состояние -и тактовые импульсы через элемент ИЛИ 5 14 не проходят, формирование импульсов Конец операции происходит по фронту, возникающему в момент окончания преобразования, когда сбрасывает. ся триггер 9 и возникает фронт на Q выходе элемента ИЛИ 14.

Сигнал Конец операции при выносной коммутации возникает с задержкой, равной времени преобразования кода и изменяющейся вместе с ним. Это повышает быстродействие по сравнению

5 с выбором постоянной задержки, соответствующей максимальному времени преобразования кода. С выхода формирователя 18 импульсы поступают на элемент 8.

0 Таким образом, предлагаемое изобретение по сравнению с известным позволяет повысить быстродействие коммутатора при выносной коммутации формированием сигнала Конец опера5 ции с переменной задержкой, соответствующей времени преобразования кода и сокращения самого времени преобразования кода в циклическом режиме до минимального благодаря оТ сутсхвию сброса в начале преобразования, а в адресном режиме сокращением максимального времени преобразования в два раза путем введения двух формирователей, двух элементов ИЛИ, четырех элементов И, инвертора и соответствующих связей. Формула изобретения Коммутатор, содержащий счетчик каналов, счетный вход которого соединен с выходом тактового генератор информационные входы подключены к входным шинам, а выходы соединены ч рез дешифратор с группой выходных шин и непосредственно с первыми вхо дами блока сравнения, вторые входы которого подключены к выходам счетчика импульсов, а также элемент задержки и триггер, единичный выход которого йоединен с входом запуска высокочастотного генератора, отличающийся тем, что, с целью повышения быстродействия, него введены два формирователя, два элемента ИЛИ, гетыре элемента И и инвертор, вход которого соединен с выходом нулевого канала дешифратора и первым входом первого элемента И, а выход подключен к первому входувторогб элемента И, второй вход кот рого соединен с выходом тактового генератора, вторым входом первого элемента И и первым входом первого элемента .ИЛИ, третий вход - с третьим входом первого элемента И, первым выходом блока сравнения и нулевым входом триггера, а выход подключен к первому входу второго элемента ИЛИ, второй вход которого через первый формирователь соединен с выходом первого элемента И, первой выходной шиной и входом сброса счетчика импульсов, а выход подключен к единичHOJviy входу триггера, нулевой выход которого соединен с вторым входом первого элемента ИЛИ, выход которого через второй формирователь подключен к входу элемента задержки, выход которого соединен с второй выходной шиной, при этрм второй и третий выходы блока сравнения подключены к первым входам соответственно третьего и четвертого элементов И, вторые входы которых объединены и соединены с выходом высокочастотного генератора, выход третьего элемента И подключен к третьей выходной шине и вычитающему входу счетчика импульсов, а выход четвертого элемента И - к четвертой выходной шине и суммирующему входу счетчика импульсов. Источники информации, принятые во внимание при экспертизе 1.Долгов В.А. и др. Коммутирующие устр ойства автоматических систем контроля. Энергия, М., 1969, с. 70, рис. 47. 2.Гитис Э.И. Преобразователи информации для электронных цифровых вычислительных устройств. Энергия, М., 1970, с. 234, рис. 5-10 б (прототип) .

Авторы

Даты

1983-02-28—Публикация

1981-10-19—Подача