Фив.1

пряжения с выхода ЦАП 7 через ключ 5 на аналоговый выход коммутатора и анализа с помощью АЦП 9 блоком 4 кодов получающихся при этом выходных напряжений. При отказах типа залипание части входных ключей 1 истинное значение напряжений, находящихся на исправных входных ключах 1, восстанавливается путем компенсации напряжения, приходящего с отказавшего

канала, напряжением с выхода ЦАП 7. Алгоритм работы коммутатора, включающий тестирование и при необходимости восстановление, выполняется автоматически перед коммутацией требуемого входного ключа 1. По результатам тестирования и восстановления коммутатором выдаются сигналы готовности или неисправности. 1 з.п. ф-лы, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ - КОД | 1991 |

|

RU2027303C1 |

| Фотоэлектрический анализатор количества и размеров частиц | 1987 |

|

SU1518727A1 |

| Система экстремального регулирования квадрупольного масс-спектрометра | 1989 |

|

SU1795419A1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2656989C1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 1999 |

|

RU2173030C2 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

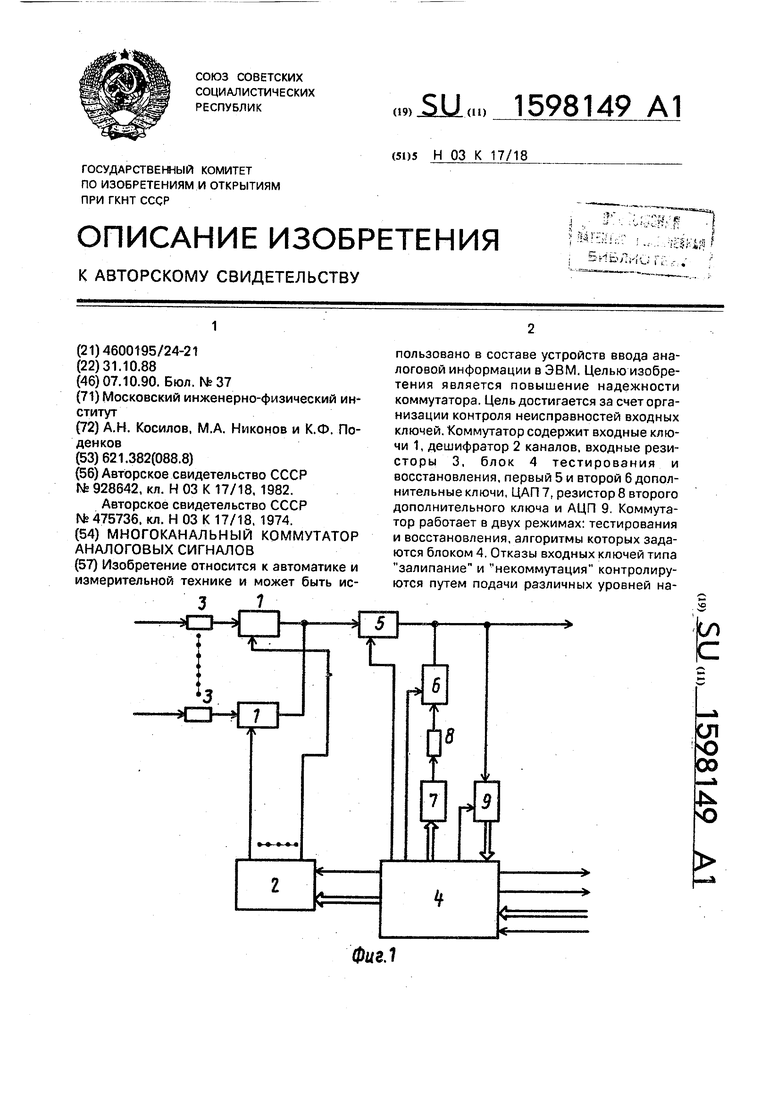

Изобретение относится к автоматике и измерительной технике и может быть использовано в составе устройств ввода аналоговой информации в ЭВМ. Целью изобретения является повышение надежности коммутатора. Цель достигаемое за счет организации контроля неисправностей входных ключей. Коммутатор содержит входные ключи 1, дешифратор 2 каналов, входные резисторы 3, блок 4 тестирования и восстановления, первый 5 и второй 6 дополнительные ключи, ЦАП 7, резистор 8 второго дополнительного ключа и АЦП 9. Коммутатор работает в двух режимах: тестирования и восстановления, алгоритмы которых задаются блоком 4. Отказы входных ключей типа "залипание" и "некоммутация" контролируются путем подачи различных уровней напряжения с выхода ЦАП 7 через ключ 5 на аналоговый выход коммутатора и анализа с помощью АЦП 9 блоком 4 кодов получающихся при этом выходных напряжений. При отказах типа "залипание" части входных ключей 1 истинное значение напряжений, находящихся на исправных входных ключах 1, восстанавливается путем компенсации напряжения, приходящего с отказавшего канала, напряжением с выхода ЦАП 7. Алгоритм работы коммутатора, включающий тестирование и при необходимости восстановление, выполняется автоматически перед коммутацией требуемого входного ключа 1. По результатам тестирования и восстановления коммутатором выдаются сигналы готовности или неисправности. 1 з.п.ф-лы, 2 ил.

Изобретение относится к автоматике и измерительной технике и может быть использовано в составе устройств ввода аналоговой информации в ЭВМ.

Целью изобретения является повыше- ние надежности коммутатора за счет организации контроля неисправностей входных ключей.

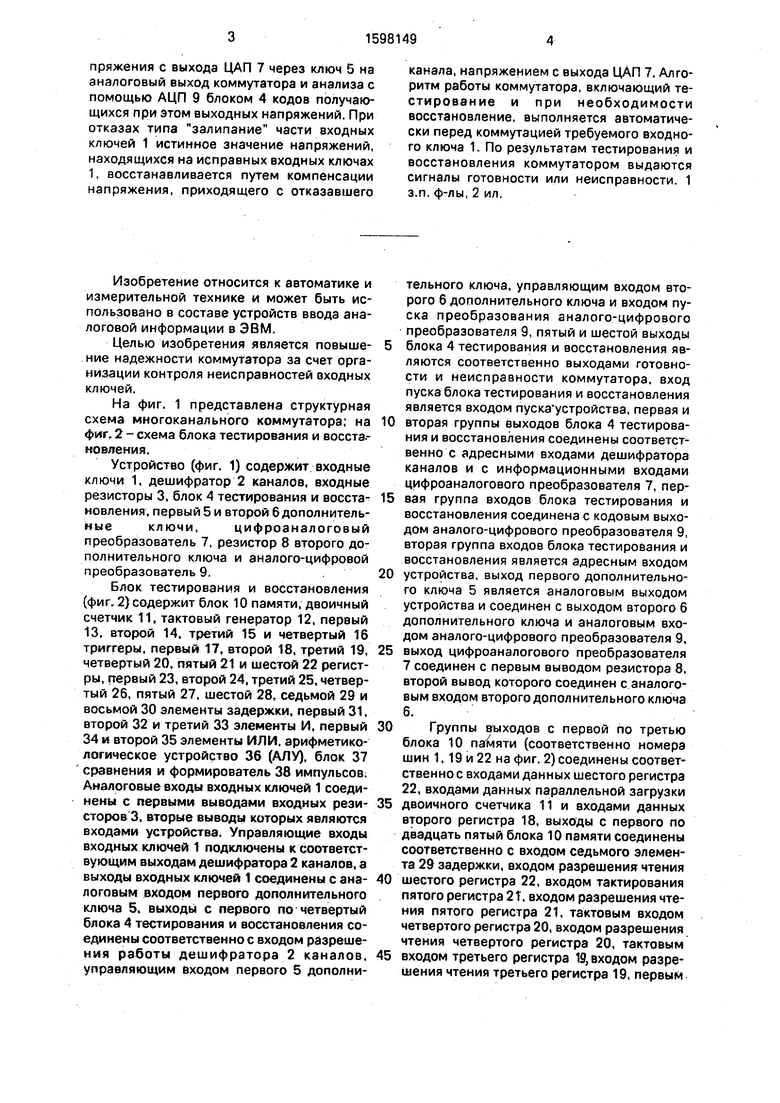

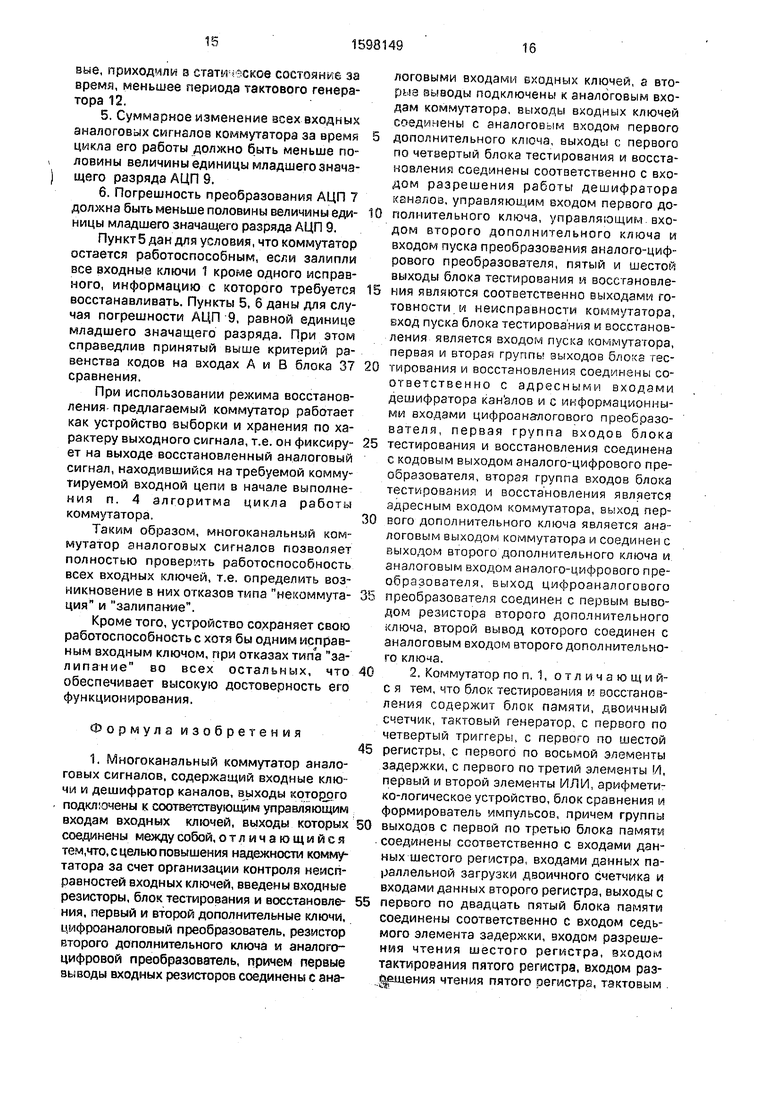

На фиг. 1 представлена структурная схема многоканального коммутатора: на фиг, 2 - схема блока тестирования и восста.- новления.

Устройство (фиг, 1) содержит входные ключи 1, дешифратор 2 каналов, входные резисторы 3, блок 4 тестирования и восста- новления, первый 5 и второй 6 дополнительные ключи, цифроаналоговый преобразователь 7, резистор 8 второго дополнительного ключа и аналого-цифровой преобразователь 9.

Блок тестирования и восстановления (фиг. 2) содержит блок 10 памяти, двоичный счетчик 11, тактовый генератор 12, первый 13, второй 14, третий 15 и четвертый 16 триггеры, первый 17, второй 18, третий 19, четвертый 20, пятый 21 и шестой 22 регистры, гтервый 23, второй 24, третий 25, четвертый 26, пятый 27, шестой 28, седьмой 29 и восьмой 30 элементы задержки, первый 31, второй 32 и третий 33 элементы И, первый 34 и второй 35 элементы ИЛИ, арифметико- логическое устройство 36 (АЛУ), блок 37 сравнения и формирователь 38 импульсов; Аналоговые входы входных ключей 1 соединены с первыми выводами входных рези- сторов 3, вторые выводы которых являются входами устройства. Управляющие входы входных ключей 1 подключены к соответствующим выходам дешифратора 2 каналов, а выходы входных ключей 1 соединены с ана- логовым входом первого дополнительного ключа 5, выходь с первого по четвертый блока 4 тестирования и восстановления соединены соответственно с входом разреше- ния работы дешифратора 2 каналов, управляющим бходом первого 5 дополнительного ключа, управляющим входом второго 6 дополнительного ключа и входом пуска преобразования аналого-цифрового преобразователя 9, пятый и шестой выходы блока 4 тестирования и восстановления являются соответственно выходами готовности и неисправности коммутатора, вход пуска блока тестирования и восстановления является входом пуска устройства, первая и вторая группы выходов блока 4 тестирования и восстановления соединены соответственно с адресными входами дешифратора каналов и с информационными входами цифроаналогового преобразователя 7, первая группа входов блока тестирования и восстановления соединена с кодовым выходом аналого-цифрового преобразователя 9, вторая группа входов блока тестиробания и восстановления является адресным входом устройства, выход первого дополнительного ключа 5 является аналоговым выходом устройства и соединен с выходом второго 6 дополнительного ключа и аналоговым входом аналого-цифрового преобразователя 9, выход цифроаналогового преобразователя 7 соединен с первым выводом резистора 8, второй вывод которого соединен с аналоговым входом второго дополнительного ключа бГруппы выходов с первой по третью блока 10 (соответственно номера шин 1,19 и 22 на фиг. 2) соединены соответственно с входами данных шестого регистра 22, входами данных параллельной загрузки двоичного счетчика 11 и входами данных второго регистра 18, выходы с первого по двадцать пятый блока 10 памяти соединены соответственно с входом седьмого элемента 29 задержки, входом разрешения чтения шестого регистра 22, входом тактирования пятого регистра 2 Т, входом разрешения чтения пятого регистра 21, тактовым входом четвертого регистра 20, входом разрешения чтения четвертого регистра 20, тактовым входом третьего регистра 19, входом разрешения чтения третьего регистра 19, первым

управляющим входом блока 37 сравнения вторым управляющим входом блока 37 сравнения, тактовым входом третьего триггера 15, тактовым входом четвертоготригге- ра 16, входом восьмого элемента 30 задержки, входом шестого элемента 28 задержки, входом пятого элемента 27 задержки, входом четвертого элемента 26 задержки, входом третьего элемента 25 задержки, первым входом первого элемента ИЛИ 34, первым выходом блока 4 (фиг. 1) тестирования и восстановления, входом второго элемента задержки 24, третьим выходом блока 4 тестирования и восстановления, четвертым выходом блока 4 тестирования и восстановления, вторым выходом блока 4 тестирования и восстановления, первым и вторым управляющими входами арифметико-логического устройства 36, входы адреса блока 10 памяти соединены с выходами двоичного счетчика 11, тактовый вход которого соединен с выходом тактового генератора 12, инверсный вход сброса двоичного счетчика 11 соединен с выходом первого триггера 13, тактовым входом первого регистра 17, инверсным входом установки в единицу второго триггера 14 и с входом формирователя 38 импульсов, вход разрешения параллельной загрузки двоичного счетчика 11 соединен с выходом второго элемента ИЛИ 35, вход данных первого триггера 13 подключен к линии единичного потенциала, тактовый вход первого триггера 13 соединен с инверсным выходом первого элемента 23 задержки, вход которого соединен с вторым входом первого элемента ИЛИ 34 и с входом блока 4 тестирования и восстановления, вход сброса первого триггера 13 соединен с выходом первого элемента ИЛИ 34, инверсный выход второго триггера 14 соединен с первым входом первого элемента И 31, вход данных второго триггера 14 соединен с первым выходом блока 37 сравнения и с первь1м входом третьего элемента И 33, тактовый вход второго триггера 14 соединен с выходом восьмого элемента 30 задержки, выход третьего триггера 15 соединен с пятым выходом блока 4 тестирования и восстановления, вход сброса третьего триггера 15 соединен с входом сброса четвертого триггера 16 и с выходом формирователя 38 импульсов, входы данных третьего 15 и четвертого 16 триггеров подключены к линии единичного потенциала, с шестым выходом блока тестирования и восстановления соединен выход четвертого триггера 16, выходы первого регистра 17 соединены с первой группой выходов блока 4 тестирования и восстановления, с второй

группой входов которого соединены входы данных первого регистра 17, тактовый вход второго регистра 18 соединен с выходом второго элемента 24 задержки, выходы вто- 5 рого регистра 18 соединены с второй группой выходов блока 4 тестирования и восстановления, входы данных третьего регистра 19 соединены с входами данных четвертого 20 и пятого 21 регистров и с первой 10 группой входов блока 4 тестирования и восстановления, выходы третьего регистра 19 соединены с выходами четвертого регистра 20 и с первой группой входов данных блока 37 сравнения, выходы пятого регистра 21 15 соединены с выходами шестого регистра 22 и с группой информационных входов арифметико-логического устройства 36, тактовый вход шестого 22 регистра соединен с выходом седьмого 29 элемента задержки, выход 20 третьего 25 элемента задержки соединен с первым входом второго элемента ИЛИ 35. выход четвертого 26 элемента задержки соединен с вторым входом первого элемента И 31, выход которого соединен с вторым 25 входом второго элемента ИЛИ 35, выход пятого элемента 27 задержки соединен с первым входом второго элемента И 32, выход которого соединен с третьим входом второго элемента ИЛИ 35, выход шестого 30 элемента 28 задержки соединен с вторым входом третьего элемента И 33, выход которого соединен с четвертым входом второго элемента ИЛИ 35, второй вход второго элемента И 32 соединен с вторым выходом бло- 35 ка 37 сравнения, вторая группа входов данных которой соединена с выходами арифметико-логического устройства 36,

Коммутатор работает следующим образом.

40 Цикл работы начинается после прихода пускового импульса на вход пуска коммутатора. По этому импульсу в блоке 4 тестирова- ния и восстановления запоминается выставленный на адресных входах коммута- 5 тора код адреса входного ключа 1, который требуется замкнуть (в дальнейшем описании будем его называть требуемым ключом). Алгоритм работы коммутатора состоит из двух частей: режима тестирования и режима 0 восстановления (если он требуется) и задается блоком 4 тестирования и восстановле- ния. Сразу после пуска коммутатор начинает работать в режиме тестирования. В этом режиме полностью проверяется ра- 5 ботоспособность требуемого входного ключа и проверяются на наличие залипаний все остальные входные ключи коммутатора. Если требуемый входной ключ полностью работоспособен, а в остальных входных ключах отсутствуют залипания, требуемый

входной ключ замыкается и на соответствующем выходе коммутатора формируется сигнал готовности, который показывает, что требуемая входная цепь замкнута и информация на аналоговом выходе коммутатора достоверна. Цикл работы коммутатора на этом прекращается. Если в требуемом входном ключе обнаружена неисправность (некоммутация или залипание), цикл работы коммутатора прекращается и на его соответствующем выходе формируется сигнал неисправности, означающий, что коммутатор на данной входной цепи неработоспособен. Если тест требуемого ключа закончился успешно, а тест на залипание остальных ключей показал, что среди них есть хотя бы один залипщий, коммутатор начинает работу в режиме восстановления. В этом режиме выполняется восстановление на аналоговом выходе коммутатора истинного значения сигнала, находящегося на входе требуемого ключа, несмотря на наличие залипших входных ключей. При успешном завершении восстановления выдается сигнал готовности на выходе коммутатора. Если восстановление не удалось (например, из- за неисправности в блоке 4), на выходе коммутатора выдается сигнал неисправности. В дальнейше м при описании работы коммутатора предполагается, что активными уровнями сигналов в его схеме являются уровни логической единицы, а активными фронтами сигналов - переходы из нуля в единицу. Аналоговые коммутируемые сигналы подаются на аналоговые входы коммутатора (фиг. 1), сигналы с выходов дешифратора 2 управляют замыканием и размыканием входных ключей 1, дешифратор 2 управляется по адресным входам и входу разрешения работы. Наличие на последнем пассивного уровня запрещает работу дешифратора 2. т.е. при этом все входные ключи 1 разомкнуты. Код на адресных входах дешифратора при активном сигнале на входе разрешения его работы определяет один замкнутый входной ключ 1, остальные входные ключи при этом разомкнуты. Код адреса и сигнал разрешения работы дешифратора поступают на его входы с соответствующих выходов блока 4. Сигналы с выходов блока 4 также управляют дополнительными ключами 5 и 6, задают код на входах ЦАП 7 и запускают цикл преобразования АЦП 9. При этом дополнительные ключи 5 и 6 замкнуты при активном уровне сигнала на их управляющих входах и разомкнуты при пассивном. Цикл преобразования АЦП 9 инициируется активным фронтом сигнала на входе пуска АЦП 9. Выходное напряжение ЦАП 7 через резистор 8 и ключ 6 может быть подано на

аналоговый выход коммутатора в любой требуемый момент независимо от состояния входных ключей 1. При этом ключи 5 и 6 управляются независимо друг от друга. АЦП 5 9 позволяет получать для анализа в блоке 4 отцифрованные значения напряжений на аналоговом выходе коммутатора. Сигналы готовности и неисправности с выходов блока 4 подаются активными уровнями. 10 Блок 4 тестирования и восстановления (фиг. 2) начинает цикл работы коммутатора по приходу единичного импульса пуска на одноименный вход коммутатора, В блоке 4 этот импульс поступает на вход элемента 23 15 задержки. Передний фронт импульса пуска через элемент ИЛИ 34 сбрасывает в нуль триггер 13, выход которого при этом сбрасывает в нуль двоичный счетчик 11 и устанавливает в единицу триггер 14. Задний 20 фронт импульса пуска с инверсного выхода элемента 23 задержки тактирует триггер 13, вызывая запись в него логической единицы Элемент 23 задержки служит для того, чтобы тактовый фронт на тактовый вход тригге- 25 ра 13 приходил после того, как будет убран сигнал сброса с входа сброса триггера 13. Положительный фронт с выхода триггера 13 тактирует регистр 17, вызывая запись в него кода адреса требуемого ключа, который с 30 выхода регистра 17 подается на адресные входы д ешифратора 2. Кроме того, положительный фронт с выхода триггера 13 вызывает формирование на выходе формирователя 38 положительного импуль- 35 са. который сбрасывает в ноль триггеры 15 и 16, т.е. снимает с выходов коммутатора сигналы готовности и неисправности, так как к этим выходам коммутатора подключены выходы триггеров 15 и 16 соответствен- 0 но, а также разрешает работу двоичному счетчику 11, который считает импульсы тактового генератора 12 и адресует блок 10 памяти, кодируя содержимое которого соответствующим образом, можно на каждом 5 такте генератора t2 выдавать сигналы по выходам блока 4 и тактировать регистры блока 4, выполняющие прием данных с АЦП 9. Предположим, что требуется подать некоторый код на входы ЦАП 7 в определяемый 0 алгоритмом работы коммутатора момент. Для этого требуемый код программируется в разрядах блока 10, выходы которых соединены с входами данных регистра 18 и по этому же адресу в разряд блока 10, соеди- 5 ненный с входом элемента 24 задержки, заносится логическая единица. Когда на выходах счетчика 11 выставляется код рассматриваемого адреса, через элемент 24 задержки, обеспечивающий надежное установление данных на входах данных регистра 18, этот регистр тактируется и требуемый код с его выходов поступает на входы ЦАП 7. Каждому шагу алгоритма работы коммутатора однозначно соответствует ячейка блока 10, адрес которой определяется выходным кодом счетчика 11. Скорость выполнения алгоритма работы коммутатора задается тактовым генератором 12. Если на некотором шаге алгоритма работы коммутатора с определенного выхода блока 10 требуется выдать активный сигнал, то в соответствующий разряд ячейки блока 10 с адресом, соответствующим требуемому шагу алгоритма работы коммутатора, должна быть записана логическая единица. Рассмотрим назначение выходов блока 10. при зтом нумерация выходов соответствует их нумерации на шине, представленной на фиг. 2, Г - первая группа выходов, соединенная с входами данных регистра 22, 2 - выход, соединенный через элемент 29 задержки с тактовым входом регистра, 22; 3- - выход, соединенный с входом разрешения чтения регистра 22 (вход разрешения чтения регистров при пассивном сигнале на нем переводит выходы регистров в третье состояние. В остальном работа регистра 22 полностью идентична работе регистра 18): 4 - выход, соединенный с тактовым входом регистра 21,- 5 - выход, соединенный с входом разрешения чтения регистра 21; 6 - выход, соединенный с тактовым входом регистра 20; 7 - выход, соединенный с входом разрешения чтения регистра 20; 8 - выход, соединенный с тактовым входом регистра 19; 9 - выход, соединенный с входом разрешения чтения регистра 19; 10 - выход, соединенный с управляющим входом разрешения проверки равенства двух кодов на входах данных А и В блока 37сравнения; 1 Г - выход, соединенный с управляющим вхадом А В блока 37 сравнения, разрешения проверки того, что код. поступающий на вход данных А блока 37 с выходов регистров 19 или 20, меньше кода, поступающего на вход данных В блока 37 с выхода АЛУ 36; 12 - выход, соединенный с тактовым входом триггера 15; 13 - выход, соединенный с тактовым входом триггера 16; 14 - выход, соединенный через элемент 30 задержки с тактовым входом триггера 14,- 20 - выход, появление логической единицы на котором приводит к тем же действиям, что и появление положительного фронта пускового импульса на входе пуска коммутатора; 21 - выход, соединенный с входом разрешения работы дешифратора 2; 22 - третья группа выходов, соединенная с входами данных регистра 18;

23 - выход, соединенный через элемент 24 задержки с тактовым входом регистра 18; 24 - выход, соединенный с входом управления дополнительного ключа 6; 5 - выход, соединенный с входом пуска преобразования АЦП 9. Выходы 15, 16, 17, 18 блока 10 предназначены для ветвления алгоритма цикла работы коммутатора: выход 18 - для безусловного 10 ветвления, выходы 15, 16 - для ветвления по результатам текущей проверки состояния выходов блока 37 сравнения, а выход 17 - для ветвления по результату проверки запомненного состояния выхода 15 блока 37 сравнения. При появлении логической единицы на выходе 18 блока 10 на выходе элемента ИЛИ 35 формируется активный сигнал, который поступает на вход разрешения параллельной загрузки 20 счетчика 11 и вызывает тактируемую генератором 12 запись в счетчик 11 адреса перехода, выставленного на второй группе выходов 19 блока 10. Элемент 25 задержки задерживает формирование активного 5 сигнала на выходе элемента ИЛИ 35 на время гарантированного установления адреса перехода на входах данных счетчика 11. Наличие элемента задержки позволяет кодировать адрес перехода и логическую 0 единицу на выходе 18 блока 10 в одном слове памяти. Назначение всех элементов задержки блока тестирования и восстановления, кроме элемента 23, заключается именно в этом. Логическая единица на вы- 5 ходе 15 блока 10 проверяет состояние выхода блока 37 сравнения. Если на этом выходе присутствует логическая единица, происходит ветвление. Логическая единица на выходе 16 блока 10 проверяет состоя- 0 ние выхода блока 37 сравнения. Если на этом выходе присутствует логическая единица, происходит ветвление. Логическая единица на выходе 17 блока 10 проверяет состояние инверсного выхода 5 триггера 14, Если этот выход находится б состояние логической единицы, происходит ветвление. Адрес перехода всегда выставляется на второй группе выходов 19 блока 10.. Блок 37 сравнения выполняет проверку соотношения-кодов на входах А и В при логической единице на соответствующем управляющем входе и . При логической единице на управляющем входе и равенстве кодов на входах А и В, на выхо- .де блока 37 сравнения устанавливается логическая единица. Во всех остальных случаях на выходе - уровень логического нуля. При логической единице на управляющем входе блока 37 сравнения и выполнении данного неравенства для реальных кодов на входах А и В на выходе блока 37 сравнения устанавливается логическая единица. Во всех остальных случаях на выходе - уровень логического нуля. Выдавая в требуемые моменты активные сигналы с выхода 14 блока 10. можно записывать в триггер 14 текущие значения выхода блока 37, т.е. запоминать результат сравнения. При этом элемент 30 задержки должен обеспечивать задержку, большую суммы задержек на элементе 29 и цепочке: регистр 22. АЛУ 36. блок 37 сравнения. В этом случае в одном слове памяти блока 10 можно кодировать выдачу кода на сравнение по первой группе 1 выходов блока 10. запись этого кода в регистр 22. выполнение сравнения на блоке 37 и запись результата сравнения в триггер 14. что позволяет экономить объем памяти. На входы данных регистров 20-22 подается выходной код АЦП 9. Содержимое регистров 19 и 20 с помощью блока 37 сравнения может сравниваться с содержимым регистров 21 и 22. Каждая пара регистров сравнивается, определяется активным уровнем сигнала на входах разрешения чтения регистров. В регистр 22 заносятся эталонные коды для сравнения с кодом, поступающим с выхода АЦП 9. Поскольку возможна погрешность АЦП 9. равная единице младшего разряда, выходы регистров 21 и 22 подаются на входы данных АЛУ 36. которое управляется сигналами с выходов 27 и 28 блока 10 и в зависимости от значений этих сигналов реализует функции: выход 20Ю. выход 28 - код передается со входа АЛУ 36 на его выход без изменений; выход . выход 28в1 - код на выходе АЛУ равен коду на его входе минус единица: выход 27я1. выход - код на выходе АЛУ равен коду на его входе плюс единица. При проверке равенства кодов на входах А и В считается, что равенство имеет место, если выполняется одно из соотношений: . . . В противном случае считается, что коды не равны. Все элементы блока тестирования и восстановления тактируются активными фронтами сигналов и сбрасываются по входам сброса в нуль единичными уровнями сигналов сброса. Исключение составляют счетчик 11 и триггер 14. Первый сбрасывается в нуль, а второй устанавливается в единицу при нулевых уровнях сигналов на соответствующих входах. Все регистры блока 4 - информационные, выполняющие функцию записи и хранения данных.

Алгоритм цикла работы устройства следующий. Предполагается, что напряжение

на аналоговых входах многоканального коммутатора может изменяться в диапазоне

О-Умакс.

10 КП.2.

15 Подать сигнал пуска АЦП 9. После окончания преобразования ввести выходной код АЦП 9 в блок 4 и сравнить этот код с нулем. Если нуль, перейти к п. 3. Если не нуль, запомнить, что имеется отказ типа залипа20 ние и перейти к п. 4. Отсутствие нулевого напряжения на аналоговом выходе коммутатора в данном случае означает, что кроме ключа 6 имеется еще Хотя бы один замкнутый ключ 1. на связанной с входом которого

26 входной коммутируемой цепи присутствует не нулевое напряжение, которое делится на резисторах 3 и 8. Если на входе залипшего ключа нулевое напряжение, отказ в данном пункте обнаружить нельзя,

0 3. Установить на выходе ЦАП 7 напряжение, равное Умакс. Подать сигнал пуска АЦП 9. После окончания преобразования ввести выходной код АЦП 9 в блок 4 и сравнить этот код с кодом, соответствующим

5 напряжению Умакс. Если коды равны, перейти к п. 4. Если коды не равны, запомнить, что имеется отказ типа залипание и перейти к п. 4. Отсутствие напряжения Умакс на аналоговом выходе коммутатора в данном случае

0 означает, что кроме ключа 6 имеется еще хотя бы один замкнутый ключ 1. на связанной с входом которого входной коммутируемой цепи присутствует напряжениеУ Умакс. Напряжение Умакс делится на рези5 сторах 3 и 8. в результате чего результирующее напряжение на аналоговом выходе коммутатора меньше Умакс.

5 аналоговом выходе коммутатора. Если А Умакс/2. перейти к п. 5. Если А У макс/2, перейти к п. 7.

код, соответствующий нулевому выходному напряжению ЦАП 7. Подать сигнал пуска АЦП 9. После окончания преобразования ввести выходной код АЦП 9 в блок 4. Предположим, что введен код, соответствующий напряжению С на аналоговом выходе коммутатора. Перейти к п. 6.

10, Проверить результаты работы в п. 2 и п. 3 алгоритма. Если залипания нет,

дать выходной сигнал готовности, закончить цикл работы коммутатора и перейти к п. 1 алгоритма. Если залипание есть, начать работу в режиме восстановления перехо- 5 дом к п, 11.

Условия надежной работы коммутатора 40 следующие.

Пункт 5 дан для условия, что коммутатор остается работоспособным, если залипли все входные ключи 1 кроме одного исправного, информацию с которого требуется восстанавливать. Пункты 5, 6 даны для случая погрешности АЦП 9, равной единице младшего значащего разряда. При этом справедлив принятый выше критерий равенства кодов на входах А и В блока 37 сравнения.

При использовании режима восстановления предлагаемый коммутатор работает как устройство выборки и хранения по характеру выходного сигнала, т.е. он фиксиру- ет на выходе восстановленный аналоговый сигнал, находившийся на требуемой коммутируемой входной цеп в начале выполнения п. 4 алгоритма цикла работы коммутатора.

Таким образом, многоканальный коммутатор аналоговых сигналов позволяет полностью проверить работоспособность всех входных ключей, т.е. определить возникновение в них отказов типа некоммута- ция и залипанме.

Кроме того, устройство сохраняет свою работоспособность с хотя бы одним исправным входным ключом, при отказах типа за- липание во всех остальных, что обеспечивает высокую достоверность его функционирования.

ормула изобретения

10

15 20

25 0

5

0

5

0 5

логовыми входами входных ключей, а вто- рыз выводы подключены к аналоговым входам коммутатора, выходы входных ключей соединены с аналоговым входом первого дополнительного ключа, выходы с первого по четвертый блока тестирования и восстановления соединены соответственно с входом разрешения работы дешифратора канзлоз, управляющим входом первого дополнительного ключа, управляющим, входом второго дополнительного ключа и входом пуска преобразования аналого-цифрового преобразователя, пятый и шестой выходы блока тестирования и восстановления являются соответственно выходами готовности, и неисправности коммутатора, вход пуска блока тестирования и восстановления, является входом пуска коммутатора, первая и вторая группы выходов блока тестирования и восстановления соединены соответственно с адресными входами дешифратора кан алов и с информационными входами цифроаналогового преобразователя, первая группа входов блока тестирования и восстановления соединена с кодовым выходом аналого-цифрового преобразователя, вторая группа входов блока тестирования и восстановления является адресным входом коммутатора, выход первого дополнительного ключа является аналоговым выходом коммутатора и соединен с выходом второго дополнительного ключа и. аналоговым входом аналого-цифрового преобразователя, выход цифроаналогового преобразователя соединен с первым выводом резистора второго дополнительного ключа, второй вывод которого соединен с аналоговым входом второго дополнительного ключа.

входом четвертого регистра, входом разрешения чтения четвертого регистра, тактовым входом третьего регистра, входом разрешения чтения третьего регистра, первым управляющим входом блока сравнения, вторым управляющим входом блока сравнения, тактовым входом третьего триггера, тактовым входом четвертого триггера, входом восьмого элемента задержки, входом шестого элемента задержки, входами четвертого и пятого элементов задержки, входом третьего элемента задержки, первым входом первого элемента ИЛИ, первым выходом блока тестирования и восстановления, входом второго элемента задержки, третьим выходом блока тестирования и восстановления, четвертым выходом блока тестирования и восстановления, вторым выходом блока тестирования и восстайовле- ния, первым управляющим входом арифметико-логического устройства, вторым управляющим входом арифметико-логического устройства, входы адреса блока памяти соединены с выходами двоичного счетчика, тактовый вход которого соединен с выходом тактового генератора, инверсный вход сброса двоичного счетчика соединен с выходом первого триггера, тактовым входом первого регистра, инверсным входом установки в Г второго триггера и с входом формирователя импульсов, вход разрешения параллельной загрузки двоичного счетчика соединен с выходом второго элемента ИЛИ, вход данных первого триггера подключен к линии единичного потенциала, тактовый вход первого триггера соединен с инверсным выходом первого элемента задержки, вход которого соединен с вторым входом первого элемента ИЛИ и с входом пуска блока тестирования и восстановления, вход сброса первого триггера соединен с выходом первого элемента ИЛИ, инверсный выход второго триггера соединен с первым входом первого элемента И, вход данных второго триггера соединен с первым выходом блока сравнения и с первым входом третьего элемента И, тактовый вход второго триггера соединен с выходом восьмого элемента задержки, выход третьего триггера соединен с пятым выходом блока тестирования и восстановления, вход сброса третьего триггера соединен с входом 5 сброса четвертого триггера и выходом формирователя импульсов, входы данных третьего и четвертого триггеров подключены к линии единичного потенциала, шестой выход блока тестирования и восстановления 10 соединен с выходом четвертого триггера, выходы первого регистра соединены с первой группой выходов блока тестирования и восстановления, с второй группой входов которого соединены входы данных первого 15 регистра, тактовый вход второго регистра соединен с выходом второго элемента задержки, выходы второго регистра соедине- н.ы с второй группой выходов блока тестирования и восстановления, входы дан- 0 ных третьего регистра соединены с входами данных четвертого и пятого регистров и с первой группой входов блока тестирования и восстановления, выходы третьего регистра соединены с выходами четвертого реги- 5 стра и с первой группой входов данных блока сравнения, выходы пятого регистра соединены с выходами шестого регистра и с группой информационных входов арифметико-логического устройства,тактовый вход 0 шестого регистра соединен с выходом седьмого элемента задержки, выход третьего элемента задержки соединен с первым входом второго элемента ИЛИ, выход четвертого элемента задержки соединен с вторым 5 входом первого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход пятого элемента задержки соединен с первым входом второго элемента И, выход которого соединен с третьим 0 входом второго элемента ИЛИ, выход шестого элемента задержки соединен с вторым входом третьего элемента И, выход которого соединен с четвертым входом второго элемента ИЛИ, второй вход второго элемен- 5 та И соединен с вторым выходом блока сравнения, вторая группа входов данных которой соединена с выходами арифметико- логического устройства.

Авторы

Даты

1990-10-07—Публикация

1988-10-31—Подача