Изобретение относится к автоматй-. ке и вычислительной технике и может быть использовано при реализации технических средств цифровых вычислитель ных машин и дискретных автоматов, По основному авт.св. 92834Т известно устройство, содержащее элементы И,-..ИЛИ, реверси&ный счетчик, узлы памяти, узлы перезаписи, комму- татор, формирователь импульсов, счетчик, причем информационный вход устройства соединен с первыми входами rt-з первого и второго э.пементов И, выход первого элемента И подключен к информациоиному входу первого узла памяти, выходы которого соединены с информации онными входами первого узла перезаписи, выходы которого подключены к информационным входам реверсивного счетчика, выходы которого соединены с входами первого элемента ИЛИ и с информационными входами второго уэла перезаписи, выходы которого подклю.чены к входам второго узла памяти, выходы которого соединены с первыми выходными шинами устройства, вход управления устройства.подключен к входу первого коммутатора, первый выход которого соединен с вторым уходом первого элемента И, второй.

третий вь1ходы первого коммутат ура ,. подключены к входам управления вого и второго узлов перезаписи, чеЧ вертый выход первого коммутатора сое динен с входом управления записью первого узла соответственно, пятый выход первого коммутатора подключен к входу управления реверсив10ного счетчика, м первому входу- второ-. го элемента ИЛИ и к входу формирователя импульсов, первый, и второй выходы которого соединены с первым входом третьего элемента И и с информационл ным входом счетчика, выходы которого с

IS : Йойключены к информационным входам третьегЪ узла перезаписи, выходам кол торого соединены с информационными входами третьего узла памяти, выход первого элемента ИЛИ подключен к вто20рым входам третьего элемента И и второго элемента ИЛИ, выход которого соединен с вторым входом второго элемента и, выход которого подк.пючей к информационному входу реверсивного

25 счетчика, вход сброса устройства соединен с входами установки в нулевое состояние узлов памяти, счетчика, реверсивного счетчика, выход третьего элемента И подключен к управляю30щему входу т ретьего узла перезаписи

кроме того, выход первого узла памяти соединен с информационными входами етвертого узла перезаписи но. ходами первой группы входов компаратора, шестой и седьмой выходы первого-коммутатора подключены к .управ- 5 ляющим входам компаратора и четвер- TOiO- узла перезаписи соответственно, выход четвертого узла,, перезаписи соединен с информационным входом четвертого узла памяти,выходы которого 10 подключены к входам второй группы входов компаратора и к входам первой группы входовраспределителя, входы второй ГРУППЫ входов которого соединены с выходами счетчика,; а выходы - «с с входами блока памяти, выходы компаратора подключены к информационным входам второго коммутатора, вход управления которого соединен с вхоом управления устройства, а выходаа с входами управления распределителя, 20 входы установки в нулевое состояниа компаратора, четвертого узла памяти и блока памяти подключены к входу сброса устройства. Устройство позволяет определить максимальное число из 25 ряда чисел, а также все локальные максимумы и их порядковые номера flj.

Однако при автоматизированной обработке данных с помощью известного устройстванеобходимо знать значения 30 и порядковые номера только тех локальных максимумов, которые превышат определенный наперед заданный поог. Например, при анализе совокупности спектральных компонент,; полу- З5в ченных в результате дискретного преобразования Фурье смеси сигнала с умом, некоторые локальные максимумы с невысоким уровнем обусловлены возействием флуктуационных шумов. При / этом полученные с помощью известного устройства результаты приходится подвергать дополнительной обработке,что снижает производительность.

Целью изобретения является расширение функциональных возможностей уст, 45 ройства за счет определения макси- мальных значений, превышающих заданный ПОРОГ.

Поставленная цель достигается тем, что. в устройство для определе- 50 ния максимального числа из ряда чи- сел введены пятый узел памяти и второй компаратор, причем выход пятого узлала яти соединен с первым информационным входом второго компаратора,второй ин- ее формационный вход которого подключен к вьтходу четвертого элемента памяти, ; правляющий вход-второго компаратора «Соединен с дополнительным выходом первого компаратора-, вйход подключен к полнительному входу компаратора О управляющий вход пятого элемента памяти соединен с входом установки порога устройства.

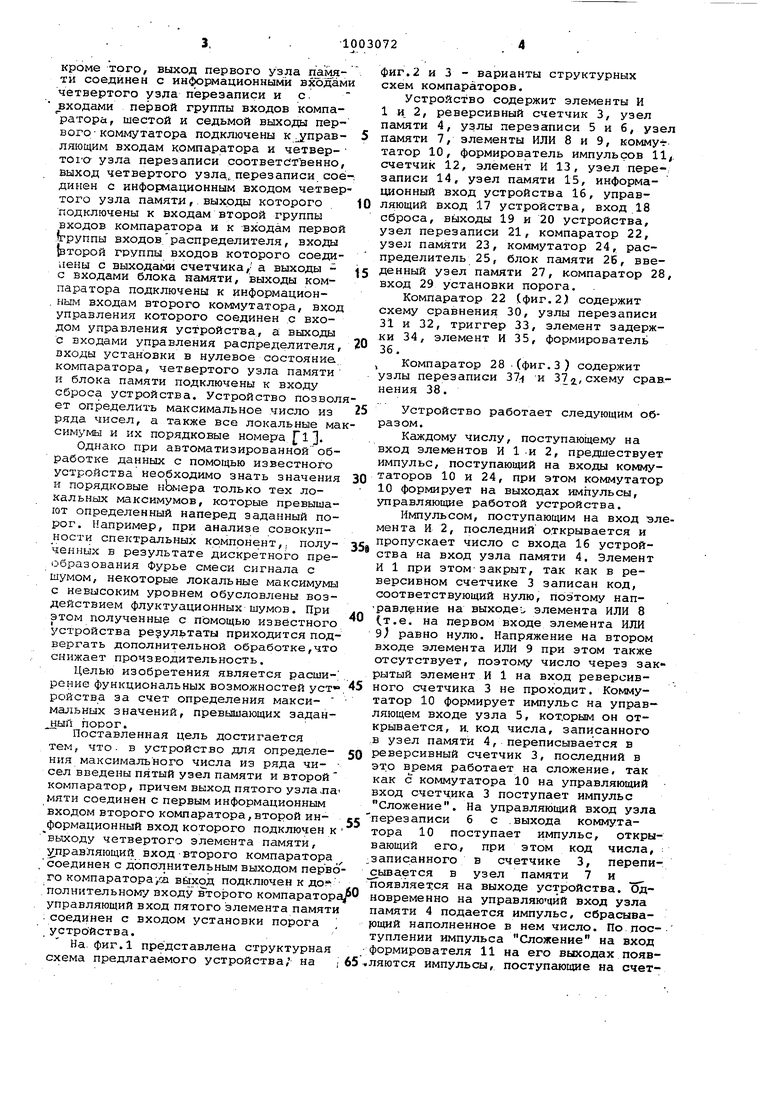

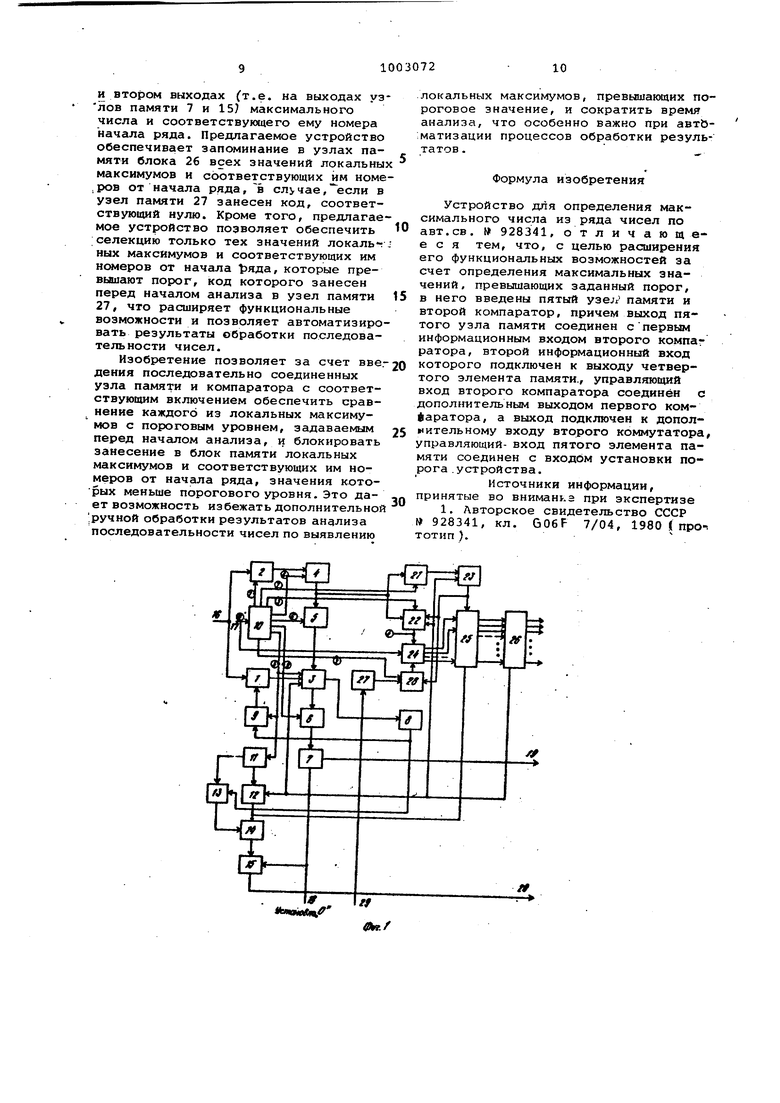

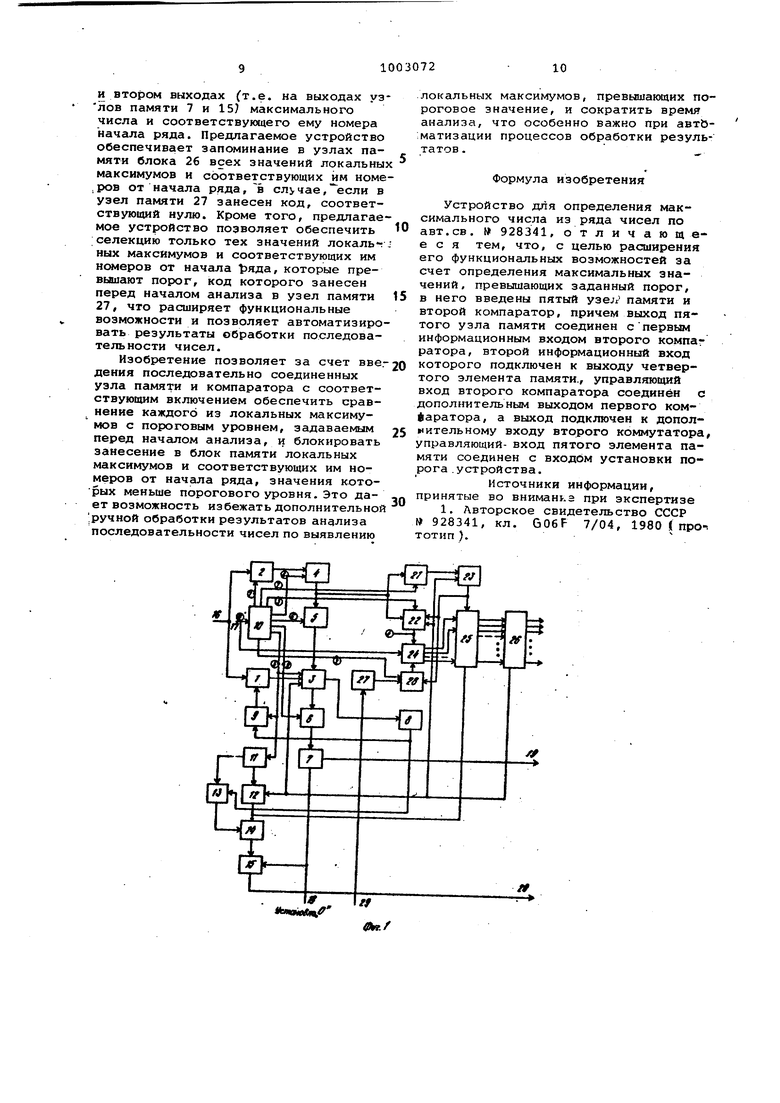

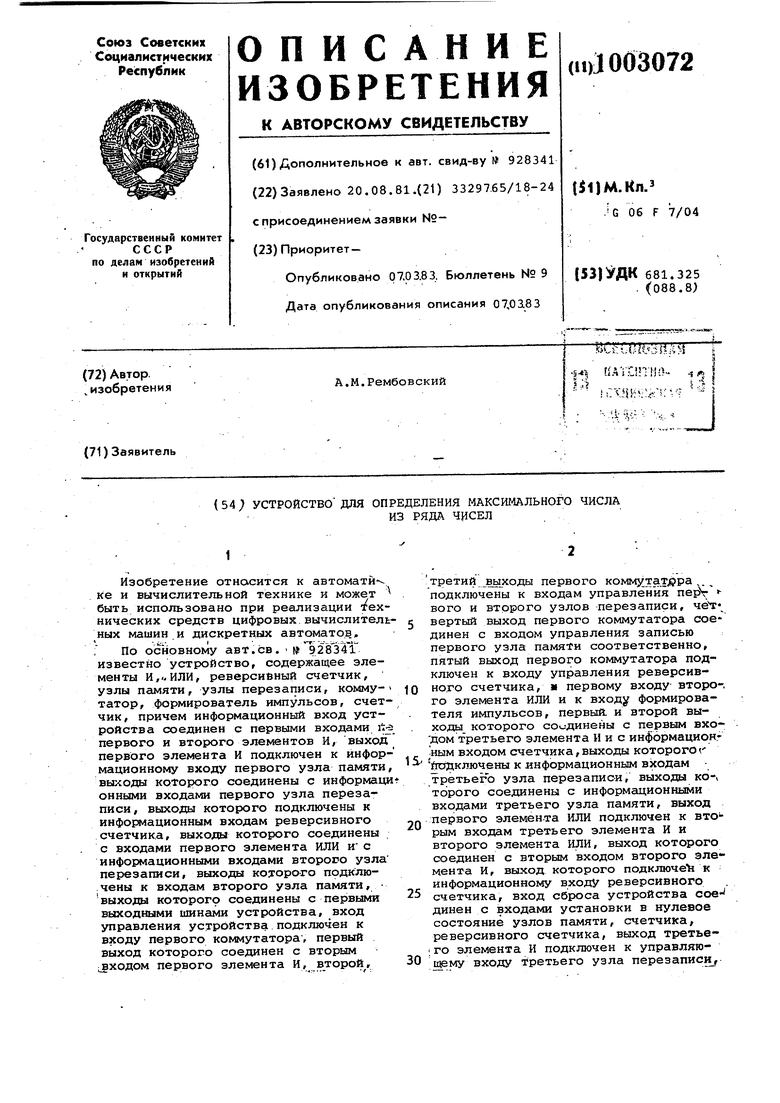

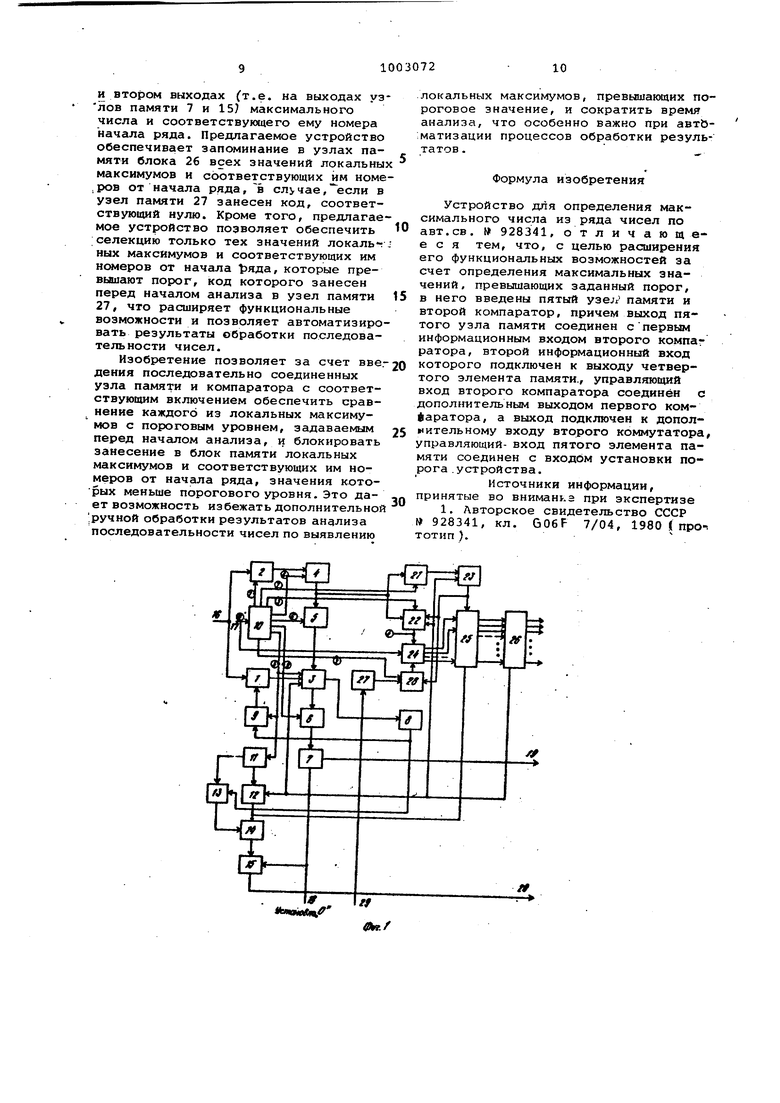

На. фиг.1 представлена структурная схема предлагаемого устройства, на . 65

фиг.2 и 3 - варианты структурных схем компараторов.

Устройство содержит элементы И 1 и, 2, реверсивный счетчик 3, узел памяти 4, узлы перезаписи 5 и б, узел памяти 7, элементы ИЛИ 8 и 9, комму-г татор 10, формирователь импульсов 11 счетчик 12, элемент И 13, узел перезаписи 14, узел памяти 15, информационный вход устройства 16, управляющий вход 17 устройства, вход 18 сброса, выходы 19 и 20 устройства, узел перезаписи 21, компаратор 22, узел памяти 23, коммутатор 24, распределитель 25, блок памяти 26, введенный узел памяти 27, компаратор 28 вход 29 установки порога.

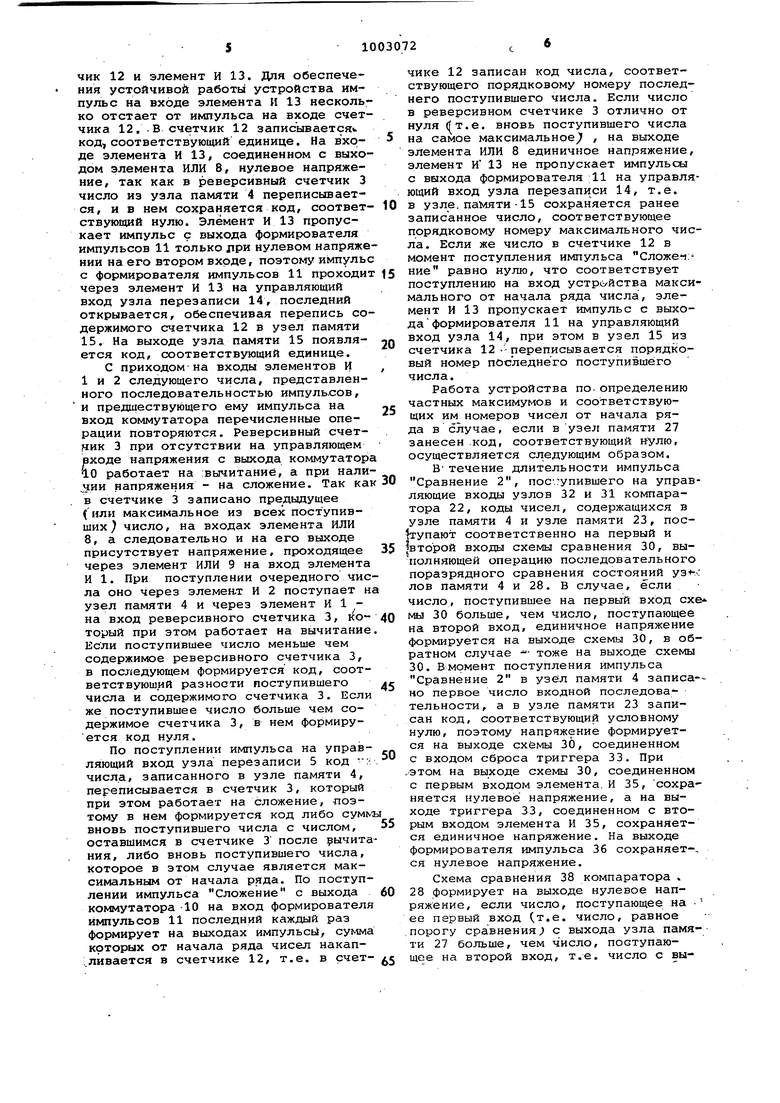

Компаратор 22 (фиг.2) содержит схему сравнения 30, узлы перезаписи 31 и 32, триггер 33, элемент задержки 34, элемент И 35, формирователь 36.

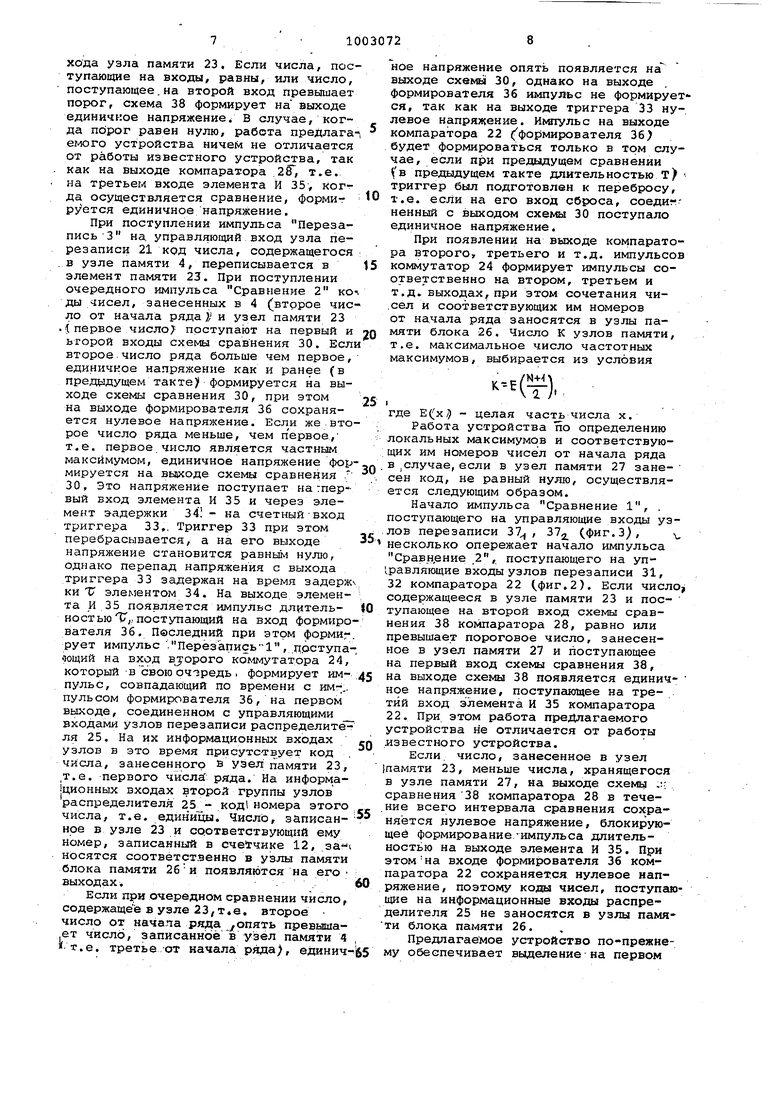

, Компаратор 28 .(фиг.З} содержит узлы перезаписи 37; и 372., схему срав.нения 38.

Устройство работает следующим образом.

Каждому числу, поступающему на вход элементов И 1 .и 2, предшествует импульс, поступающий на входы коммутаторов 10 и 24, при этом коммутатор 10 формирует на выходах импульсы, управляющие работой устройства.

Импульсом, поступающим на вход элмента И 2, последний о.ткрывается и пропускает число с входа 16 устройства на вход узла памяти 4. Элемент И 1 при этом-закрыт, так как в реверсивном счетчике 3 записан код, соответствующий нулю, поз1тому направл ние на выходе элемента ИЛИ В (т.е. на первом входе элемента ИЛИ Э) равно нулю. Напряжение на втором входе элемента ИЛИ 9 при этом также отсутствует, поэтому число через закрытый элемент И 1 на вход реверсивного счетчика 3 не проходит. Коммутатор 10 формирует импульс на управ- ляющем входе узла 5, которым он открывается, и. код числа, записанного в узел памяти 4, переписывается в реверсивный счетчик 3, последний в это время работает на сложение, так как с коммутатора 10 на управляющий вход счетчика 3 поступает импульс Сложение. На управляющий вход узла

перезаписи 6 с .выхода коммутатора 10 поступает импульс, открывающий его, при этом код числа,

:,записанного в счетчике 3, перепи ьшается в узел памяти 7 и

появляется на выходе устройства. Одновременно на управляющий вход узла памяти 4 подается импульс, сбрасыварэщий наполненное в нем число. По пос туплении импульса Сложение на вход формирователя 11 на его выходах появ.ляются импульсы, поступающие на счетчик 12 и элемент И 13. Для обеспечения устойчивой работы устройства импульс на входе элемента Н 13 несколь ко отстает от импульса на входе счет чика 12, -В счетчик 12 записывается, код, соответствующий единице. На вхрде элемента И 13, соединенном с выхо дом элемента ИЛИ 8, нулевое напряжение, так как в реверсивный счетчик 3 число из узла памяти 4 переписывается, ив нем сохраняется код, соответ ствующий нулю. Элемент И 13 пропускает импульс с выхода формирователя импульсов 11 только лри нулевом напряже нии на его втором входе, поэтому импуль с формирователя импульсов 11 проходи через элемент И 13 на управляющий вход узла перезаписи 14, последний открывается, обеспечивая перепись со держимого счетчика 12 в узел памяти 15. На выходе узла памяти 15 появляется код, соответствующий единице. С приходом-на входы элементов И 1 и 2 следующего числа, представленного последовательностью импуль.сов, и предшествующего ему импульса на вход коммутатора перечисленные операции повторяются. Реверсивный счет 1ик 3 при отсутствии на управляющем входе напряжения с выхода коммутатор 10 работает на :вычитаниё, а при нали ,чии напряжения - на сложение. Так ка в счетчике 3 записано предыдущее (или максимальное из всех поступивших число, на входах элемента ИЛИ 8, а следовательно и на его выходе присутствует напряжение, проходящее через элемент ИЛИ 9 на вход элемента И 1. При поступлении очередного чис ла оно через элемент И 2 поступает н узел памяти 4 и через элемент И 1 на вход реверсивного счетчика 3, i oторый при этом работает на вычитание Если поступившее число меньше чем содержимое реверсивного счетчика 3, в последующем формируется код, соответствуюший разности поступившего числа и содержимого счетчика 3. Если же поступившее число больше чем содержимое счетчика 3, в нем формируется код нуля. По поступлении импульса на управляющий вход узла перезаписи 5 код :-: числа, записанного в узле памяти 4, переписывается в счетчик 3, который при этом работает на сложение, поэтому в нем формируется код либо cyMNb вновь поступившего числа с числом, оставшимся в счетчике 3 после рычита ния, либо вновь поступившего числа, которое в этом случае является максимальным от начала ряда. По поступлении импульса Сложение с выхода коммутатора -10 на вход формирователя импульсов 11 последний каждый раз Формирует на выходах импульсы, сумма которых от начала ряда чисел накап..ливается в счетчике 12, т.е. в счетчике 12 записан код числа, соответствующего порядковому номеру последнего поступившего числа. Если число в реверсивном счетчике 3 отлично от нуля ((т.е. вновь поступившего числа на самое максимальное , на выходе элемента ИЛИ 8 единичное напряжение, элемент И 13 не пропускает импульсы с выхода формирователя 11 на управляющий вход узла перезаписи 14, т.е. в узле.памяти-15 сохраняется ранее записанное число, соответствующее порядковому номеру максимального числа. Если же число в счетчике 12 в момент поступления импульса Сложен; ние равно нулю, что соответствует поступлению на вход устро йства максимального от начала ряда числа, элемент И 13 пропускает импульс с выхода формирователя 11 на управляющий вход узла 14, при этом в узел 15 из счетчика 12 переписывается порядковый номер последнего поступившего числа. Работа устройства по-определению частных максимумов и соответствующих им номеров чисел от начала ряда в случае, если в узел памяти 27 занесен код, соответствующий н-улю, осуществляется следующим образом. Втечение длительности импульса Сравнение 2, пос.гупившего на управляющие входы узлов 32 и 31 компаратора 22, коды чисел, содержащихся в узле памяти 4 и узле памяти 23, пос|тупают соответственно на первый и |второй входы схемы сравнения 30, выполняющей операцию последовательного поразрядного сравнения состояний лов памяти 4 и 28. В случае, число, поступившее на первый вход схе мы 30 больше, чем число, поступающее на второй вход, единичное напряжение формируется на выходе схемы 30, в обратном случае тоже на выходе схемы 30. В момент поступления импульса Сравнение 2 в узел памяти 4 записа-но первое число входной последовательности, а в узле памяти 23 записан код, соответствующий условному нулю, поэтому напряжение формируется на выходе схемы 30, соединенном с входом сброса триггера 33. При этом на выходе схемы 30, соединенном с первым входом элемента. И 35, сохраняется нулевое напряжение, а на выходе триггера 33, соединенном с вторым входом элемента И 35, сохраняется единичное напряжение. На выходе формирователя импульса 36 сохраняет-, ся нулевое напряжение. Схема сравнения 38 компаратора . 28 формирует на выходе нулевое напряжение, если число, поступающее на ее первый вход (т.е. число, равное порогу сравнения с выхода узла памяти 27 больше, чем число, поступающее на второй вход, т.е. число с выхода узла памяти 23, Если числа, поступающие на входы, равны, или число, поступающее.на второй вход превышает порог, схема 38 формирует на выходе единичное напряжение/ В случае, когда порог равен нулю, работа предлагал егдаго устройства ничем не отличается от работы известного устройства, так как на выходе компаратора .28, т.е. на третьем входе элемента И 35, когда осуществляется сравнение, формиг руется единичное напряжение.

При поступлении импульса Перезапись 3 на. управляющий вход узла перезаписи 21 код числа, содержащегося в узле памяти 4, переписывается в элемент памяти 23. При поступлении очередного импульса Сравнение 2 ко ды чисел, занесенных в 4 (второе число от начала ряда)/ и узел памяти 23 . f первое число} поступают на первый и второй входы схемы сравнения 30. Есл второе число ряда больше чем первое, единичное напряжение как и ранее (в предыдущем такте) формируется на выходе схемы сравнения 30, при этом на выходе формирователя 36 сохраняется нулевое напряжение. же . вто рое число ряда меньше, чем первое, т.е. первое число является частным максимумом, единичное напряжение фор мируется на выходе схемы сравнения 30, Это напряжение поступает на тпер-вый вход элемента И 35 и через элемент з-адержки 341 - на счетныйвход триггера 33,. Триггер 33 при этом перебрасывается, а на его выходе напряжение становится равньпи нулю, однако перепад напряжения с выхода .триггера 33 задержан на время задерж ки Т элементом 34. На выходе элемента И 35 появляется импулвс длительноетью Т,, поступающий на вход формирователя 36. Пвследний при этом формирует импульс .Перезапись ,поступа оощий на вход Bjoporo коммутатора 24, который в свою оч-эредь . формирует импульс, совпадающий по времени с им-... пульсом формирователя 36, на первом

выходе, соединенном с управляющими

входами узлов перезаписи распределителя 25. На их информационных входах узлов в это время присутстгвует код числа, занесенного в уэел; памяти 23, ,т.е. первого числи ряда. На информа1ционных входах второй группы узлов распределителя 25 - код1 номера этого числа, т.е. единицы. Число, записанное в узле 23 и срответствующий ему Номер, записанный в счеТчике 12, заносятся соответственно в узлы памяти блока памяти 26и появляются на его выходах.. .

Если при очередном сравнении чйсЯо, содержащее в узле 23,Т4в. второе число от начала ряда oпять превышает число, записанное в узел памяти 4

i

т.е. третье от начала ряда), единич

ное напряжение опят1з появляется на выходе схемы 30, однако на выходе формирователя 36 импуяьс не формируется, так как на выходе триггера 33 нулевое напряжение. Иквгульс на выходе компаратора 22 (формирователя 36) будет формироваться только в том случае, если при предыдущем сравнении (в предыдущем такте длительностью Т триггер был подготовлен к перебросу, т.е. если на его вход сброса, соедигненный с выходом схемы 30 поступало единичное напряжение

При появлении на выходе компаратора второго, третьего и т.д. импульсов коммутатор 24 формирует импульсы соответственно на втором, третьем и т.д. выходах, при этом сочетания чи.сел и соответствующих им номеров от начала ряда заносятся в узлы памяти блока 26, Число К узлов памяти, т.е. максимальное число частотных максимумов, выбирается из условия

К--Б(

гУ I

где Е(х5 - целая часть числа х.

Работа устройства по определению локальных максимумов и соответствующих им номеров чисел от начала ряда в ,случае, если в узел памяти 27 занесен код, не равный нулю, осуществляется следующим образом.

Начало импульса Сравнение 1, . поступающего на управляющие входы узлов перезаписи 37.., 372 (фиг.З), несколько опережает начало импульса Сравнение .2, поступающего на уп1равляющие входы узлов перезаписи 31, 32 компаратора 22 фиг.2). Если число содержащееся в узле памяти 23 и поступающее на второй вход схемы сравнения 38 компаратора 28, равно или превышает пороговое число, занесенное в узел памяти 27 и поступающее на первый вход схемы сравнения 38, на выходе схемы 38 появляется единичное напряжение, поступающее на третий вход элемента И 35 компаратора 22. При этом работа предлагаемого устройства не отличается от работы известного устройства.

Если, число, занесенное в узел памяти 23, меньше числа, хранящегося в узле памяти 27, на выходе схемы ,:; сравнения 38 компаратора 28 в тече.ние всего интервала сравнения сохраняется нулевое напряжение, блокирующее формирование -импульса длительностью на выходе элемента И 35. При этомна входе фopмиix5вaтeля 36 компаратора 22 сохраняется нулевое напряжение, поэтому коды чисел, поступающие на информационные входа распределителя 25 не заносятся в узлы памяти блока пагляти 26.

Предлагаемое устройство по-прежнему обеспечивает выделение на первом

и втором выходах (т.е. на выходах узлов памяти 7 и 15) максимального числа и соответствующего ему номера начала ряда. Предлагаемое устройство обеспечивает запоминание в узлах памяти блока 26 всех значений локальных максимумов и соответствующих м номе, ров от начала ряда, в елv чае, если в узел памяти 27 занесен код, соответствующий нулю. Кроме того, предлагаемое устройство позволяет обеспечить селекцию только тех значений локалы ных максимумов и соответствующих им номеров от начала яда, которые превышают порог, код которого занесен перед началом анализа в узел памяти 27, что расширяет функциональные возможности и позволяет автоматизировать результаты обработки последовательности чисел.

Изобретение позволяет за счет вве.дения последовательно соединенных узла памяти и компаратора с соответствующим включением обеспечить сравнение каждого из локальных максимумов с пороговым уровнем, задаваемым перед началом анализа, и блокировать занесение в блок памяти локальных максимумов и соответствующих им номеров от начала ряда, значения которах меньше порогового уровня. Это дает возможность избежать дополнительной .ручной обработки результатов анализа последовательности чисел по выявлению

.лоЕсальных максимумов, превышающих пороговое значение, и сократить время анализа, что особенно важно при автб;матизации процессов обработки результатов.

Формула изобретения

Устройство для определения максимального числа из ряда чисел по авт.св. 928341, отличающееся тем, что, с целью расширения его функциональных возможностей за счет определения максимальных значений, превышающих заданный порог, в него введены пятый памяти и второй компаратор, причем выход пятого узла памяти соединен спервым информационным входом второго компаратора, второй информационный вход которого подключен к выходу четвертого элемента памяти., управляющий вход второго компаратора соединён с дополнительным выходом первого комйаратора, а выход подключен к дополнительному входу второго коммутатора управляющий- вход пятого элемента памяти соединен с входом установки порога .устройства.

Источники информации, принятые во вниманкз при экспертизе

1. Авторское свидетельство СССР 928341, кл. G06F 7/04, 1980 ( про тотип ).

crrfpfiOfifaM

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения максимального числа из ряда чисел | 1980 |

|

SU928341A1 |

| Устройство для определенияМАКСиМАльНОгО чиСлА из РядА чиСЕл | 1979 |

|

SU800990A1 |

| Устройство для определения максимального числа из ряда чисел | 1978 |

|

SU725072A1 |

| УСТРОЙСТВО ДЛЯ УЛЬТРАЗВУКОВОГО КОНТРОЛЯ СВАРНЫХ СОЕДИНЕНИЙ И ИЗДЕЛИЙ | 1990 |

|

RU2018816C1 |

| Устройство для упорядочивания чисел | 1980 |

|

SU932487A1 |

| Устройство для упорядочивания чисел | 1981 |

|

SU1012239A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ НАГРУЖЕНИЕМ ПРИ ПРОГРАММНЫХ ИСПЫТАНИЯХ МЕХАНИЧЕСКИХ КОНСТРУКЦИЙ НА УСТАЛОСТНУЮ ПРОЧНОСТЬ | 2007 |

|

RU2365963C2 |

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1481813A1 |

L.

Авторы

Даты

1983-03-07—Публикация

1981-08-20—Подача