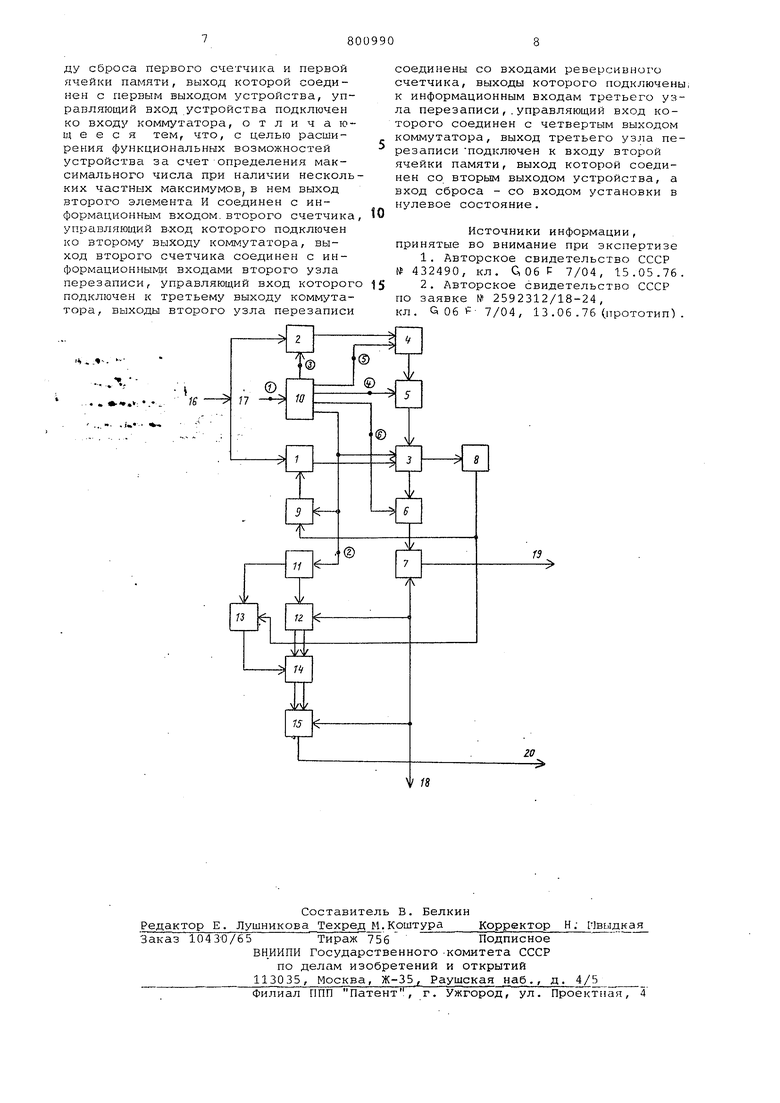

54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МАКСИМАЛЬНОГО ЧИСЛА ИЗ РЯДА ЧИСЕЛ ко входу сброса первого счетчика и первой ячейки памлти, выход которой соединен с первым выходом устройства, управляющий вход устройства подключен ко входу коммутатора 2 . Недостаток этого устройства заключается в том, что оно обеспечивает правильное выделение максимального числа из ряда чисел только в случаях если в поступившей последовательност чисел содержится один максимум. Если поступившей последовательность чисел содержит несколько частных максимумо нормальная работа устройства нарушается и оно не обеспечивает правильно выделение максимального числа. Цель изобретения - расширение фун циональных воэможностерТ устройства за счет определения максимального чи ла при наличии нескольких частных ма симумов . Подтавленная цель достигается тем что в устройстве для определения мак симального числа из ряда ч:исел, содержащем элементы И, реверсивный счетчик, элементы ИЛИ, коммутатор, формирователь импульсов, счетчики, узлы перезаписи, ячейки памяти, причем информационный вход устройства соединен с первыми входами первого и второго элементов И, выход первого элемента И подключен к информационному входу реверсивного счетчика, выходы которого соединены со входами первого элемента ИЛИ, выход которого подключен к первому входу второго элемента ИЛИ, выход которого соедине со вторым входом первого элемента И первый выход ком.мутатора подключен к управляющему входу реверсивного счетчика,- ко второму входу второго элемента ИЛИ и ко входу формирователя импульсов, первый выход которого соединен со входом первого счетчика выходы которого подключены к информационны входам первого узла перезаписи, выход которого соединен со входом первой ячейки памяти, второй вход формирователя импульсов подключен к первому входу третьего §лемента И, второй вход которого соединен с выходом первого элемента ИЛИ, а выход - со входом управления первого узла перезаписи, вход установки в нулевое состояние подключен ко входу сброса первого счетчика и первой . яче ки памяти, выход которой соединен с первым выходом устройства, управляющий вход устройства подключен ко вхо ду коммутатораj выход второго элемента И со динен с информационным входом второго счетчика, управляющий вход которого подключен ко второму выходу коммутатора, выход второго счетчика соединен с информационными входами второго узла перезаписи, уп равляющий вход которого подключен к третьему выходу коммутатора, выходы второго узла перезаписи соединены со входами реверсивного счетчика, выходы которого подключены к информационным входам третьего узла перезаписи, управляющий вход которого соединен с четвертым выходом коммутатора, выход третьего узла перезаписи подключен к входу второй ячейки памяти, выход которой соединен со вторым выходом устройства, а вход сброса - со входом установки в нулевое состояние. На чертеже представлена блок-схема устройства. Устройство содержит элементы И 1 и 2, реверсивный счетчик 3, счетчик 4, узлы 5 и б перезаписи, ячейку 7 памяти, элементы ИЛИ 8 и 9, коммутатор 10, формирователь 11 импульсов, счетчик 12, элемент И 13, узел 14 перезаписи, ячейку 15 памяти, информационный вход 16 устройства, управляющий вход 17 устройства, вход 18 установки в нулевое состояние, выходы 19 и 10 устройства. Устройство работает следующим образом. До поступления на вход устройства анализируемых чисел в реверсивном счетчике 3, в счетчиках 4 и 12, ячейках 7 и 15 памяти записан код, соответствующий нулю.Каждому числу,поступающему на вход элементов И 1 и 2 предшествует импульс,поступающий на вход элементов И 1 и 2,предшествует импульс,поступающий на вход коммутатора 10, который формирует на выходах импульсы, управляющие работой устройства. Поступающий импульс открывает вход элемента И 2, и пропускает число с информационного входа 16 устройства на вход ячейки 4 памяти. Элемент И 17 при этом закрыт, так как в реверсивном счетчике 3 записан код, соответствующий нулю, поэтому на выходе элемента ИЛИ 8 формируется нулевой уровень. На втором входе элемента ИЛИ 9 при этом также нулевой уровень и поэтому число через закрытый элемент И 1 на вход реверсивного счетчика 3 не проходит. Коммутатор формирует импульс на управляющем входе узла 5 перезаписи, которым он открывается, и код числа записанного в счетчике 4, перезаписывается в реверсивный счетчик 3, который в это время работает на сложение, так как с выхода коммутатора 10 на-управляющий вход реверсивного счетчика 3 поступает импульс Сложение . На управляющий вход узла 6 перезаписи выхода коммутатора 10 поступает импульс, открывающий его, при этом код числа, записанного в реверсивном счетчи-ке 3, перезаписывается в ячейку 7 памяти и появляется на выходе устройства 19. Одновременно на управляющий вход счетчика.4 подается импульс, сбрасывающий накопленное на ней число. По поступлении импульса Сложение на вход формирователя 11 импульсов на его выходах появляются импульсы, поступающие на счетчик 12 и элемент И 13. Для обеспечения устойчивой работы устройства импульс на выходе элемента И 13 несколько от стает от импульса на входе счетчика 12, в котором записывается код, соответствующий единице. На входе эле мента И 13, соединенном с выходом элемента ИЛИ 8 поступает нулевой уровень, элемент и 13 пропускает и пульс с выхода формирователя 11 импульсов только при нулевом напряжении на его втором входе; поэтому им пульс с формирователя 11 импульсов проходит через элемента И 13 на управляющий вход узла перезаписи 30 который открывается, обеспечивая пе резапись содержимого счетчика 12 в ячейку 15 памяти, на выходе которой появляется код, соответствующий еди нице . С приходом на входы элементов И 1 и 2 следующего числа, представлен ного последовательностью импульсов, и предшествующего ему импульса на вход коммутатора 10, вышеперечислен ные операции повторяются. Реверсивны счетчик 3 при.нулевом сигнале с выхода коммутатора 10 работает на вычитание, а при наличии единичного сигнала работает на сложение. Так ка в реверсивном счетчике 3 записано пр дыдущее (или максимальное из всех поступивших) число на входах элемен та ИЛИ 8, а следовательно и на его выходе , присутствует сигнал,проходящий через элемент ИЛИ 9, на вход элемент И 1. При поступлении очередного чис ла оно через элемент И 2 записывается в счетчик 4 и через элемент И 1 на вход реверсивного счетчика 3, который при этом работает на вычитание Если поступившее число меньше, чем содержимое реверсивного счетчика 3, в нем формируется код, соответствующ разности поступившего числа и содер жимого реверсивного счетчика 3. Если же поступившее число больше, чем содержимое реверсивного счетчика 3, в нем формируется код нуля. При поступлении импульса на управ ляющий вход узла 5 перезаписи код чи ла, записанный в счетчике 4, перезаписывается в реверсивный счетчик 3, который при этом работает на сложение , поэтому Б нем формируется код либо суммы вновь поступившего числа с числом, оставшимся в реверсивном счетчике 3 после вычитания, либо вно поступившего числа, которое в этом случае является максимальным от начала ряда. По поступлении импульса Сложение с выхода коммутатора на вход формирователя 11 импульсов он каждый раз формирует на выходах импульсы, сумма которых от начала рядг чисел накапливается в счетчике 12, т.е. в нем записан код числа, соответствующий порядковому номеру последнего поступившего числа. Если число в реверсивном счетчике 3 отлично от нуля; (т.е. вновь поступившее число не самое максимальное) на выходе элемента ИЛИ 8 появляется еди-. ничный уровень, И 13 не пропускает импульсы с выхода формирователя импульсов и на управляющий вход узла перезаписи 14, т.е. в ячейке 15 памяти сохраняется ранее записанное число, соответствующее порядковому номеру максимального числа. Если же число в реверсивном счетчике 3 в момент поступления импульса Сложение равно нулю, что соответствует поступлению на вход устройства максимального от начала ряда числа, элемент И 13, пропускает импульс с выхода формирователя 11 импульсов на управляющий вход узла перезаписи 14, при этом в ячейку IS памяти из счетчика 12 перезаписывается порядковый номер последнего поступившего числа. Устройство Обеспечивает ныделение максимального числа из ряда чисел и его порядковый номер для любой совокупности чисел, что рас1ииряет возможность его применения в ряде технических приложений. Формула изобретения Устройство для определения максимального, числа и:з ряда чисел, содержащее элементы И, реверсивный счетчик, элементы ИЛИ, коммутатор, формирователь импульсов, счетчик, узлы перезаписи, ячейки памяти,причем информационный вход устройства соединен с первыми входами первого и второго элементов И, выход первого элемента И подключен к информационному входу реверсивного счетчика, выходы которого соединены со входами первого элемента ИЛИ, выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен со вторым входом первого элемента И, первый выход коммутатора подключен к управляющему входу реверсивного счетчика, ко второму входу второго элемента ИЛИ и ко входу формирователя импульсов, первый выход которого соединен со входом первого счетчика,.выходы которого подключены к информационным входам первого узла перезаписи, выход которого соединен со входом первой ячейки памяти, второй выход формирователя импульсов подключен к первому входу третьего элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, а выход - со входом управления первого узла перезаписи, вход установки в нулевое состояние подключен ко входу сброса первого счетчика и первой ячейки памяти, выход которой соединен с первым выходом устройства, управляющий вход устройства подключен ко входу коммутатора, отличающееся тем, что, с целью расширения функциональных возможностей устройстве за счет определения максимального числа при наличии нескольких частных максимумов, в нем выход второго элемента И соединен с информационным входом.второго счетчика, управляющий в-ход которого подключен ко второму выходу коммутатора, выход второго счетчика соединен с инфopмaциoнны IИ входами второго узла перезаписи, управляющий вход которого подключен к третьему выходу коммутатора, выходы второго узла перезаписи

соединены со входами реверсивного счетчика, выходы которого подключены к информационным входам третьего узла перезаписи,.управляющий вход которого соединен с четвертым выходом коммутатора, выход третьего узла перезаписи подключен к входу второй ячейки памяти, выход которой соединен со вторым выходом устройства, а вход сброса - со входом установки в нулевое состояние.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

№ 432490, кл. G, 06 Р 7/04, 15.05.76.

2.Авторское свидетельство СССР по заявке № 2592312/18-24,

кл. G 06 Р- 7/04, 13.06 .76 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения максимального числа из ряда чисел | 1980 |

|

SU928341A1 |

| Устройство для определения максимального числа из ряда чисел | 1981 |

|

SU1003072A2 |

| Устройство для упорядочивания чисел | 1981 |

|

SU1012239A1 |

| Устройство для определения максимального числа из ряда чисел | 1978 |

|

SU725072A1 |

| Устройство для упорядочивания чисел | 1980 |

|

SU932487A1 |

| Устройство для ранжирования чисел | 2022 |

|

RU2792182C1 |

| Устройство для упорядочивания чисел | 1983 |

|

SU1144103A1 |

| Устройство циклового фазирования аппаратуры передачи дискретной информации | 1989 |

|

SU1626432A1 |

| Устройство для матричных вычислений | 1980 |

|

SU938286A1 |

| Устройство для контроля цифровыхОб'ЕКТОВ | 1978 |

|

SU798844A1 |

Авторы

Даты

1981-01-30—Публикация

1979-04-16—Подача