Изобретение относится к автомата ке и вычислительной технике и может быть Использовано при реализации технических средств цифровых вычислительных машин и дискретных автоматов .

Известно устройство для сравнения чисел, содержащее регистры,элементы И, ИЛИ 1.

Недостатком этого .устройства является сложность.

Наиболее близким к изобретению является устройство, содержащее, элементы И, реверсивный счетчик, элементы ИЛИ, коммутатор, формирователь импульсов, счетчики, узлы перезаписи, элементы памяти, причем информационный вход устройства соединен с первыми входами первого)и второго элементов И, выход первого элемента И подключен к информационному входу реверсивного счетчика, выходы которого соединены со входами первого элемента ИЛИ, выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен со вторым входом первого элемента И, первый выход коммутатора подключен к управляющему входу реверсивного счетчика, ко второму

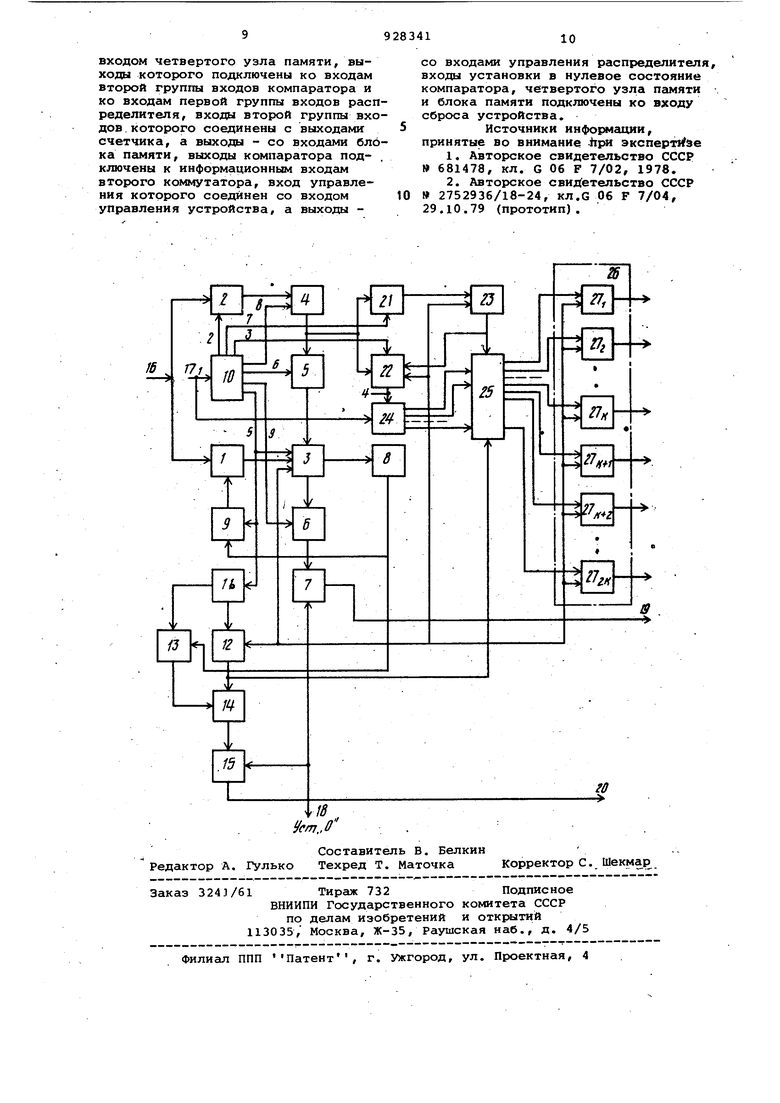

входу второго элемента ИЛИ и ко входу формирователя импульсов, первый выход которого соединен со входом первого счетчика, выходы которого подключены к информационным входам первого узла перезаписи, выход которого соединен со входом первого элемента памяти, второй выход формирователя импульсов подключен к niepsoму входу третьего элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, а выход - со входом управления первого узла перезаписи , вход установки в нулевое состояние подключен ко входам сброса первого счетчика, реверсивного счетчика и. первого элемента-Пс1мяти, выход которого соединен с первым выходом устройства, управляющий вход устройства подключен ко входу коммутатора, причем выход второго элемента И соединен с информационным входом второго счетчика, управляющий вход которого подключен ко второму выходу коммутатора, выход второго счетчика соединен с информационными входами второго узла перезаписи, управляющий вход которого подключен к третьему выходу коммутатора, выходы второго узла перезаписи соелийены со ;входами реверсивного счетчика, выходы которого подключены к информационным входам третьего узла перезаписи, управляющий -вход которбго соединен с четвертым выходом коммутатора, пятый выход которого подключен ко второму входу второго элемента И, выход третьего узла перезаписи подключен ко входу второго элемента памяти, выход которого соединен со вторьал выходом уст ройства, а вход сброса - со входом установки в нулевое состояние. Уст.ройство позволяет определить максимальное число из ряда чисел при наличин нескольких частных максимумов ( Недостатком такого устройства является Невозможность определения уровней частных максимумов и соответствующих им номеров от начала ряда чисел.. Цель изобретения - расширение функциональных возможностей устройства за счет определения значений локальных максимумов и их порядковых номеров. Поставленная цель достигается тем что в устройстве для определения максимального числа из ряда чисел, содержащем элементы И, ИЛИ, ре версивный счетчик, узлы памяти, узл перезаписи, коммутатор формирователь импульсов, счетчик, причем информационный вход устройства соединен с первыми входами первого и вто рого элементов И, выход первого элемента И подключен к информационному входу первого узла памяти, выходы которого соединены с информационны ш входами первого узла перезаписи, выходы крторогр подключены к информационным,вход;ам реверсивног счетчика, выходы которого соединены со входами первого элемента ИЛИ и с информационными входами второго узл перезаписи,входы которого подключен ко входам второго узла памяти/выход которого соединены с первыми выходными шинами у стройствй, вход управ7 ления устройства подключён ко входу первого коммутатора, первый выход которого соединен со вторым входом первого элемента И, второй, третий и четвертый выходы первого коммутатора подключены ко входам управления первого и второго узлов перезаписи соответственно, четвертый выхо первого коммутатора соединен со вхо дом управления записью первого узла памяти, пятый выход первого.коммутатора подключен ко входу управлени реверсивного счетчика, к первому входу второго элемента ИЛИ и ко вхо ду формирователя импульсов, первый и второй выходы которого соединены с первым входом третьего элемента И и с информационным входом счётчика, выходы которого подключены к информационным входам третьего узла перезаписи, выходы которого соединены с информационными входами третьего памяти, выход первого элемента ИЛИ подключен ко вторым входам третьего элемента И и второго элемента ИЛИ, выход которого соединен со вторым входом второго элемента И, выход которого подключен к информационному входу реверсивного счетчика, вход сброса устройства соединён со входами установки в нулевое состояние узлов памяти счетчика, реверсивного счетчика, выход третьего элемента И подключен к управляющему входу третьего узла перезаписи, введены блок памяти, распределитель, четвертый узел перезаписи, четвертый узел памяти, компаратор, причем выход первого узла памяти соединен с информационными входами четвертого узла перезаписи и со входами первой группы входов компаратора, шестой И седьмой выходы первого кЪммутатора подключены к управляющим входам компаратора и четвертого узла перезаписи соответственно, выход четвертого узла перезаписи соединен с информационным входом четвертого узла памяти, выходы которого подключены ко входам второй группы входов компаратора и ко входам первой группы входов распределителя, входы второй группы входов которого соединены с .вых:одами счетчика, авыходы - со :Входа№1 блока памяти, выходы компаратора подключены к информационным рходам второго ком утатора, вход управления которого соединен со входом управления устройства, а выходы со входами управления распре- . делителя, вхрды установки в нулевое состояние компаратора, четвертого узла памяти и блока памяти подключены ко ВХОДУ сброса устройства. На чертежепредставлена блок-схема устройства. Устройство содеЕЯкит элементы И 1 и 2, реверсивный счетчик 3, узел памяти 4, узлы перезаписи 5 и б, узел памяти 7/ элементы ИЛИ 8 и 9, коммутатор 10 ,фО1Ж1Ирователь импульсов 11, счётчик; 12, элемент И 13, узел перезаписи 14f узел памяти 15, Информационный вход 16, вход упрайления 17, вход сброса 18, выходы устройства 19 и 20, узел перезаписи 21, компаратор 22, узел памяти 23, коммутатор 24, распределитель 25, узел памяти 26, состоящий из элементов памяти 27t 27t. , ...27 . Работа известного устройства осущестеляется следующим образом. , Каждому числу, поступающему на 8ХОД элементов И 1 и. 2, предшествует импульс, поступающий на входы коммутаторов 10 и 24, При этом коммутатор 10 формирует на выходах импульсы, управляющие работой устройства. Импульсом, поступающим На вход элемента И 2j последний отк1 лвается и пропускает число со входа 16 устройства на вход счетчика 4. Элемент И 1 при этом закрыт, .так как в реверсивном счетчике 3 записан код, соответ ствующий нулю, поэтому напряжение на выходе элемента ИЛИ 8 (т.е. на первом входе элемента ИЛИ 9) равно нулю. Напряжение на втором входе элемента ИЛИ 9 при этом также отсутствует, поэтому число через закрытый элемент И 1 на вход реверсивного счетчика 3 не проходит. Коммутатор 10 формирует импульс на управляющем входе узла 5, которым он отк1 тается,и код числа, записанного в счетчике 4, переписывается в реверсивный счетчик 3. Последний в это время работает на сложение, так как с коммутатора 10 на управляющий вход счетчика 3 поступает, импульс. сложение .. На упра вляющий вход узла перезаписи 6 с выхода коммутатора Ю поступает имдульс, отк|зывающий его, при. этом код числа, записанного в счетчике 3, переписывается в элемент памяти 7 и появляеся на выходе устройства. Одновременно на управляющий вход счетчика подается импульс, сбрасывающий накопленное в нем число. По поступлесложение

нии импульса

на вход

формирователя 11на его выходах появляются импульсы. Поступающие на счетчик 12 и элемен.т И 13. Для обеспечения устойчивой работы устройства импульс на взЯэде И 13 несколько отстает от импульса на входе счетчика 12. В счетчик 12 записывается код, соответствующий единице. На входе элемента И 13, соединенном с выходом элемента ИЛИ 8, в этом интервале времени нулевое напряжение, так как в реверсивный счетчик 3 число из счетчика 4 перезаписывается, а до этого момента в нем сохраняется код,.соответствующий нулю. Элемент И 13 пропускает импульс с выхода формирователя только при нулевом Напряжении на его втором входе., поэтому импульс с формирователя проходит через элемент И 13 на управляющий вход узла перезаписи 14, последний открывается, обеспечивая перезапись содержимого счетчикА 12 в элемент памяти 15. На выходе элемента 15 появляется код, соответствую11у1й единице. С приходом на входы элементов И 1 и 2 следующего числа, представленного последовательностью импульсов, и предшествующего ему импульса на вход коммутатора 10 перечисленные операции повторяются. Реверсивный счетчик 3 при отсутствии на управляющем входе напряжения с выхода коммутатора 10 работает

на вычитание, а при наличии напс яжения - на сложение. Так как в счетчике 3 записано предыдущее (или максимальное из всех поступивших) число, на входах элемента ИЛИ 8, а, следовательно, и на ее выходе при-, сутствует напряжение, проходящее через элемент ИЛИ 9 на вход элемента И 1 . При поступлении очередного числа оно через элемент И 2 поступает на счетчик 4 и через И 1 - на

o вход реверсивного счетчика 3, который при этом работает на вычитание. Если поступившее число меньше,чем содержимое реверсивного счетчика 3, в последнем формируется код соот5ветствующий разности поступившего числа и содержимого счетчика 3. Бели же поступив.шее число болыие, чем содержимое счетчика 3, в нём фо1 даруется код нуля. По поступлении им0пульса на управляющий вход узла перезаписи .5 код числа, записанного в счетчике 4, переписывается в счетчик 3, который при этом работает на сложение, поэтому в нем формируется код либо сумуы вновь поступившего

5 числа с числом, оставшимся в- счетчике 3 после вычитания, либо вновь поступившего числа, которое в этом случае является максимальным от начали ряда. По поступлении импульса слежение

D с выхода коммутатора 10 на вход формирователя импульсов 11 последний каждый раз формирует на выходах импульсы, сумма которых от начала ряда чисел накапливается в счетчике 12,

5 т.е. в счетчике 12 записан код чИс|ла, соответствующего порядковому номеру последнего поступившего числа. Если число в ревер сивном счетчике 3 отлично от нуля (т.е. вновь посту0пившее число не самое максимальное) на выходе.элемента ИЛИ 8 - единичное напряжение, элемент И 13 не пропускает импульсы с выхода формирователя 11 на управляющий вход узла перезаписи 14, т.е. в элементе памя- .

5 ти 15 сохраняется ранее записанное / число, соответствующее порядковому номеру максимального числа. Если же число в счетчике 13 в момент поступления импульса сложение равно

0 нулю, что соответствует поступлению на вход устройства максимёшьного от начала ряда числа, элемент И 13 .пропускает импульс с выхода формирователя 11 на управляющий вход узла

5 14, njMi этом в элемент 15 из счетчика 12 перезаписывается порядковый номер последнего поступившего числа.

Работа устройства по определению частных максимумов и соответствующих

0 им номеров чисел от начала ряда осуществляется следующим образом.

В течение длительности импульса сравнение, поступающего иа управляющий вход компаратора 22 с выхода коммутатора 10, коды чисел.

5

содержа;«ихсяв счетчике 4 и узла па j мяти 23, поступают соответственно на первый и второй входы компаратора. В момент поступления импульса сравнение в счетчике 4 записано первое число входной последовательности, а В узле памяти 23 записан код, соответствующий условному нулю. При этом на выходе компаратора 22 сохраняется нулевое напряжение. При поступленик очередного импульса сравнение коды чисел, занесенных в счетчик 4 (второе число от начала ряда) и узел 23 (первое.число) поступают на первый и второй входа компаратора. Если йторОе число ряда больше,чем первое,на ,выходе компаратора 22 сохраняется нулевое напряже-; ние.Если же второе число ряда меньше: чем первое,т.е.первое число являет- i ся частным максимумом, компаратор 22 формирует на выходе импульс,поступающий на вход второго коммутатора 24, который в свою очередь формирует срвпадающий по времени импульс на перв.ом управляющем входе распределителя 25. На информационных входах первой группы входов распределителя в это время присутствует код числа, занесенного в узел памяти 23, т.е. первого числа ряда, а на информационных входах второй группы - код номера этого числа, т.е, единицы. Число, записанное в узле 23 И соответствующий ему номер от начаа числового ряда, заносятся в элеенты памяти 27 и 21 km узла памяти 26 и появляются на его выходах. Если при очередном сравнении число, соержащее в узле. 23 (т.е. второе чисо от начала ряда), опять превьшает число, занесенное в счетчик 4 (т.е. третье от начала ряда), импульс на выходе компаратора не формируется.

При появлении на выходе компаратора второго, третьего и т.д. импульсов коммутатор 24- формирует им- пульсы соответственно на втором, третьем и т.д. выходах, при этом числа и соответствующие им номера от начала ряда заносятся в соответствующие элементы памяти узла 26.

Предлагаемое устройство по сравнению с известньгм обеспечивает дополнительно запоминание значений частных максимумов и соответствующих им номеров, что расширяет функциональные возможности.

Формула изобретения,

Устройство для определения мак симального числа из ряда чисел, содержащее элементы И, ИЛИ, реверсивный счетчик, узлы памяти, узлы перезаписи, коммутатор, -формирователь импульсов, счетчик, причем информаиноиный вход устройства сое.динен с

первыми входами первого и второго элементов И, выход первого элемента И подключен к информационному входу первого узла памяти, выходы которого соединены с информационными входами первого урла перезаписи, выходы которого подключены к информационным входам реверсивного, счетчика, выходы которого соединены со входами первого элемента ИЛИ и с информационными входами второго узла перезаписи,, выходы которого подключены ко входам второго узла памяти, выходы которого соединены с первыми выходными шинами устройства, вход управления устройства подключен ко входу первого коммутатора, первый выход которого соединен со вторым входом первого элемента И, второй, третий и четв;ертый выходы первого коммутатора подключены ко входам управле/ шя /первого и второго узлов перезаiписи соответственно, четвертый выход первого коммутатора соединен со входом управления записью первого узла памяти, пятый выход первого коммутатора подключен ко входу уп- , равления реверсивного счетчика, к первому входу второго элемента ИЛИ и ко входу формирователя импульсов, первый и второй вьлходы которого соединены с первым входом третьего элемента и и с информационным входом счетчика , выходы, которого подключены к информациЬнныг.1 входам третьего узла перезаписи, выходы которого йоединены с информационными Е гсодами третьего узла памяти, выход первого элемента ИЛИ подключен ко вторым входам третьего элемента И и второго элемента ИЛИ, выход которого соединен со вторым входом второго элемента И, выход которого подключен к информационному входу реверсивного счетчика, вход сброса устройства соединен- со входами установки в нулевое состояние узлов памяти, счетчика, реверсивного счетчика, выход третьего элемента И подключен к управляющему входу третьего узла перезаписи, отличающеес ятем, что, с целью расширения функциональных возможностей за счет определения значений локальных максимумов и их порядковых номеров, в него введены блок памяти, распределитель, четвертый узел перезаписи, Четвертый узел памяти, компаратор, причем выход первого узла памяти соединен с информационными входами Четвертого узла перезаписи и со входами первой, группы входов компаратора, шестой и седьмой выходы первого компаратора подключены к управляющим входам компаратора и четвертого узла перезаписи соответственно, выход четвертого узла пе5 ,оея1аписи соединен с ин(Ьормациоин1лм

входом четвертого узла памяти, выходы которого подключены ко входам второй группы входов компаратора и ко входам первой группы входов распределителя, входы второй группы входов, которого соединены с выходами счетчика, а выходы - со входами блбка памятиf выходы компаратора подключены к информационным входгии второго коммутатора, вход управления которого соединен со входом управления устройства, а выходы со входами управления распределителя, входы установки в нулевое состояние компаратора, четвертого узла памяти и блока памяти подключены ко входу сброса устройства.

Источники информации, принятые во внимание -йри эксперт1 де

1.Авторское свидетельство СССР 681478, кл. G Об F 7/02, 1978.

2.Авторское свид етельство СССР 2752936/18-24, кл.С 06 F 7/04, 29.10.79 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения максимального числа из ряда чисел | 1981 |

|

SU1003072A2 |

| Устройство для определенияМАКСиМАльНОгО чиСлА из РядА чиСЕл | 1979 |

|

SU800990A1 |

| Устройство для упорядочивания чисел | 1981 |

|

SU1012239A1 |

| Устройство для упорядочивания чисел | 1980 |

|

SU932487A1 |

| УСТРОЙСТВО ДЛЯ УЛЬТРАЗВУКОВОГО КОНТРОЛЯ СВАРНЫХ СОЕДИНЕНИЙ И ИЗДЕЛИЙ | 1990 |

|

RU2018816C1 |

| Устройство для определения максимального числа из ряда чисел | 1978 |

|

SU725072A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для упорядочивания чисел | 1983 |

|

SU1144103A1 |

| Устройство для регистрации информации | 1982 |

|

SU1167635A1 |

Авторы

Даты

1982-05-15—Публикация

1980-04-07—Подача