(5) ЗАПОМИНАЮУ1ЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка запоминающего устройства | 1979 |

|

SU879749A1 |

| Однотактный регистр сдвига | 1979 |

|

SU826424A1 |

| Полупроводниковый элемент памятидля пОСТОяННОгО зАпОМиНАющЕгО уСТРОйСТВА | 1979 |

|

SU824313A1 |

| Интегрирующий частотомер | 1985 |

|

SU1308921A1 |

| СПОСОБ ПОЛУЧЕНИЯ АМОРФНЫХ ПЛЕНОК ХАЛЬКОГЕНИДНЫХ СТЕКЛООБРАЗНЫХ ПОЛУПРОВОДНИКОВ С ЭФФЕКТОМ ФАЗОВОЙ ПАМЯТИ | 2016 |

|

RU2631071C2 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Магнитное запоминающее устройство с самоконтролем | 1984 |

|

SU1169025A1 |

| Способ записи голограмм | 1976 |

|

SU570281A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU875642A1 |

| Многоканальный резонансный коммутатор | 1985 |

|

SU1298891A1 |

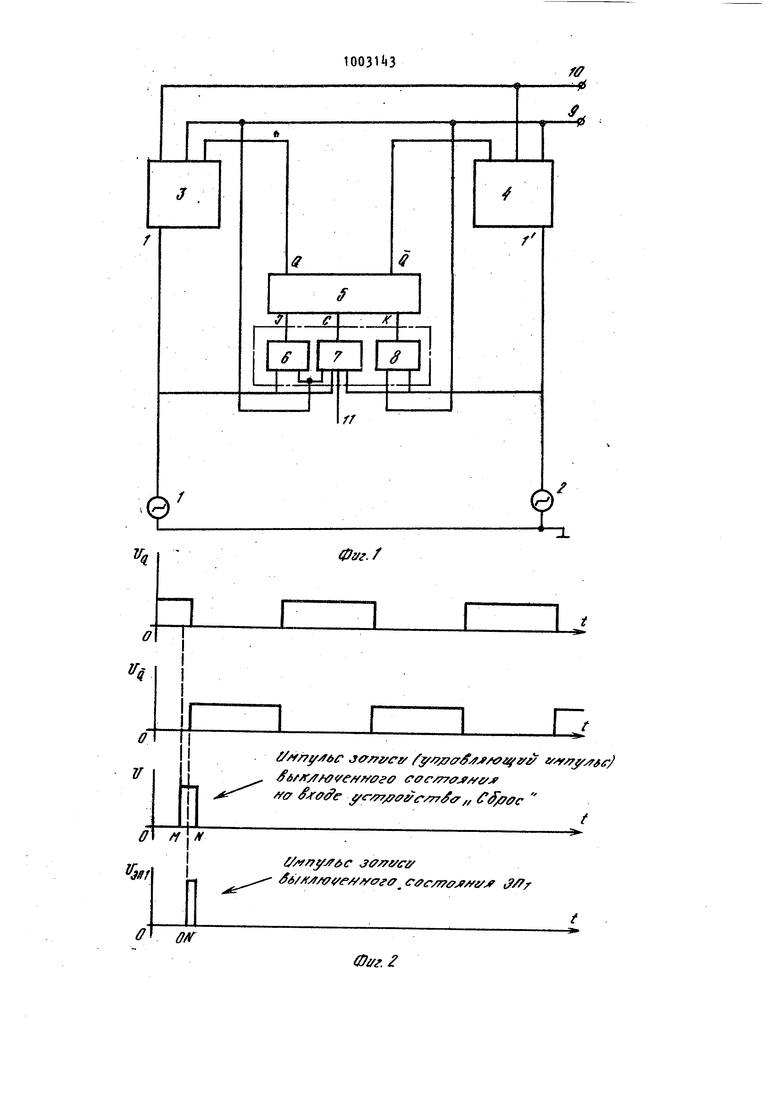

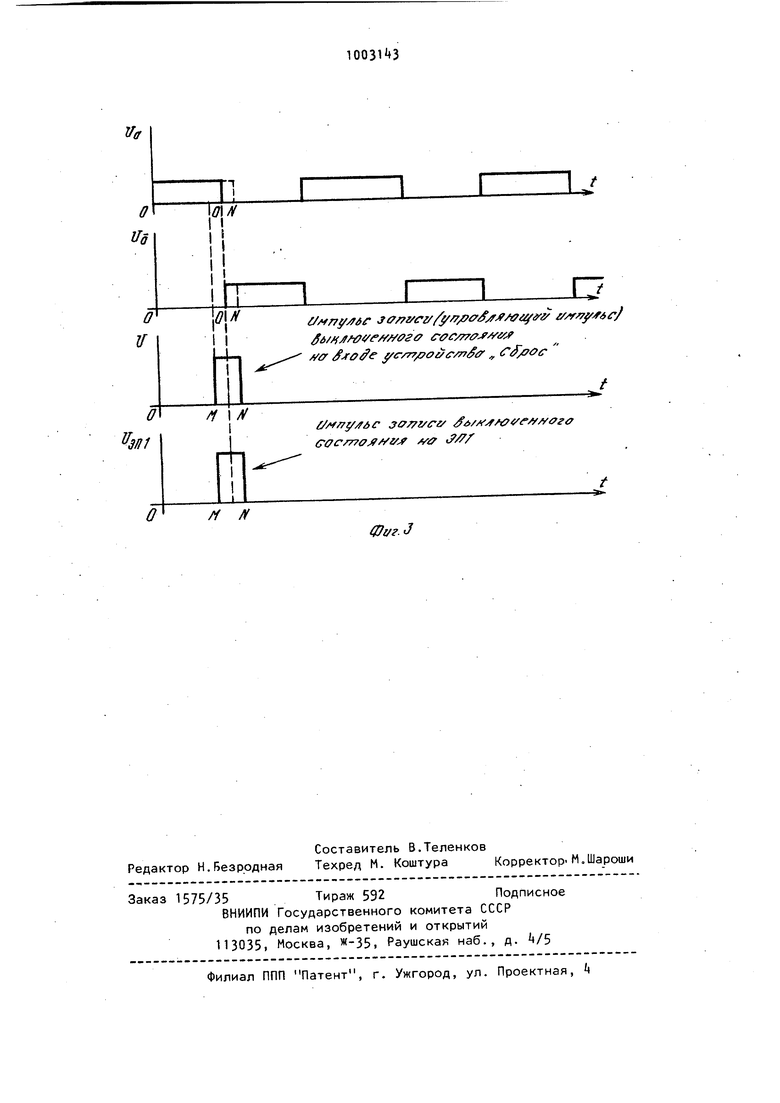

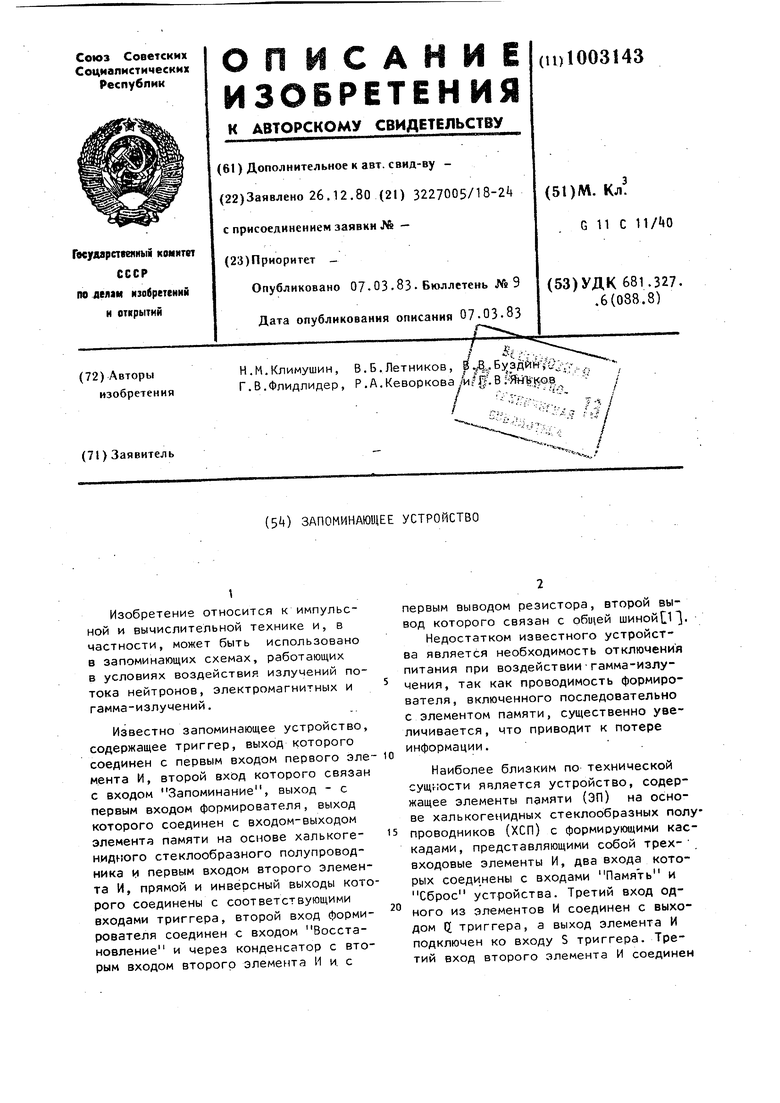

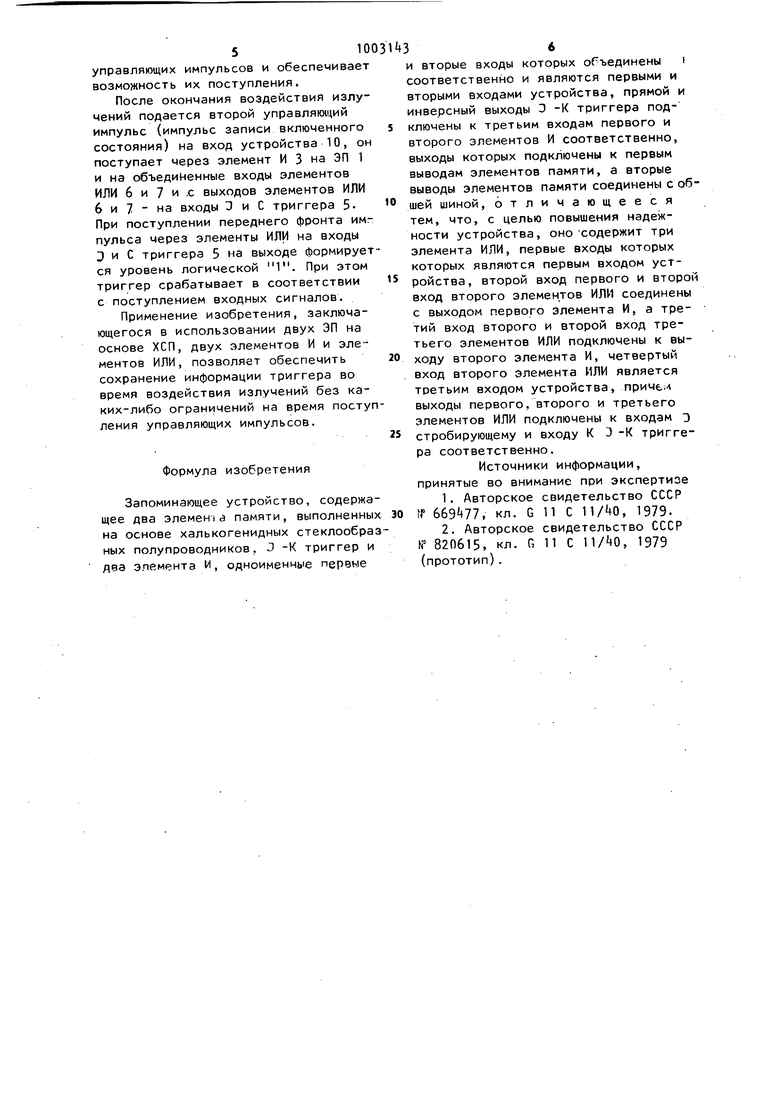

Изобретение относится к импульсной и вычислительной технике и, в частности, может быть использовано в запоминающих схемах, работающих в условиях воздействия, излучений потока нейтронов, электромагнитных и гамма-излучений. Известно запоминающее устройство содержащее триггер, выход которого соединен с первым входом первого эле мента И, второй вход которого связан с входом Запоминание, выход - с первым входом формирователя, выход которого соединен с входом-выходом элемента памяти на основе халькогенидного стеклообразного полупроводника и первым входом второго элемен та И, прямой и инверсный выходы кото рого соединены с соответствующими входами триггера, второй вход форми рователя соединен с входом Восстановление и через конденсатор с вто рым входом второго элемента И и. с первым выводом резистора, второй вывод которого связан с общей шиной Т. Недостатком известного устройства является необходимость отключения питания при воздействиигамма-излучения, так как проводимость формирователя, включенного последовательно с элементом памяти, существенно увеличивается , что приводит к потере информации. Наиболее близким по технической сущности является устройство, содержащее элементы памяти (ЭП) на основе халькогеиидных стеклообразных полупроводников (ХСП) с формирующими каскадами, представляющими собой трех-, входовые элементы И, два входа которых соединены с входами Память и Сброс устройства. Третий вход одного из элементов И соединен с выходом (J триггера, а выход элемента И подключен ко входу S триггера- Третий вход второго элемента И соединен 310 с выходом триггера Q, а выход его подключен к входу R триггера 2} . Недостатком такого устройства является возможность сбоев в работе ЭП при совмещении управляющих импульсов фронтами импульсов тактовой частоты. В случае совмещения управляющих импульсов фронтами импульсов, поступающих с выходов триггера, может произойти сбой в работе ЭП, т.е. может не произойти переключения ЭП в требуемое состояние. Цель изобретения - повышение надежности запоминающего устройства. Указанная цель достигается тем, что запоминающее устройство, содержащее два элемента памяти, выполненных ня основе халькогенилних стеклообразных полупроводников, 3-К триггер и два элемента И, одноименные первые и вторые входы которых объеди нены соответственно и являются первыми и вторыми входами запоминающего устройства, прямой и инверсный выходы 3-К триггера подключены к третьим входам первого и второго элементов И соответственно, выходы которых подключены к первым выводам элементов памяти, а вторые выводы элементов памяти соединены с общей шиной, включает три элемента ИЛИ, первые входы которых объединены и являются первым входом запоминающего устройства, второй вход первого и второй вход второго элементов ИЛИ соединены с выходом первого элемента И, а третий вход вто рого и второй вход третьего элементов ИЛИ подключены к выходу второго элемента И, четвертый вход второго элемента ИЛИ является третьим входом запоминающего устройства, причем выходы первого, второго и третьего элементов ИЛИ подключены к входам 3, стробирующему и входу К 3-К триггера соответст венно. На.фиг.1 представлена функциональная схема запоминающего устройства; на фиг.2 - временная диаграмма, иллюстрирующая, работу устройства при поступлении на него управляющего сигнала с входа Сброс ; на фиг.З - временная диаграмма, иллюстрирующая работу устройства при поступлении на него второго управляющего сигнала с входа Память.i Запоминающее устройство содержит элементы 1 и 2 памяти 1ЭП), на основе ХСП, элементы И 3 и , триггер 5, 34 элементы ИЛИ 6, 7 и 8. Вход 9 запоминающего устройства соединен с первыми входами элементов И 3 и 4 и первыми входами элементов ИЛИ 6, 7 и 8. Вход 10 запоминающего устройства подключен к вторым входам элементов И 3 и Ц. Первые выводы ЭП 1 и 2 подключены к общей шине, вторые выводы соединены с выходами элементов И 3 и i и входами элементов ИЛИ 6, 7 или 7, 8 соответственно. Третий вход элемента ИЛИ 7 , соединен с входом синхронизации 11. Выходы элементов ИЛИ 6, 7 и 8 связаны с входами П, С и К триггера 5. Прямой и инверсный выходы триггера 5 соединены с соответствующими входами элементов И 3 и t. До подачи управляющего сигнала на вход устройства 9 триггер 5 функц- онирует в-соответствии с поступающими на него импульсами тактовой частоты, так как ЭП 1 и 2 находятся во включенном (низкоомном) состоянии и не меиают работе триггера 5. Схема работает следующим образом. До воздейстрия излучений ма вход устройства подается управляющий импульс (импульс записи включенного (высокоомного)) состояния. ЕСЛИ в этот момент логическая 1 находится , например, на выходе триггера, то управляю1ций импульс через элемент И 3 поступает на ЭП 1 и переводит его В выключенное состояние. Управляющий импульс одновременно с поступлением на ЭП 1 поступает на объединенные входы элементов ИЛИ и с выходов этих элементов - на входы 3 и С триггера 5. Это обеспечивает сохранение заданной длительности управляющих сигналов, поступающих на вход ЭП 1 в случае совмещения управляющего сигнала на временной интервал MN при работе триггера 5 (фиг.2). Для запоминающего устройства для совмещении управляющего импульса (импульса записи выключенного состояния) на временной интервал MN происходит небольшой, не превышающий длительности управляющего импульса rjlO мкс) временной сдвиг ON (фиг.З) логической 1 или логического О на входах 3 и К три1- гера 5.и соответственно на выходах Q и Q. При этом сохраняется длительность управляющего импульса, поступающего на ЭП, что исключает сбои в работе ЭП при изменении длительности

управляющих импульсов и обеспечивает возможность их поступления.

После окончания воздействия излучений подается второй управлякнций импульс (импульс записи включенного состояния) на вход устройства 10, он поступает через элемент И 3 на ЭП 1 и на объединенные входы элементов ИЛИ 6 и 7 и .с выходов элементов ИЛИ 6 и 7 на входы D и С триггера 5. При поступлении переднего фронта имг пульса через элементы ИЛИ на входы Э и С триггера 5 на выходе формируется уровень логической 1. При этом триггер срабатывает в соответствии с поступлением входных сигналов.

Применение изобретения, заключающегося в использовании двух ЭП на основе ХСП, двух элементов И и элементов ИЛИ, позволяет обеспечить сохранение информации триггера во время воздействия излучений без каких-либо ограничений на время поступления управляющих импульсов.

Формула изобретения

Запоминающее устройство, содержащее два элемен1а памяти, выполненных на основе халькогенидных стеклообразных полупроводников. J -К триггер и два элемента И, одноименнье первые

и вторые входы которых объединены i соответственйо и являются первыми и вторыми входами устройства, прямой и инверсный выходы Э -К триггера подключены к третьим входам первого и второго элементов И соответственно, выходы которых подключены к первым выводам элементов памяти, а вторые выводы элементов памяти соединены с обшей шиной, отличающееся тем, что, с целью повышения надежности устройства, оносодержит три элемента ИЛИ, первые входы которых которых являются первым входом устройства, второй вход первого и второ вход второго элементов ИЛИ соединены с выходом первого элемента И, а третий вход второго и второй вход третьего элементов ИЛИ подключены к выходу второго элемента И, четвертый вход второго элемента ИЛИ является третьим входом устройства, причем выходы первого/второго и третьего элементов ИЛИ подключены к входам Э стробирующему и входу К Э -К триггера соответственно.

Источники информации, принятые во внимание при экспертизе

1003ЙЗ

s

с

Фг/г.

v

II-r 1Г I

о

4 1 0

0 0/r

fff

-46

ll

фуг. 2 f//f/7y 6f y/ a jf / ityyj AfA/j ye n ffeff /ya f/ /fffy{r rr7 ty , f /ffffc l//Vf y AC Jff i/C-ff s/ f/f/ff eA /j ffeff cffc/7 ffjf f/j /7

О

/i /If

Фuг.J

Авторы

Даты

1983-03-07—Публикация

1980-12-26—Подача