Изобретение относится к измерительной технике и предназначено для преобразования частотно-временных сигналов в цифровой код.

Цель изобретения - расширение функциональных возможностей частотомера.

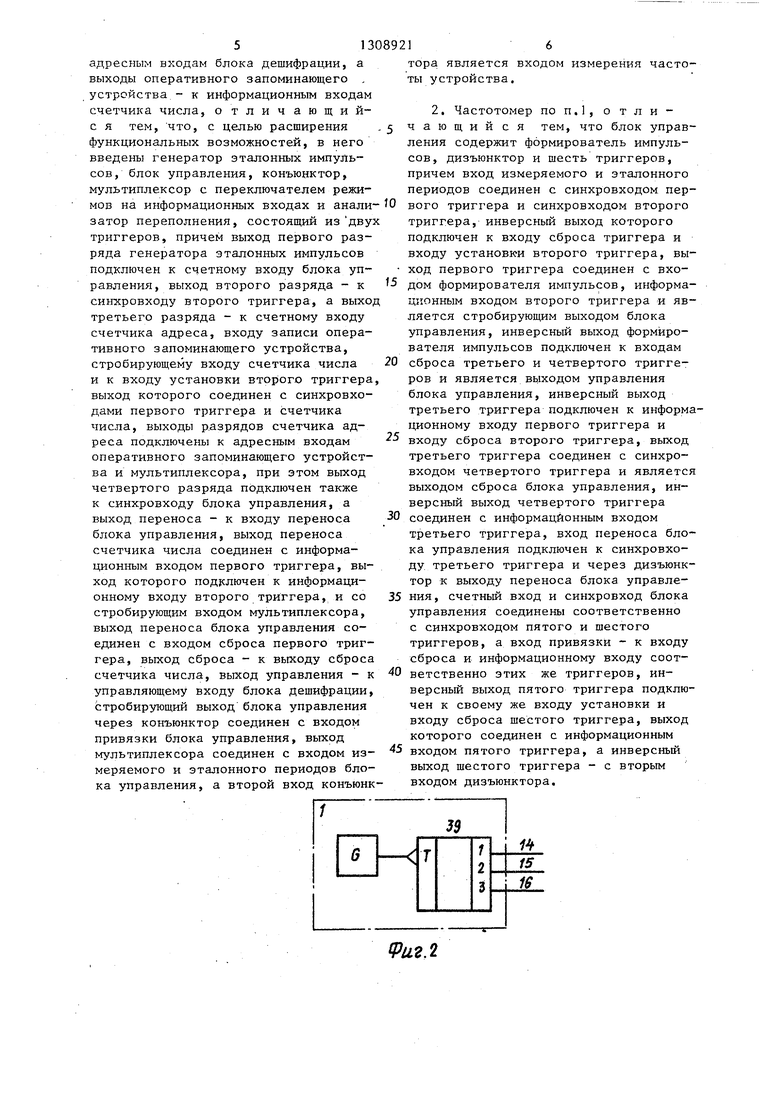

На фиг,1 представлена структурная схема частотомера; на фиг.2-4 - схем входящих блоков; на фиг.5 - временны диаграммы работы частотомера.

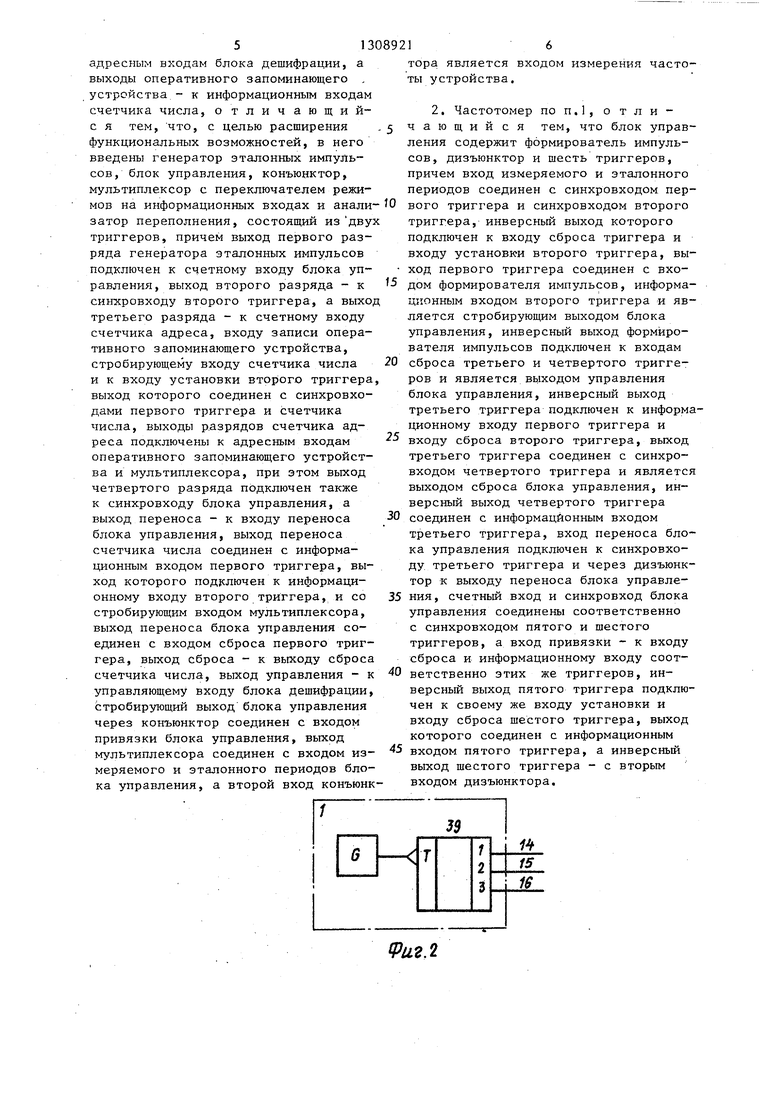

Интегрирующий частотомер содержит генератор 1 эталонных импульсов (ГЭИ и счетный блок 2, в состав которого входят счетчик 3 адреса, счетчик 4 числа, оперативное запоминающее устройство (ОЗУ) 5 и анализатор 6 переполнения, содержащий триггеры 7 и 8, а также мультиплексор 9 с переключателем 10 режимов, конъюнктор II, блок 12 управления (БУ) и блок 13 дешифрации.

Выход 14 первого разряда ГЭИ 1

Вход 25 измеряемого и эталонного периодов соединен с синхровходами триггеров 30 и 31, при этом инверсный выход триггера 31 подключен к .собственному входу установки в 1 и входу сброса триггера 30, Выход последнего объединен с информационным входом триггера 31, с входом формирователя 34 импульсов и стробирующим выходом 23 БУ 12. Инверсньй выход формирователя 34 импульсов соединен с входами сброса триггеров 35 и 36 и выходом 28 управления индикацией, Инверсньш выход триггера 35 объединен с информационным входом триггера 30 и входом сброса триггера 31, а

тзчг 1 о . - прямой выход - с синхровходом тригге- соединен со счетным входом БУ 12, вы-25 , „ .„

ра 36 и выходом 27 сброса БУ 12, при

этом инверсный выход триггера 36 подключен к информационному входу триггера 35.

ход 15 второго разряда - с синхровхо- дом триггера 8, выход 16 третьего разряда - со счетным входом счетчика

3адреса, входом записи ОЗУ 5, стробирующим входом счетчика 4 числа и входом установки триггера 8, выходы - 17 счетчика 3 адреса соединены с адресными входами ОЗУ 5, мультиплексора 9 и блока 13 дешифрации, а выход четвертого разряда - с синхровходом БУ 12,

Выходы 18 и входы 19 ОЗУ 5 соединены соответственно с информационными входами и выходами счетчика 4 числа. Выход 20 переноса счетчика 4 числа соединен со стробирующим входом мультиплексора 9 и информационным входом триггера 7. Выход 21 триггера 8 соединен с синхровходами счетчика

4числа и триггера 7, выход которого подключен к информационному входу триггера 8. Вход 22 измеряемой и эталонной частоты соединен с вторым входом конъйнктора 11, первый вход которого соединен со стробирующим выходом 23 БУ 12, а выход - с входом 24 привязки БУ 2. Вход 25 измеряемого и эталонного периодов подключен к выходу мультиплексора 9, Выход 26 переноса БУ 12 соединен с входом сброса триггера 7, а выход 27 сброса - с входом сброса счетчика 4 числа. Выход 28 управления индикацией БУ 12 соединен с .управляющим входом

I

30 Выход 37 переноса соединен с синхровходом триггера 35 и через дизъюн- ктор 29 с выходом переноса БУ 12. Счетньш вход 14 и синхровход 38 БУ 12 соединены соответственно с син35 хроводами триггеров 32 и 33, а вход 24 привязки - с входом сброса и информационным входом соответственно триггеров 32 и 33, Инверсньй выход триггера 32 объединен с .его входом

40 установки в 1 и входом сброса триггера 33, выход которого соединен с информационным входом триггера 32, а инверсный выход - с вторым входом дизъюнктора 29.

45 Триггеры 30 и 31 со связями между ними представляют собой формирователь временного интервала, триггеры 32 и 33 и дизъюнктор 29 - узел привязки, а формирователь 34 импульсов, тригге50 ры 35 и 36 - формирователь управления индикацией,

ГЭИ 1, счетный блок 2, мультиплексор 9 с переключателем 10 режимов и ,, блок 13 дешифрации со связями между ними представляют собой счетное устройство.

Частотомер работает следующим образом.

блока 13 дешифрации, выход переноса счетчика 3 адреса подключен к входу переноса БУ 12.

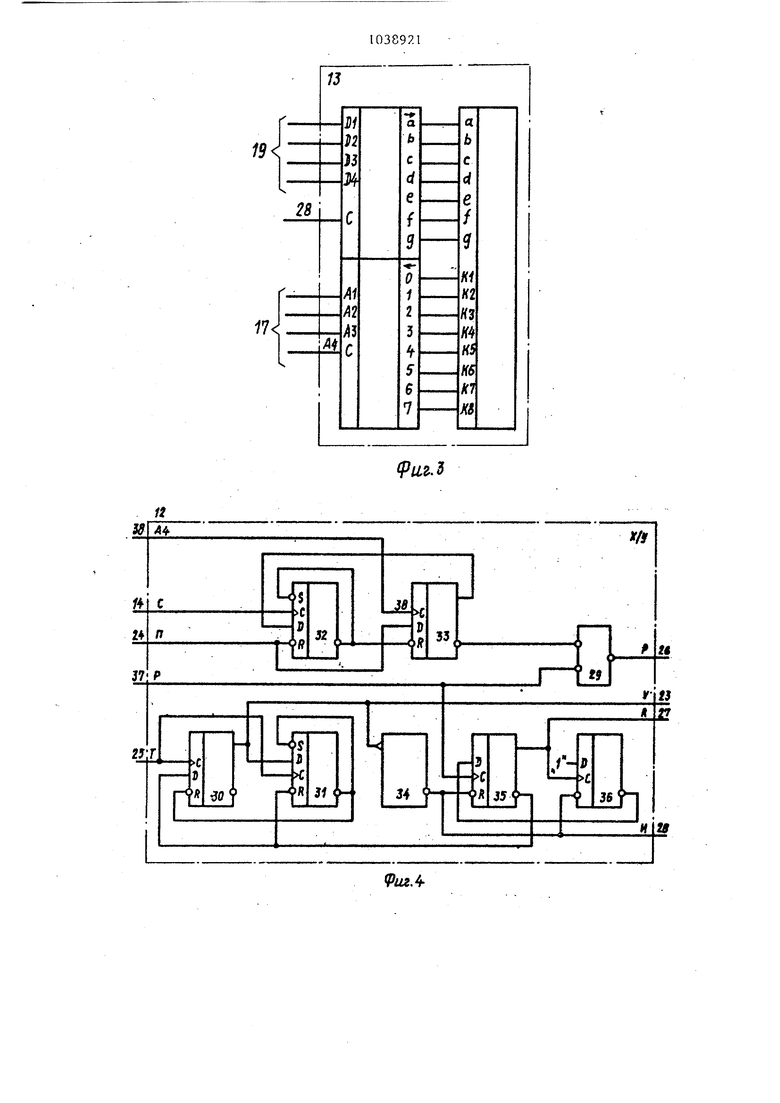

Блок 1 2 зшравления содержит дизъ- юнктор 29, четыре триггера 30-33, формирователь 34 импульсов и два триггера 35 и 36,

Вход 25 измеряемого и эталонного периодов соединен с синхровходами триггеров 30 и 31, при этом инверсный выход триггера 31 подключен к .собственному входу установки в 1 и входу сброса триггера 30, Выход последнего объединен с информационным входом триггера 31, с входом формирователя 34 импульсов и стробирующим выходом 23 БУ 12. Инверсньй выход формирователя 34 импульсов соединен с входами сброса триггеров 35 и 36 и выходом 28 управления индикацией, Инверсньш выход триггера 35 объединен с информационным входом триггера 30 и входом сброса триггера 31, а

I

Выход 37 переноса соединен с синхровходом триггера 35 и через дизъюн- ктор 29 с выходом переноса БУ 12. Счетньш вход 14 и синхровход 38 БУ 12 соединены соответственно с синхроводами триггеров 32 и 33, а вход 24 привязки - с входом сброса и информационным входом соответственно триггеров 32 и 33, Инверсньй выход триггера 32 объединен с .его входом

установки в 1 и входом сброса триггера 33, выход которого соединен с информационным входом триггера 32, а инверсный выход - с вторым входом дизъюнктора 29.

Триггеры 30 и 31 со связями между ними представляют собой формирователь временного интервала, триггеры 32 и 33 и дизъюнктор 29 - узел привязки, а формирователь 34 импульсов, триггеры 35 и 36 - формирователь управления индикацией,

ГЭИ 1, счетный блок 2, мультиплексор 9 с переключателем 10 режимов и блок 13 дешифрации со связями между ними представляют собой счетное устройство.

Частотомер работает следующим образом.

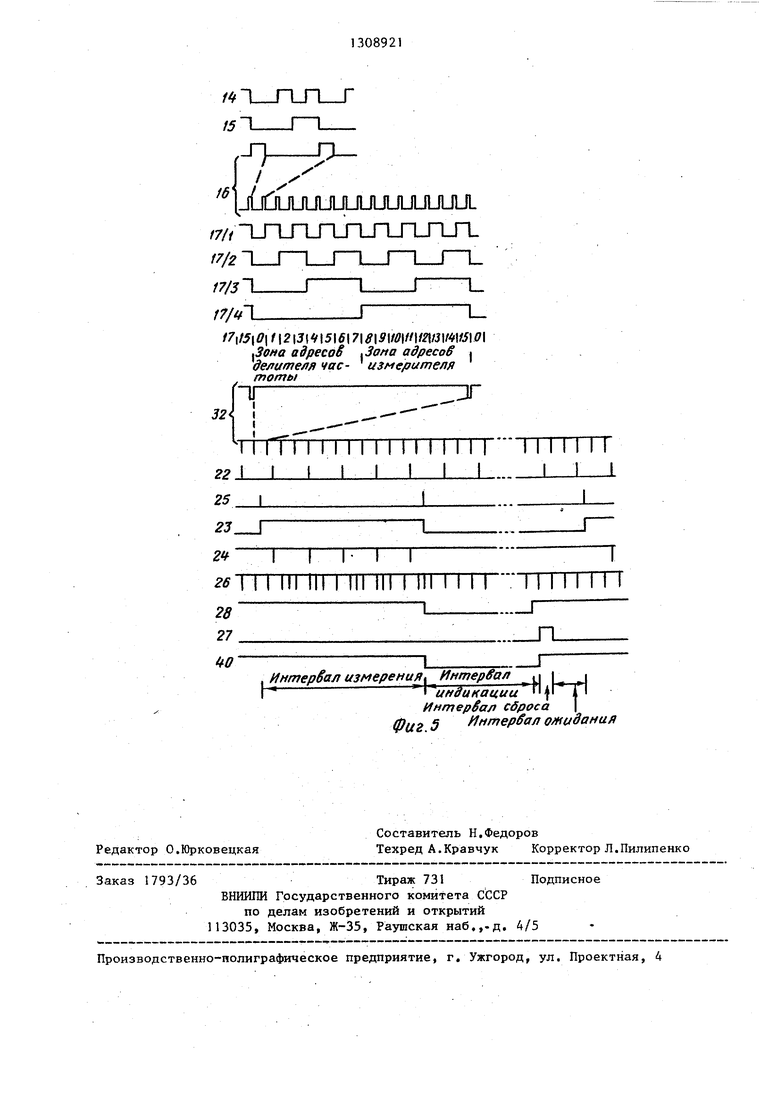

но-пятиричньш счетчик 39 ГЭИ 1 обеспечивает постоянный перебор счетчиком 3 адреса всех адресов ОЗУ 5 и в каждом адресе производит съем информации 5 с ОЗУ 5, запись ее в счетчик 4 числа и перепись обратно в ОЗУ 5 (по тому же адресу). При наличии сигнала сброса с выхода 27 содержимое ОЗУ 5 обнухода 23 формируется на триггерах 30 и 31 и определяется первым после импульса сброса с выхода 27 полным периодом импульса с входа 25.

Импульсы заполнения на входе 22, простробированные импульсом на выходе 23 (несинхронизированные со строб- импульсом) , с входа 24 поступают на

ляется (по всем адресам). По оконча- tO узел привязки (синхронизации)на триг

НИИ сигнала сброса при каждом переполнении счетчика 3 адреса (в конце периода с адресом 15 при четырех- р азрядном двоичном счетчике 3 адреса) через дизъюнктор 29 в БУ 12 по выхо- 5 ду 26 обеспечивается установ в О триггера 7 и в следующем адресе (адресе 00) установ в О триггера 8 по синхровходу и установ его в 1 импульсом с выхода 16 по установоч- 20 ному входу. Сформированный на выходе 21 отрицательный импульс по положительному фронту прибавляет единицу в счетчик 4 числа и переписывает в

герах 32 и 33, представляющий собой схему генератора одиночных импульсов, привязанных к концу периода с адресом .7 поступлением на вход 38 положительного фронта со старшего разряда счетчика 3 адреса. Импульс с триггера 33 формирует через дизъюнктор 29 дополнительный сигнал переноса с

выхода 26. I

Таким образом, по адресам с вось мого по пятнадцатый в ОЗУ 5 организуется восьмиразрядный счетчик импульсов заполнения строб-импульса, работающий совместно с делителем зта30

„,,, у раоотающии совместно с делителем этатриггер 7 по синхровходу уровень 1 ,5 импульсов (по адресам с нуле- поступающии с выхода переноса счет- седьмой).

чика 4 числа. Таким образом, во всех Отрицательный фронт положительного строб-импульса на выходе 23 запускает формирователь 34 импульсов съема информации, который по окончании съема информации из ОЗУ 5 с адресами с восьмого по пятнадцатый запускает формирователь управления индикацией на триггерах 35 и 36. Длительность его импульса сброса равна периоду импульсов переполнения на выходе 37.

Для измерения длительности периода необходимо выход мультиплексора 9 соединить с входом 22, а измеряемый сигнал подать на вход 25..

Изобретение обеспечивает экономию рее. Таким образом обеспечивается

перенос в следующую декаду, хра-. нящуюся по следующему адресу в

последующих адресах вплоть по 15 в триггере 8 по обоим входам (синкро- и установочному) подтверждается 1, т.е. отрицательный импульс по выходу 21 не формируется и к следующему импульсу переполнения с выхода в ОЗУ 5 содержатся по младшему адресу (00) код 1, а по остальным адресам - код О. Каждый последующий цикл перебора адресов добавляет к содержимому ОЗУ 5 по адресу 00 единицу. При коде 9, переписанном из ОЗУ 5 в счетчик 4 числа, импульс с выхода 21 продлевает время нахождения триггера 7 в состоянии О на следующий ад35

40

45

элементов памяти, что при интегральном исполнении частотомера позволяет уменьшить количество интегральных схем или площадь кристалла.

ОЗУ 5.

.Частота следования импульсов на выходах 37 и 20 в каждом последующем адресе уменьшается в 10 раз и обеспе- чивает на выходе мультиплексора 9 формирование частот, поделенных на степень десяти, определяемую положением логической единицы переключателя 10 режимов, и используемых как эталонные при измерении периода входных импульсов и для формирования эталонного периода при измерении частоты входных импульсов.

хода 23 формируется на триггерах 30 и 31 и определяется первым после импульса сброса с выхода 27 полным периодом импульса с входа 25.

Импульсы заполнения на входе 22, простробированные импульсом на выходе 23 (несинхронизированные со строб- импульсом) , с входа 24 поступают на

узел привязки (синхронизации)на триггерах 32 и 33, представляющий собой схему генератора одиночных импульсов привязанных к концу периода с адресом .7 поступлением на вход 38 положительного фронта со старшего разряда счетчика 3 адреса. Импульс с триггера 33 формирует через дизъюнктор 29 дополнительный сигнал переноса с

выхода 26. I

Таким образом, по адресам с вось мого по пятнадцатый в ОЗУ 5 организуется восьмиразрядный счетчик импульсов заполнения строб-импульса, работающий совместно с делителем зтараоотающии совместно с делителем эта импульсов (по адресам с нуле- седьмой).

30

35

40

Изобретение обеспечивает экономию

элементов памяти, что при интегральном исполнении частотомера позволяет уменьшить количество интегральных схем или площадь кристалла.

Формула изобретения

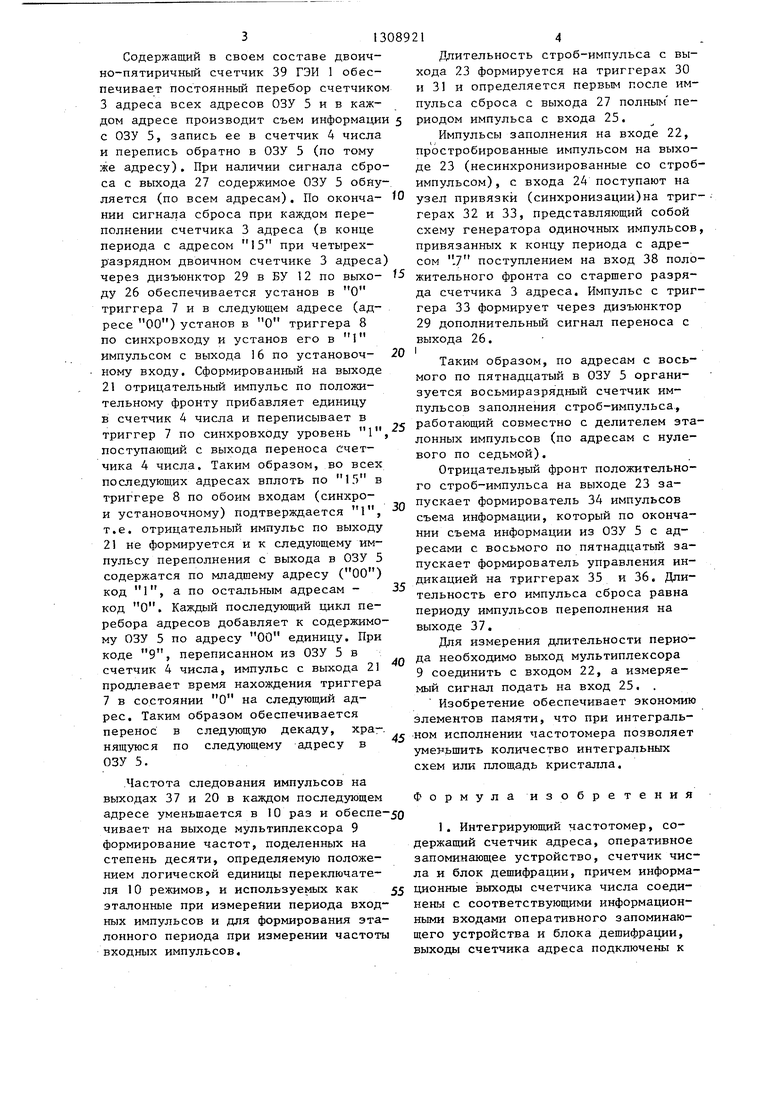

1. Интегрирующий частотомер, содержащий счетчик адреса, оперативное запоминающее устройство, счетчик числа и блок дещифрации, причем информационные выходы счетчика числа соединены с соответствующими информацион- ньмн вxoдa ш оперативного запоминающего устройства и блока дешифрации, выходы счетчика адреса подключены к

5130892

адресным Бходам блока дешифрации, а выходы оперативного запоминающего устройства - к информационным входам счетчика числа, отличающий- с я тем, что, с целью расширения . 5 функциональных возможностей, в него введены генератор эталонных импульсов, блок управления, конъюнктор, мультиплексор с переключателем режимов на информационных входах и анали- 0 вого триггера и синхровходом второго

затор переполнения, состоящий из дву триггеров, причем выход первого разряда генератора эталонных импульсов подключен к счетному входу блока управления, выход второго разряда - к синхравходу второго триггера, а выхо третьего разряда - к счетному входу счетчика адреса, входу записи оперативного запоминающего устройства, стробирующему входу счетчика числа и к входу установки второго триггера выход которого соединен с синхровхо- дами первого триггера и счетчика числа, выходы разрядов счетчика адреса подключены к адресным входам оперативного запоминающего устройства и мультиплексора, при этом выход четвертого разряда подключен также к синхровходу блока управления, а выход переноса - к входу переноса блока управления, выход переноса счетчика числа соединен с информа

ционным входом первого триггера, выход которого подключен к информационному входу второго триггера, и со стробирующим входом мультиплексора, выход переноса блока управления соединен с входом сброса первого триггера, выход сброса - к выходу сброса счетчика числа, выход управления - к управляющему входу блока дешифрации, стробирующий выход блока управления через конъюнктор соединен с входом привязки блока управления, выход мультиплексора соединен с входом измеряемого и эталонного периодов блока управления, а второй вход конъюнктора является входом измерения частоты устройства.

2, Частотомер по п,1, отличающийся тем, что блок управления содержит формирователь импульсов, дизъюнктор и шесть триггеров, причем вход измеряемого и эталонного периодов соединен с синхровходом пертриггера, инверсный выход которого подключен к входу сброса триггера и входу установ1си второго триггера, вы

ход первого триггера соединен с входом формирователя импульсов, информационным входом второго триггера и является стробирующим выходом блока управления, инверсный выход формирователя импульсов подключен к входам сброса третьего и четвертого триггеров и является выходом управления блока управления, инверсный выход третьего триггера подключен к информационному входу первого триггера и

входу сброса второго триггера, выход третьего триггера соединен с синхровходом четвертого триггера и является выходом сброса блока управления, инверсный выход четвертого триггера соединен с информационным входом третьего триггера, вход переноса блока управления подключен к синхровходу третьего триггера и через дизъюнктор к выходу переноса блока управления, счетный вход и синхровход блока управления соединены соответственно с синхровходом пятого и шестого триггеров, а вход привязки - к входу сброса и информационному входу соответственно этих же триггеров, инверсный выход пятого триггера подключен к своему же входу установки и входу сброса шестого триггера, выход которого соединен с информационным входом пятого триггера, а инверсный выход шестого триггера - с вторым входом дизъюнктора.

fPu2.2

ipa.S

РигЛ

J/JIIJUIJIJUIJ

17h (.

17/2

/7/jT

l7/ti.

S

17 15 0 2 3 4 5 6 7 8 9 mnmmW5 0 .Зона adpecoS За ft a адресов i

ftf mffvtf ae 4 л.

делите/гя яас- измерителя fnomt i

J2 I

22

MI iTi I I 11 I I I 11 M I I I i I I I I I I I I I I I I I 1 i

25L

23Г

24-

L

i I III III I ill ill I III I I I I I I I I I M I

....

Интервал

L

измерениЯ1 Интербал .i i i ипдикации i I

Интервал сброса Фиг 5 Интербал отидания

Редактор О.Юрковецкая

Заказ 1793/36Тираж 731Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,,.д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

J

....

1

Составитель Н.Федоров

Техред А.Кравчук Корректор Л.Пилнпенко

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотомер-периодомер | 1985 |

|

SU1337800A1 |

| Генератор последовательности импульсов | 1984 |

|

SU1309275A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МАТРИЦЫ НЕПОЛНОГО ПАРАЛЛЕЛИЗМА | 2009 |

|

RU2421804C2 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Формирователь сетки частот | 1985 |

|

SU1287257A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Устройство для контроля монтажа | 1986 |

|

SU1312616A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для контроля оперативной памяти | 1985 |

|

SU1302325A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

Изобретение относится к измерительной технике и может быть использовано для преобразования частотно- временных сигналов в цифровой код. Целью изобретения является расширение функциональных возможностей устройства. Для достижения этой цели в устройство дополнительно введены генератор 1 эталонных импульсов, блок 12 управления, конъюнктор 11, мультиплексор 9 с переключателем 10 режимов на информационных входах и анализатор 6 переполнения, выполненный на двух триггерах 7 и 8. Кроме того, устройство содержит счетный блок 2, счетчик 3 адреса, счетчик 4 числа, . оперативное запоминающее устройство 5 и блок 13 дешифрации. Генератор 1, счетный блок 2, мультиплексор 9 с переключателем 10 и блок 13 дешифрации со связями между ними образуют счетное устройство. Устройство экономит элементы памяти, в интегральном исполнении позволяет уменьшить количество интегральных схем или площадь кристалла, 1 з.п, ф-лы, 5 ил. I (Л Сл: X) :о ut.t

| Счетное устройство | 1979 |

|

SU856011A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Муттер В.М | |||

| и др | |||

| Проектирование аналого-цифровых систем на интегральных схемах | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Водяные лыжи | 1919 |

|

SU181A1 |

| Насос | 1917 |

|

SU13A1 |

| Новопашенный Г.Н | |||

| Информационно- измерительные системы, 1977 | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-05-07—Публикация

1985-06-27—Подача