1

Изобретение относится к импульсной и вычислительной технике, в частности, может быть использовано в запоминающих схемах, работающих в условиях спецвоздействия: потока нейтронов, электромагнитных и гаммаизлучений.

Известно устройство, обладающее свойствами длительного запоминания информации, для подключения к триггерам 1J.

Устройство может быть использовано для создания запоминающих схем на базе триггеров. Его недостаток невозможность использования для фиксации информации триггера в условиях спецвоздействия.

Известна ячейка запоминающего устройства, содержащая триггер, выход которого соединен с первым входом первого элемента И, второй вход которого соединен со входом Запись, выход - с первым входом формирователя, выход которого соединен со входом-выходом халькогенидного элемента памяти (ЗП) и первым входом второго элемента И, прямой и инверсный выходы которого соединены с соответствующими входами триггерного элемента, второй вход формирователя соединен со входом восстановление информации и через конденсатор - со вторьм входом второго элемента И и с первьм выводом резистора, второй выход кото10рого соединен с общей шиной 2.

Ecjfc в момент спецвоздействия, особенно импульса гамма излучения, питание устройства не отключено, проводимость фогмирователя, включенного пос15ледовательно с элементом памяти, резко увеличивается и через него протекает так, что приводит к потере информации.

Цель изобретения - расширение

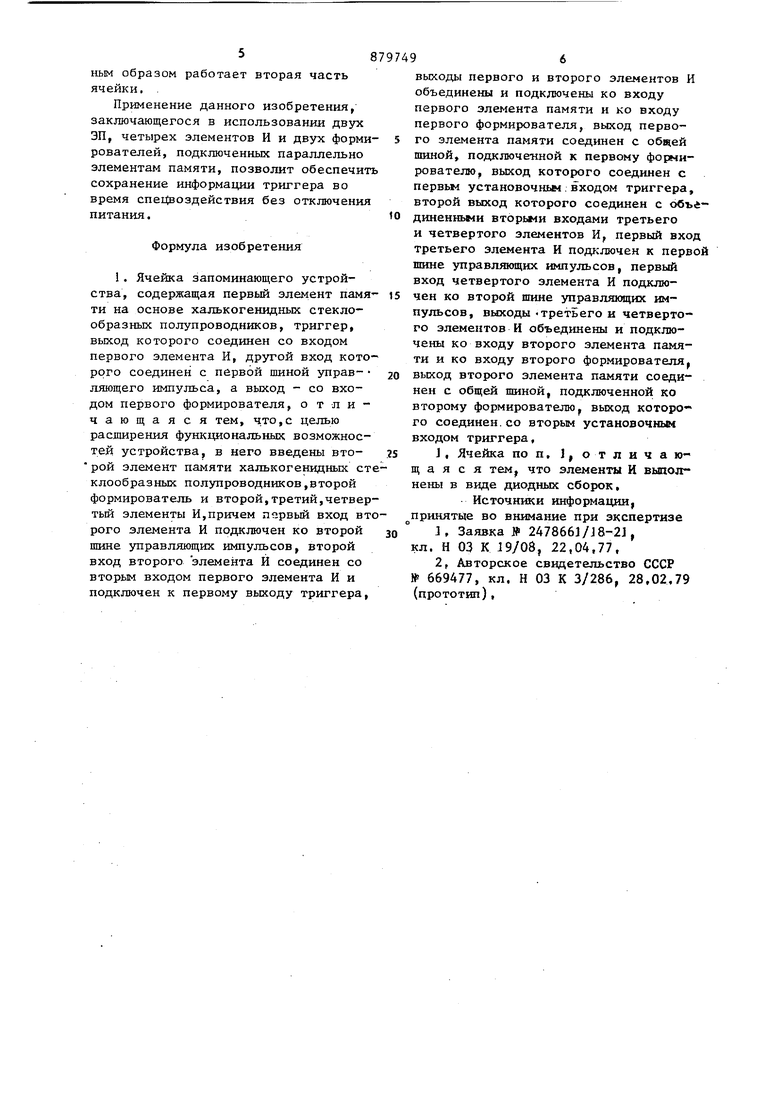

20 функциональных возможностей для обеспечения сохранения информации в условиях спецвоздействия без отключения питания. Указанная цель достигается тем, что в ячейку запоминающего устройства содержащую первый элемент памяти на основе халькогенидных стеклообраг ньк полупроводников,триггер,выход которого соединен .со входом первого эл мента И, другой вход которого соединен с первой шиной управляющего импульса а -выход - со входом первого формирователя, введены второй элемент памяти на основе халькогенидных стеклообразных полупроводников, второй фор мирователь и второй, третий, четверт элементы И причем первый вход второ го элемента И подключен ко второй ши неуправляющих импульсов, второй Вход второго элемента И соединен со вторым входом первого элемента И и подключен к первому выходу триггера, выходы первого и второго элементов И объединены и подключены ко входу пер вого элемента памяти и ко входу перв го Формирователя|выход первого элеме та памяти соединен с общей шиной, подключенной к первому формирователю, выход которого соединен с первым установочным входом триггера, второй выход которого соединен с объединенн ми вторыми входами третьего и четвертого элементов И; первый вход третьего элемента И подключен к первой шине управляющих импушзсов, перBbrii вход четвертого элемента И подключен ко второй шине управляющих импульсов; выходы третьего и четверт го элементов И объединены и подключены ко входу второго элемента памяти и ко входу второго формирователя; выход второго элемента памяти соединен с общей шиной, подк:воченной ко второму формирователю, выход которого соединен со вторым установочным входом триггера, В ячейке запоминающего устройства элементы И выполнены в виде диодных сборок, На чертеже представлена принципиатпзная схема запоминающего устройства, . Ячейка, представляет собой симметричную схему, СОСТОЯЩ5ДО из двух частейр подключенных к триггеру и шине питания, Одна из частей состоит из элемент памяти СЭЦ), выход которого соедин с общей шиной, подключенного к формирователю 2, выход которого соединен с первым установочным входом триггеру 3, вход.- со входом элемент памяти и объединенными вьгоодами эле94ментов И 4 и 5, первые входы которых соединены с соответствующими шинами (входами) 6 и 7 управляющих импульсов а вторые объединены и подключены к первому выходу триггера 3, Вторая часть ячейки состоит из элемента 8 памяти (ЭП), выход которого соединен с общей шиной, подключенной к формирователю 9, Выход формирователя 9 подключен ко второму установочному входу триггера 3, объединенные вторые входы элементов И 10, 11 ко второму выходу триггера 3, Элементы И 4,5,10,JJ вьшолнены в виде диодных сборок t До подачи сигналов на входы 6 и 7 триггер 3 функционирует в соответствии с 1|;остуда,ющими на его входы сигналами | ЭЦ J и 8 находятся во включенном (низкоомном) состоянии. До спецвоздействия, во время него и после его окончаьшя схема работает .без отклонения питания, Ячейка функционирует следующи образом. При подаче первого управл.яющего импульса, предупреждающего о начале воздействия, на вход б и при наличии, напр1шер, на втором выходе триггера 3 логит.1еского О на выходе элемента И 10 импульс .-напряжения отсутствует, а поскольку на первом выходе триггера 3 в этот же момент имеется логи ческая 1, на выходе элемента И 4 появляется импульс напряжения, который поступает на вход ЭП 1 и переводит его в вьпслюченное (высокоомное) состояние. При этом напряжение на входе формирователя 2 повьш1ается, и на первый установочный, вход триггер3 подается логический О, Состояние триггера фиксируется. Второй управляющий импульс подается на вход,7 после окончания воздействия. При этом на выходе элемента И П импульсы напряжения отсутствует, в то время как на выходе элемента И 5 появляется импульс напряжения, KOTopbui поступает на вход ЭП I nepeвoдзiт его во включенное состояние; напряжение на входе формирователя 2 понижается; на первьй установочньш вход триггера 3 поступает логическая 1, Триггер (Начинает функционировать в соответствии с поступающими на его входы сигналами. Если при подаче управляющего импульса логический О ;имеется, на первом выходе триггера 3, аналогичиым образом работает вторая часть ячейки. .

Применение данного изобретения, заключающегося в использовании двух ЭП, четырех элементов И и двух формирователей, подключенных параллельно элементам памяти, позволит обеспечить сохранение информации триггера во время спе1(воздействия без отключения питания.

Формула изобретения

1. Ячейка запоминающего устройства, содержащая первый элемент памяти на основе халькогенидных стеклообразных полупроводников, триггер, выход которого соединен со входом первого элемента И, другой вход которого соединен с первой шиной управ- ляющего импульса, а выход - со входом первого формирователя, о т л и чающаяся тем, что,с целью расширения функциональньщ возможностей устройства, в него введены второй элемент памяти халькогенидных сте клообразных полупроводников,второй формирователь и второй,третий,четвертый элементы И,причем первый вход второго элемента И подключен ко второй шине управляющих импульсов второй вход второго элемента И соединен со вторым входом первого элемента И и подключен к первому выходу триггера.

выходы первого и второго элементов И объединены и подключены ко входу первого элемента памяти и ко входу первого формирователя, выход первого элемента памяти соединен с шиной, подключеяной к первому формирователю, выход которого соединен с первьм установочньм .входом триггера, второй выход которого соединен с овь диненньми вторыми входами третьего и четвертого элементов И, первый вход третьего элемента И под слючен к первой шине управляющих импульсов, первый вход четвертого элемента И подключен ко второй шине управляющих импульсов, выходы «третьего и четвертого элементов И объединены и подключены ко входу второго элемента памяти и ко входу второго формирователяJ

выход второго элемента памяти соединен с общей шиной, подключенной ко второму формирователю, выход которого соединен.со вторым установочньм входом триггера,

J f Ячейка по п. J, отличающаяся тем, что элементы И выполнены в виде диодных сборок.

Источники информации, принятые во внимание при экспертизе

J, Заявка № 247866 /J8-2J, кл. Н 03 К 19/08, 22,04,77,

2, Авторское свидетельство СССР 669477, кл. Н 03 К 3/286, 28,02,79 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU1003143A1 |

| Логическое запоминающее устройство | 1977 |

|

SU661609A1 |

| Устройство для ввода изображения в ЭВМ | 1986 |

|

SU1432494A1 |

| Устройство для измерения параметров магнитных лент | 1986 |

|

SU1434376A1 |

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

| Программируемое постоянное запоминающее устройство | 1980 |

|

SU886055A1 |

| Распределитель импульсовупРАВлЕНия | 1979 |

|

SU805288A1 |

| Генератор многомерных случайных процессов | 1990 |

|

SU1755279A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

i

Ф

Т

Авторы

Даты

1981-11-07—Публикация

1979-11-11—Подача