(5) РЕЛЕ НАПРАВЛЕНИЯ МОЩНОСТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Реле сопротивления | 1978 |

|

SU736256A1 |

| Устройство для сравнения электрических величин по фазе | 1982 |

|

SU1108549A1 |

| Орган контроля синхронизма при автоматическом повторном включении линии электропередачи | 1979 |

|

SU855822A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Орган контроля синхронизма при автоматическом повторном включении линии электропередачи | 1980 |

|

SU928495A1 |

| Импульсный регулятор | 1984 |

|

SU1259209A1 |

| Устройство для предварительной проверки транзисторов | 1982 |

|

SU1101762A1 |

| Устройство для сравнения фаз двух электрических величин | 1980 |

|

SU947782A1 |

| Устройство для сравнения фаз двух электрических величин | 1983 |

|

SU1150695A1 |

| Устройство синхронизации импульсных приемников | 1978 |

|

SU725256A1 |

1

Изобретение относится к электротехнике и может быть использовано в направленных устройствах защиты элементов электрических систем.

Известно реле направления мощности , содержащее блок совпадения положительных знаков двух величин, блок совпадения отрицательных знаков, сумматор, интегратор и пороговый элемент СО

Это устройство надежно отстроено от влияния апериодических помех, искажающих входные сигналы, но может ложно сработать при подаче на. входы сигналов разных частот,, что проявляется при использовании реле в защитах, реагирующих на нулевую последовательность напряжений и токов.

Указанный недостаток отсутствует в реле направления мощности, содержащем два блока совпадения, интегратор, пороговый элемент и счетчик, осуществляющий счет импульсов, поступающих с одного из блоков совпадения в паузах между импульсами другого блока совпадения, и быстрый разряд интегратора, если первый блок выдает два импульса подряд t2l.

Полный разряд интегратор означает возврат реле, и это будет происходить всякий раз, когда один из блоков совпадения выдаст два импульса. Если нарушение порядка чередования

to импульсов наблюдается многократно, то возврат реле, конечно, оправдан. Но такое явление может произойти и однократно, например, в переходном режиме при изменении разности фаз

ts между входными величинами или же вследствие случайного сбоя. Тогда оно вызовет ложный возврат pehe или заметное повышение времени срабатывания, что приводит к снижению устой20чивости функционирования реле.

Цель изобретения - повышение устойчивости функционирования реле направления мощности.

Поставленная цель достигается тек. то в реле направления мощности, одержащее блок .совпадения положиельных знаков электрических величин, лок совпадения отрицательных знаков j лектрических величин и последоваельно включенные интегратор и пооговый элемент, выход которого я&- , яется выходом реле, дополнительно введены сумматор, два элемента памя- ю ти, два логических элемента ИЛИ, триггер и блок предварительной установки, при этом выход каждого из блоков совпадения положительных (отрицательных) знаков электрических is величин подключен к одному из. входов блока предварительной установки и одному из входов соответствующего элемента памяти, выходы которых подключены ко входам триггера и сумма- 20 тора, подключеннбго выходом ко входу интегратора, выход упомянутого блока -предварительной установки подключен к одному из входов обоих элементов ИЛИ, к другим входам которых 25 подключены соответствующие выходы триггера, а выходы элементов ИЛИ подключены к другим входам соответствующих элементов памяти.

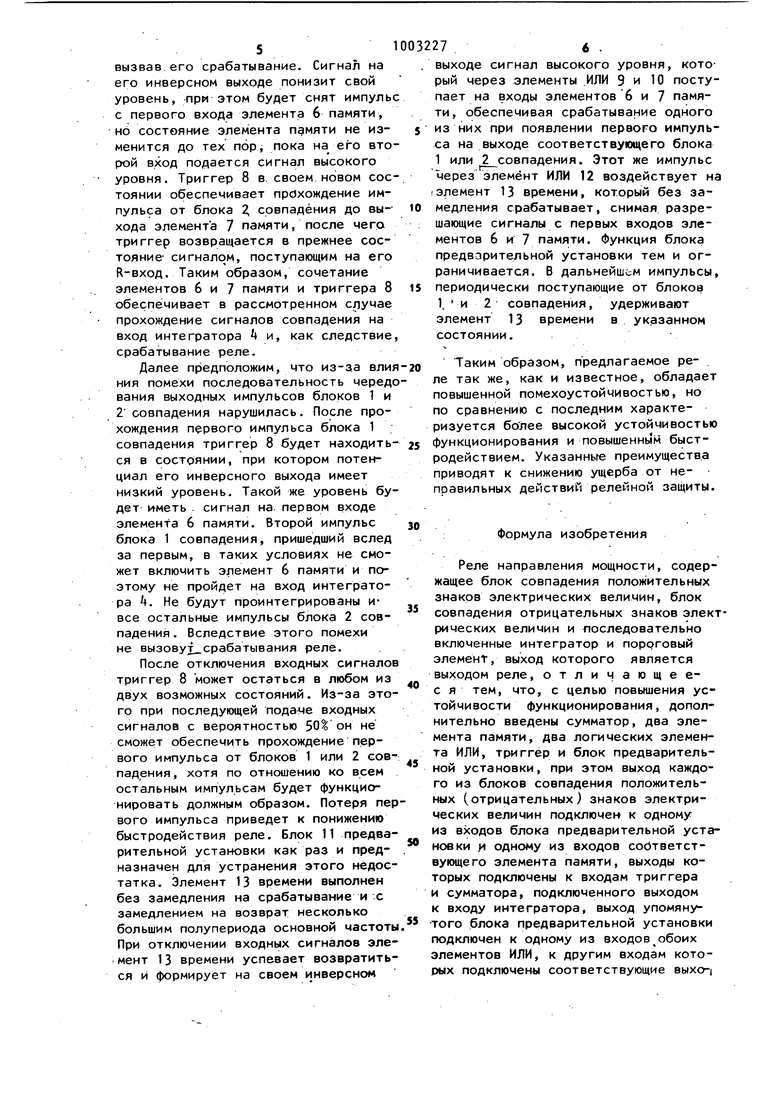

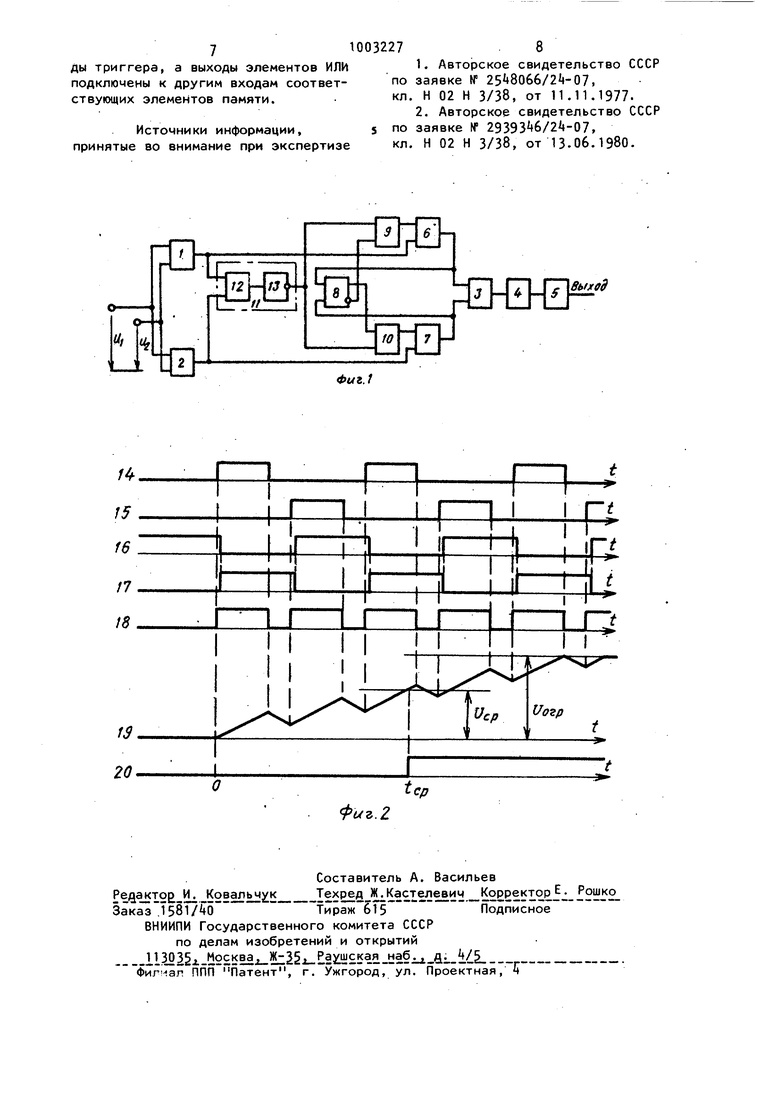

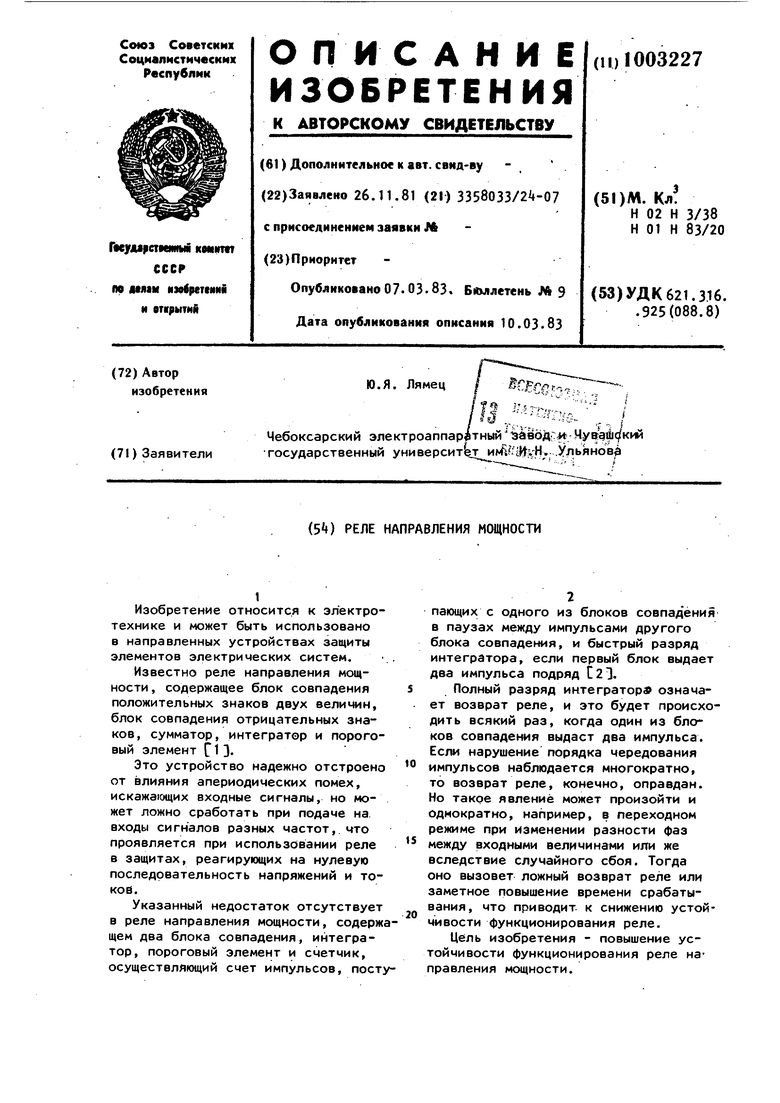

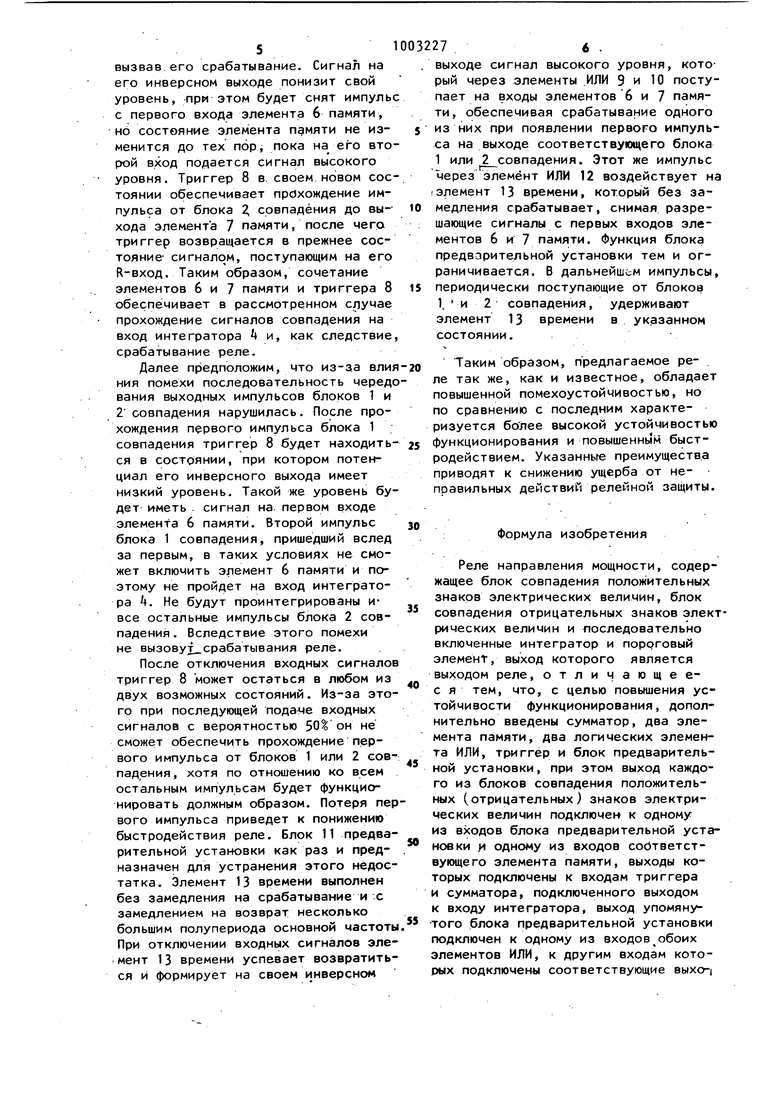

На фиг. t приведена функциональ- зо ная схема реле направления мощности; на фиг. 2 - диаграммы сигналов при правильном порядке их чередования в условиях, соответствующих срабатыванию реле.J5

Реле содержит блок 1 совпадения положительных знаков электрических величин, блок 2 совпадения отрицательных знаков электрических величин, последовательно включённые сумматор 3, интегратор , пороговый элемент 5, элементы 6 и 7 памяти, подключенные выходами к входам сумматора 3 и триггера 8, логические элементы ИЛИ 9 и 10, подключенные одним из входов ., к выходу блока 11 предварительной установки, а другим входом к соответствующему выходу триггера 8.

Блок 11 предварительной установки может быть выполнен, например., в виде последовательно включенных элемента ИЛИ 12 и элемента 13 времени.

Элементы 6 и 7 памяти реализуют логическую функцию

Y ().Х,JJ

где Х - сигнал на первом (верхнем по схеме) входе элемента; Х2 сигнал на втором входе; Y - сигнал на выходе.

Они могут быть выполнены на логических элементах И, ИЛИ, а также на RS-триггерах с вторым инверсным входом.

Блок 1 совпадения содержит выходной сигнал 1, блок 2 совпадения выходной сигнал 15, сигнал 16 на инверсном выходе триггера 8. Устройство содержит также сигнал 17 на прямом выходе триггера 8, сигнал 18 на выходе сумматора 3 сигнал 19 на выходе интегратора i,выходкой сигнал 20 реле (порогового элемента 5), Ucp и Ugj - напряжения срабатывания и возврата порогового элемента 5, UOTP уровень ограничения выходного сигнала -интегратора k, О - момент подачи входных сигналов (показан там, где необходимо рассмотреть переходный процесс), - момент срабатывания реле.

На графиках выходных сигналов триггера учтено запаздывание по отношению к сигналам блоков 1 и 2 совпадения, имеющее принципиальное значение.

Блок 1 совпадения формирует сигнал высокого уровня на интервалах совпадения положительных знаков входных величин U j и. и 2 и низкого уровня в остальное время, а сигнал блока .2 совпадения имеет высокий уровень на интервалах совпадения отрицательных знаков входных величин.

Рассмотрим работу реле, начиная с момента появления импульса на выходе блока .1 совпадения.

Предположим, что импульсы на выходах блоков 1 ,и 2 совпадения образуют правильную последовательность (фиг. в паузах сигнала одного из блоков появляется только один импульс другого блока. Это означает, что импульсу блока 1 совпадения предшествовал импульс блока 2 совпадения, который прошел на выход элемента 7 памяти и, соответственно, на R-вход триггера 8, установив тем самым на инверсном выходе триггера 8 сигнал высокого уровня. Как следствие, через элемент ИЛИ 9 на первый вход элемента 6 памяти также поступает сигнал высокого уровня. В сложившихся условиях импульс блока 1 совпадения пройдет через элемент 6 памяти и затем через сумматор 3 поступит на вход интегратора k. Кроме того, с выхода элемента 6 памяти импульс будет подан на S-вход триггера 8, 5 вызвав его срабатывание. Сигнал на его инверсном выходе понизит свой уровень, при этом будет снят импуль с первого входа элемента 6 памяти, но состояние элемента памяти не изменится до тех порj пока на его вто рой вход подается сигнал высокого уровня. Триггер 8 в. своем новом сос тоянии обеспечивает прсзхождение импульса от блока 2, совпадения до выхода элемента 7 памяти, после чего триггер возвращается в прежнее состояние сигналом, поступающим на его R-вход. Таким образом, сочетание элементов 6 и 7 памяти и триггера 8 обеспечивает в рассмотренном случае прохождение сигналов совпадения на вход интегратора и, как следствие срабатывание реле. Далее предположим, что из-за вли ния помехи последовательность черед вания выходных импульсов блоков 1 и 2 совпадения нарушилась. После прохождения первого импульса блока 1 совпадения триггер 8 будет находить ся в состоянии, при котором потенциал его инверсного выхода имеет низкий уровень. Такой же уровень бу дет иметь . сигнал на первом входе элемента 6 памяти. Второй импульс блока 1 совпадения, пришедший вслед за первым, в таких условиях не сможет включить элемент 6 памяти и поэтому не пройдет на вход интегратора . Не будут проинтегрированы ивсе остальные импульсы блока 2 совпадения. Вследствие этого помехи не вызовут срабатывания реле. После отключения входных сигналов триггер 8 может остаться в любом из двух возможных состояний. Из-за этого при последующей подаче входных сигналов с вероятностью 50% он не сможет обеспечить прохождение первого импульса от блоков 1 или 2 совпадения , хотя по отношению ко всем остальным импульсам будет функционировать должным образом. Потеря пер вого импульса приведет к понижению быстродействия реле. Блок 11 предварительной установки как раз и предназначен для устранения этого недостатка. Элемент 13 времени выполнен без замедления на срабатывание и с замедлением на возврат несколько большим полупериода основной частоты При отключении входных сигналов элемент 13 времени успевает возвратиться и формирует на своем инверсном 27 выходе сигнал высокого уровня, который через элементы .ИЛИ 9 и 10 поступает на входы элементов6 и 7 памяти, обеспечивая срабатывание одного из них при появлении первого импульса на выходе соответствующего блока 1 или Д совпадения. Этот же импульс через элемент ИЛИ 12 воздействует на Iэлемент 13 времени, который без замедления срабатывает, снимая разрешающие сигналы с первых входов элементов 6 и 7 памяти. Функция блока предварительной установки тем и ограничивается. В дальнейшем импульсы, периодически поступающие от блоков 1. и 2 совпадения, удерживают элемент 13 времени в указанном состоянии. Таким образом, предлагаемое реле так же, как и известное, обладает повышенной помехоустойчивостью, но по сравнению с последним характеризуется более высокой устойчивостью функционирования и повышенным быстродействием. Указаннью преимущества приводят к снижению ущерба от неправильных действий релейной защиты. Формула изобретения Реле направления мощности, содержащее блок совпадения положительных знаков электрических величин, блок совпадения отрицательных знаков электрических величин и последовательно включенные интегратор и пороговый элемент, выход которого является выходом реле,отличающеес я тем, что, с целью повышения устойчивости функционирования, дополнительно введены сумматор, два элемента памяти, два логических элемента ИЛИ, триггер и блок предварительной установки, при этом выход каждого из блоков совпадения положительных (отрицательных) знаков электрических величин подключен к одному из входов блока предварительной установки и одному из входов соответствующего элемента памяти, выходы которых подключены к входам триггера сумматора, подключенного выходом к входу интегратора, выход упомянуого блока предварительной установки одключен к одному из входов обоих лементов ИЛИ, к другим входам котоых подключены соответствующие выхо-(

710032278

ды триггера, а выходы элементов ИЛИ Ь Авторское свидетельство СССР подключены к другим входам соответствующих элементов памяти.

Источники информации, принятые во внимание при экспертизе Фuг.f

по заявке № 25 80б6/2«-07,

кл. Н 02 Н 3/38, от 11.11.1977.

кл. Н 02 Н 3/38, от 13.06.1980. Выход

Авторы

Даты

1983-03-07—Публикация

1981-11-26—Подача