(54) СГЛАЖИВАЮЩИЙ ФИЛЬТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный прогнозатор | 1982 |

|

SU1049866A1 |

| Управляемый фильтр | 1984 |

|

SU1149214A1 |

| Управляемый фильтр | 1981 |

|

SU1004962A1 |

| Управляемый сглаживающий фильтр | 1982 |

|

SU1061250A1 |

| Управляемый фильтр | 1979 |

|

SU884082A1 |

| Управляемый фильтр | 1981 |

|

SU970644A1 |

| Управляемый фильтр | 1985 |

|

SU1279054A2 |

| Управляемый фильтр | 1980 |

|

SU959268A2 |

| Интерполирующий фильтр | 1982 |

|

SU1030958A1 |

| Интерполирующий фильтр | 1983 |

|

SU1109891A1 |

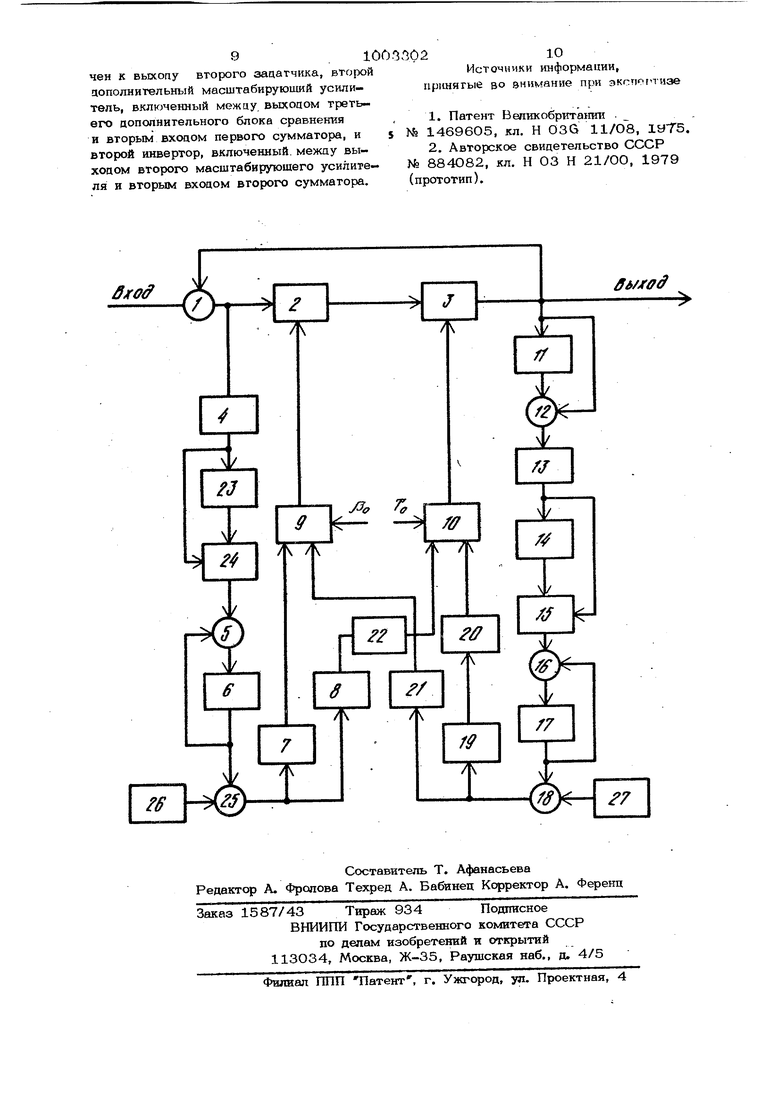

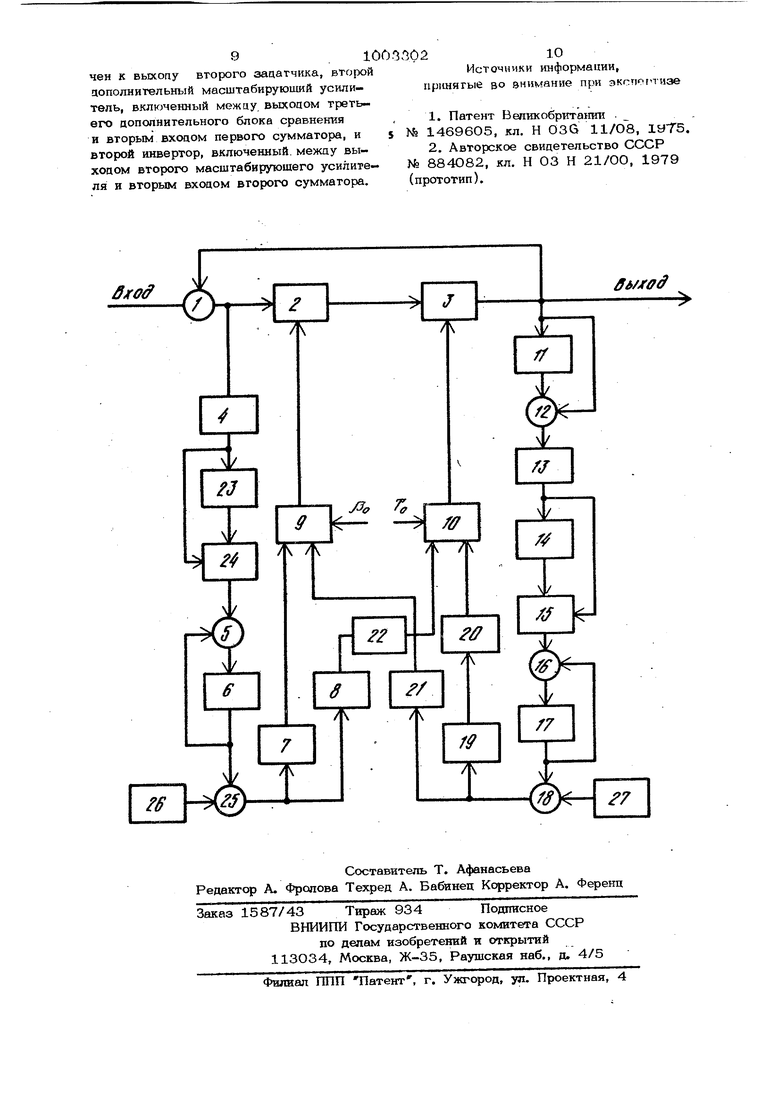

Изобретение огносигся к радиотехник и можег быть использовано для выделен полезной низкочастогной составляющей измеренных сигналов. Известно сглаживающее устройство, соцержащее ограничитель уровня сигнала цва интегратора, масщтабирующий усилитель, блок сравнения, первый вход котор го подключен к входу устройства, а выхо через ограничитель уровня сигнала к входу первого интегратора, выход которого подключен к выходу устройства, к второму вхоцу блока сравнения и через второй интегратор и масштабирующий усилитель к ограничителю уровня сигнала. Сглаживающее устройство уменьшает влияние как помех типа выбросов, характеризующихся кратковременным измен нием сигнала на входе устройства на значителыгую величину, гак и обычных помех, распрепеленных, например, по нормальному закону 1Л. . Недостатком известного устройства является низкая точность выделения полезного сигнала в случае, когда статистические и структурные свойства полезного сигнала и помехи изменяются. Настроечные же параметры сглаживающего устройства, к которым относятся постоянная времени интегрирования первого интегратора и величина ограничивающего напряжения ограничителя сигнала, определяются при фиксированных указанных свойствах сигнала. Известен управляемый фильтр, содержащий последовательно включенные первый блок сравнения, ограничитель и первый интегратор, выход которого соединен с другим входом блока сравнения, последовательно соединенные детектор знака, вход которого подключен к выходу первого блока сравнения, второй блок сравнения, второй интегратор, квадрагор, первый масштабирующий усилитель, первый сумматор, выход которого подключен к уп3равляющему вхоцу ограничителя, поолецс вательно соециненные второй масштаби- руюший усилитель, вход KOTOfxiro подключен к выходу квадратора, и второй сумматор, выход которого соединен с управЛЯЮ1ЦИМ входом первого интегратора, при чем вторые входы обоих- сумматоров подключены к источникам сигналов постоянной величины 2 . Однако известный управляемый фильтр имеет недостаточную точность выделения полезного сигнала, особенно в том случае, .когда имеются его монотонные сое- тавляющие вследствие того, что учиТываются только свойства отклонений измерен ного сигнала от его выделенных оценок и не учитываются свойства самих оценок полезного сигнала. Цель изобретения - повышение точноети фильтрации. Поставленная цель достигается тем, что в сглаживающий фильтр содержащий последовательно соединенные первьй блок сравнения, ограничитель и первый интегратор, выход которого подключен к другому входу первого блока сравнения, выход которого соединен также с входом детектора знака, последовательно соединенные второй блок сравнения и второй интегратор, выход которого подключен к первому входу второго блока сравнения, последовательно соециненные первый масштабирующий усилитель и первый сумматор, выход которого подключен к управляющему входу ограничителя, а также второй масштабирующий усилитель, в.ход которого объединен с входом первого масштабирующего усилителя, и второй сумматор, выход которого подключен к управл5тющему входу первого интегратора, введены последовательно соединенные первьщ блок задержки, первый дополнительный блок сравнения, другой вхоц которого соединен с выходом первого интегратора, дополнительный детектор знака, второй блок задержки, первый блок умножения, другой вход которого соединен с выходом ,. дополнительного детектора знака, второй дополнительный блок сравнет1я, дополнительный тгтегратор, выход которого соединен также с другим входом второго дополнительного блока сравнения, третий дополнительный блок сравнения, другой вход которого соединен с выходом первого задатчика, первый дополнительный масштабирующий усилитель и первый инвертор, включенные между вь1ходом перво го интегратора и первым входом второго 3024 сумматог, нсхзлоновотольно соединени1,1е блок запержки и блок умножения, включенные межцу выходом це- тектс ра знака и вторым входом вгорого блока сравнения, причем второй вхоа второго блока умножения соединен с выходом детектору знака, а также четвертый дополнительный блок сравнения, вкл1оченный между выходом второго интеграто- ра и входом первого масштабирующего усилителя, причем второй вход четвертого дополнительного блока сравнения поаключен к выходу второго задатчика, второй дополнительный масштабирующий усилитель, включенный между в ходом третьего дополнительного блока сравнения и вторым входом первого сумматора, и второй инвертор,, включенный-между выходом второго масштабирующего усилите- „я и вторым входом второго сумматора. На чертеже представлена структурная электрическая схема сглаживающего фильтра. Сглаживающий фильтр содержит первый блок 1 сравнения, ограничитель 2, первый интегратор 3, детектор 4 знака, второй блок 5 сравнения, второй интегратор 6, первый масшгабир поший усилитель 7, второй масштабирующий усилитель 8, первый сумматор О второй сумматор 10, первый блок J.J. задеряиси, первьй дополнительный блок 12 сравнения, дополнительный детектор 13 знака, второй блок 14 задержки, первый блок 15 умножения, второй дополнительный блок 16 сравнения, допоязштельный интегратор 17, третий дополнительный блок 18 сравнения, первый дополнительный масштабируюший усилитель 19, первьш инвертор 20, второй дополнительнь1Й м юшта- бируюший усилитель 21, второй инвертор 22, третий блок 23 задеркки, второй блок 24 умножения, четвертый допол- нительиый блок 25 сравнения, .задатчики 26 и 27. Сглаживающий фильтр работает следующим образом. Входной сигнал поступает на вход первого блока 1 сравнения, в котором из него вычитается выходной сигнал устройства, и получаемая разность 5o(4i поступает на вход ограничителя 2 и на вход первого детектора 4 знака. сг;(.4;7 превьшлает величину ограничиваюшетю напряжения ограничителя 2, то в ограничителе 2 он ограничив-аетол до этой ве- личины, ч го можно прс пставигь выражением: (Ъ EoCt) i (t)p -р eoct)sp гае 6 (-fc) - выходной сигнал ограничителя 2, Р) - величина ограничивающего напряжения. Ограничитель 2 может быть реализо ван, например, с помощью операционного усилителя в режиме насыщения. Сигнал t(-t) с выхоаа ограничителя 2 поступае на вхоц первого интегратора 3, выполненного, например, с помощью операцион ного усилителя с емкостной отрицательно обратной связью. На выходе интегратора 3 получается сглаженный сигнал, которы и поступает на вход устройства. Все остальные блоки сглаживающего фильтра прецназначены цля адаптации его настроек: величины ограничивающего напряжения Ь ограничителя 2 и постоянн времени интегрирования Т интегратора 3. Величина ограничивающего напряжения jb и постоянная времени интегрирования Т корректируются по отклонению измеренного сигнала от выцеленных оценок его полезной составляющей Eoa)--X(i)-X(4:C,) и по оценке скорости изменения выделен ной полезной составляющей сигнала е-л-и-хад-хй-т,), - входной сигнал устройства (из меренный сигнал W,Xtt-t,)X выходной сигнал устройства (сгла женный сигнал). По обоим показателям рассчитывается аналог автокорреляционного момента, затем полученная величина сигнала срав нивается с желаемым (заданным) сигналом и по полученному отклонению определяются корректировки р и Т, Для реализации описанной процедуры сигнал to (-t) с выхода первого блока 1 сравнения поступает на детектор 4 знака где на выходе получается сигнал либо , либо -1, в зависимости от знака о( . Полученный сигнал поступает на вход третьего блока 23 задержки и на второй вход второго блоко 24 умножения, где сигналы Sigvi (i и SigVi 1 перемножаются. В результате выходной сигнал второго блока 24 умножения принимает величину +1, еоли to it) 3 HSigM fco(t-t,) одного знака, и,, если они разного знака. Затем во втором блоке 5 сравнения вычитается сигнал с выхода второго интегра гора 6. На выходе которого получается сглаженный выходной сигнал второго блока 5 сравнения, т.е. cf, a)--cf, (t-T ,)к ,|sigTi eo(-t) 5ig toa-t,)-d(t-T,)j, гцо cffCt) - сглаженное значение сигнала (-t-r,)c выхода второго блока 5 сравнения. В блоке 25 сравнения из сигнала ,(4;) вычитается желаемый сигнал 2 налога автокорреляционного момента: )-cruo-z. (в частном случао Jl O)i который П(ступает на входы первого 7 и второго 8 масштабирующих усилителей, где у тожа- ется на коэффициенты К, и Kj. Пля определения скорости изменения сглаженного сигнала ..С) выходной сиг- )шл первого интеграго хг 3 запоминается в первом бт же 11 задеркки на интервале времени-ТГ , а затем задержанный сигнал вьмитаегся в блоке 12 сравнения из сигнале ) . Сигнал с полученной разности (4: обрабатывается аналогично сигналу ) с помощью дополнительного детектора 13 знака, второго блока 14 задержки, первого блока 15 умножения, блока 16 сравнения, дополнительного интегратора 17, т въсхоце которого получается сигнал cr,2,(t)-cf2.(-t-z:i)+k ig h fcncW X sig-vi ПС ) -4( )J, гае d (t) - сглаженное значение сигнала Sig-H ) -5ig Bnc -C 2.)I- выхода п-jpDOro блока 15 умножсиия. В блоке 18 сравнения из сигнала cflCt) вычитается желаемый сигнал 2, ана.,:га автокорреляционного момента: tM-cf iO-l. 71 in частном случае сигнал Zg 1), кото рый поступает на вхоцы первого 19 и второго 21 аопотштельных масштабирующих усилителей, гае умножается на коэффициенты К и К. Таким образом, на выходах масштаби рующих усилителей 7, 8, 19 и 21 полу- чаютг::;я сигналы: K,,e(-t)-|K4ei(-k); ц а х-Кбе с)Далее в первом сумматоре 9 сигналы с выхоцов первого 7 и второго дополнительного 21 масштабирующих усилителей суммируются с сигналом источника посто янной величины feO, зацавая величину ограничивающего напряжения рограничителя 2; |(t))tn.i(t)4fb, f (-t) P,j () корректировки ограничивающего напряжения по показателям ott) ncWСигналы же с второго 8 и первого дополнительного 19 масштабирующих усилителей поступают через инверторы 2О и 22 на второй сумматор 1О, где суммируются с сигналом источника посто янной величины Т, задавая величину постоянной времени интегрирования Т интегратора 3: Т(0--ТДО-ТгШ Т raeT(-t) , T(-fc) - корректировки посто янной времени интегрирования по пока за гелям &оС{:)и encW. Инверторы 2О и 22 введены, чтобы производить корректировку Т. Если показатели 2 Q (-t) и j,j.jCt) увеличиваютСИ, то постоянная времени интегрировани уменылаегся, и наоборот, если покязатели EpCt) ,{.(-t) уменьшаются, то постоян ная времени интегрирования увеличивается, Точность выделения полезного сигнала оценивают по срецнемодульному критериюцi:,UU)-yct)| N где X(jt) - полезный сигнал, (4)- сглаженный сигнал; |sj - коли шстно точек. ,()-2В 1. .:1езультате введенич {ов),.х элементов повышена точность выцелепия полезного сигнала по cpaBHeHHKj с: п эототипом примерно на 15% по указаиыому критерию. Формула изобретения Сглаживающий фильтр, соаержашнй послецовательно соеаиненные первый блок сравнения, ограничитель и первый интегратор, выход которого попкльочен к другому вхоцу первого блока сравнения, выход которого соединен также с входом детектора знака, последоватупьно соеди- ненн1 1е второй блок сравнения и второй интегратор, выход которого подключен к первому входу второго блска сравнения, последовательно соединенные первый мае- щтабирующий усилитель и первый сумматор выход которого подключен к управляющем входу ограничителя, а также второй масщтабирующий усилитель, вход которого объединен с входом первого масштабирующего усилителя, и второй сумматор, выход которого подключен к управляющему входу первого интегратора, от л И;- чающийся тем, что, с целью повы- щения точности фильтрации, в него введены последовательно соединенные первый блок задержкг), первый дополнительный блок сравнения., другой вход которого соединен с выходом первого интегратора, дополнительный детектор знака, второй блок задержки, первый блок умножения, другой вход которого соединен с выходом дополнительного детектора знакЬ, второй дополнительный блок сра&нения, дополнительный интегратор, выход которого соединен также с пругт-м входом второго дополнительного блока сравнения, третий дополнительный блок сравнения, другой в..од которого соединен с выходом первого задатчика, первый дополнительный масштабирующий усилитель и первый инвертор, включенные мел.ду выходом первого интегратора и первым ..вхоцом второго сумматора, последовательно соединенные третий блок задержки и второй блок умножения, включенные межцу выходом детектора знака и вторым входом второго блока сравнения, причем второй вход второго блока умножения соединен с выходом детектора знака, а также четвертый дополнительный блок ,:равнения, включенный между выходом второго интегратора и входом первого масшгабирук -щего усилителя, второй вход четвертохю допопнительного блока сравнения подклк

Авторы

Даты

1983-03-07—Публикация

1981-11-06—Подача