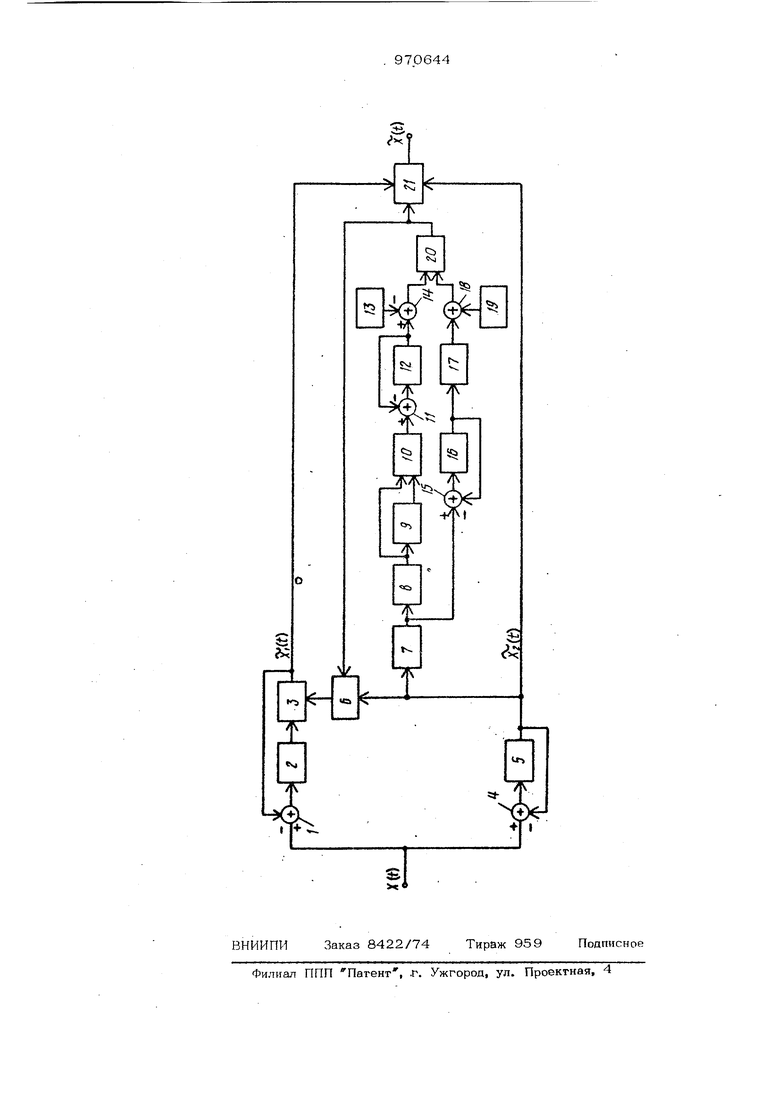

Изобретение относится к автоматическому регулированию и управлению и может быть использовано в обшетехнических системах управления для выделения полезной низкочастотной составляющей измеренных сигналов. Известен управляемый фильтр для выделения полезной составляющей измеренного сигнала, содержащий ограничитель уровня сигнала, два интегратора, масштабирующий блок, блок сравнения, первый вход которого подключен к входу устройства, а выход через ограничитель уровня сигнала к входу первого интегратора, выход которого подключен к выход устройства, к второму входу блока срав нения и через второй интегратор и масщтабирующий блок к ограничителю уровня сигнала Г 1 Недостатком указанного фильтра является низкая точность выделения полез ного сигнала при нестгшионарных структурно-статических свойствах полезного сигнала и помехи. Известен управляемый фильтр, содержащий последовательно включенные первый блок сравнения, ограничитель уровня сигнала, и первый интегратор, последовательно включенные детектор, знака, второй блок сравнения, второй интегретор, квадратор, первый масштабирующий блок и первый сумматор, последовательно включенные второй масштабирующий блок и второй сумматор, причем первый вход первого блока сравнения соединен с входом управляемого фильтра, выход первого интегратора подключен к второму входу первого блока сравнения и к выходу управляемого фильтра, выход первого блока сравнения соединен с входом детектора знака, выход второго интегратора - с вторым входом второго блока сравнения, выход квадратора - с входом второго масштабирующего блока, выход первого сумматора - с дополни. тельным входом огранинителя уровня сигнала, выход второго сумматора - с дополнительным входом первого интегратора Г 2 . В известном фильтре производится - адаптация зоны ограничения ограничителя . уровня сигнала и постоянной времени интег рирования первого интегратора. С этой целью сигнал о разности измеренного и сглаженного значений сигнала подается на детектор знака, выходной сигнал которого в виде последовательности +1 и -1 сглаживается экспоненциальным сглаживаюшим фильтром, возводится в квадрат, умножается на постоянную величину и суммируется с постояьшыми сигналами. Недостатком известного управляемого фильтра является также низкая точность выделения полезного сигнала вследствие сравнительно медленной адаптации настро ечных коэффициентов управляемого фильтра при больших .по величине (скачкообразных) изменениях полезного сигнала. Цель изобретения - повышение точнос ти фильтрации. Поставленная цель достигается тем, что в управляемый фильтр, содержащий последовательно соединенные первый блок сравнения, первый вход которого подкл очен к входной шине, ограничитель уровня сигнала и первый интегратор, выход которого подключен к второму входу первого блока сравнения, детектор знака и последовательно соединенные . второй блок сравнения, второй интеграто выход которого подключен к первому вхо ду второго блока сравнения, и гсвадратор введены дополнительные блоки сравнения дополнительные интеграторы, ключи, дифференциатор, блок задержки, блок у1 шожения, элемент ИЛИ и задатчики, причем первый дополнительный блок сравнения, первый вход которого объединен с первы входом первого блока сравнения, первый дополнительныйинтегратор, выход котс рого подключен к второму входу первого дополнительного блока сравнения, дифференциатор, детектор знака; блок задержки, блок умножения, другой вход которог подключен к выходу детектора знака, второй дополнительный блок сра знения, второй дополнительный интегратор, выход которого подключен к другому входу второго дополнительного блока сравнения третий дополнительный блок сравнения, другой выход которого подключен к выхо ду первого задатчика, элемент ИЛИ и 9 44 первый ключ соединены последовательно, при этом выход дифференциатора подклк чен к второму входу второго блока сравнения, между выходом квадратора и другим входом элемента ИЛИ включен четвертый дополнительный блок сравнения, другой вход которого соединен с выходом второго задатчика, выход первого дополнительного интегратора подключен к информационным входам первого и второго ключей, управляющий вход второго ключа - к выходу элемента ИЛИ, а выход - к управляющему входу первого интегратдра, выход которого соединен с другим информационным входом первого ключа. На чертеже представлена структурная электрическая схема предлагаемого фильтра. Управляемый фильтр содержит последовательно соединенные первый блок 1 сравнения, ограничитель 2 уровня сигнала, первый интегратор 3, выход которого подключен к второму входу первого блока 1 сравнения, последовательно соединенные первый дополнительный блок 4 сравнения, и первый дополнительный интегратор 5, выход которого подключен к второму входу первого дополнительного блока 4 сравнения. Первые входы блоков 1 и 4 сравнения являются входом устройства. Выход первого дополнительного интегратора 5 подключен к информационному входу ключа 6 и к входу дифференциатора 7, выход ключа 6 подключен к второму входу первого интегратора 3. К выходу дифференциатора 7 подключеньг последовательно соединенные детектор 8 знака, блок 9 задержки, блок 10 умножения, второй дополнительный блок 11 сравнения, второй дополнительный интегратор 12, выход которого соединен с вторым входом второго дополнительного блока 11 сравнения. Выход первого задатчика 13 подсоединен к второму входу третьего дополнительного блока 14 сравнения, к первому входу которого также подсоединен выход второго дополнительного интегратора 12. Выход детектора 8 знака подключен также к второму входу блока 10 умножения. К выходу дифференциатора 7 подключены также последовательно соединенные второй блок 15 сравнения, второй интегратор 16, выход которого подключен к второму входу второго блока 15 сравнения, квадратор 17, четвертый дополнительный блок 18 сравнения, второй вход которого соединен с выходом второго задатчика

19. Выходы третьего дополнительного блока 14 сравнения и четвертого дополнительного блока 18 сравнения подключены к входам элемента ИЛИ 20, выход которого подключен к управляющим входам ключей 6 и 21. Выходы первого интегратора 3 и первого дополнительного интегратора 5 подключены соответственно к информационным входам ключа 21, выход которого является выходом фильтра. При этом X ( -t ) - измеренный в момент времени t сигнал, Х ( t ) - выходной сигнал первого интегратора 3, Х2 ( t ) - выходной сигнал первого допонительного интегратора 5, х (t ) оценка полезного сигнала (на выходе ключа 21).

Управляемый фильтр работает следующим образом.

Измеренный сигнал х ( t ) поступает на вход блока 1 сравнения, где из него вычитается выходной сигнал интегратора

3X ( t ) об оценке полезного сигнала фильтром, реализованным с помощью блока 1 сравнения, ограничителя 2 уровня сигнала и интегратора 3. Сигнал о полученной разности 6(tj x(t -5c{tJ подается на ограничитель 3 уровня сигнала, в котором срезаются большие выбросы ( t ). что повышает точность дальнейшего преобразования сигнала. Выходной сигнал ограничителя 2 уровня сигнала поступает на вход интегратора 3 Аналогично работает и фильтр второй

цепи, реализованный с помощью блока

4сравнения и интегратора 5. Для увеличения быстродействия в него- не введан ограничитель уровня сигнала и постоянная интегрирования меньше, чем в интеграторе 3. Выходные сигналы х (-fc и Xri(fc) интеграторов 3 и 5 поступают

на входы ключа 21.

Сигнал на переключение ключей 6 и 21 вырабатывается исходя из анализа свойств сигнала XQ(t). Для этого сигнал XQ(-t) поступает на вход дифференциатора 7, на выходе которого получается сигнал vet) о скорости изменения T(.n(i.J. Этот сигнал V(-fc) гщет на детектор 8 знака с законом функционирования7fi) Р ( О 1-1 при V(i) О

где 2(4;)- выходной ситналдетектора 8знака.

Сигнал 2 ()с выхо;1а детектора 8 знака постутгает на блок 9 задержки, где задерживается на время t и подает ся на блок 10 умножения, где умножается на сигнал 2 (t). Тем самым на выходе блока 10 умножения получается сигнал о знаковой корреляции 2(thi 2(t-T). Этот сигнал подается на сглаживающий фильтр, реализованный с помощью блока 11 сравнения и интегратора 12. В результате получаем если сигнал У()имеет знакопеременный характер, то сигнал о знаковой корреляции имеет также знакопеременный характер, а выходной сигнал интегратора 12 стремится к нулю; если сигнал V(t) имеет один знак положительный или отрицательный, то сигнал о знаковой корреляции равняется + 1, а выходной сигнал интегратора, 12 стремится к +1.

В первом случае в сигнале x(-tJnpHсутствует высокочастотная составляющая обусловленная помехой и поэтому целесообразно подключение на вход устройства выхода интегратора 3. Во втором случае имеет место большая скорость изменения полезного сигнала, и поэтому целесообразно подключение на вход устройства выхода интегратора 5. С этой целью выходной сигнал интегратора 12 сравнивается в блоке 14 сравнения с постоянным сигналом, поступающим с первого задатчика 13 и подается на элемент ИЛИ 20.

Кроме того, выходной сигнал дифференциатора 7 поступает на сглаживающий фильтр, реализованный с помощью блока 15 сравнения и интегратора 16, а затем возводится в квадрат в квадраторе 17 для устранения знака сигнала. Выходной сигнал квадратора 17 сравнивается в блоке 18 сравнения с постоянным сигналом, поступающим со второго задатчика 19, и подается на элемент ИЛИ 2О.

Если сигнал с выхода интегратора 12 и (или) сигнал с выхода квадратора 17 превышает задание величины, то в элементе ИЛИ 2О вырабатывается сигнал, поступающий на управляющий вход ключа 21, который подключает к выходу устройства сигнал выхода интегратора 5. В это же время ключ 6 находится в разомкнутом состоянии.

Если же сигналы с выходов интегратора12 и квадратора 17 не превышают заданные величины, то ключ 21 подключается к выходу устройства сигнал X(t) с выхода интегратора 3. В момент, когда происходит переключение, по сигналу с выхода элемента ИЛИ 20 включается ключ бив интегратор 3 записываются новые начальные условия с выхода интегратора 5. Затем через заданный про-межуток времени ключ 6 выключается. В результате в интегратор 3 вводятся новые начальные условия, соответствующие выходному сигналу интегратора 5. Применение предлагаемого устройства позволяет повысить точность выделения полезного сигнала в среднем на 35-45% по среднеподульному критерию, что приводит к повышению точности расчета управляющих воздействий в прогнозируки щих регуляторах. Формула изобретения Управляемый фильтр, содержащий последовательно соединенные первый блок сравнения, первый вход которого подклю чен к входной шине, ограничитель уровня сигнала и первый интегратор, выход кото рого подключен к второму входу первого блока сравнения, детектор знака и последовательно соединенные второй блок сравнения, второй интегратор, выход которого подключен к первому входу второ го блока сравнения, и квадратор, о т л и чаюшийся тем, что, с целью повышения точности фильтрация, в него вв дены дополнительные блоки сравнения, дополнительные интеграторы, ключи, дифференциатор, блок задержки, б,ок умножения, элемент ИЛИ и зацатчики, причем первый дополнительный блок срав нения, первый вход которого об)единен с первым входом первого блока сравне- ния, первый дополнительный интегратор. выход которого подключен v. старому входу первого дополнительного блгжа сравнения, дифференциатор, детектор знака, блок задержки, блок умножения, другой вход которого подключен к выходу детектора знака, второй дополнительный блок сравнения, второй дополнительный интегратор, выход которого подключен к другому входу второго дополнительного блока сравнения, третий дополнительный блок сравнения, другой выход которого подключен к выходу первого задатчика, элемент ИЛИ и первый ключ соединены последовательно, при этом выход дифференциатора подключен к второму входу второго блока сравнения, между выходом квадратора и другим входом элемента ИЛИ включен четвертый дополнительный блок сравнения, другой вход которого соединен с выходом второго задатчика, выход первого дополнительного интегратора подключен к информационным входам первого и второго ключей, управляющий вход второго ключа - к выходу элемента ИЛИ, а выход - к управляющему входу первого интегратора, выход которого соединен с другим информационным входом первого ключа. Источники информации, принятые во внимание при экспертизе 1.Патент Великобритании № 1469605, кл. Н 3 W , 1977. 2.Авторское свидетельство СССР . по заявке № 2848482/О9, кл. Н 03 Н 21/00, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Сглаживающий фильтр | 1981 |

|

SU980065A1 |

| Сглаживающий фильтр | 1983 |

|

SU1117583A2 |

| Сглаживающий фильтр | 1981 |

|

SU1003302A1 |

| Адаптивная двухцелевая система управления | 1982 |

|

SU1100608A1 |

| Управляемый сглаживающий фильтр | 1982 |

|

SU1061250A1 |

| Управляемый фильтр | 1980 |

|

SU959268A2 |

| Управляемый фильтр | 1981 |

|

SU1004962A1 |

| Управляемый фильтр | 1979 |

|

SU884082A1 |

| Адаптивная система регулирования объекта с нестационарной характеристикой,например,дуговой сталеплавильной печи | 1983 |

|

SU1068891A1 |

| Управляемый фильтр | 1984 |

|

SU1149214A1 |

Авторы

Даты

1982-10-30—Публикация

1981-04-24—Подача