Изобретение относится к радиотех нике и может быть использовано для запаздывающего вьщеления полезной низкочастотной составляющей измерен ных сигналов, которая может быть применена, например, при решении за дач запаздьшающего моделирования, а также в обучающихся по предыстории системах. Известен интерполирующий фильтр содержащий блоки задержки, выходы которых через масштабирующие блоки подключены к блоку суммирования 13 Недостаток интерполирующего фильтра заключается в низкой точнос фильтрации. Наиболее близким к изобретению ПО технической сущности является интерполирующий фильтр-, содержащий последовательно соединенные элемент сравнения, ограничитель, интегратор блок задержки-,и сумматор, п блоков памяти (п+1) блоков вычитания, (п+1) блоков ограничения и (п+1) масштабирующих элементов, при этом выход интегратора подключен к второ му входу элемента сравнения, первый вход которого является входом устройства ii-й блок памяти, 1-й блок вычитания, i-й блок ограничения и i-й масштабируюищй элемент (,2, ..п) включены последовательно между входом устройства и (1+1)-ым входом сумматора, (п+1)-и блок вычитания, (п+1)-й блок ограничения и (п+1)-й масштабирующий элемент включены последовательно между входом устройст ва и (т1+2)-ым входом сумматора, а выход блока задержки соединен с вто рым входом блока вычитания С21. Недостатком известного интерполирующего фильтра я-вляется низкая точность фильтрации, так как уточнение предварительно сглаженного сигнала х (t-t) производится по конечному числу, равному п+1, разностей между этим сигналом и значениями входного сигнала устройства на интервале времени Ct-t, t, а не по всем значениям разностей соот ветствующих непрерывных сигналов внутри указанного отрезка времени. Повысить точность вьиеления полезного сигнала с помощью известного интерполирующего фильтра можно путем увеличения количества (п+1) учи тываемых разностей, -однако это связано с повышением сложности устройства, Кроме того, упомянутые разности находятся мевду- значениями входного сигнала x( , относящимися к разным моментам времени t-6-i внутри временного интервала Ct-tr, tl и только одним значением предвари- тельно сглаженного сигнала x(t-t ), тем самым не используется полученная к моменту времени t полезная информация о значениях предварительно сглаженного сигнала внутри отрезка времени tt-t , t1 Целью изобретения является повышение точности фильтрации.. I . Цель достигается тем, что в интерполирующий фильтр, содержащий последовательно соединенные элемент сравнения, первый вход которого является входом интерполирующего фильтра, ограничитель, первый интегратор, блок задержки и сумматор, а также четьфе блока шлчитания, пять масштабирующих элементов и блок памяти, при этом второй вход элемента сравнения подключен к выходу первого интегратора., введены второй, третий, четвертый и пятый интеграторь, четыре блока: умножения и задатчик, при том последовательно соединенные второй интегратор, первый блок вычитания и первый блок умножения включены между выходом ограничителя и вторым входом сумматора, последовательно соединенные третийинтегратор, второй блок вычитания и второй блок умножения включены между выходом первого блока вычитания и третьим входом сумматора, последовательно соединенные первый масштабирующий элемент, четвертый интегратор, третий блок вычитания и третий блок умножения включены между выходом второго блока вычитания и четвертым ВХОДОМсумматора, последовательно соединенные второй масштабирующий элемент, пятый интегратор, четвертый блок вjычитaния и четвертый блок умножения включены между выходом третьего блока вычитания и пятым входом сумматора, последовательно соединенные блок памяти, выход которого подключен к второму входу первого блока вычитания, третий масштабирующий элемент, выход которого подключек к второму входу второго блока вычитания, четвертый масштабирующий

элемент8выход которого подключен к ВТО.РОМУ входу третьего блока вычитания, и пятый масштабирующий элемент включены между выходом второго интегратора и вторым входом четвертого блока вычитания, причем выход задатчика подключен к вторым входам первого, второго, третьего и четвертого блоков умножения.

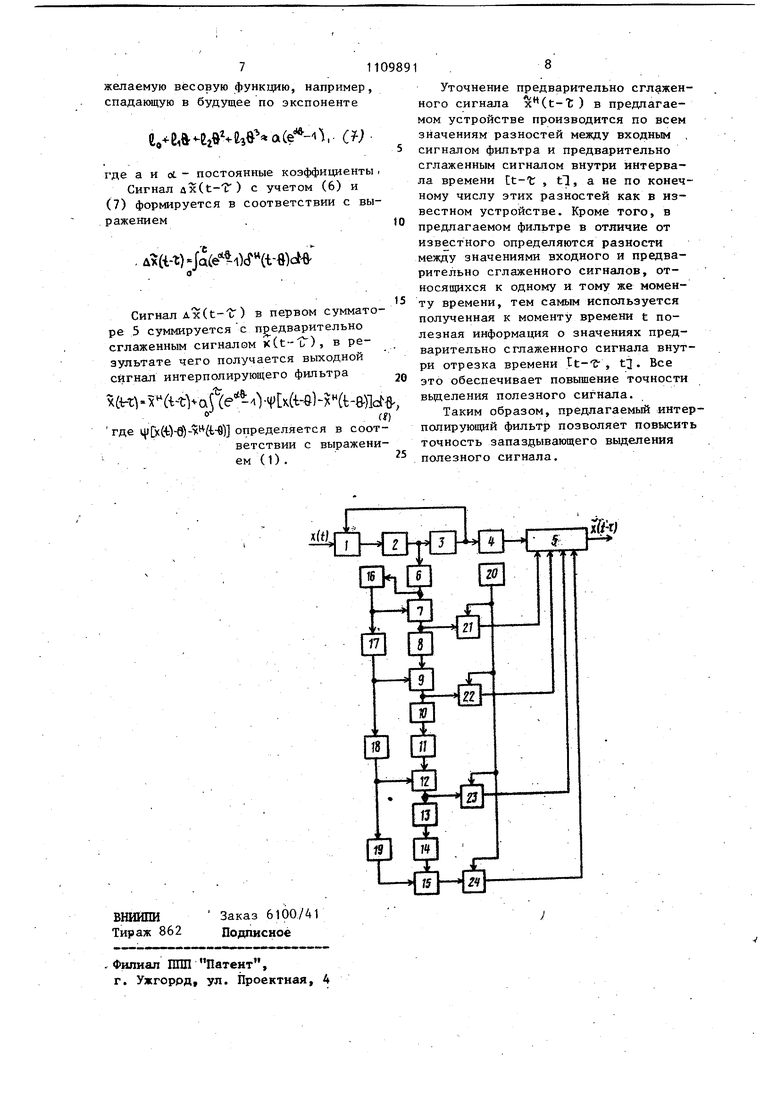

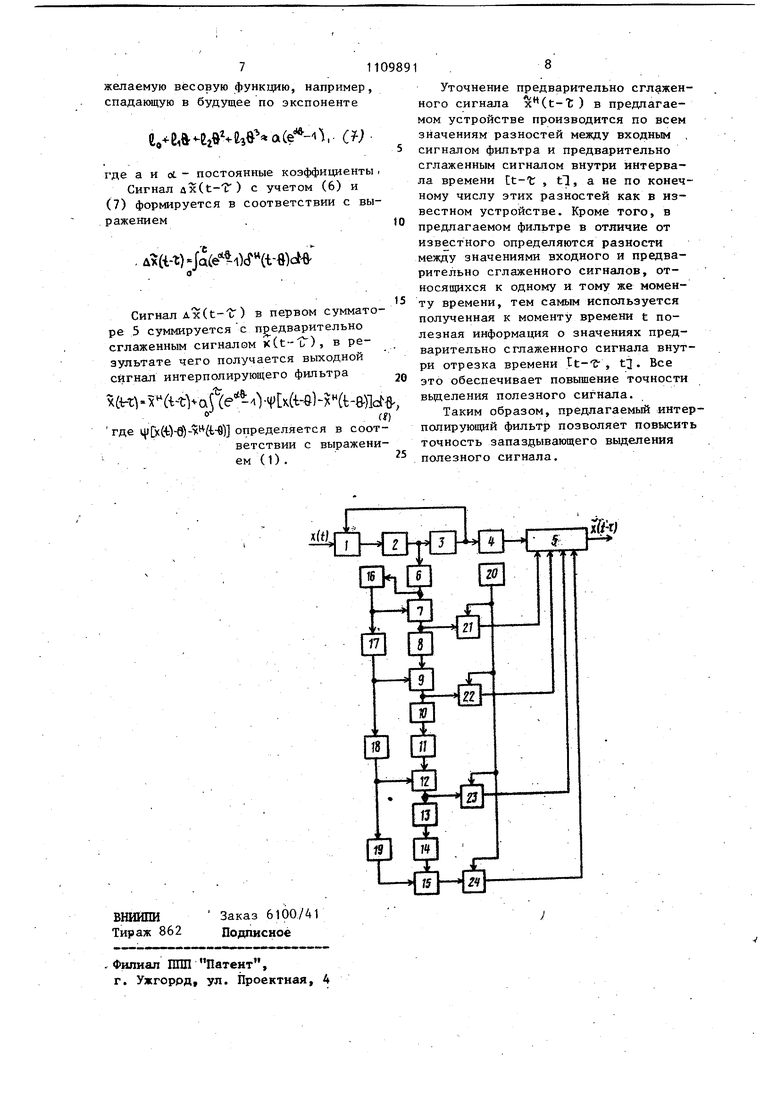

На чертеже предстайНена структурная электрическая схема интерполирующего фильтра.

Интерполирующий фильтр содержит последовательно соединенные элемент 1 сравнения, ограничитель 2, первый интегратор 3, блок 4 задержки и сумматор 5, причем выход первого интегратора 3 связан с вторым входом элемента 1 сравнения,первый вход которого является входом фильтра, последовательно соединенные второй .интегратор 6, вход которого подключен к выходу ограничителя 2, первый блок 7 вычитания, третий интегратор 8j второй блок 9 вычитания, первый масштабирующий элемент 10, четвертый интегратор 11, третий блок 12 вычитания , второй масштабирующий элемент 13-, пятый интегратор 14 и четвертый блок 15 вычитания, последовательно соединенные блок 16 памяти, третий масштабирующий элемент 17, четвертый масштабирующий элемент 18 и пятый масштабируюш ий элемент 19, подключенные между выходом второго интегратора 6 и вторым входом четвертого блока 15 вычитания, входы третьего 17, четвертого 18 и пятого 19 масщтабируюших элементов объединены с вторыми входами соответственно первого, второго и третьего блоков 7, 9 и 12 вычитания, задатчик 20, первый, второй, третий и четвертый блоки 21-24 умножения, первые входы которьк соединены с выходами соответствующих блоков 7, 9, 12 и 1 вычитания, вторые входы соединены с выходом задатчика 20, а выходы подключены к второму, третьему, четвертому и пятому входам сумматора:5

На чертеже обозначены x(t) - вхоной сигнал устройства-, x(t-t ) сглаженный сигнал на выходе устройства ,

Интерполирующий фильтр работает следующим образом.

Входной сигнал x(t) предварительно сглаживается фильтром низкой

частоты, состоящим из элемента 1 сравнения, ограничителя 2 и первого интегратора 3. С этой целью сигнал x(t) поступает на первый вход элемента 1 сравнения, где из него вычитается выходной сигнал фильтра низкой частоты x(t) ,-поступающий с выхода первого интегратора 3. Полученная разность

i«(t) x(t) - x«(t)

поступает на вход ограничителя 2, который может быть реализован, например , в виде усилителя с насыщени5ем. Если сигнал .(-) превьшгает величину ограничивающего напряжения Jj, то в ограничителе 2 он огранич;ивается до этой величины. Это можно представить выражением

0

t)--fC 4t h4 «UHeS-S« l . Ujb еслц «4t).,.

где ) - выходной сигнал ограни5чителя 2 i

Сигнал crCt) поступает на вход первого интегратора 3 и интегрируется в нем. С выхода первого интегра0 тора 3 предварительно сглаженный . фильтром низкой частоты сигнал x(t) подается на вход блока 4 задержки, где запоминается на интервал времени Ь . Сигнал Т) с выхода

5 блока 4 задержки поступает на первый вход сумматора 5.

Выходной сигнал интерполирующего фильтра формируется путем уточнения предварительно сглаженного сигнала

0 x(t-t) по разностям между знамениями этого сигнала и входного сигнала устройства на интервале времени It-t , tl.

С этой целью сигнал 5(t) с вы5 хода ограничителя 2 поступает на

вход второго интегратора 6, в котором он интегрируется. Сигнал с выхода второго интегратора 6 поступает на вход блока 16 памяти, в котором

50 он задерживается на интервал времени t, и далее на вход первого блока 7 вычитания, в котором он вычитается из сигнала с выхода второго интегратора 6.

Сигнал с выхода первого блока 7 вычитания поступает на вход третьего интегратора 8, в котором он интегрируется , Сигнал с выхода блока 16 памяти подается на вход третьего масш табирзпощего элемента 17, умножается в нем на коэффициент Ут,. и поступает далее на вход второго блока 9 вычитания, в котором он вычитается из сигнала с выхода третьего интегр тора 8. Сигнал с выхода второго блока 9 вычитания поступает на вход первого масштабирующего элемента 10, умножа ется в нем на коэффициент jj 2 и подается далее на. вход четвертого интегратора 11, в котором он интегрируется. Сигнал с выхода третьего масштабирующего элемента 17 подается на вход четвертого масштабирующего элемента 18, умножается в нем на ко эффициент и Поступает далее на вход третьего блока 12 вычитания, в котором он вычитается из сигнала с выхода четвертого интегратора 11. Сигнал с выхода третьего блока 12 вычитания поступает на вход второ го масштабирующего элемента 13, умно жается в нем на коэффи1Ц1ент Jfi 3 и подается далее на вход пятого интегратора 14, в котором он интегрируется. Сигнал с выхода четвертого масштабируяицего элемента 18 подается на вход пятого масштабирукщего элемента 19, умножается в нем на коэффициент и поступает далее на вход четвертого блока 15 вычитания, в котором он вычитается из сигнала с выхода пятого интегратора 14. Коэффициенты усиления второго, третьего, четвертого и пятого интеграторов 6, 8, 11 и 14 устанавливаются равными единице. Передаточная функция схемы, состо щей из блоков 6, 7 и 16 имеет вид )/ - передаточная функция ин тегратора; - передаточная функция блока 16 памяти, а соответствующая импульсная характерисV-,/оЧвИ, ©САМ Чо если (2) Передаточная функция схемы, состоящей из блоков 6, 7, 8, 9, 16 и 17, имеет вид W., а соответствующая импульсная характеристика (в,Сд :.,«« «САМ t Передаточная функция схемы, состоящей из блоков 6, 7, 8, 9, 10, 11, 12, 16, 17 и 18, имеет вид Nk/2( ) ..е..« Р-, а соответствующая импульсная характеристика если (д){о: «САИ Передаточная функция схемы, состоящей из блоков 6-19, имеет вид ) -е а соответствующая импульсная характеристикад если OidA- ; () - «САМ . (5) Сигналы с выходов блоков 7, 9, 12 и 15 вычитания поступают-на первые входы соответствующих блоков 21-24 умножения, умножаются в них на коэффициенты to, t , f и t, задаваемые с выхода задатчика 20 на торые входы блоков 21-24 умножения, подаются далее на второй, третий, етвертый и пятый входы сумматора 5, котором они суммируются, в резуль ате чего получается сигнал ux(t-C). Импульсная характеристика схемы, ходом которой является входной сигал d(t) второго интегратора 6, а ыходом - результат суммирования x(t-t), имеет вид йНой)о( e,«,(e«%() ) ,« есАМ lO, «САМ -ftyt, выходной ux(t-lr ) сигнал этой схемы формируется в соответствии с выражением(t-tbx4t-t)vaf().4 LxMmi-ft a r(; Коэффициенты to, J-i, г г Устанавливаются на выходе задатчика 20 таким образом, чтобы обеспечить

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполирующий фильтр | 1985 |

|

SU1241421A2 |

| Управляемый сглаживающий фильтр | 1982 |

|

SU1061250A1 |

| Интерполирующий фильтр | 1982 |

|

SU1030958A1 |

| Адаптивный прогнозатор | 1982 |

|

SU1049866A1 |

| Сглаживающий фильтр | 1981 |

|

SU1003302A1 |

| Управляемый фильтр | 1984 |

|

SU1149214A1 |

| Адаптивная система регулирования многомерного объекта | 1981 |

|

SU1174901A1 |

| Управляемый фильтр | 1981 |

|

SU970644A1 |

| Адаптивная система регулирования объекта с нестационарной характеристикой,например,дуговой сталеплавильной печи | 1983 |

|

SU1068891A1 |

| РЕГУЛЯТОР | 1990 |

|

RU2015520C1 |

ИНТЕРПОЛИРУКШЩЙ ФИЛЬТР,- содержащий последовательно соединенные элемент сравнения, первый вход которого является входом интерполирующего фильтра, ограничитель, первьй интегратор, блок задержки и сумматор, а также четыре блока вычитания, пять масштабирующих элементов и блок памяти, при этом второй вход элемента сравнения подключен к выходу первого интегратора, отличающ и и с я тем, что,, с целью повьш1ения точности фильтрования в него введены второй, третий, четвертый и пятый интеграторы, четыре блока умножения и задатчик, при этом последовательно соединенные второй интегратор, первый блок вычитания и первьй блок умножения включены между выходом ограничителя и вторым входом .сумматора, последовательно соединенные третий интегратор, второй блок вычитания и второй блок умножения включены между выходом первого блока вычитания и третьим входом сумматора, последовательно соединенные первый масштабирующий элемент, четвертый интегратор, третий блок вычитания и третий блок умножения включены между выходом второго блока вычитания и четвертым входом сумматора, последовательно соединенные второй масштабирую1щй элемент, пятый интегратор, четвертый блок вычитания и четвертый блок умножения включены между выходом третьего блока вычитания и пятым входом сумматора, последовательно соединенные блок памяти, выход которого подключен к второму входу первого блока вычитания, третий масштабирующий элемент, выход которого подключен к второму входу С0 00 второго блока вычитания, четвертый ма штабирукяций элемент, выход которого подключен к второму входу третьесо го блока вьиитания, и пятый масштабиру ощий элемент включены между выходом второго интегратора и вторым входом четвертого блока вычитания, причем выход задатчика подключен к вторым входам первого, второго, третьего и четвертого блоков умножения.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ицкович Э.Л | |||

| Контроль производства с помощью вычислительных машин | |||

| М., Энергия, 1975, с | |||

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Интерполирующий фильтр | 1982 |

|

SU1030958A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-08-23—Публикация

1983-04-07—Подача