(54) УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов с дробным коэффициентом деления | 1985 |

|

SU1265997A1 |

| Цифровой частотомер | 1973 |

|

SU447637A1 |

| Дробный делитель частоты следования импульсов | 1981 |

|

SU993480A1 |

| Делитель частоты с дробным автоматическиизМЕНяющиМСя КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU819966A1 |

| Программируемый делитель частоты следования импульсов | 1980 |

|

SU945998A1 |

| Делитель частоты с управляемым коэффициентом деления | 1986 |

|

SU1334370A1 |

| Делитель частоты следования импульсов с управляемым дробным коэффициентом деления | 1982 |

|

SU1043827A1 |

| Дробный делитель частоты следования импульсов | 1983 |

|

SU1120490A1 |

| Делитель частоты с дробным коэффициентом деления | 1978 |

|

SU750744A1 |

| Устройство для деления частоты импульсов с дробным коэффициентом деления | 1977 |

|

SU621101A1 |

1

Изобретение относится к импульсной технике и может найти применение в цифровых приборах.

Известен управляемый делитель частоты с дробным коэффициентом деления, содержащий пересчетный блок, сумматор, вентили дробной и целой части, элемент эапрета, элемеит задержки и триггер 1.

Недостатками указанного устройства являются низкое быстродействие и узкий диапазон частот следования входных импульсов, что обусловлено структурой устройства; содержащего последовательно включенные пересчетиый блок и сумматор, для которого характерно низкое быстродействие.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее элемент запрета, вентиль, источник кода -шслителя. источник кода знаменателя, элемент ИЛИ, сумматор, триггер и элемент задержки 2.

Недостатком известного устройства является низкое быстродействие.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в управляемьш делитель частоты с дробным коэффициентом деления, содержащий источник кода числителя, источник кода знаменателя и блок вентилей, введены.регистр, первый сумматор и второй сумматор, выход переиоса которого соединен с управляющим входом блока вентилей, группа входов которого соединена с выходами ис10точника кода числителя, а группа выходов - с первой группой входов первого сумматора, вторая группа входов которого соединена с группой выходов второго сумматора, а выходы - с входами регистра, управляющий вход

15 которого соединен с входной шиной,а выходы - с первой группой входов второго сумматора, вторая группа входов которого соединена с выходами источника кода знаменателя.

20

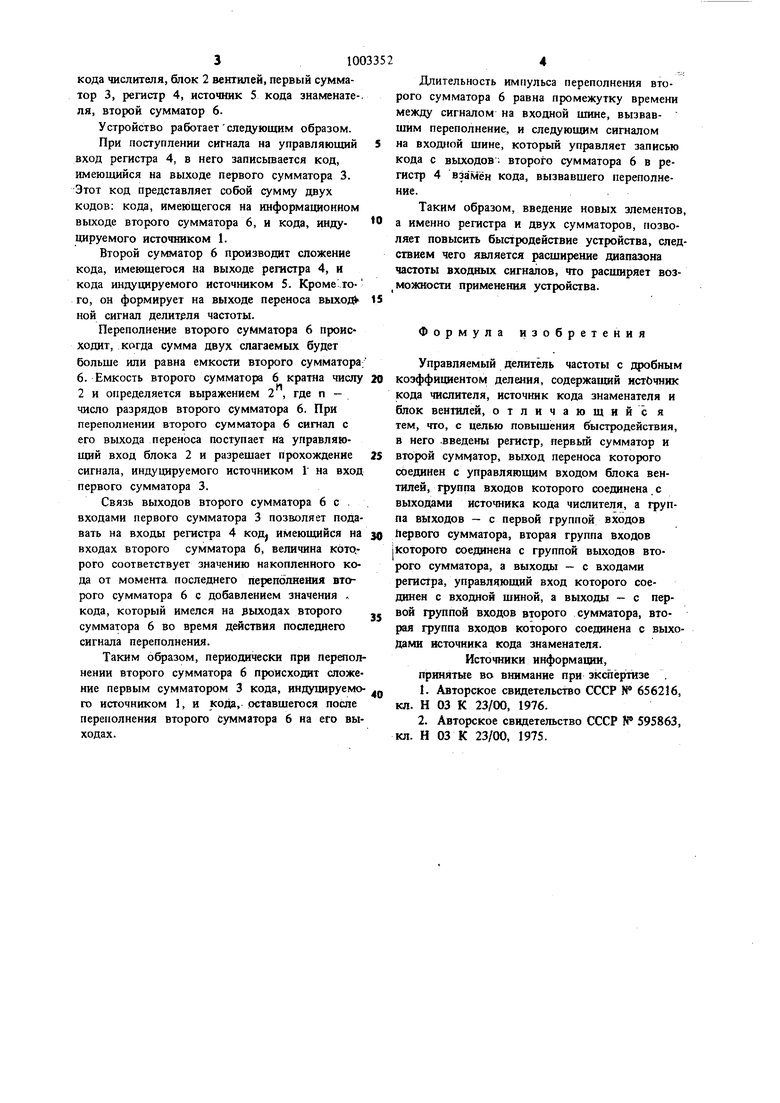

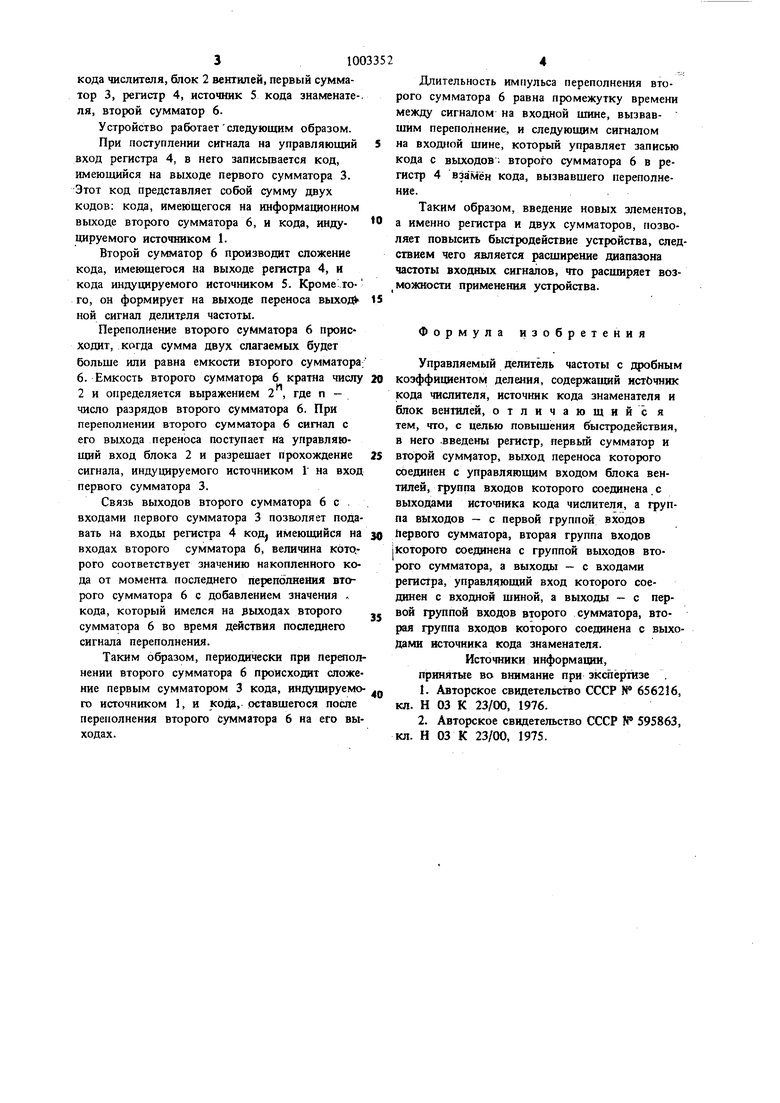

На чертеже представлена структурная схема предлагаемого устройства.

Управляемый делитель частоты с дробным коэффициентом деления содержит исючмик 1 3100 кода числителя, блок 2 вентилей, первый сумматор 3, регистр 4, источник 5 кода знаменате-. ля, второй сумматор 6. Устройство работаетследующим образом. При поступлении сигнала на управляющий вход регистра 4, в него записьгеается код, имеющийся на выходе первого сумматора 3. Этот код представляет собой сумму двух кодов: кода, имеющегося на информационном выходе второго сумматора 6, и кода, индуцируемого источником 1. Второй сумматор 6 производит сложение кода, имеющегося на выходе регистра 4, и кода индуцируемого источником 5. Кроме: того, он формирует на выходе переноса выхода ной сигнал делителя частоты. Переполнение второго сумматора 6 происходит, когда сумма двух слагаемых будет больще или равна емкости второго сумматора; 6. Емкость второго сумматора 6 кратна числу 2 и определяется выражением 2 , где п - число разрядов второго сумматора 6. При переполнении вторюго сумматора 6 сигнал с его выхода переноса поступает на управляющий вход блока 2 и разрещает прохождение сигнала, индуцируемого источником 1 на вход первого сумматора 3. Связь выходов второго сумматора 6с. входами первого сумматора 3 позволяет подавать на входы регистра 4 код имеющийся на входах второго сумматора 6, величина кото,рого соответствует значению накопленного кода от момента последнего переполнения второго сумматора 6 с добавлением значения . кода, который имелся на выходах второго сумматора 6 во время действия последнего сигнала переполнения. Таким образом, периодически при перепол нении второго сумматора 6 происходит сложение первым сумматором 3 кода, индуцируемо го источником 1, и кода,, оставшегося после переполнения второго сумматора 6 на его выходах. Длительность импульса переполнения второго сумматора 6 равна промежутку времени между сигналом на входной шине, вызвавшим переполнение, и следующим сигналом на входной щине, который управляет записью кода с ВЫХОДОВ, второго сумматора 6 в регистр 4 взамён кода, вызвавшего переполнение. Таким образом, введение новых элементов, а именно регистра и двух сумматоров, позволяет повысить быстродействие устройства, следствием чего является расщире1Ше диапазона частоты входных сигналов, что расширяет возможности применения устройства. Формула изобретения Управляемый делитель частоты с дробным коэффициентом деления, содержащий истЬчник кода числителя, источник кода знаменателя и блок вентилей, отличающий с я тем, что, с целью повыщения быстродействия, в него .введены регистр, первый сумматор и второй сумматор, выход переноса которого сбединен с управляющим входом блока вентилей, группа входов которого соединена с выходами источника кода числителя, а группа выходов - с первой группой входов tiepBoro сумматора, вторая группа входов j Которого соединена с группой выходов второго сумматора, а выходы - с входами регистра, управляющий вход которого соединен с входной шиной, а выходы - с первой группой входов второго сумматора, вторая группа входов которого соеданена с выходами источника кода знаменателя. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 656216, кл. Н 03 К 23/00, 1976. 2.Авторское свидетельство СССР № 595863, кл. Н 03 К 23/00, 1975.

Авторы

Даты

1983-03-07—Публикация

1981-10-06—Подача