13343702

Изобретение относится к импульснойвлены по двоичному закону (соответтехнике и может быть использовано вственно С,2С,...,2 С). Вторые выводы

,измерительных системах, в синтезато-конденсаторов 13-1,13-2,.,.,13-р черах частот,рез соответствующие ключи ,

Цель изобретения - повьшение быст-14-2,...,14-р из набора ключей соедиродействия при перестройке частотынены с общей шиной. Управляющие входы

и надежности,ключей 14-1,14-2,,,.,14-р соединены

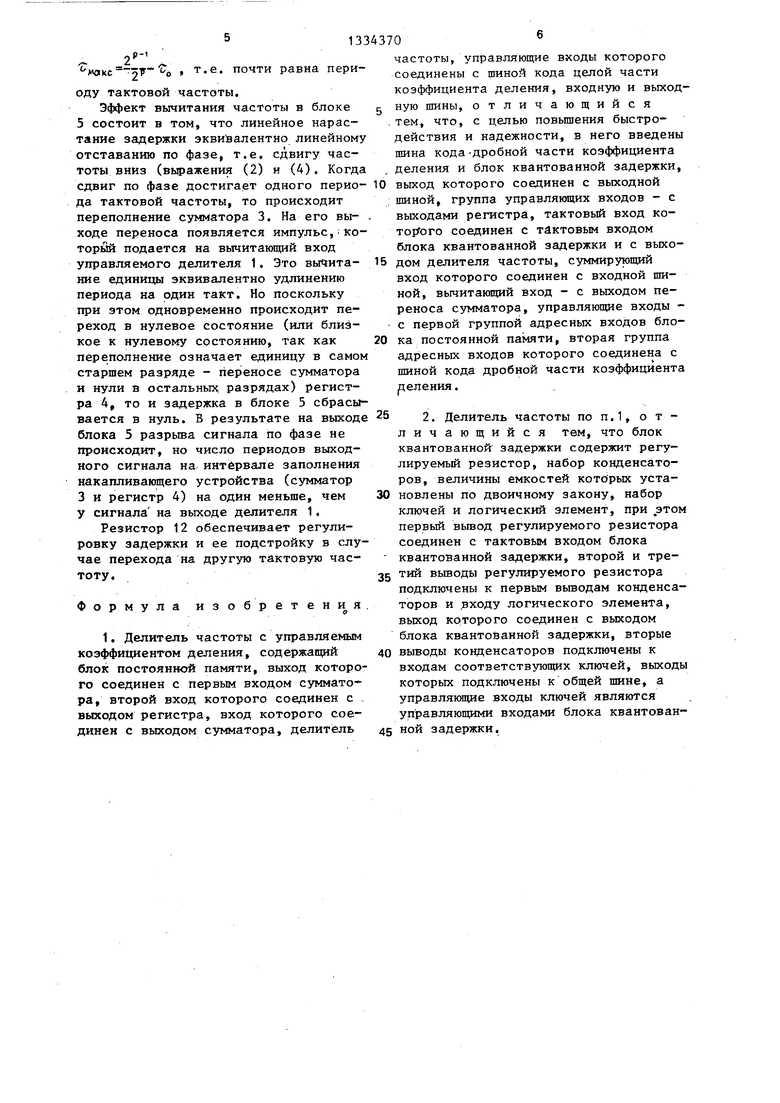

На фиг,1 приведена электрическаяс соответствующими управлякщими вхоструктурная схема устройства; на юдами 11-1,11-211-р блока квантофиг,2 - причем вьтолнения блока кван-ванной задержки,

тованной задержки.Делитель работает следующим обра- Делитель частоты с управляемымзом,

коэффициентом деления содержит дели- - Представим коэффициент деления чатель 1 частоты, блок 2 постоянной 15стоты Кд5 в виде целой и дробной чапамяти, сумматор 3, регистр 4, блоксти Кде А+а,

5 квантованной задержки, входную ши- Выходная частота устройства fg

ну 6, шину 7 дробной части коэффици-образуется из тактовой частоты f пуента деления, шину 8 целой части ко-тем деления в К. раз, т.е, fgb,,,

эффициента деления, выходную шину 9, 20

Блок 5 квантованной задержки име- f /К.,. :--Т iy В Л

ет тактовый вход 10. управляющие входм 11-1, 11-2,,,,,11-р, регулируемьй Домножим числитель и знаменатель

резистор 12, набор конденсаторов ° ° вьфажения на (А -А а+,,,-ь

.п п

13-1, 13-2,,,,, 13-р, набор ключей 25 .,. .J .- - i , .. - -

ил л г f л tы .av,,, -а ) тт

-1, 14-2, ,,,, 14-р, логический,А+а

элемент 15, выход 16, Входная шина 6 (для четного п}, тогда

соединена с суммирующим входом дели- , , ,

теля 1 частоты, управляющие входы ко- f -rjr -( а+... + () fj а +

торого соединены с шиной 8 кода целой зо д л

части коэффициента деления и с первой .,.а а ),

группой адресных входов блока 2 пос- .,, ,

Минимальное значение А..., а тоянной памяти, вторая группа адрес- . /„р

I f fj rtf максимальное значение а„.,. 1-1/2 , ных входов которого соединена с шиной

, „ .,где р - количество разрядов двоичного

7 кода дробной части коэффициента де- „

о . „ .35 представления дробной части, ления. Выход блока 2 постоянной памя- гт лп п Для А «а необходимо, чтобы п

ти соединен с первым входом сумматора - -и „

о ..было больше некоторого числа п., Наи3, второй вход которого соединен с.

/Дем его следующим образом

выходом регистра 4 и с управляющим

входом блока 5 квантованной задержки, Q ,. 1 о Пд1„( . выход которого соединен с выходной2

шиной 9, тактовый вход - с выходомгде 1„ (1-1/2 ) - -1/2 , делителя 1 частоты и с тактовым входом регистра 4, Вычитаюящй вход дели- Если допустимое значение з. не теля 1 частоты соединен с выходом должнОрПревьш1ать некоторого а , то

переноса сумматора 3, выход которого . откуда /По/ /2 1„а,/,

соединен с входом регистра 4,Например, , , п «100, ТаВ блоке 5 квантованной задержкиким образом, при некотором пгПд

выход логического элемента 15, в ка-А а и в знаменателе выражения (1)

честве которого может быть использо- вместо А - а можно записать А ,

ван логический инвертор, соединен сТогда (1) упрощается и принимает вид вь1ходом 16, Первый вьшод регулируемо- - , 2 дз пго резистора 12 соединен с тактовым аых А А А А входом 10 блока 5 квантованной задержки, второй и третий выводы - с вхо- f f fi-с ч

л f-55 Т. V -ч /

дом логического элемента 15 и с пер- А А

выми выводами конденсаторов 13-1,г де | по формуле суммы членов геомет13-2, ,,,, 13-р из набора конденсато-рической прогрессии можно свести к

ров, величины емкости которых устано-виду

,,,-ь

.п п

h-i

i:(-i)

I a

A

lh

1+a/A

Из выражения (2) следует, что можно использовать делитель частоты на целое число А, но в выходную частоту вводить поправку - вычитать некоторую часть выходной частоты , определяемую коэффициентом | из выражения (3), Если в выражении (2) от частоты перейти к фазе t

j вых

V

dt 2 r|bt-2 fr| t, А AS

(4)

то поправка по фазе &Y 27-- t

BDIX А 7

образуется линейным накоплением во времени коэффициента . Отсюда, для получения частоты fg необходимо иметь, кроме делителя частоты в А раз устройство вычисления коэффициента I по данным А и а (по формуле 3); устройство для накопления t; устройство для вычитания фазы - блок квантованной задержки.

В качестве вычислительного устройства используется блок 2 постоянной памяти, поскольку каждому сочетанию целой и дробной частей А и а соответствует однозначно коэффициент . Нап3

ример, при (, ,

f 0,0447 или в двоичном коде

0,00001011, при Кде, 1, 0,407

или в двоичном коде 0,01101000. Накапливающее устройство образовано соответствующим соединением сумматора 3 и регистра 4, причем на тактовьй вход регистра подаются выходные импульсы делителя 1 частоты . Поэтому в накопителе за единицу времени накапливается

чисел

т.е.

-Ч

А

а в текущем времени

t.

Это число поступает на блок 5 квантованной задержки, которая представляет собой импульсную задержку, управляемую двоичным кодом. Максимальная длина задержки равна одному периоду тактовой частоты. Постепенное, линейное во времени увеличение задержки .эквивалентно вычитанию частоты в соответствии с выражением (4).

34370

Импульсы тактовой (входной) частоты по шине 6 поступают на суммирующий вход делителя 1. На управляющие входы делителя 1 поступает код целой части коэффициента деления А с шины 8. На выходе делителя 1 появляются импульсы с частотой fgp,, f /А. На адресные входы блока 2 поступают коды целой

Q (А) и дробной (а) частей коэффициента деления с шин 7 и 8. С выходов блока 2 снимается число, определяемое выражением (3). Число поступает на первый вход сумматора 3, на его второй

Ig вход поступает число, записанное в регистре 4.

С каждым импульсом частоты f /А, подаваемым на тактовый вход регистра 2Q 4, в Него записьшается сумма числа | с числом регистра 4. Таким образом, производится накопление чисел , Очевидно, что за время t накапливает35

25 ся число I --t, --t - число им гл.А.

пульсов записи в регистр 4. Это число поступает на управляющие входы блока

2Q 5, где время задержки ZJj Т,- С - элементарная задержка на единицу

кода. Код числа подается

(фиг.2) на входы 1 1-1,11-2,. .,, 11-р. Логическая единица, поданная на управляющий вход ключа 14-1,14-2,..,, 14-р, подключает соответствующий конденсатор 13-1,13-2,...,13-р. Причем

40 У конденсатора 13-2 емкость в два

раза больше, чем у конденсатора 13-1, у конденсатора 13-3 - в 2 раза больше, чем у конденсатора 13-2 и т.д. Таким образом, величина емкости про45 порциональна числу в двоичном коде, подаваемому по шине 11-1,11-2,..., 11-р. Вместе с регистром 12 эти конденсаторы образуют интегрирующую цепь с постоянной времени , R( f С; ) .

i -

50 Перепад напряжения, поступающий на вход 10, задерживается на время и поступает на вход элемента 15 (это может быть инвертор, триггер Шмитта), которьм снова формирует крутой фронт

55 сигнала, но задержанный на время Г,. Элементарная задержка t RC составляет 1/2 часть периода тактовой частоты f , а максимальная задержка

о -. f

макс о

т.е. почти равна периоду тактовой частоты.

Эффект вычитания частоты в блоке 5 состоит в том, что линейное нарастание задержки экви валентно линейному отставанию по фазе, т.е. сдвигу частоты вниз (выражения (2) и (А). Когда

сдвиг по фазе достигает одного перио- 10 выход которого соединен с выходной да тактовой частоты, то происходит шиной, группа управляющих входов - с

На

переполнение сумматора 3. На его выходе переноса появляется импульс,ко- торйй подается на вычитающий вход управляемого делителя 1. Это вычитание единицы эквивалентно удлинению периода на один такт. Но поскольку при этом одновременно происходит переход в нулевое состояние (или близкое к нулевому состоянию, так как переполнение означает единицу в самом старшем разряде - переносе сумматора и нули в остальньщ разрядах) регистра 4, то и задержка в блоке 5 сбрасывается в нуль. В результате на выходе блока 5 разрыва сигнала по фазе не происходит, но число периодов выходного сигнала на интервале заполнения накапливающего устройства (сумматор 3 и регистр 4) на один меньше, чем у сигнала на выходе делителя 1.

Резистор 12 обеспечивает регулировку задержки и ее подстройку в случае перехода на другую тактовую частоту.

вькодами регистра, тактовый вход ко- Topforo соединен с ТАКТОВЫМ входом блока квантованной задержки и с выхо

15 дом делителя частоты, суммирующий вход которого соединен с входной щи- ной, вычитающий вход - с выходом переноса сумматора, управляющие входы с первой группой адресных входов бло

20 ка постоянной памяти, вторая группа адресных входов которого соединенна с шиной кода дробной части коэффициент реления.

25 2. Делитель частоты по п.1, о т - личающийся тем, что блок квантованной задержки содержит регу- лируемьй резистор, набор конденсаторов, величины емкостей котьрых уста30 новлены по двоичному закону, набор ключей и логический элемент, при ,это первьй вьгаод регулируемого резистора соединен с тактовым входом блока квантованной задержки, второй и тре35 тий вьшоды регулируемого резистора подключены к первым вьшодам конденса торов и входу логического элемента, выход которого соединен с выходом блока квантованной задержки, вторые

Формула изобрете

н и я

о

1. Делитель частоты с управляемым коэффициентом деления, содержащий блок постоянной памяти, выход которого соединен с первым входом сумматора, второй вход которого соединен с . выходом регистра, вход которого соединен с выходом сумматора, делитель

70

частоты, управляющие входы которого соединены с шиной кода целой части коэффициента деления, входную и выходную шины, отличающийся тем, что, с целью повышения быстродействия и надежности, в него введены шина кода -дробной части коэффициента деления и блок квантованной задержки.

вькодами регистра, тактовый вход ко- Topforo соединен с ТАКТОВЫМ входом блока квантованной задержки и с выходом делителя частоты, суммирующий вход которого соединен с входной щи- ной, вычитающий вход - с выходом переноса сумматора, управляющие входы - с первой группой адресных входов блока постоянной памяти, вторая группа адресных входов которого соединенна с шиной кода дробной части коэффициента реления.

2. Делитель частоты по п.1, о т - личающийся тем, что блок квантованной задержки содержит регу- лируемьй резистор, набор конденсаторов, величины емкостей котьрых установлены по двоичному закону, набор ключей и логический элемент, при ,этом первьй вьгаод регулируемого резистора соединен с тактовым входом блока квантованной задержки, второй и третий вьшоды регулируемого резистора подключены к первым вьшодам конденсаторов и входу логического элемента, выход которого соединен с выходом блока квантованной задержки, вторые

вьгеоды конденсаторов подключены к входам соответствующих ключей, выходы которых подключены к общей шине, а управлякш1ие входы ключей являются управляющими входами блока квантованной задержки.

Редактор И.Касарда

Составитель А.Соколов

Техред В.Кадар Корректор М.Шароши

Заказ 3980/57 Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная,

фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Делитель частоты импульсов с переменным коэффициентом деления | 1980 |

|

SU940315A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1992 |

|

RU2041563C1 |

| Делитель частоты следования импульсов с дробным коэффициентом деления | 1978 |

|

SU771877A1 |

| Способ цифрового фазового детектирования импульсных последовательностей на неравных частотах и устройство для его осуществления | 1979 |

|

SU879738A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1064421A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Делитель частоты следования импульсов | 1989 |

|

SU1709514A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Цифровой накопитель с дробной переменной емкостью | 1987 |

|

SU1481756A1 |

Изобретение относится к опто- электронике и может найти применение для юстировки лазеров в видимой и ближней инфракрасной областях спектра. Цель изобретения - увеличение Чувствительности и разрешающей способности катодолюминесцентного преобразователя. На пластине 1 нанесен прозрачньм электрод 4 на основе SnO или , на котором размещен фото- проводящий слой 5 на основе соединений или , С последним контактируют сквозные металлические, например алюминиевые проводники 6 непрозрачной стеклянной пластины 7. Перед катодолюминесцентным слоем 8 расположен электрод 9 в виде плоской сетки и излучатель. Введение пластины 7 с проводниками 6 позволяет осуществить раздельное изготовление катодо- люминесцентного и фотопроводящего слоев 8 и 5. 2 ил. § (Л &д CAD 4: 00 | фиг. J

| Устройство для деления частоты импульсов с дробным коэффициентом деления | 1978 |

|

SU744990A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой синтезатор прямого действия | 1979 |

|

SU834873A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1064477A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-08-30—Публикация

1986-04-03—Подача