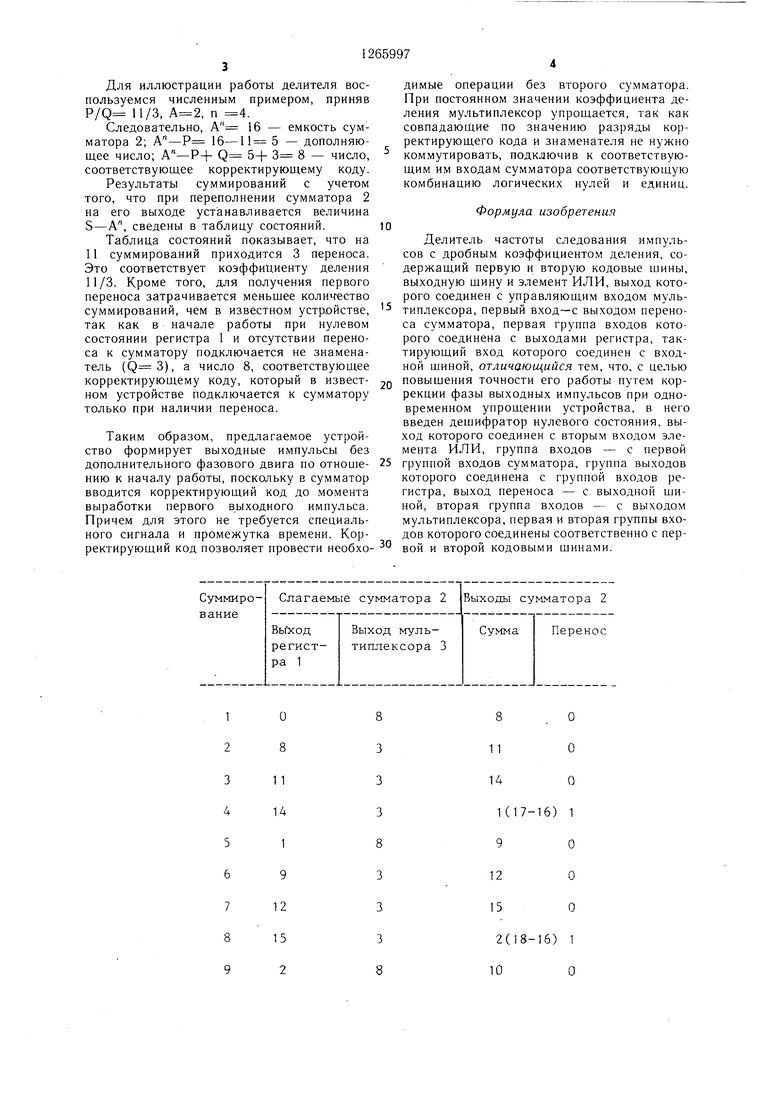

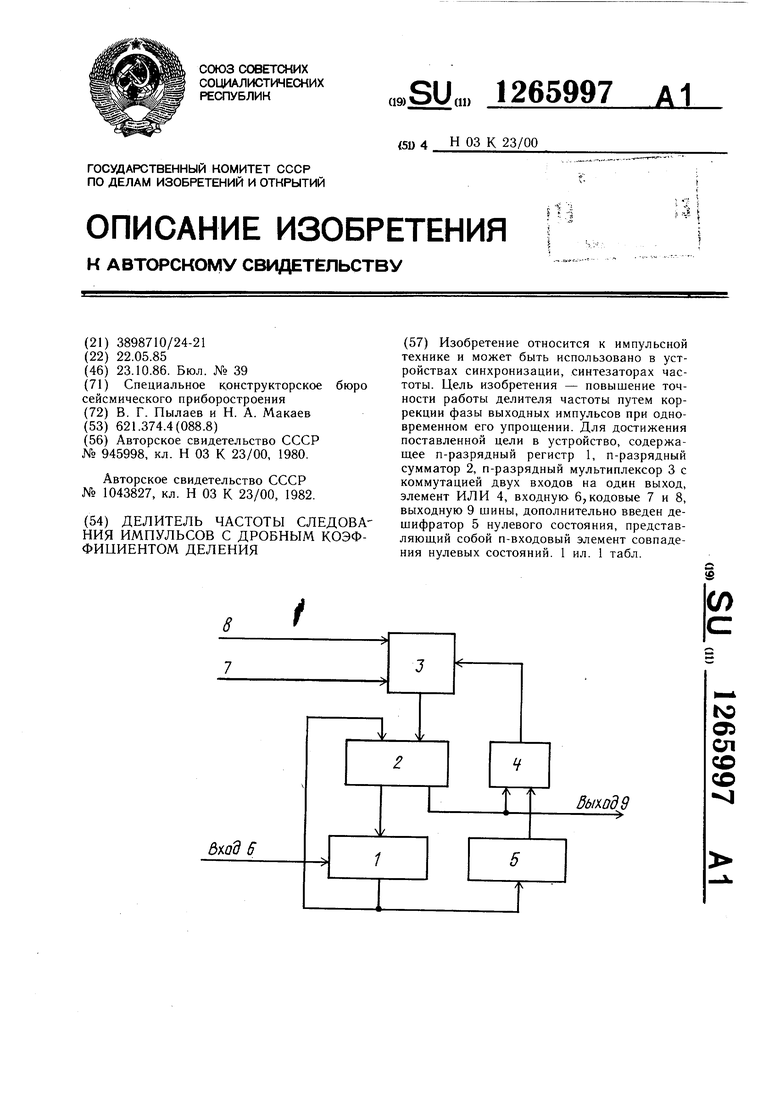

Изобретение относится к импульсной технике и может быть использовано в устройствах синхронизации, синтезаторах частот. Целью изобретения является повышение точности работы делителя частоты следования импульсов с дробным коэффициентом деления путем коррекции фазы выходных импульсов при одновременном его упрощении. На чертеже представлена электрическая структурная схема устройства. Устройство содержит п-разрядный реристр 1, п-разрядный сумматор 2, п-разрязный мультиплексор 3 с коммутацией двух входов на один выход, элемент ИЛИ 4, дешифратор 5 нулевого состояния, представляющий собой п-входовый элемент совпадения нулевых состояний, группа выходов регистра 1 соединена с первой группой входов сумматора 2 и с группой входов дешифратора 5, выход которого соединен с вторым входом элемента 4 ИЛИ; группа выходов сумматора 2 соединена с группой входов регистра 1, выход переноса сумматора 2 соединен с первым входом элемента ИЛИ 4, выход которого соединен с управляющим входом мультиплексора 3, группа выходов которого соединена с второй группой входов сумматора 2, тактирующий вход регистра 1 соединен с входной шиной 6 устройства; первая группа входов мультиплексора 3 соединена с первой кодовой шиной 7 (ввода знаменателя); вторая группа входов мультиплексора 3 соединена с второй кодовой шиной 8 (ввода корректирующего кода); выход переноса сумматора 2 соединен с выходной ншной 9 устройства. Делитель частоты следования импульсов с дробным коэффициентом деления работает следующим образом. Дробный коэффициент деления с числителем Р и знаменателем Q реализуется многократным суммированием числа Q при помощи сумматора 2 накапливающего типа с емкостью, совпадающей с величиной Р. При этом каждое из суммирований осуществляется по соответствующему импульсу входной последовательности с шины 6, а выходными являются импульсы переполнения, каждый из которых возникает на выходе переноса сумматора 2 при превышении накапливаемой суммой S величины Р. После Р суммирований числа Q должна накопиться сумма, по величине равная P-Q. По так как эта величина больше емкости сумматора 2, то она не зафиксируется в нем, а выработается P-Q/P Q импульсов переполнения. Это и соответствует коэффициенту деления P/Q, поскольку Р входным импульсам соответствует Q выходных. В общем случае величина числителя Р пе равна емкости сумматора А, где А - основание системы счисления: п - количество разрядов. Тогда коэффициент, деления P/Q соблюдается лишь в том случае, если после каждого переполнения сумматора в него вводить число , дополняющее числитель Р до емкости А . Входная последовательность импульсов поступает на тактирующий вход регистра 1, устанавливаемого перед началом работы в нулевое состояние, например, стандартным сигналом общего сброса устройства, в котором используется предлагаемое устройство. Пулевое состояние регистра 1 возбуждает выход дешифратора 5, который воздействует через элемент 4 на управляющий вход мультиплексора 3 и при помощи него подключает шину 8 (ввода корректирующего кода) к второй группе входов сумматора 2. Корректирующий код представляет собой сумму чисел и Q задается на входе мультиплексора 3, как и знаменатель Q коэффициента деления, соответствующей комбинацией логических пулей и единиц. „ По первому входному импульсу корректирующий код через сумматор 2 записывается в регистр 1. В результате в нем фиксируется первая сумма, включающая в себя знаменатель Q и число А -Р, которое уже в начале работы делает емкость накапливающего сумматора, равной числителю Р, не требуя на это ни специально отведенного момента времени, ни специальной операции. Поскольку после первого суммирования состояние .регистра 1 становится ненулевым, то прекращается воздействие дешифратора 5 на управляющий вход мультиплексора 3 и к входу сумматора 2 подключается шина 7 (ввода знаменателя Q). В дальнейшем по каждому входному импульсу сумма возрастает на величину Q, так как на первую группу входов сумматора 2 воздействует выходной код регистра 1, а на вторую - код знаменателя Q. Если после -очередного суммирования сумма S знаменателя Q и выходного кода регистра 1 превысит величину А, то на выходах сумматора 2 формируются остаток S- А и сигнал переноса, который подается через элемент 4 на управляющий вход мультиплексора 3, и вновь при помощи него шина 8 подключается к входу сумматора 2. При этом сигнал переноса сохраняется, а на выходе сумматора 2 формируется сумма следующих величину: остатка S-А, числа , знаменателя Q. Эта сумма записывается в регистр 1 по следующему входному импульсу. Тогда сигнал переноса исчезает, в результате чего к входу сумматора 2 через мультиплексор 3 подключается шина ввода знаменателя Q и по мере поступления входных импульсов устройство нродолжает работать по описанному алгоритму, в соответствии с которым на каждые Р входных импульсов вырабатывается Q выходных импульсов. Для иллюстрации работы делителя воспользуемся численным примером, приняв P/Q 11/3, , п 4. Следовательно, А 16 - емкость сумматора 2; 16-11 5 - дополняющее число; Q 5+ 3 8 - число, соответствующее корректирующему коду. Результаты суммирований с учетом того, что при переполнении сумматора 2 па его выходе устанавливается величина S-А, сведены в таблицу состояний. Таблица состояний показывает, что на 11 суммирований приходится 3 переноса. Это соответствует коэффициенту деления 11/3. Кроме того, для получения первого переноса затрачивается меньщее количество суммирований, чем в известном устройстве, так как в начале работы при нулевом состоянии регистра 1 и отсутствии переноса к сумматору подключается не знаменатель (), а число 8, соответствующее корректирующему коду, который в известном устройстве подключается к сумматору только при наличии переноса. Таким образом, предлагаемое устройство формирует выходные импульсы без дополнительного фазового двига по отнощению к началу работы, поскольку в сумматор вводится корректирующий код до момента выработки первого выходного импульса. Причем для этого не требуется специального сигнала и промежутка времени. Корректирующий код позволяет провести необходимые операции без второго сумматора. При постоянном значении коэффициента деления мультиплексор упрощается, так как совпадающие по значению разряды корректирующего кода и знаменателя не нужно коммутировать, подключив к соответствующим им входам сумматора соответствующую комбинацию логических нулей и единиц. Формула изобретения Делитель частоты следования импульсов с дробным коэффициентом деления, содержащий первую и вторую кодовые щины, выходную щину и элемент ИЛИ, выход которого соединен с управляющим входом мультиплексора, первый вход-с выходом переноса сумматора, первая группа входов которого соединена с выходами регистра, тактирующий вход которого соединен с входной шиной, отличающийся тем, что, с целью повыщения точности его работы путем коррекции фазы выходных импульсов при одновременном упрощении устройства, в него введен дешифратор нулевого состояния, выход которого соединен с вторым входом элемента ИЛИ, группа входов - с первой группой входов сумматора, группа выходов которого соединена с группой входов регистра, выход переноса - с выходной щиной, вторая группа входов - с выходом мультиплексора, первая и вторая группы входов которого соединены соответственно с первой и второй кодовыми щинами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов с управляемым дробным коэффициентом деления | 1982 |

|

SU1043827A1 |

| Дробный делитель частоты следования импульсов | 1981 |

|

SU993480A1 |

| СИНТЕЗАТОР ЧАСТОТЫ ДЛЯ СОЗДАНИЯ СИНТЕЗИРОВАННОЙ ВЫХОДНОЙ ЧАСТОТЫ | 1989 |

|

RU2085031C1 |

| Программируемый делитель частоты следования импульсов | 1980 |

|

SU945998A1 |

| Устройство для измерения частоты повторения импульсов | 1977 |

|

SU660266A1 |

| Делитель частоты с управляемым коэффициентом деления | 1986 |

|

SU1334370A1 |

| Устройство для умножения | 1986 |

|

SU1425658A1 |

| Управляемый делитель частоты с дробным коэффициентом деления | 1981 |

|

SU1003352A1 |

| Устройство для деления чисел | 1981 |

|

SU1013948A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1997 |

|

RU2137287C1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах синхронизации, синтезаторах частоты. Цель изобретения - повышение точности работы делителя частоты путем коррекции фазы выходных импульсов при одновременном его упрощении. Для достижения поставленной цели в устройство, содержащее п-разрядный регистр 1, п-разрядный сумматор 2, п-разрядный мультиплексор 3 с коммутацией двух входов на один выход, элемент ИЛИ 4, входную 6, кодовые 7 и 8, выходную 9 шины, дополнительно введен дещифратор 5 нулевого состояния, представляющий собой п-входовый элемент совпадения нулевых состояний. 1 ил. 1 табл. бш одд

.О

О

О 16)1

О

О

О 16)1

О

1010

1113

Продолжение таблицы

13О

3 3 8

О1

8О

| Программируемый делитель частоты следования импульсов | 1980 |

|

SU945998A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты следования импульсов с управляемым дробным коэффициентом деления | 1982 |

|

SU1043827A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-10-23—Публикация

1985-05-22—Подача