Изобретение относится к импульсвой технике и может быть применено в частотнопреобразукидих узлах аппар туры времени и этсшонных частот, электронных часов, измерительных пр боров/ в устройствах синхронизации систем передачи данных, в синтезирую щих блоках аппаратуры связи ; Известен делитель частоты с дроб ным коэффициентом деления, который содержит генератор сигналов, счетчик, регистр счетчик-делитель на М, вентилИ) счетчик делитель на N, синхронизатор и два дополнительных делителя 11. Недостатком известного делителя частоты с дробным коэффициентом деления является его сложность. Известен также делитель частоты с дробным коэффициентом деления, содержащий делитель частоты с управляемым коэффициентом деления, один вход которого соединен с шиной эталонной частоты, второй вход - с первой шиной управления, третий вход с первым выходом блока сравнения кодов, входы которого соединены с выходами двух cyMi-iaTopoB, первые входы KOToptix подклинены ко второй и третьей шине управления, второй вход одного сумматора соединен с выходом BTOpoio сумматора, а выход делителя частоты с управляемым коэффициентом деления через управлкемыЛ элемент задержки соединен с выходной шиной 2. Недостатком известного делителя частоты с дробным коэффициентом деления является узкий диапазон установки коэффициентов деления. Целью изобретения является расширение диапазона установки коэффициентов деления делителя частоты с дробным коэффициентом деления. Это достигается тем, что в делитель частоты с дробным коэффициентом деления введены блок памяти, первый и второй входы которого соединены с выходами сумматоров, два вентиля, умножитель и делитель чисел, входы которого соединены с третьей и четвертой шинами управ- . ляющих сигналов а выход соединен с первым входом умножителя чисел, второй вход которого соединен с выходом управляемого элемента задержки и первыми входами вентилей, вторые ВХОД1Ы которых соединены с выходами .

блока сравнения кодов, а выходы вентилей подключены к третьему и четвертому входам блока памяти, выход которого соединен с третьим входом умножителя чисел, с выходом которого соединен вход управления управляемого элемента задержки.

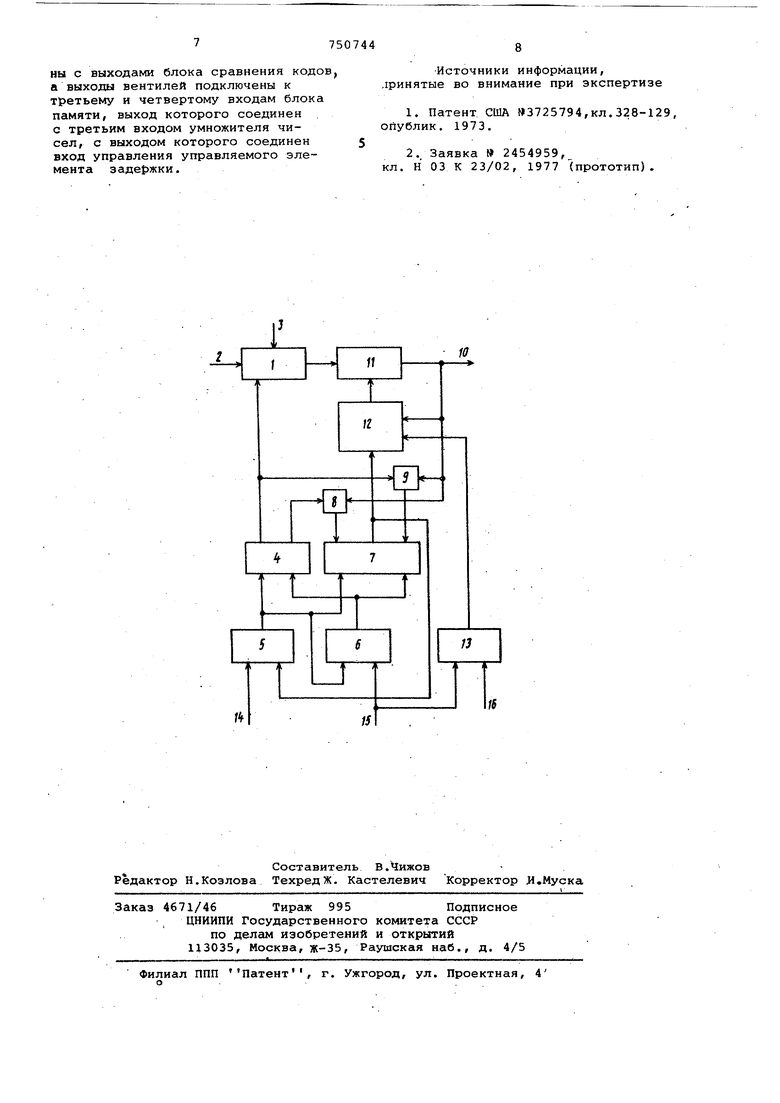

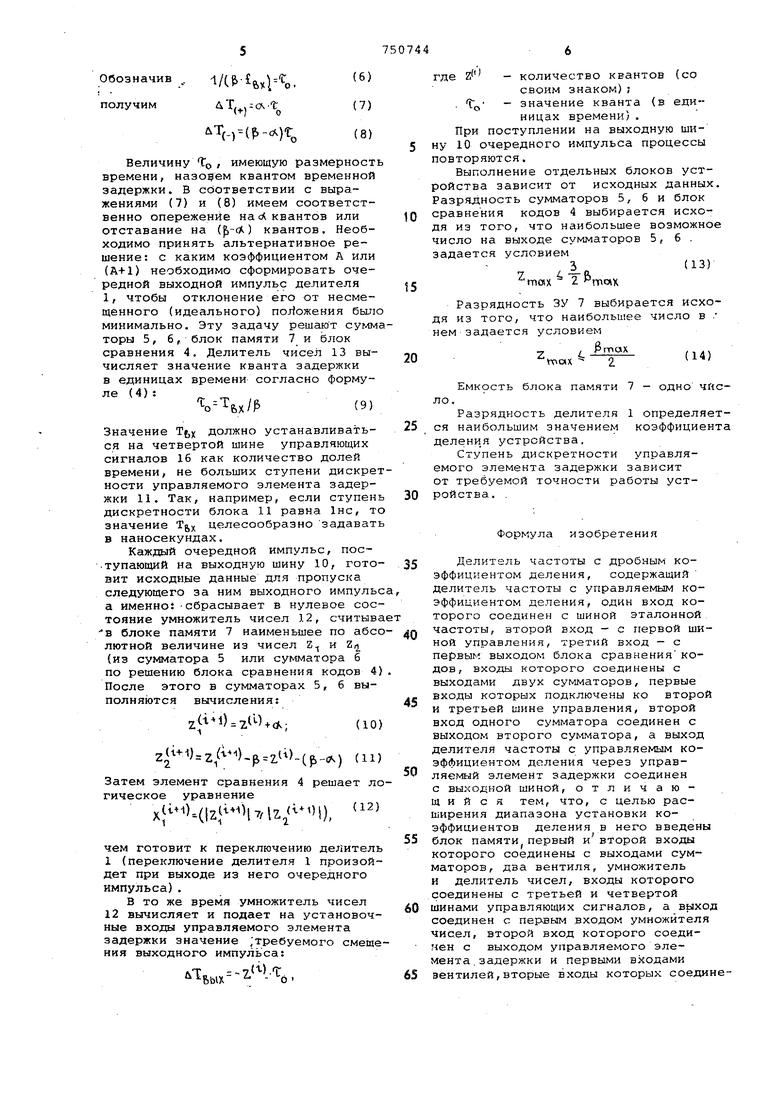

Структурная электрическая схема делителя частоты с дробным коэффициентом деления приведена на чертеже.

На чертеже приняты следующие обозначения: 1 - делитель частоты с управляемым коэффициентом деления; 2 - шина эталонной частоты; 3 - первая шина управления;, 4 - блок сравнения кодов; 5 и 6 сумматоры; 7 - блок памяти; 8, 9 вентили; 10 - выходная шина; 11- управляемый элемент задержки; 12 - умножитель чисел; 13 - делитель чисе 14 - вторая шина управления; 15 - третья шина управляющих сигналов; 16 - четвертая шина управляющих сигналов ,

Делитель частоты с переменным коэффициентом деления работает следующим образом.

Делитель частоты 1 с управляемым коэффициентом частоты соединен с шиной 2 эталонной частоты, с первой шиной управления 3, кроме того, он . имеет управляющий вход для переключения коэффициента деления на единицу, соединенный с первым выходом блока сравнения кодов 4, первый и второй входы которого соединены с .выходами соответственно сумматора 5 и сумматора б,

Выход сумматора 5 соединен с первым входом сумматора 6 и первым информационным входом блока памяти второй информационный вход которого связан с выходом сумматора ,6,Первый и второй входы занесения чисел в блок памяти 7 служат для разрешения записи в блок памяти 7 кодов соотве ственно по -первому и второму информационному входам«Первый и второй входы занесения блока памяти 7 связны соответственно с выходом вентиля и вентиля ,9 .Первые одноименные вход вентилей 8 и 9 связаны соответствен со вторым и первым выходами блока сравнения кодов 4, а вторые одноименные входы - с выходной шиной 10 и выхбдом управляемого элемента задержки 11, установочные входы , которого связаны с выходом умножителя 12 чисел. Умножитель 12 подключен входом одного сомножителя к выходу блока памяти 7, входом второго сомножителя - к выходу делителя 13 чисел, входом установки нуля к выходной шине 10, Первый и второй входы сумматора 5 связаны соответственно со второй шиной управления 14 и информационным выходом блока памяти 7. Первд1й и второй входы сумматора 6 связаны соответственно с выходом сумматора Бис третьей шиной управляющих сигналов 15 подачи знаменателя дробной части коэффициента деления. Делитель чисел 13 соединен входом делимого с четвертой шиной управляющих сигналов 16, а входом делителя - со вторым входом сумматора 6,

В сумматоре 5 со второй шины управления 14 числа воспринимсцотся как

положительные, а с третьей шины управляющих сигналов 15 в сумматоре 6 как отрицательные, В блоке памяти 7 с сумматоров 5, 6, в сумматоре 5 с блока памяти- 7, в сумматоре 6 с су,м5 матора 5 числа воспринимаются со своими знаками. Из блока памяти 7 в умножитель чисел 12 числа выдаются со своим знаком, но при выдаче результата на управляемый элемент

0 задержки 11 знак инвертируется. Блок сравнения 4 решает логические уравнения

u2.,,l} (1)

5 ...), (2)

где Х,Х2 - логические переменные

( 1 или ) соответственно на первом и втором выходах элемента 0 . сравнения 4;

2,2 - числа, принятые соответственно из суммато-. ров 5 и б,

Если Х 1, то делитель частоты 1 очередной раз срабатывает с коэффициентом деления (А + 1), а если , то коэффициент деления устанавливается равным А, где А - целая часть коэффициента деления. Соответственно очередной выходной импульс делителя 1 сдвигается по времени в сторону отставания или опережения, так как

/ bx /fbxMA D/fbx

ьх

где , - дробный коэффициент

деления;

о, - числитель и знаменатель его дробной части; - частота импульсов на

входе устройства.

Если первое срабатывание произоло с коэффициентом деления А, fo выходной импульс сдвигается Б сторону опережения на величину

д JL А Л

(4)

йТ, X - . - 7Г

-ьх

-ЬУ i« Если первое срабатывание произошло с коэффициентом деления (А+1), то выходной импульс сдвигается в сторону отставания на ве„ AM К . -Л ..

личину 41 ,.

ЬЛУ Л р tgx

М

ЬХ Обозначив ,. l/C -ffty fo, получим А Т,.,-ел-г () о ЛТ(,-()Г Величину tp, имеющую размерност времени, назовем квантом временной задержки. В соответствии с выражениями (7) и (8) имеем соответственно опережение на Л квантов или отставание на (f,-) квантов. Необходимо принять альтернативное решение: с каким коэффициентом А или (A+l) необходимо сформировать очередной выходной импульс делителя 1, чтобы отклонение его от несмещенного (идеального) по11ожекия был минимально. Эту задачу решают сумм торы 5, 6, блок памяти 7 и блок сравнения 4, Делитель чисел 13 вычисляет значение кванта задержки в единицах времени согласно формуле (4): (9) Значение должно устанавливаться на четвертой шине управляющих сигналов 16 как количество долей времени, не больших ступени дискре ности управляемого элемента задержки 11. Так, например, если ступен дискретности блока 11 равна 1нс, т значение Tj,) целесообразно задават в наносекундах. Каждый очередной импульс, поступающий на выходную шину 10, гото вит исходные данные для пропуска следующего за ним выходного импуль а именное -сбрасывает в нулевое сос тояние умножитель чисел 12, считыв в блоке памяти 7 наименьшее по абс лютной величине из чисел Z и Z (из сумматора 5 или сумматора 6 по решению блока сравнения кодов 4 После этого в сумматорах 5, б выполняются вычисления: 2(tM) ;iCl),.(10 )Z/)-p.zU)-(-) (11 Затем элемент сравнения 4 решает л элемент сравнения 4 реш гическое уравнение ое уравнение ).,2(W)j 7,1x)1) чем готовит к переключению делитель 1 (переключение делителя 1 произойдет при выходе из него очередного импульса). в то же время умножитель чисел 12 вычисляет и подает на установочные входы управляемого элемента задержки значение ;требуемого смеще ния выходного импульса: -J 7(г).гг ,ых - о где - количество квантов (со своим знаком); . tp - значение кванта (в единицах времени). При поступлении на выходную шину 10 очередного импульса процессы повторяются. Выполнение отдельных блоков устройства зависит от исходных данных. Разрядность сумматоров 5, б и блок сравнения кодов 4 выбирается исходя из того, что наибольшее возможное число на выходе сумматоров 5, 6 . задается условием (13) тах 2 mwx Разрядность ЗУ 7 выбирается исходя из того, что наибольшее число в . нем задается условием n.m Емкость блока памяти 7 - одно число. Разрядность делителя 1 определяется наибольшим значением коэффициента делени я устройства. Ступень дискретности управляемого элемента задержки зависит от требуемой точности работы устройства. . Формула изобретения Делитель частоты с дробным коэффициентом деления, содержащий делитель частоты с управляемым коэффициентом деления, один вход которого соединен с шиной эталонной частоты, второй вход - с первой шиной управления, третий вход - с первым выходом блока сравнениякодов, входы которого соединены с выходами двух сумматоров, первые входы которых подключены ко второй и третьей шине управления, второй вход одного сумматора соединен с выходом второго сумматора, а выход делителя частоты с управляемым коэффициентом деления через управляемый элемент задержки соединен с выходной шиной, отличающийся тем, что, с целью расширения диапазона установки коэффициентов деления в него введены блок памяти первый и второй входы которого соединены с выходами сумматоров, два вентиля, умножитель и делитель чисел, входы которого соединены с третьей и четвертой инами управляющих сигналов, а выход соединен с первым входом умножителя исел, второй вход которого соедиен с выходом управляемого элеента . задержки и Первыми входами вентилей,вторые входы которых соедине75ны с выходами блока сравнения кодов, а выходы вентилей подключены к третьему и четвертому входам блока памяти, выход которого соединен . с третьим входом умножителя чисел, с выходом которого соединен вход управления управляемого элемента задержки. 8 Источники информации, лринятые во внимание при экспертизе 1. Патент США 1 3725794,кл. 328-129 , опублик. 1973. 2.. Заявка 2454959, кл. Н 03 К 23/02, 1977 (прототип)..

| название | год | авторы | номер документа |

|---|---|---|---|

| Дробный делитель частоты следования импульсов | 1981 |

|

SU993480A1 |

| Делитель частоты следования импульсов с дробным коэффициентом деления | 1981 |

|

SU984056A1 |

| Делитель частоты следования импульсов с дробным коэффициентом деления | 1978 |

|

SU771877A1 |

| Умножитель частоты с переменным коэффициентом умножения | 1977 |

|

SU743180A1 |

| Цифровой умножитель частоты | 1980 |

|

SU930575A2 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1037420A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| Делитель частоты с дробным коэффициентом деления | 1986 |

|

SU1347184A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU949789A1 |

lit

10

16

Авторы

Даты

1980-07-23—Публикация

1978-01-18—Подача