С 5) ПРОГРАММИРУЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ

ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый делитель частоты с дробным коэффициентом деления | 1981 |

|

SU1003352A1 |

| Делитель частоты следования импульсов с дробным коэффициентом деления | 1985 |

|

SU1265997A1 |

| Делитель частоты следования импульсов с управляемым дробным коэффициентом деления | 1982 |

|

SU1043827A1 |

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1981 |

|

SU951713A1 |

| Корреляционный измеритель фазовых соотношений узкополосных случайных процессов | 1990 |

|

SU1714616A1 |

| Делитель частоты | 1980 |

|

SU940314A1 |

| Делитель частоты с дробным переменным коэффициентом деления | 1983 |

|

SU1156252A1 |

| Делитель частоты следования импульсов с дробным коэффициентом деления | 1978 |

|

SU771877A1 |

| Делитель частоты с управляемым коэффициентом деления | 1986 |

|

SU1334370A1 |

| Дробный делитель частоты следования импульсов | 1981 |

|

SU993480A1 |

1

Изобретение относится к импульсной технике и может быть использовано в цифровых синтезаторах частоты, устройствах синхронизации, цифро-частотных устройствах вычислительной техники.

Известен делитель частоты следования импульсов,содержащий элементы совпадения, декадные счетчики, дополнительные декады с переменнь1м коЭ(1)(5ициёнтом деления, элементы ИЛИ, триггеры памяти и делитель частоты 1.

Недостаток известного устройства - ограниченные функциональные возможности из-за того, что данное устройство позволяет получать коэффициенты деления только в виде десятичных дробей.

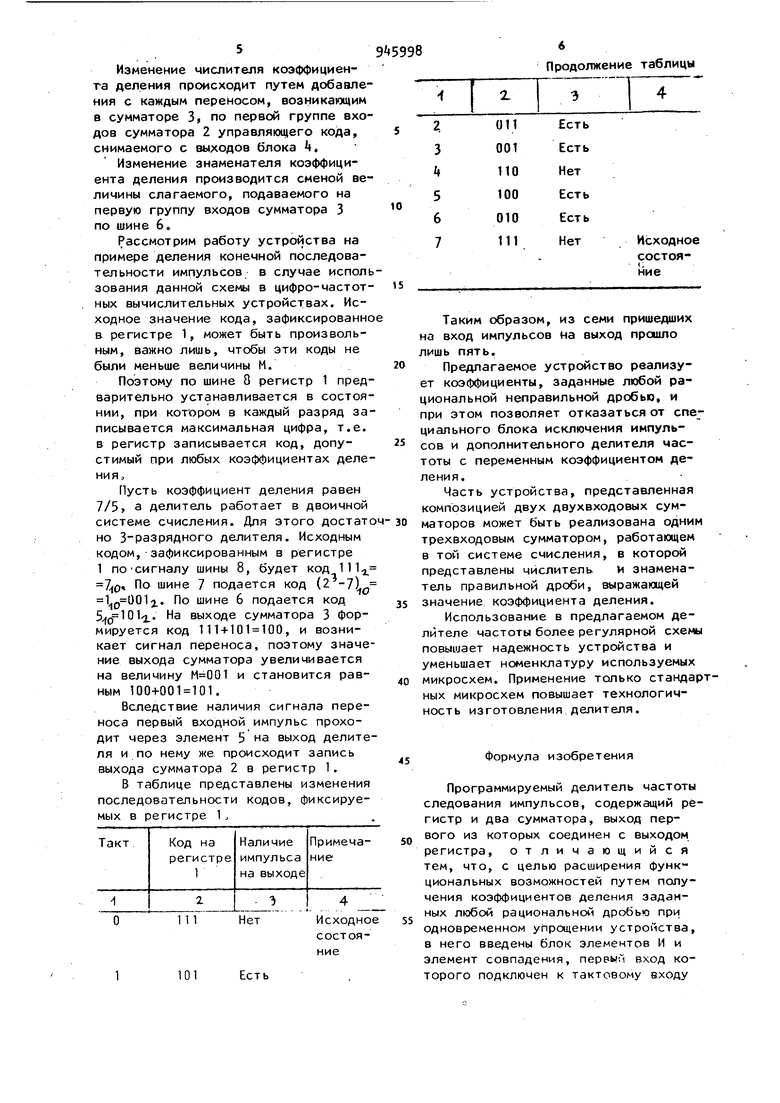

Наиболее близким по технической сущности к изобретению является делитель частоты с дробным переменным коэ(;х})ициентом деления, позволящий получать программу равномерно распределенного исключения импульсов для формирования дробных десятичных разрядов коэффициента деления делителя и содержащий делитель частоты с переменным коэффициентом деления, блок исключения импульсов, регистры и сумматоры, причем первые входы делителя частоты с переменным коэффициентом деления и блока исключения импульсов объединены и подключены к входной шине, второй вход делителя частоты с переменным коэффициентом деления соединен с выходом блока исключения импульсов, первый выход - со вторым входом блока исключения импульсов, а выход с тактовыми входами регистров, входы которых подключены к выходам- сумматоров cooтвeтcтвyюu иx разрядов, а выходы - к первым входам сумматоров соответствующих разрядов, вторые входы которых и третий вход делителя частоты с переменным коэффициентом деления подключены к шине ввода 39 управлящего кода, причем выход пере носа сумматора старшего разряда соединен с управляющими входами блока исключения импульсов, а выход переноса - с выходом переноса сумматора последующего младшего разряда 2д. Недостаток известного устройства заключается в том, что оно не позволяет получать коэффициенты, заданные произврльными рациональными дробями, причем невозможна реализация в виде конечной схемы кодффициентов деления, выражаемых бесконечной десятичной дробью. Кроме того, схема сложна по построению, так как кроме регистров и сумматоров содержит специальный блок исключения импульсов и дополнительный делитель частоты с переменным коэффициентом деления. Цель изобретения - расширение фун циональных возможностей путем получе ния коэффициентов деления, заданных любой рациональной дробью при одновременном упрощении устройства. С этой целью в программируемый де литель частоты следования импульсов содержащий регистр и два сумматора, выход первого из которых соединен с входом регистра, введены блок эле,, ментов И и элемент совпадения, первы вход которого подключен к тактовому входу регистра и к входной шине, а второй вход - к выходу переноса втор го сумматора и первой группе входов блока элементов И, вторая группа входов которого подключена к шине вв да управляющего кода, а выходы - к первой группе входов первого сумматора, вторая группа входов которого соединена с выходом второго сумматор первая группа входов которого соединена с шиной ввода кода знаменателя а вторая группа входов - с выходом р гистра, установочный вход которого соединен с установочной шиной. На чертеже представлена структурfidfl схема устройства Устройство содержит регистр 1, И-разрядные сумматоры 2 и 3, блок элементов И, количество которых соответствует числу разрядов сумматора, элемент 5 совпадения. Цифрами 6-8 обозначены соответственно шины ввода кода знаменателя, ввода управляющего кода и установочная. Деление частоты следования импульсов в предлагаемом устройстве происходит следующим образом , Коэффициент деления, заданный дробью P/Q, где Р, Q - целые числа, означает, что из пришедших на вход устройства Р импульсов на выход должны пройти только Q из них. Это реализуется в накопителе чисел, работающем по модулю Р, В качестве слагаемого с каждым импульсом на один из входов накопителя по входной шине подается число, равное Q, а на другой вход - код управления, стробируемый сигналом переноса, возникающим в случае превышения над модулем Р, Если на вход пришло L импульсов, количество импульсов на выходе определяется как р-ГОЬ . Тогда в накопителе будет остаток Ql.- p--QL(Hiodp; В частности, если на вход приходят Р импульсов, на выходе будет Q импульсов. В предлагаемом устройстве накопитель реализован как сумматор накапливаюи(его типа, работающий по модулю, определяемому числителем коэффициента деления путем прибавления с каждым переносом, возникающим в сумматоре 3 управляющего кода (1 по шине 7 , причем где Р - числитель коэффициента деления;И - разрядность сумматоров и регистра; А -основание используемой системы счисления, в которой работает используемый сумматор. Если при отсутствии данного слагаемого М сумматор 3 работал бы по модулю А, то при наличии в качестве слагаемого управляющего кода М (1), он работает по модулю Р, причем все остатки по модулю фиксируются в регистре 1 со смеи1ением на величину М, Каждое превышение над модулем передается на выход делителя в виде импульса, появляющегося на элементе 5. 5 Изменение числителя коэффициента деления происходит путем добавле ния с каждым переносом, возникающим в сумматоре 3, по первой группе вхо дов сумматора 2 управляющего кода, снимаемого с выходов блока k. Изменение знаменателя коэффициента деления производится сменой величины слагаемого, подаваемого на первую группу входов сумматора 3 по шине 6, Рассмотрим работу устройства на примере деления конечной последовательности импульсов в случае испол зования данной схемы в цифро-частотных вычислительных устройствах. Исходное значение кода, зафиксированно в регистре 1, может быть произвольным, важно лишь, чтобы эти коды не были меньше величины М. Поэтому по шине 8 регистр 1 предварительно устанавливается в состоянии, при котором в каждый разряд за писывается максимальная цифра, т.е. в регистр записывается код, допустимый при любых коэффициентах деления. Пусть коэффициент деления равен 7/5, а делитель работает в двоичной системе счисления. Для этого достато но 3-разрядного делителя. Исходным кодом, зафиксированным в регистре 1 поСигналу шины 8, будет код 111 7,0 По шине 7 подается код (2 -7) 1... По шине 6 подается код . На выходе сумматора 3 формируется код 111+101 100, и возникает сигнал переноса, поэтому значение выхода сумматора увеличивается на величину и становится равным 100+001 101. Вследствие наличия сигнала переноса первый входной импульс проходит через элемент 5 на выход делителя и по нему же происходит запись выхода сумматора 2 в регистр 1. В таблице представлены изменения последовательности кодов, фиксируемых в регистре 1 Исходное состояние8 Продолжение таблицы Таким образом, из семи пришедших на вход импульсов На выход прошло лишь пять. Предлагаемое устройство реализует коэффициенты, заданные любой рациональной неправильной дробью, и при этом позволяет отказаться от специального блока исключения импульсов и дополнительного делителя частоты с переменным коэффициентом деления. Часть устройства, представленная композицией двух двухвходовых сумматоров может быть реализована одним трехвходовым сумматором, работающем в той системе счисления, в которой представлены числитель и знаменатель правильной дроби, выражающей значение коэффициента деления. Использование в предлагаемом делителе частоты более регулярной схемы повышает надежность устройства и уменьшает номенклатуру используемых микросхем. Применение только стандартных микросхем повышает технологичность изготовления.делителя. Формула изобретения Программируемый делитель частоты следования импульсов, содержащий регистр и два сумматора, выход первого из которых соединен с выходом регистра, отличающийся тем, что, с целью расширения функциональных возможностей путем получения коэффициентов деления заданных любой рациональной дробью при одновременном упрощении устройства, в него введены блок элементов И и элемент совпадения, первмй вход которого подключен к тактовому входу регистра и к входной шине, а второй вход - к выходу переноса второго сум матора и первой группе входов блока элементов И, вторая группа входов которого подключена к шине ввода управляющего кода, а выходы - к первой группе входов первого сумматора, вто рая группа входов которого соединена с выходом второго сумматора, первая группа входов которого соединена с

88 шлнрй ввода кода знаменателя, а вто рая группа входов - с выходом регистра, установочный вход которого соединен с установочной шиной. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР V 506130, кл. Н 03 К 23/00, IS. 2.Авторское свидетельство СССР № 657615, кл. Н 03 К 23/00, 1976.

Авторы

Даты

1982-07-23—Публикация

1980-12-02—Подача