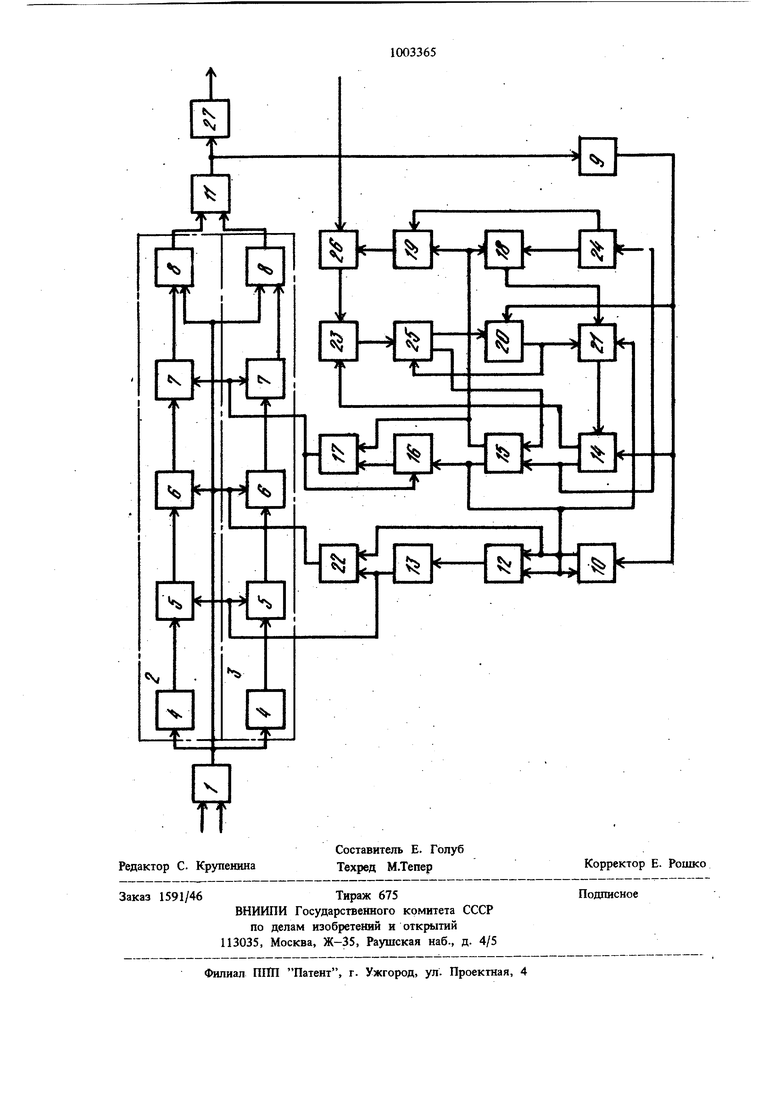

Изобретение относится к технике передачи /даиных по каналам связи и может использоваться в -устройствах преобразования сигналов с частотной модуляцией. Известно устройство для контроля качества частотно-модулированных сигналов с саморегулируемыми пороговыми величинами, содержащее первый усилитель, выход которого сое динен с входами двух каналов обработки сигналов, каждый из которых состоит из последовательно соединенных ограничителя, первого накопителя сигнала, первого переключателя, второго накопителя сигнала и компаратора, вторые входы и выходы которых соеди нены соответственно с выходом первого усили теля и входами первого элемента ИЛИ, выход которого соединен с входом второго уси лителя и входом формирователя импульсов индикации помех, выход которого соединен с первыми входами цифро-аналогового преобразователя, счетчика числа индикации помех и второго переключателя, второй вход и выход которого соединен с первыми входами второго и третьего элементов ИЛИ и вторым входом второго элемента ИЛИ, выход которого соединен с входом блока управления, выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом второго переключателя, и с вторыми входами первых накопителей сигнала, причем выход цифроаналогового преобразователя через трютий элемент ИЛИ соединен с вторым входом счетчика числа индикации помех 1 . Однако известное устройство имеет низкую точность контроля. Цель изобретения - повышение точности контроля., Указанная цель достигается тем, что в устройство для контроля качества частотномодулированных сигналов с саморегулируемыми пороговыми величинами введены первый и второй блоки сравнения, двоичный счетчик, первый и второй регистры, пятый элемент ИЛИ, три элемента И, при этом первый и второй выходы счетчика числа индикаютй помех соединены соответственно с первыми входами первого и второго блоков сравнения и первым входом пятого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом второго регистра и первым входом первого регистра, второй вход и выходы которого соединены соответственно с выходом цифроаналогового преобразователя, с вторым входом цифроаналогового преобразователя и вторым входом первого блока сравне.шя, первый и второй выходы которого соединены а ответственно с вторым входом второго переключателя и объединенными первыми входами первого, второго и третьего элементов И, выход и второй вход которого соединены соответственно с входом второго регистра и первым выходом второго блока сравнения, второй, выход которого через второй элемент И соединен с третьим входом третьего э- емента ИЛИ, причем первый выход первого блока сравнения соединен с входом двоичного счетчика, второй вход и выход которого соединены соответственно с выходом и вторым входом первого элемента И, выход которого соединен с вторыми входами вторых накопителей сигнала. На чертеже представлена структурная электрическая схема предлагаемого устройства. Устройство содержит первый усилитель 1, два канала 2 и 3 обработки сигналов, каждый из которых состоит из ограничителя 4, первого накопителя 5 сигнала, первого переключателя 6, второго накопителя 7 сигнала и компаратора 8, формирователь 9 импульсов и дикации помех, второй переключатель 10, пер вый элемент ИЛИ 11, второй элемент ИЛИ 1 блок 13 управления, счетчик 14 числа индика ции помех, первый блок 15 сравнения, двоичный счетчик 16, первый, второй и третий элементы И 17-19 соответственно, цифроаналоговый преобразователь 20, третий, четвер тый и пятый элементы ИЛИ 21-23 соответственно, второй блок 24 сравнения, первый и второй регистры 25 и 26 соответственно, второй усилитель 27. Устройство работает следующим образом. Напряжения частотных дискриминаторов мо дема подаются на входы устройства и сумми руются, в первом усилителе 1, суммарное напряжение подается на входы ограничителя 4 обоих каналов 2 и 3, где делится на положи тельную и отрицательную части (последующие режимы работ будут описаны лишь для поло жительной части, так как часть для отрицательного порога совершенно идентична за исключением того, что должна быть учтена отри цательная полярность). Пиковое значение напряжения, появляющееся в определенный ийтервал времени, накапливается в первом нако пителе 5. Содержимое первого накопителя 5 подается во второй накопитель 7 через первы переключатель 6 как пороговое значение напряжения. После этой операции первый накопитель 5 освобождается. Решение о том, имеет ли место помеха (сомнительный сигнал) или нет, . принимается компаратором 8. На входы компаратора 8 подается пороговое значение напряжения из второго накопителя 7 и суммарное напряже1«1е из первого усилителя 1. Выходы компараторов 8 соединены с входом первого элемента ИЛИ И, сигнал на выходе которого, усиленный вторым усилителем 27, используется для индикации помех и выдачи сигналов о сомнительном элементе последовательности импульсов в устройство защиты от ошибок (УЗО), где осушествляется решение о приеме или стирании каждого блока (массива) данных. Для индикации помех неважно, какой порог оказывается повышенным. Для того, чтобы искажения значения суммарного напряжения не накапливались в качестве порогов, индикации помехи используются для удержания первых переключателей 6 в разомкнутом состоянии и для освобождения первых накопителей 5. Это достигается посредством схемы обратной связи, состояшей из формирователя 9, второго переключателя 10, блока 13 управления, второго и четвертого злемента ИЛИ 12 и 22. Формирователь 9 формирует импульсы определенной длительности (например, равной длине защищаемого массива данных). Индикации помех, появляющиеся в течение длительности этого импульса, не влияют, на формирователь 9, который предотвращает накопление искаженного значения напряжения во вторых накопителях 7 путем немедленного размыкания первых переключателей 6 через второй элемент ИЛИ 12 и освобождает первые накопители 5 сигнала путем синхронизации блока 13 .управления через четвертый элемент ИЛИ 22. При этом режиме работы второй переключатель 10 постоянно замкнут. Индикации помех из формирователя 9 поступают также на счетчик 14, а первый импульс последовательности индикаций помех одновременно подается на цифро-аналоговый преобразователь (ЦАП) 20, куда также подается из первого регистра 25 соответствующее число, которое в период начального включения устройства пересылается через пятый элемент ИЛИ 23 из второго регистра 26. На выходе ЦАП 20 формируется импульс, длительность которого пропорциональна величине среднего значения порога числа индикаций. В течение длительности этого импульса в счетчике 14 осуществляется накопление индикаций помех. По окончании этого импульса сигналом с выхода ЦАП 20 через третий элемент ИЛИ иакопленное число индикаций (Nf ) из счетчика 14 передается в первый блок 15 сравнения и второй блок 24 сравне ния, куда же считывается величина порога числа индикаций (N ) из первого регистра 2 Далее возможны следующие случаи работы в зависимости от соотношения N и Мр 6 двух следующих друг за другом периодах импульса на выходе ЦАП 20: а) I период N N II период Щ Nn В конце 1-го периода с первого выхода блока 15 сравнения выдается Корректирующий импульс, который размыкает второй переключатель 10, производит через второй злемент ИЛИ 12 перерегулировку на новые пороги блока 13 управления, освобождает счетчик 14 через третий злемент ИЛИ 21, пересылая число индикаций через, пятый злемент ИЛИ 23 в первьш регистр 25, и устанавливает в положение 1 двоичный счетчик 16. ff, В конце Н-го периода вся указанная выще процедура повторяется за исключением того, что двоичный счетчик остается в положении Корректирование пороговых величин произ водится так же, как описано выще, но при других параметрах выходных импульсов блока 13 управления. б) I период Nt Np . II период N Np В конце первого периода процедура выпол няется как и ранее при N . N,. В конце второго периода с второго выход первого блока 15 сравнения вьщается сигнал, йоступающий на второй вход первого элемент И 17, с выхода которого в зтом случае cmiM ется сигнал, коюрый освобождает вторые накопители 7 и переводит в состояние О дво ичный счетчик 16. Тот же сигнал с второго выхода первого блока сравнения подается на вторые входы соответствующих злементов И одновременно, если N О, с первого выход второго блока сравнения подается сигнал на второй вход второго элемента И 18, сигналом с выхода которого через третий злемент ИЛИ 21 считывает;ся из счетчика 14 текущее число индикаций, поступающее через пятый злемент ИЛИ 23 в первый регистр 25 Если же N О, то с второго вьгхода вто рого блока 24 сравнения поступает сигнал на второй вход третьего злемента И 19, с выхода которого среднее значение порога числа индикаций помех из второго регистра 26 через пятый злвмект ИЛИ 23 подается в первый регистр 25. в) 1 период Nt Nn II период Nf Np В конце t-ro и 11-го периодов процедура вьшолняется как и ранее при N Np за исключением того, что сигнал на выходе первого элемента И 17 не вырабатывается, вторые накопители 7 не освобождаются, и двоичный счетчик остается в состоянии О. г) I период Nt N период 14 ,,р В конце 1-го периода процедура выполняется как и ранее при N N, В конце II-го периода процедура выполняется как в пункте а) при N Np. Величина среднего значения порога числа индикаций помех определяется таким образом, чтобы пропорциональная ему длительность импульса, вырабатываемого цифроаналоговым преобразователем, была достаточно большой по отношению к максимально возможной длине пачек ошибок для данного типа каналов связи. Таким образом, введенные блоки обеспечивают как увеличение, так и уменьшение пороговых величин устройства, изменение порога числа индикаций помех и соответствующее изменение величины интервала времени, в течение кото{юго накапливаются индикации помех, в зависимости от уровня внешних помех и изменений, вызываемых системой связи (аппаратурой), что влечет за собой уменьшение частости ложных стираний и ложных приемов. Как показывает анализ, по отношению к известному устройству вьшгрыщ составляет 1,5-2 порядка, а по отношению к детектору с фиксированными порогами выигрыш составляет 0,5-1 порядок, в зависимости от длины блоков п, по которым принимается в УЗО решение о их приеме или стирании. Формула изобретения Устройство для контроля качества частотномодулированных сигналов с саморегулируемыми пороговыми величинами, содержащее первый усилитель, выход которого соединен с входами двух каналов обработки сигналов, Из которых состоит из последовательно соединенных ограничителе, первого накопителя сигнала, первого переключателя, второго накопителя сигнала и компаратора, вторые входы и выходы которых соединены соответственно с выходом первого усилителя и рходами первого элемента ИЛИ, выход которого соединен с входом второго усилителя и входом формирователя импульсов индикации помех, выход которого соединен с первыми входами цифроаналогового преобразователя, счетчика числа индикации помех и второго переключателя, второй вход и выход которого соединен с первыми входами второго и третьего злементов ИЛИ и вторым входом второго элемента ИЛИ, выход которого соединен с входом блока управления, выход которого соединен с первым входом четвертого элемента ИЛИ, второй вхо которого соединен с выходом второго переключателя, и с вторыми входами первых накопителей сигнала, причем выход цифроаналогового преобразователя через третий элемент ИЛИ соединен с вторым входом счетчика числа индикации помех, отличающееся тем, что, с целью повышения точности контроля, в иего введены первый и второй блоки сравнения, двоичный счетчик, первый и второй регистры, пятый элемент ИЛИ, три элемента И, при этом первый и второй выходы счетчика числа индикации помех соединены соответственно с первыми входами первого и второго блоков сравнения и первым входом пятого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом второго регистра и первым входо первого регистра, второй вход и выходы которого соединены соотвмственно с выходом цифроаналогового преобразователя, с вторым входом цифроаналогового преобразователя и

вторым входом первого блока сравнения, первый и второй выходы которого соединены соответственно с вторым входом второго переключателя и объединенными первыми входами

первого, второго и третьего элементов И, выход и второй вход которого соединены соответственно с входом второго регистра и первым выходом второго блока сравнения, второй выход которого через второй элемент

И соединен с третьим входом третьего элемента ИЛИ, причем первый выход первого блока срав1{ения соединен с входом двоичного счетчика, второй вход и выход которого соединены соответственно с выходом и вторым

входом первого элемента И, выход которого соединен с вторыми входами вторых накопителей сигнала.

Источники информации, принятые во внимание при экспертизе

Способы защиты от оцшбки в аппаратуре передачи данных Спец. исследов. комитета А- Вклад. №71, AEG Телефункен. Переводы документов ИССМККТТ, Ленинград, 1972

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-МОДУЛИРОВАННЫЙ ВЫСОТОМЕР | 1996 |

|

RU2106655C1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| Амплитудный временной квантователь с регулируемым порогом | 1982 |

|

SU1345150A1 |

| Устройство для распознавания прямых линий и краев изображений объектов | 1985 |

|

SU1327136A1 |

| РАДИОЛОКАЦИОННОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДАЛЬНОСТИ (ВАРИАНТЫ) | 1999 |

|

RU2154285C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство для цифровой обработки аналогового сигнала | 1986 |

|

SU1332335A1 |

| Устройство для измерения отношения сигнал-шум канала связи | 1980 |

|

SU883775A1 |

Авторы

Даты

1983-03-07—Публикация

1981-10-21—Подача