Изобретение относится к радиосвя зи и может быть использовано для формирования сигналов частотной телеграфии,

Известна система с частотной модуляцией, содержащая последовательно соединенные фазовый детектор, делитель частоты и подстраиваемый ге- нератор, второй вход которого соединен с выходом управляющего элемента, вход которого соединен с выходом фильтра нижних частот, вход ко- торого соединен с выходом фазового детектора, к второму входу которого подключен выход эталонного генератора 1 3.

Недостатком известной системы является сдвиг средней .частоты сигнала при передаче длинной последовательности единиц или нулей.

Наиболее близким к предлагаемому по технической сущности является устройство для формирования частотН5 -манипулированных сигналов, содержащее последовательно соединенные фильтр нижних частот, блок управления, автогенератор, смеситель и усилитель промежуточной частоты, причем второй вход автогенератора подключен к выходу частотного модулятора.

а второй вход смесителя соединен с выходом эталонного генератора 2.

Однако устройство обладает недостаточной точностью формирования сигналов частотной телеграфиц.

Цель изобретения - повышение точности формирования частотно-манипулированных сигналов, а также уменьшение времени установки частоты и

10 повышение помехоустойчивости при больших расстройках.

Для достижения поставленной цели в устройство для формирования час тотно-манипулированных сигналов вве15дены датчик кода, два цифроаналоговых преобразователя, сумматор, вычислительный блок и блок измерения частоты, первый выход которого соединен с первым входом вычисли20тельного блока, основные и дополнительный выходы которого соединены соответственно с основными и дополнительным входами первого цифро-аналогового преобразователя, синхро-/

25 низирующий вход которого соединен с вторлм выходом блока измерения ,1частоты, первый вход которого соединен с входом частотного модулятора и с.первым входом датчика кода,

30 .первый выход которого через второй

цифроаналоговый преобразователь соединен с первым входом сумматора, второй вход которого соединен с выходом первого цифроаналогового преобразователя, при этом выход сумматора соединен с входом фильтра нижних частот, второй выход датчика кода соединен с вторым входом вы(числительного- блока, выход усилителя промежуточной частоты соединен с вторым входом блока измерения частоты.

При этом введены инвертор, третий цифроаналоговый преобразователь, реверсивный счетчик, два элемента И и генератор тактовых импульсов, выход которого соединен с первыми входами первого и второго элементов И, выходы которых соединены соответственно с первым и вторым входами реверсивного счетчика, выход которого через третий цифроаналоговый преобразователь подключен к третьему входу сумматора, причем дополнительный вход первого цифроаналогового преобразователя соединен с вторым входом первого элемента И и с входом инвертора, выход которого соединен с вторым входом второго элемента И, третий вход которого соединен с дополнительным выходом блока измерения частоты и с третьим входом первого элемента И.

Кроме того. введены последовательно соединенные дешифратор и коммутатор, выход которого соединен с основными входами первого цифроаналогового преобразователя, причем основные выходы вычислительного блока соединены с входами дешифратора с входами коммутатора.

,и

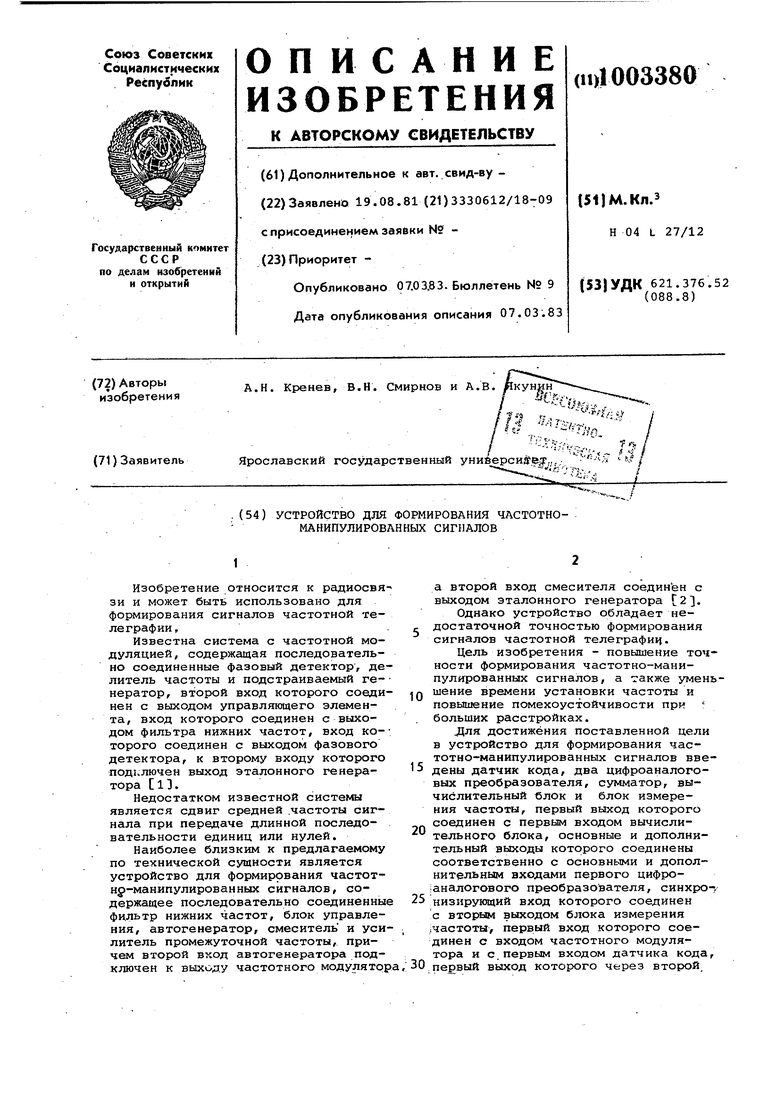

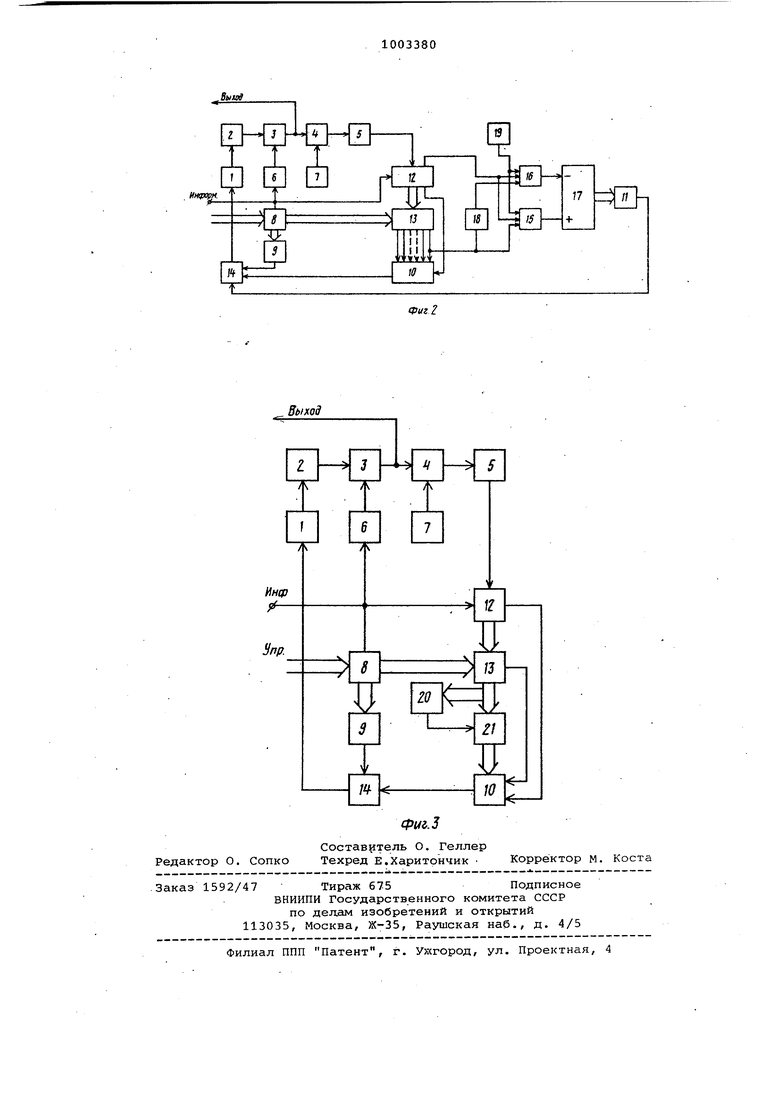

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на фиг. 2 и 3 - структурные электрические схемы, варианты

Предлагаемое устройство содержит фильтр 1 нижних частот, блок 2 управления, автогенератор 3, смеситель 4, усилитель 5 промежуточной частоты, частотный модулятор б, эталонный генератор 7, датчик 8 кода, цифроаналоговые преобразователи 9-11, блок 12 измерения частоты, вычислительный блок 13, сумматор 14, элементы И 15 и 16, реверсивный счетчик 17 инвертор 18, генератор 19 тактовых импульсов, дешифратор 20, коммутатор 21.

Устройство работает следующим образом.

Информационный сигнал подается на частотный модулятор б, датчик 8 кода и блок 12 измерения частоты. С выходка частотного модулятора 6 он поступает на вход автогенератора 3, где осуществляется частотная манипуляция. С выхода автогенератора 3 частотно-манипулированный сигнал

подается на смеситель 4, на второй вход которого подается сигнал с выхода эталонного генератора 7. С выхода смесителя 4 сигнал промежуточной частоты через усилитель 5 проме жуточной частоты подается на выход блока 12 измерения частоты, который измеряет частоту сигнала. Блок 12 измерения частоты работает в автоматическом режиме, т.е. непрерывно производит измерения. Если во время измерения производится манипуляция частоты, то данное измерение бракуется и на первом выходе блока 12 измерения частоты сохраняется код предыдущего результата, а с второго Выхода запрещается, прохождение сиг;хросигнала на цифроаналоговый прё образователь 10. Результат измерения, представленный в двоичном коде подается на вычислительный блок 13, на второй вход которого подается ко соответствукяций требуемому значению выходной частоты устройства с выхода датчика 8 кода. В датчике 8 кода хранится набор возможных значений несущих частот Q и девиаций д. Выбор необходимой несущей частоты и девиации осуществляется подачей соответствующего кода на вход датчика 8 кода. На первом вЕлходе датчика 8 кода устанавливается код несущей частоты fо, а с второго выхода код подается на вычислительный блок 13, соответственно код частоты нажатия или отжатия в зависимости от значения информационного сигнала Вычислительный блок 13 осуществляет вычисление модуля и знака разности между кодом опорной частоты и кодом измеренной частоты. Результат вычисления с помощью дифроаналогового преобразователя 10, синхронизируемого импульсом синхронизации, с второго выхода блока 12 измерения частоты преобразуется в напряжение ошики, которое суммируется в сумматоре 14 с напряжением, определяющем несущую частоту и через фильтр 1 нижних частот и блок 2 управления Подается на первый вход автогенератора изменяя при этом частоту на величину определяемую сигналом ошибки.

Такое выполнение устройства позволяет получить высокую точность подстройки частоты за счет уменьше ния полосы захвата.

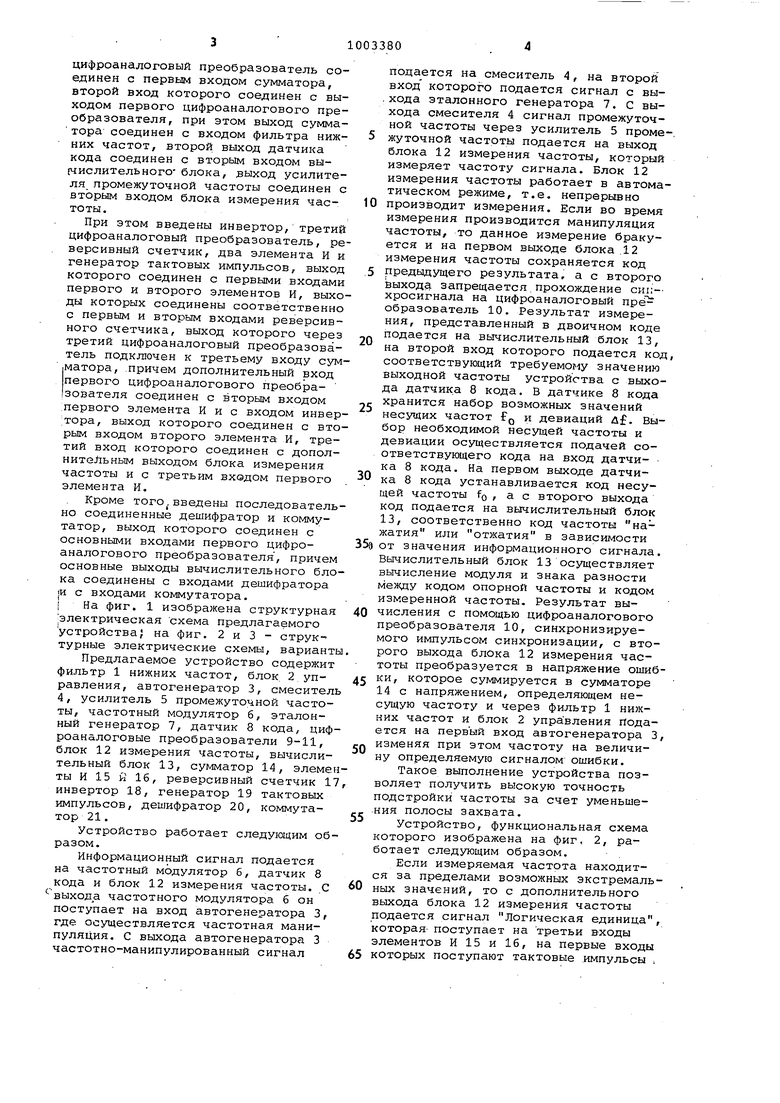

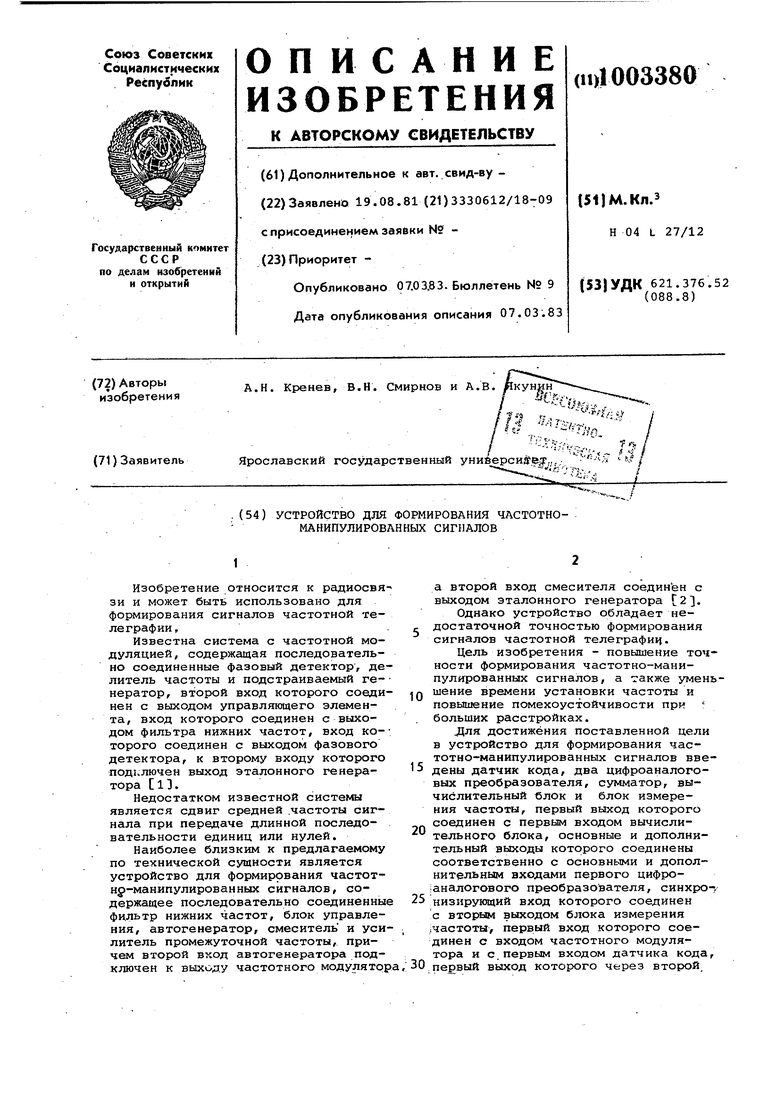

Устройство, функциональная схема которого изображена на фиг, 2, работает следующим образом.

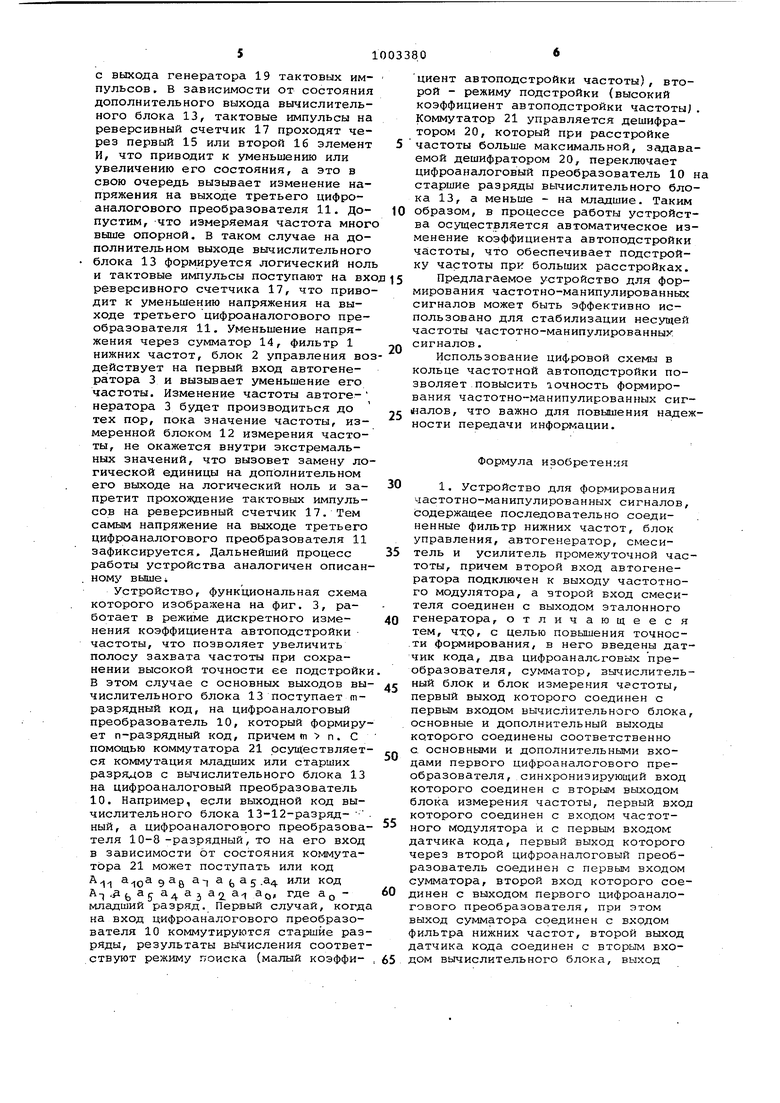

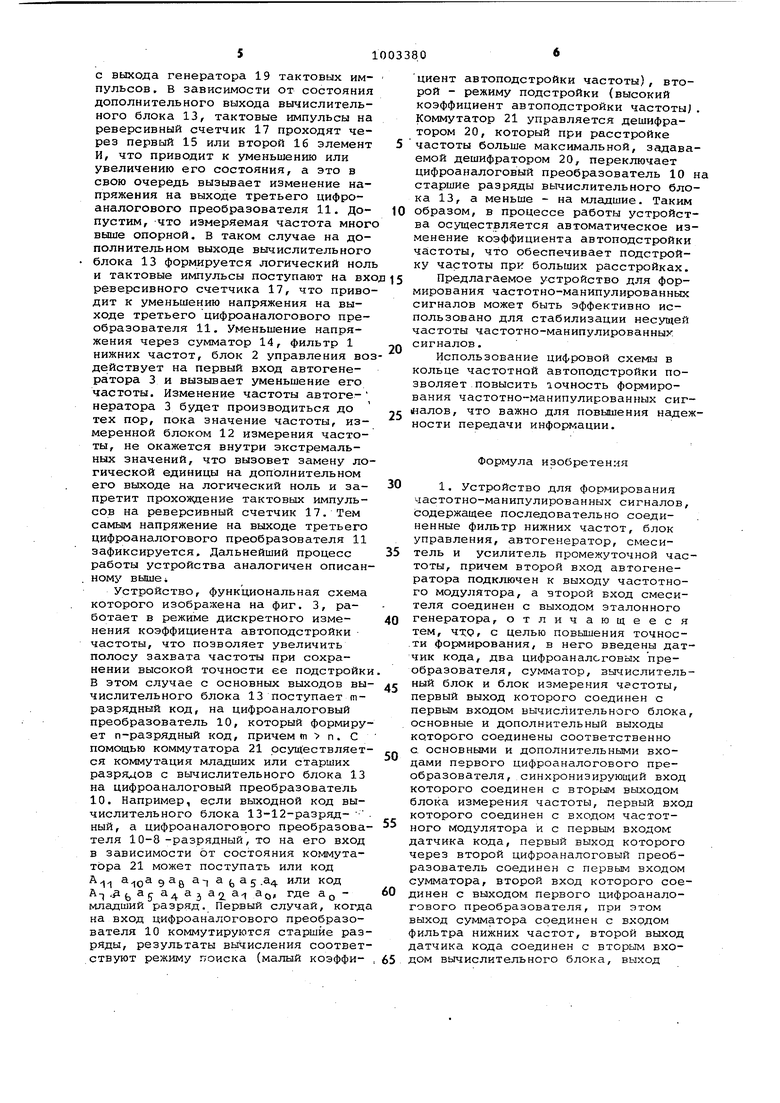

Если измеряемая частота находится за пределами возможных экстремалных значений, то с дополнительного выхода блока 12 измерения частоты подается сигнал Логическая единица которая- поступает на третьи входы элементов И 15 и 16, на первые вход которых поступают тактовые импульсы с выхода генератора 19 тактовых импульсов. В зависимости от состояния дополнительного выхода вычислительного блока 13, тактовые импульсы на реверсивный счетчик 17 проходят через первый 15 или второй 16 элемент И, что приводит к уменьшению или увеличению его состояния, а это в свою очередь вызывает изменение напряжения на выходе третьего цифроаналогового преобразователя 11. Допустим, что измеряемая частота мног выше опорной. в таком случае на дополнительном выходе вычислительного блока 13 формируется логический нол и тактовые импульсы поступают на вх реверсивного счетчика 17, что приво дит к уменьшению напряжения на выходе третьего цифроаналогового преобразователя 11. Уменьшение напряжения через сумматор 14, фильтр 1 нижних частот, блок 2 управления во действует на первый вход автогенератора 3 и вызывает уменьшение его частоты. Изменение частоты автогенератора 3 будет производиться до тех пор, пока значение частоты, измеренной блоком 12 измерения частоты, не окажется внутри экстремальных значений, что вызовет замену ло гической единицы на дополнительном его выходе на логический ноль и запретит прохояодение тактовых импульсов на реверсивный счетчик 17. Тем самым напряжение на выходе третьего цифроаналогового преобразователя 11 зафиксируется. Дальнейший процесс работы устройства аналогичен описан ному выше i Устройство, функциональная схема которого изображена на фиг. 3, работает в режиме дискретного изменения коэффициента автоподстройки частоты, что позволяет увеличить полосу захвата частоты при сохранении высокой точности ее подстройк В этом случае с основных выходов вы числительного блока 13 поступает тразрядный код, на цифроаналоговый преобразователь 10, который формиру ет п-разрядный код, причем m п. С помощью коммутатора 21 осуществляет ся коммутация младших или старших разрядов с вычислительного блока 13 на цифроаналоговый преобразователь 10. Например, если выходной код вычислительного блока 13-12-разряд- ный, а цифроаналогового преобразова теля 10-8-разрядный, то на его вход в зависимости от состояния коммутатора 21 может поступать или код А 10 Т () °Д А- ,д а а. а J а а ац, где а, младший разряд. Первый случай, когд на вход ц-ифроаналогового преобразователя 10 коммутируются старшие раз ряды, результаты вычисления соответ ствуют режиму поиска (малый коэффициент автоподстройки частоты), второй - режиму подстройки (высокий коэффициент автоподстройки частоты. Коммутатор 21 управляется дешифратором 20, который при расстройке частоты больше максимальной, задаваемой дешифратором 20, переключает цифроаналоговый преобразователь 10 на старшие разряды вычислительного блока 13, а меньше - на младшие. Таким образом, в процессе работы устройства осуществляется автоматическое изменение коэффициента автоподстройки частоты, что обеспечивает подстройку частоты при больших расстройках. Предлагаемое устройство для формирования частотно-манипулированных сигналов может быть эффективно использовано для стабилизации несущей частоты частотно-манипулированных сигналов. Использование цифровой схемы в кольце частотной автоподстройки позволяет повысить ючность формирования частотно-манипулированных сиг«алов, что важно для повышения надежности передачи информации. Формула изобретения 1. Устройство для формирования частотно-манипулированных сигналов, содержащее последовательно соединенные фильтр нижних частот, блок управления, автогенератор, смеситель и усилитель промежуточной частоты, причем второй вход автогенератора подключен к выходу частотного модулятора, а второй вход смесителя соединен с выходом эталонного генератора, отличающееся тем, что, с целью повышения точности формирования, в него введены датчик кода, два цифроаналсговых преобразователя, сумматор, вычислительный блок и блок измерения частоты, первый выход которого соединен с первым входом вычислительного блока, основные и дополнительный выходы которого соединены соответственно с. основными и дополнительными входами первого цифроаналогового преобразователя, синхронизирующий вход которого соединен с вторым выходом блока измерения частоты, первый вход которого соединен с входом частотного модулятора и с первым входом датчика кода, первый выход которого через второй цифроаналоговый преобразователь соединен с первьом входом сумматора, второй вход которого соединен с выходом первого цифроаналогового преобразователя, при этом выход сумматора соединен с входом фильтра нижних частот, второй выход датчика кода соединен с вторым входом вычислительного блока, выход

усилителя промежуточной частоты соединен с вторьом входом блока измерения частоты.

2. Устройство по п. 1, о т л ич .а ю щ 6 е с я тем, что, с целью уменьшения времени установки частоты, в введены инвертор, третий цифроаналоговый преобразователь, реверсивный счетчик, два элемента И и генератор тактовых импульсов, выход которого соединен с первыми входами первого и второго элементов И, выходы которых соединены соответственно с первым и вторымвходами реверсивного счетчика, выход которого через третий цифроаналоговый преобразователь подключен к третьему входу сумматора, причем дополнительный вход первого гифроаналогового преобразователя соединен с вторым входом первого элемента и и с входом инвертора, выход которого соединен с вторым входом второго элемента И, третий вход которого соединен с дополнительным выходом блока измерения частоты и с третьим входом первого элемента И.

3. Устройство по п. 1,0 т личающееся тем, что, с целью повышения помехоустойчивости при

больших расстройках, в него введены последовательно соединенные дешифратор и коммута1 ор, выход которого соединен с основными входами первого цифроаналогового преобразователя,

причем основные первые выходы вычислительного блока соединены с вхо-: дами дешифратора и с входами коммутатора .

Источники информации, принятые во внимание при экспертизе

1.Чупраков В.А, Частотная модуляция в системе фазовой АПЧ с делением частоты в кольце обратной связи, Вопросы радиоэлектроники. Вып. 1, сер. Радйоизмерительная техника, 1969, с. 62-72.

2.Каганов В.И. Системы автоматического регулирования в радиопередатчиках. М., СЕЯЗЬ, 1969, с. 117

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приема телеметрической информации | 1989 |

|

SU1735883A1 |

| ГЕНЕРАТОР С АВТОМАТИЧЕСКОЙ ПОДСТРОЙКОЙ ЧАСТОТЫ | 1992 |

|

RU2060584C1 |

| Частотный манипулятор | 1980 |

|

SU873450A1 |

| Измеритель электропроводности | 1989 |

|

SU1670623A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Цифровое устройство частотной автоподстройки | 1983 |

|

SU1104659A1 |

| Устройство для ограничения спектра частотно-манипулированного сигнала | 1980 |

|

SU907852A1 |

| Частотный манипулятор | 1979 |

|

SU886300A1 |

| Фотоэлектрический анализатор количества и размеров частиц | 1987 |

|

SU1518727A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

Авторы

Даты

1983-03-07—Публикация

1981-08-19—Подача