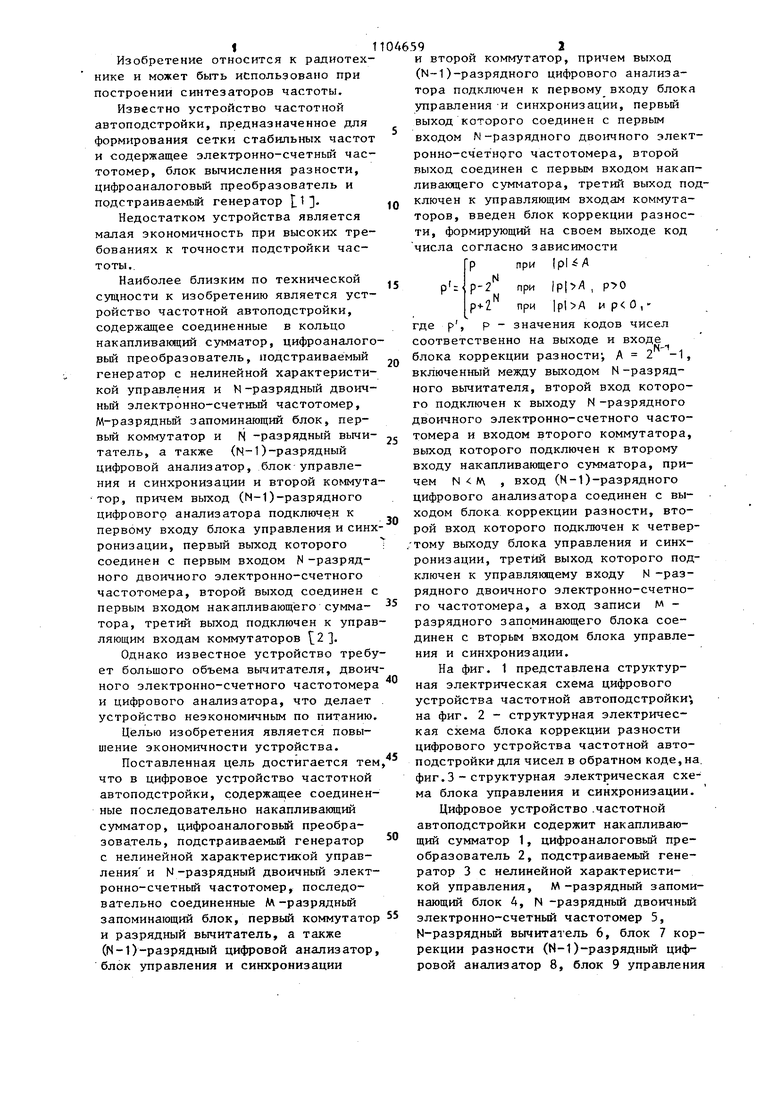

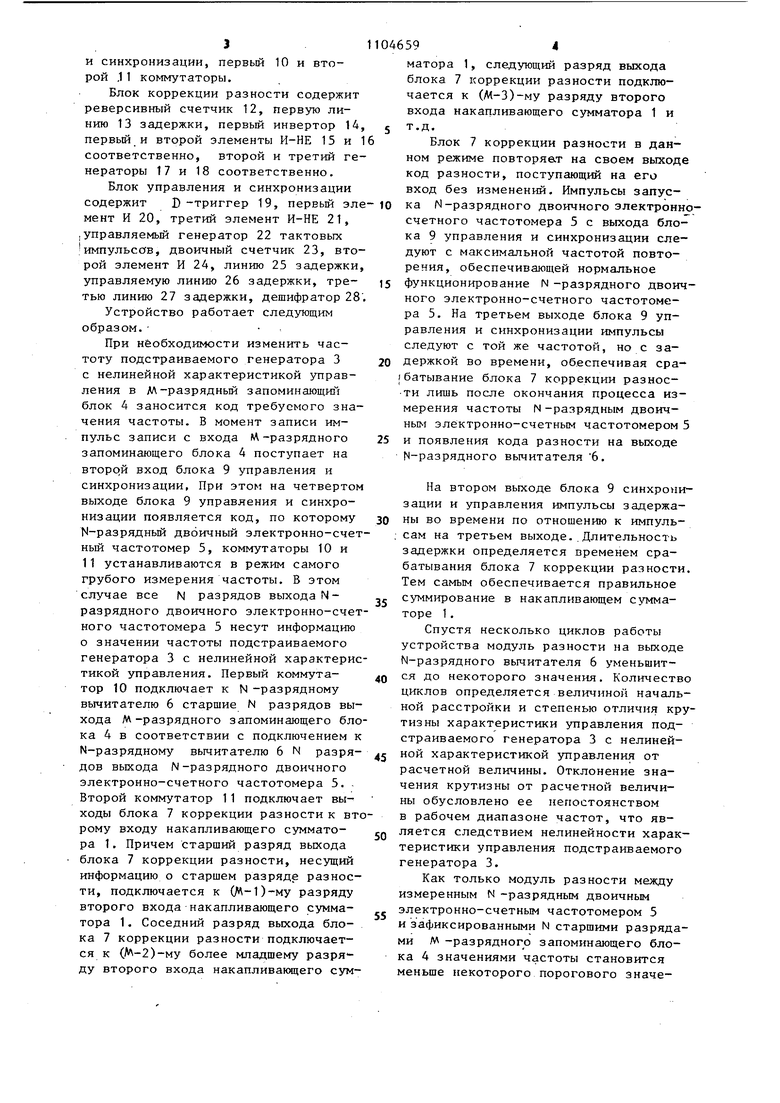

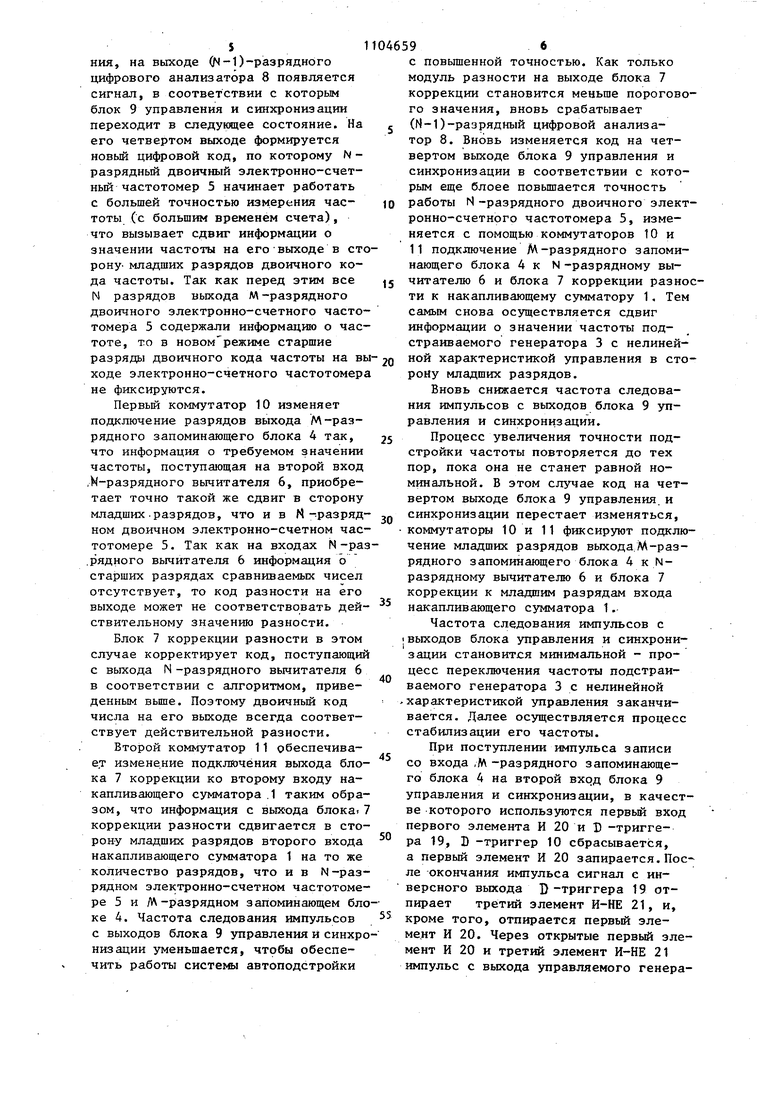

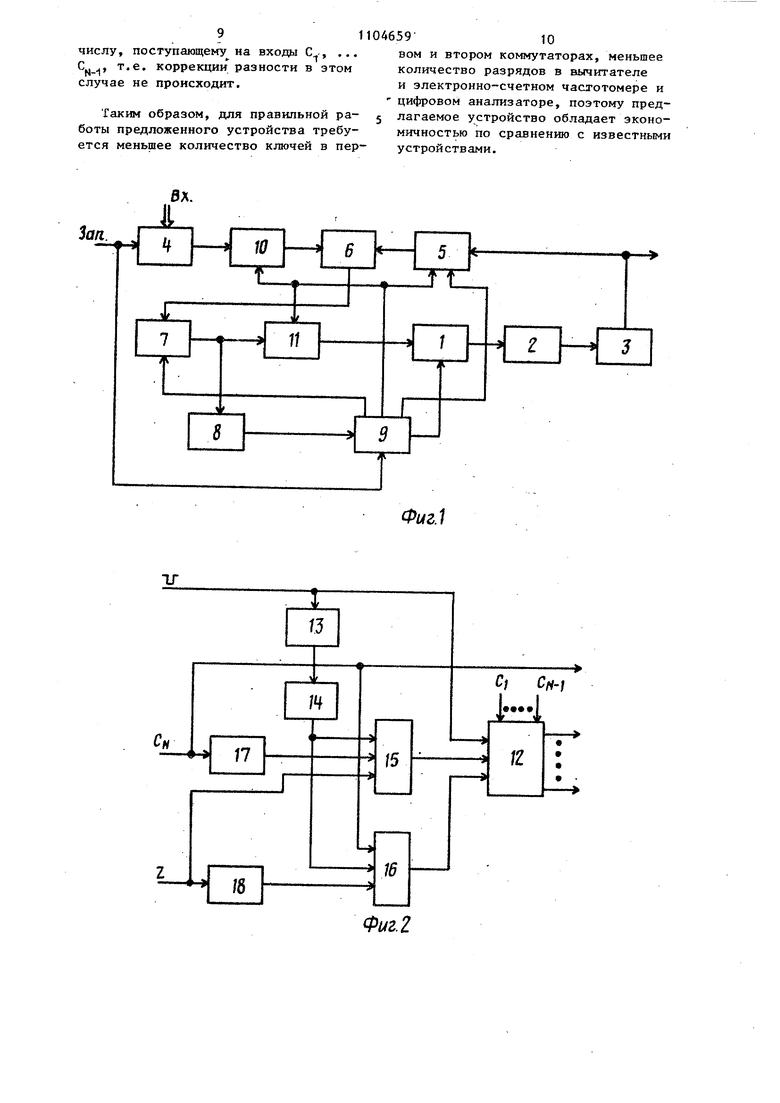

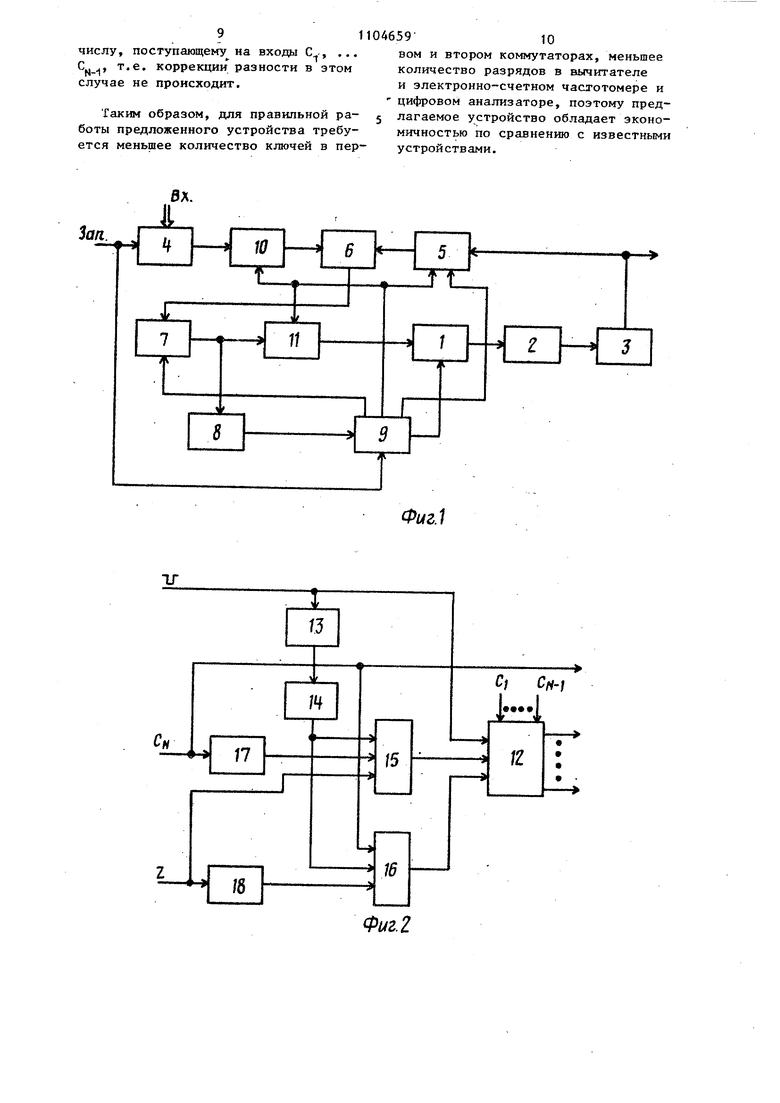

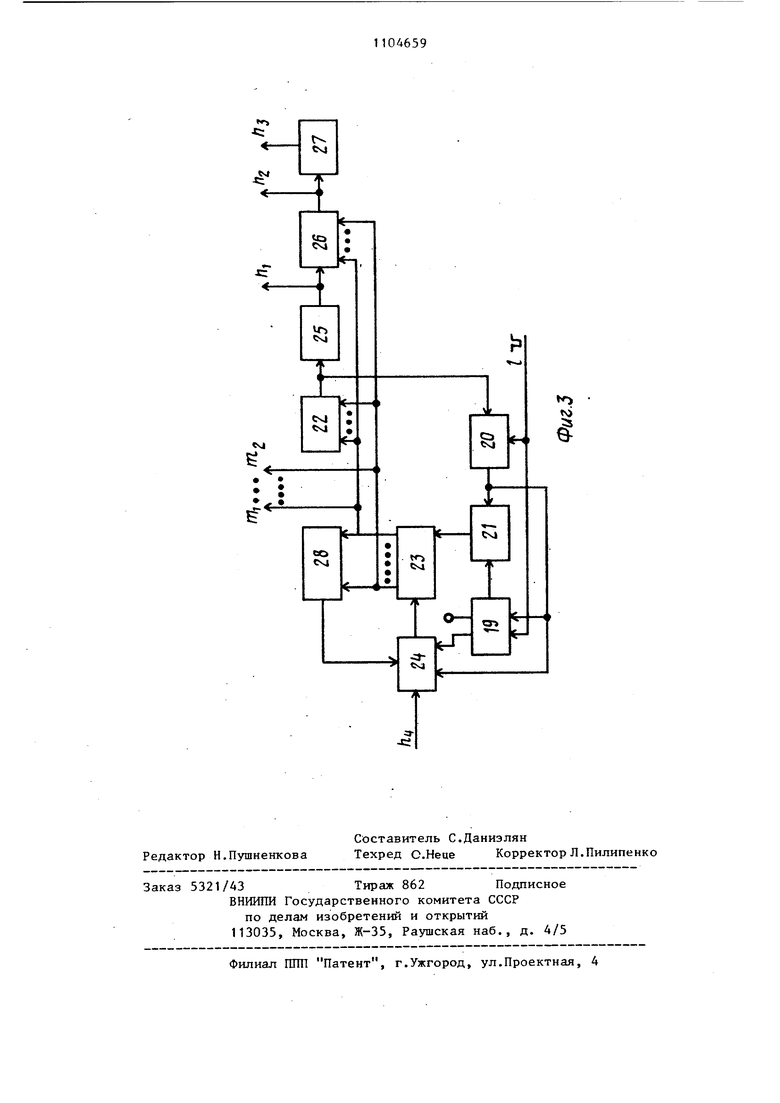

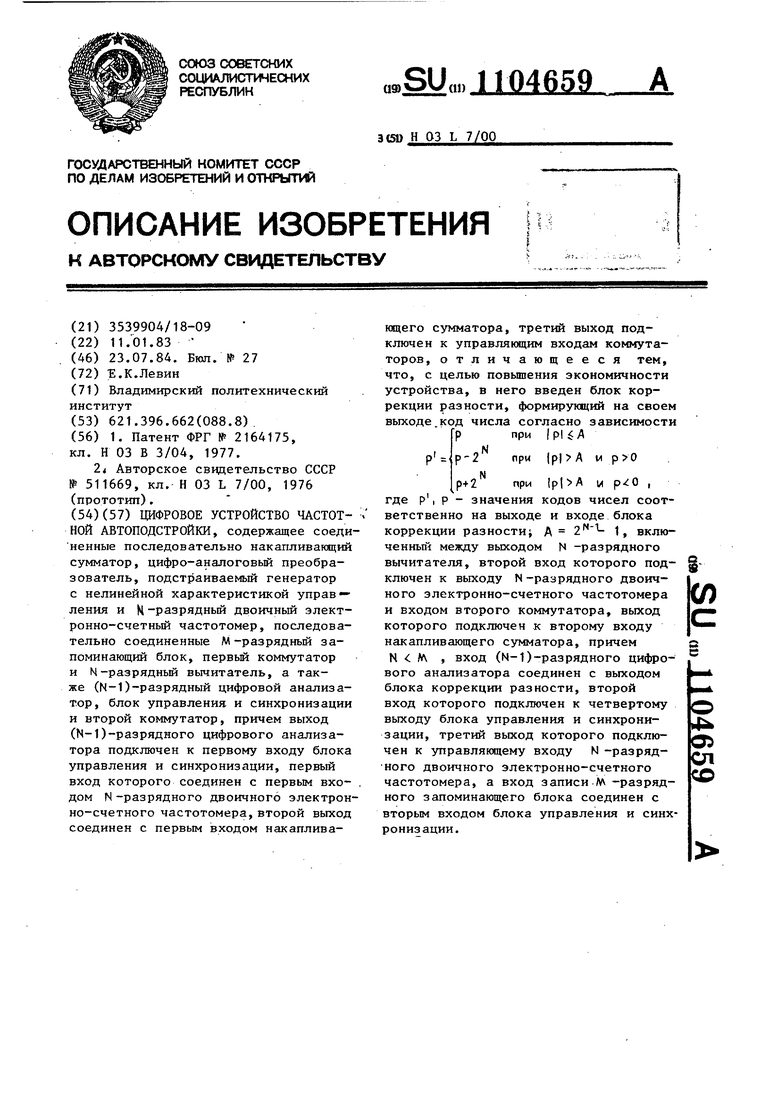

Изобретение относится к радиотехнике и может быть использовано при построении синтезаторов частоты. Известно устройство частотной автоподстройки, предназначенное для формирования сетки стабильных частот и содержащее электронно-счетньй частотомер, блок вычисления разности, цифроаналоговьй преобразователь и подстраиваемьй генератор 1. Недостатком устройства является малая экономичность при высоких требованиях к точности подстройки частоты.. Наиболее близким по технической сущности к изобретению является устройство частотной автоподстройки, содержащее соединенные в кольцо накапливающий сумматор, цифроаналого вьй преобразователь, подстраиваемый генератор с нелинейной характеристикой управления и N-разрядный двоичньм электронно-счетный частотомер, М-разрядньй запоминающий блок, первый коммутатор и IX -разрядный вычитатель, а также (N-1)-разрядный цифровой анализатор, блок управления и синхронизации и второй коммута тор, причем выход (М-1)-разрядного цифрового анализатора подключен к первому входу блока управления и синх ронизации, первый выход которого соединен с первым входом N-разрядного двоичного электронно-счетного частотомера, второй выход соединен с первым входом накапливающего сумматора, третий выход подключен к управ ляющим входам коммутаторов 23Однако известное устройство требу ет большого объема вычитателя, двоич ного электронно-счетного частотомера и цифрового анализатора, что делает устройство неэкономичным по питанию Целью изобретения является повышение экономичности устройства. Поставленная цель достигается тем что в цифровое устройство частотной автоподстройки, содержащее соединенные последовательно накапливающий сумматор, цифроаналоговьй преобразователь, подстраиваемьй генератор с нелинейной характеристикой управления и N-разрядный двоичный электронно-счетньй частотомер, последовательно соединенные Ал -разрядньй запоминающий блок, первый коммутатор и разрядный вычитатель, а также (Н-1)-разрядный цифровой анализатор блок управления и синхронизации и второй коммутатор, причем выход (N-1)-разрядного цифрового анализатора подключен к первому входу блока управления -и синхронизации, первьй выход которого соединен с первым входом N-разрядного дво1тчного электронно-счетного частотомера, второй выход соединен с первым входом накапливающего сумматора, третий выход подключен к управляющим входам коммутаторов, введен блок коррекции разности, формирующий на своем выходе код числа согласно зависимости при при , при |р1 А и р О , где р, р значения кодов чисел соответственно на выходе и входе блока коррекции разности-, Л 2 -1, включенный между выходом N-разрядного вычитателя, второй вход которого подключен к выходу N-разрядного двоичного электронно-счетного частотомера и входом второго коммутатора, выход которого подключен к второму входу накапливающего сумматора, причем N fA , вход (N-1)-разрядного цифрового анализатора соединен с выходом блока коррекции разности, второй вход которого подключен к четвертому вьрсоду блока управления и синхронизации, третий выход которого подключен к управляющему входу N -разрядного двоичного электронно-счетного частотомера, а вход записи м разрядного запоминающего блока соединен с вторым входом блока управления и синхронизации. На фиг. 1 представлена структурная электрическая схема цифрового устройства частотной автоподстройки, на фиг. 2 - структурная электрическая схема блока коррекции разности цифрового устройства частотной автоподе тройки для чисел в обратном коде,на. фиг.3 - структурная электрическая схема блока управления и синхронизации. Цифровое устройство .частотной автоподстройки содержит накапливающий сумматор 1, цифроаналоговьй преобразователь 2, подстраиваемьй генератор 3 с нелинейной характеристикой управления, М -разрядный запоминающий блок А, N -разрядный двоичньй электронно-счетный частотомер 5, N-разрядньй вычитатель 6, блок 7 коррекции разности (N-1)-разрядный цифровой анализатор 8, блок 9 управления и синхронизации, первый 10 и второй ,1 1 коммутаторы. Блок коррекции разности содержит реверсивный счетчик 12, первую линию 13 задержки, первый инвертор 14 первый и второй элементы И-НЕ 15 и соответственно, второй и третий генераторы 17 и 18 соответственно. Блок управления и синхронизации содержит D -триггер 19, первый эл мент И 20, третий элемент И-НЕ 21, I управляемый генератор 22 тактовых импульсав, двоичный счетчик 23, второй элемент И 24, линию 25 задержки управляемую линию 26 задержки, третью линию 27 задержки, дешифратор 28 Устройство работает следующим образом. При необходимости изменить частоту подстраиваемого генератора 3 с нелинейной характеристикой управления в М-разрядный запоминающий блок 4 заносится код требуемого значения частоты. В момент записи импульс записи с входа N -разрядного запоминающего блока 4 поступает на второй вход блока 9 управления и синхронизации, При этом на четвертом выходе блока 9 управления и синхронизации появляется код, по которому N-разрядньй двоичный электронно-счет ный частотомер 5, коммутаторы 10 и 11 устанавливаются в режим самого грубого измерения частоты. В этом случае все N разрядов выхода Nразрядного двоичного электронно-счет ного частотомера 5 несут информацию о значении частоты подстраиваемого генератора 3 с нелинейной характерис тикой управления. Первый коммутатор 10 подключает к N -разрядному вьгчитателю 6 старшие N разрядов выхода М-разрядного запоминающего бло ка 4 в соответствии с подключением к N-разрядному вьгчитателю 6 N разрядов выхода N-разрядного двоичного электронно-счетного частотомера 5. . Второй коммутатор 11 подключает выходы блока 7 коррекции разности к вт рому входу накапливающего сумматора 1. Причем старший разряд выхода блока 7 коррекции разности, несущий информацию о старшем разряде разности, подключается к (-1)-му разряду второго входа накапливающего сумматора 1. Соседний разряд выхода блока 7 коррекции разности подключается к (М-2)-му более младшему разряду второго входа накапливающего сум 594 матора 1, следующий разряд выхода блока 7 коррекции разности подключается к (М-З)-му разряду второго входа накапливающего сумматора 1 и т.д. Блок 7 коррекции разности в данном режиме повторяел на своем выходе код разности, поступающий на его вход без изменений. Импульсы запуска N-разрядного двоичного электронносчетного частотомера 5 с выхода блока 9 управления и синхронизации следуют с максимальной частотой повторения, обеспечивающей нормальное функционирование N -разрядного двоичного электронно-счетного частотомера 5. На третьем выходе блока 9 управления и синхронизации импульсы следуют с той же частотой, но с задержкой во времени, обеспечивая срабатывание блока 7 коррекции разности лишь после окончания процесса измерения частоты N-разрядным двоичным электронно-счетным частотомером 5 и появления кода разности на выходе N-разрядного вычитателя 6. На втором выходе блока 9 синхронизации и управления импульсы задержаны во времени по отношению к импульсам на третьем выходе..Длительность задержки определяется временем срабатывания блока 7 коррекции разности. Тем самым обеспечивается правильное суммирование в накапливающем сумматоре 1. Спустя несколько циклов работы устройства модуль разности на выходе N-разрядного вычитателя 6 уменьшится до некоторого значения. Количество циклов определяется величиной начальной расстройки и степенью отличия крутизны характеристики управления подстраиваемого генератора 3 с нелинейной характеристикой управления от расчетной величины. Отклонение значения крутизны от расчетной величины обусловлено ее непостоянством в рабочем диапазоне частот, что является следствием нелинейности характеристики управления подстраиваемого генератора 3. Как только модуль разности между измеренным N -разрядным двоичным электронно-счетным частотомером 5 и зафиксированными N старшими разрядами W -разрядного запоминающего блока 4 значениями частоты становится меньше некоторого порогового значения, на выходе (N-l)-pa3pflAHoro цифрового анализатора 8 появляется сигнал, в соответствии с которым блок 9 управления и синхронизации переходит в следующее состояние. На его четвертом выходе формируется новый цифровой код, по которому N разрядный двоичный электронно-счетньй частотомер 5 начинает работать с большей точностью измерения частоты (с большим временем счета), что вызывает сдвиг информации о значении частоты на его выходе в сто рону- младших разрядов двоичного кода частоты. Так как перед этим все N разрядов выхода М-разрядного двоичного электронно-счетного частотомера 5 содержали информацию о частоте, то в новомрежиме старшие разряды двоичного кода частоты на вы ходе электронно-счетного частотомера не фиксируются. Первьй коммутатор 10 изменяет подключение разрядов выхода М-разрядного запоминающего блока 4 так, что информация о требуемом значении частоты, поступающая на второй вход .-разрядного вычитателя 6, приобретает точно такой же сдвиг в сторону младших .разрядов, что и в Н--разрядном двоичном электронно-счетном частотомере 5. Так как иа входах N-раз .рядного вычитателя 6 информация о старших разрядах сравниваемых чисел отсутствует, то код разности на его выходе может не соответствовать действительному значению разности. Блок 7 коррекции разности в этом случае корректирует код, поступающий с выхода N-разрядного вычитателя 6 в соответствии с алгоритмом, приведенным выше. Поэтому двоичный код числа на его выходе всегда соответствует действительной разности. Второй коммутатор 11 обеспечивает измене.ние подключения выхода блока 7 коррекции ко второму входу накапливающего сумматора .1 таким образом, что информация с вых-ода блока 7 коррекции разности сдвигается в сторон-у младших разрядов второго входа накапливающего сумматора 1 на то же количество разрядов, что и в N-разрядном электронно-счетном частотомере 5 и А -разрядном запоминающем бло ке 4. Частота следования импульсов с выходов блока 9 управления и синхро низации уменьшается, чтобы обеспечить работы систе а1 автоподстройки С повышенной точностью. Как только модуль разности на выходе блока 7 коррекции становится меньше порогового значения, вновь срабатывает (N-1)-разрядный цифровой анализатор 8. Вновь изменяется код на четвертом выходе блока 9 управления и синхронизации в соответствии с которым еще блоее повьштается точность работы N -разрядного двоичного электронно-счетного частотомера 5, изменяется с помощью коммутаторов 10 и 11 подключение М-разрядного запоминающего блока 4 к N-разрядному вычитателю 6 и блока 7 коррекции разности к накапливающему сумматору 1. Тем самым снова осзта(ествляется сдвиг информации о значении частоты подстраиваемого генератора 3 с нелинейной характеристикой управления в сторону младших разрядов. Вновь снижается частота следования импульсов с выходов блока 9 управления и синхронизации. Процесс увеличения точности подстройки частоты повторяется до тех пор, пока она не станет равной номинальной. В этом случае код на четвертом выходе блока 9 управления, и синхронизации перестает изменяться, коммутаторы 10 и 11 фиксируют подключение младших разрядов выход а. М-разрядного запоминающего блока 4 к Nразрядному вычитателю 6 и блока 7 коррекции к младшим разрядам входа накапливающего сумматора 1. Частота следования импульсов с выходов блока управления и синхронизации становится минимальной - процесс переключения частоты подстраиваемого генератора 3 с нелинейной характеристикой управления заканчивается. Далее осуществляется процесс стабилизации его частоты. При поступлении импульса записи со входа ,М -разрядного запоминающего блока 4 на второй вход блока 9 управления и синхронизации, в качестве которого используются первьй вход первого элемента И 20 и Б -триггера 19, D -триггер 10 сбрасывается, а первый элемент И 20 запирается. После окончания импульса сигнал с инверсного выхода D Триггера 19 отпирает третий элемент И-НЕ 21, и, кроме того, отпирается первый элеме.нт И 20. Через открытые первый элемент И 20 и третий элемент И-НЕ 21 импульс с выхода управляемого генератора 22 тактовых импульсов проходит на вход установки нуля двоичного счетчика 23, устанавливая его в исходное состояние и на синхровход D-триггера 19, переводя его в единич ное состояние (наD-входD-триггера 19 подана логическая единица), что вызывает запирание третьего элемента И-НЕ 21 и передачу разрешающего потенциала на второй элемент И 24 Блок 7 коррекции разности (фиг. 2) работает следующим образом. Информация с выхода N -разрядного счетчика 6 поступает на входы реверсивного счетчика 12, Таким образом, после первого прошедшего первый элемент И 20 импульса с выхода управляемого генерато- . ра 22 на выходах двоичного счетчика 23, являющихся третьим выходом блока 9 управления и синхронизации, устанавливается начальный код управляющей коммутации 10 и 11 и N-разрядника двоичным электронно-счетным частотомером. Спустя время, необходимое для окончания процесса установ ки двоичного счетчика 23 в исходное состояние на выходе первого элемента 25 задержки, являкяцегося вторым входом блока 9, появляется импульс запуска N -разрядного двоичного электронно-счетного частотомера 5. После того, как на его выходе появит ся результат измерения частоты подстраиваемого генератора 3, на выходе управляемой линии 26 задержки, являкяцейся четвертым выходом блока 9, появляется импульс, поступающий на второй вход элемента 7 коррекции раз ности. После окончания процесса коррекции разности на выходе второй линии 27 задержки, являющейся вторым выходом блока 9, появляется импульс, поступающий на первьй вход накапливающего сумматора 1. С появлением, следующего импульса на выходе управляемого генератора 22 вся последовательность импульсов на выходах блока повторяется. Как только модуль разности на выхо де блока 7 коррекции разности станет меньше искомого порогового значения, срабатьгоает (N-1)-разрядныйцифровой сигнализатор 8. Сигнал с его выхода поступает на вход второго элемента И 24, являющегося первым входом блока 9, и отк рывает едо, второй элемент И 24 про- 598 пускает очередной импульс с выхода управляемого генератора 22, прошедший через открытый первый элемент И 20 на счетный вход двоичного счетчика 23. Изменение кода на выходе двоичного счетчика 23 вызовет увеличение точности работы М-разрядного электронно-счетного частотомера 5 и соответствующего переключения коммутаторов 10 и 11, а также увеличит период следования импульсов с выхода управляемого генератора 22 и время задержки в управляемой линии 26 задержки. При последующих срабатываниях (N-1)-разрядного цифрового анализатора 8 состояние двоичного счетчика 23 изменяется, что вызывает увеличение точности автоподстройки частоты, при номинальной точности автоподстройки срабатывает дешифратор 28, который закрывает второй элемент И 24, -запрещая прохождение импульсов на счетный вход двоичного счетчика 23. Изменение состояния двоичного счетчика 23 прекращается и все устройство переходит в режим стабилизации частоты подстраиваемого генератора 3. Информации с выхода (М-1)-разрядного вычитателя 6 поступает на входы реверсивного счетчика 12. При поступлении импульса с четвертого, выхода блока 9 проходит запись этой информации реверсивного счетчика 12.После окончания процесса записи импульс появляется на выходе первой линии 13 задержки. Пройдя через первый инвертор 14, он поступает на первые входы первого и второго элементов И-НЕ 15 и 16. На эти же элементы непосредственно и через второй и третий инверторы 17 и 18 поступает информация со старшего (С|) и знакового (2) разрядов (N-1)-разрядного вычитателя 6. Если число, поступившее с выхода (N-1)-разрядного вычитателя 6 положительное, то . Если при этом С1 1, то на вычитающий счетчик вход реверсивного счетчика 12 поступает импульс, уменьшающий записанное в реверсивном счетчике 12 число на единицу. Если же число отрицательное, С О, то импульс поступает на суммирующий счетный вход и происходит увеличение записанного ранее числа на единицу. Если же или Z 1 иС|, 1, то на счетные входы импульсы не поступают и число на выходах реверсивного счетчика 12 равно

числу, поступающему на входы С, ... Си J, т.е. коррекции разности в этом случае не происходит.

Таким образом, для правильной работы предложенного устройства требуется меньшее количество ключей в пер- устройствами.

1104659-10

вом и втором коммутаторах, меньшее количество разрядов в вычитателе и электронно-счетном частотомере и цифровом анализаторе, поэтому предлагаемое устройство обладает экономичностью по сравнению с известными

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угловых перемещений в код | 1985 |

|

SU1311024A1 |

| Спектроанализатор кардиосигналов | 1984 |

|

SU1170371A1 |

| Цифровой частотомер | 1981 |

|

SU1068834A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Цифровая следящая система | 1986 |

|

SU1416936A1 |

| Многоканальный релейный спектроанализатор | 1983 |

|

SU1140129A1 |

| Устройство автоматической подстройки частоты генератора | 1980 |

|

SU982203A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ АНОМАЛЬНЫХ ЦИФРОВЫХ ОШИБОК ПРИ ПЕРЕДАЧЕ РЕЧИ МЕТОДОМ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИИ | 1999 |

|

RU2159470C1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

ЦИФРОВОЕ УСТРОЙСТВО ЧАСТОТ- НОЙ АВТОПОДСТРОЙКИ, содержащее соединенные последовательно накапливающий сумматор, цифро-аналоговый преобразователь, подстраиваемый генератор с нелинейной характеристикой управления и К-разрядньй двоичный электронно-счетный частотомер, последовательно соединенные М-разрядный запоминающий блок, первьй коммутатор и N-разрядный вычитатель, а также (N-1)-paзpядный цифровой анализатор, блок управления и синхронизации и второй коммутатор, причем выход (N-1)-разрядного цифрового анализатора подключен к первому входу блока управления и синхронизации, первый вход которого соединен с первым входом N-разрядного двоичного электронно-счетного частотомера, второй выход соединен с первым входом накапливающего сумматора, третий выход подключен к управлякящим входам коммутаторов, отличающееся тем, что, с целью повьштения зкономичности устройства, в него введен блок коррекции разности, формирутоций на своем выходе.код числа согласно зависимости р при ( р1 л .N р, р-2 прм |р| А и р 0 .N и р+2 при где р I р - значения кодов чисел соответственно на выходе и входе блока коррекции разности; А 1, включенньш между выходом N -разрядного вычитателя, второй вход которого подключен к выходу N-разрядного двоич(Л ного электронно-счетного частотомера и входом второго коммутатора, выход с которого подключен к второму входу накапливающего сумматора, причем N V , вход (N-1)-разрядного цифрового анализатора соединен с выходом блока коррекции разности, второй вход которого подключен к четвертому выходу блока управления и синхрони4 зации, третий выход которого подклюО) чен к управляющему входу N -разрядел ного двоичного электронно-счетного со частотомера, а вход записи Л -разрядного запоминающего блока соединен с вторым входом блока управления и синхронизации.

бл.

А.

Зап.

Фиг.1

Фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ДЛЯ ОЧИСТКИ ГАЗА | 1999 |

|

RU2164175C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-07-23—Публикация

1983-01-11—Подача