Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств ЭВМ и цифровых систем контроля.

Известно-устройство, содержащее три счетчика, генератор импульсов, триггеры и элементы И,ИЛИ, позволяю-щие определять разность двух чисел с сохранением информации об операндах i .

Недостатком этого устройства является низкое быстродействие. .

Наиболее близким к изобретению является устройство для сложениявычитания двоичных чисел, содержащее два ре гистра, триггер, шесть элементов И, два элемента ИЛИ и два элемента задержки 2.

Недостатками такого устройства являются его функциональная ограниченность, состоящая в том, что оно не обеспечивает сохранения значения второго операнда после выполнения операции сложения или вычитания, а также низкое быстродействие.

Цель изобретения - повыиения быстродейстция и расширение функциональных возможностей устройства за счет возможности сохранения значения второго операнда при выполнении операции.

Указанная цель достигается тем, что в устройство, содержоидещее два регистра, триггер, четыре элемента И и элемент ИЛИ, причем прямой выход триггера соединен с первым входом первого элемента И, второй вход кото рого соединен с выхрдом первого ре10гистра, введены четыре сумматора по модулю два, при этом первый и второй входы первого сумматора по модулю два соединены соответственно с выходом первого регистра и прямым выходом

15 триггера, выход первого сумматора по модулю два соединен с первым входом второго сумматора по модулю два и с первым входом второго элемента И, второй вход которого соединен с вы20ходом третьего cyNMaTopa по модулю два, выход первого элемента И соединен с первым входом элемента ИЛИ, выход второго элемента И соединен со вторым входом элемента ИЛИ, выход

25 которого соединен с первым входом четвертого сумматора по.модулю два, второй вход которого соединен с прямым выходом триггера, выход четвертого сумматора по модулю два соединен

30 с первым входом третьего элемента И,

выход которого соединен со счетным входом триггера, первый вход третьег сумматора по модулю два соединен с шиной управления устройства, вторые входы-второго и третьего сумматоров по модулю два соединены с выходом второго регистра, вход которого подключен к выходу четвертого элемента И, вход первого регистра сего выходом, выход второго сумматора по модулю два подключен к первому входу четвертого элемента И, вторые входы третьего и четвертого элементов И соединены с шиной синхронизаци устройства, а установочный вход триггера соединен с шиной сброса устройства.

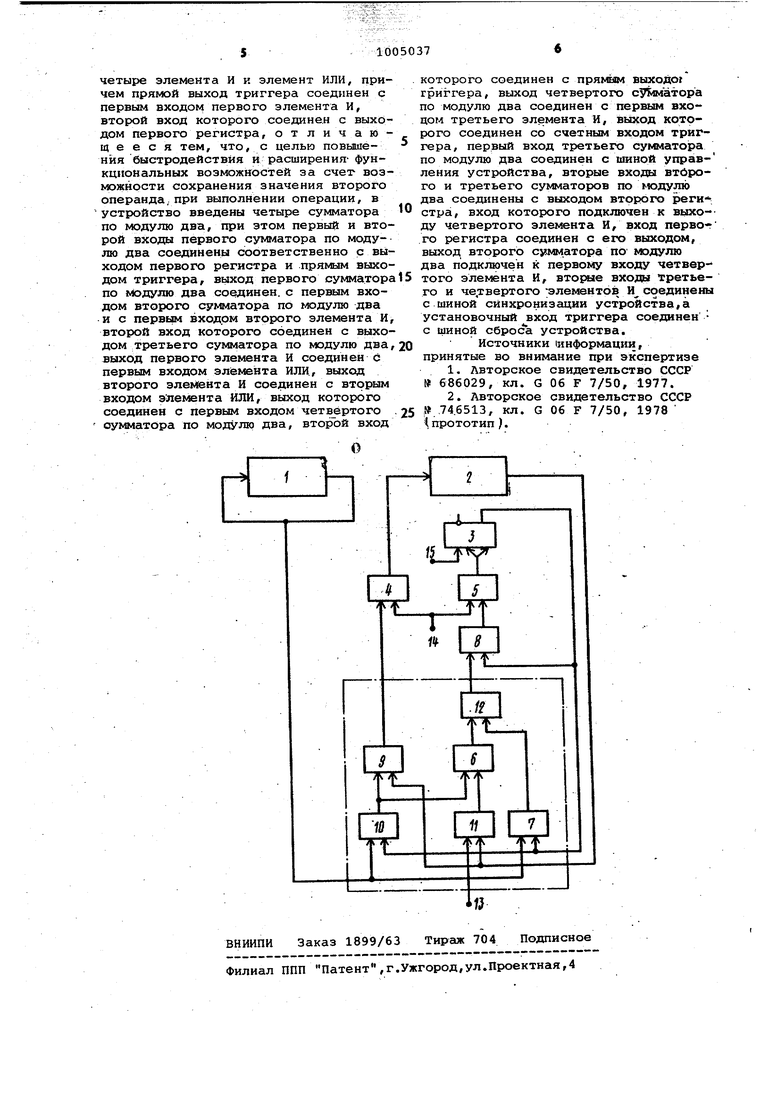

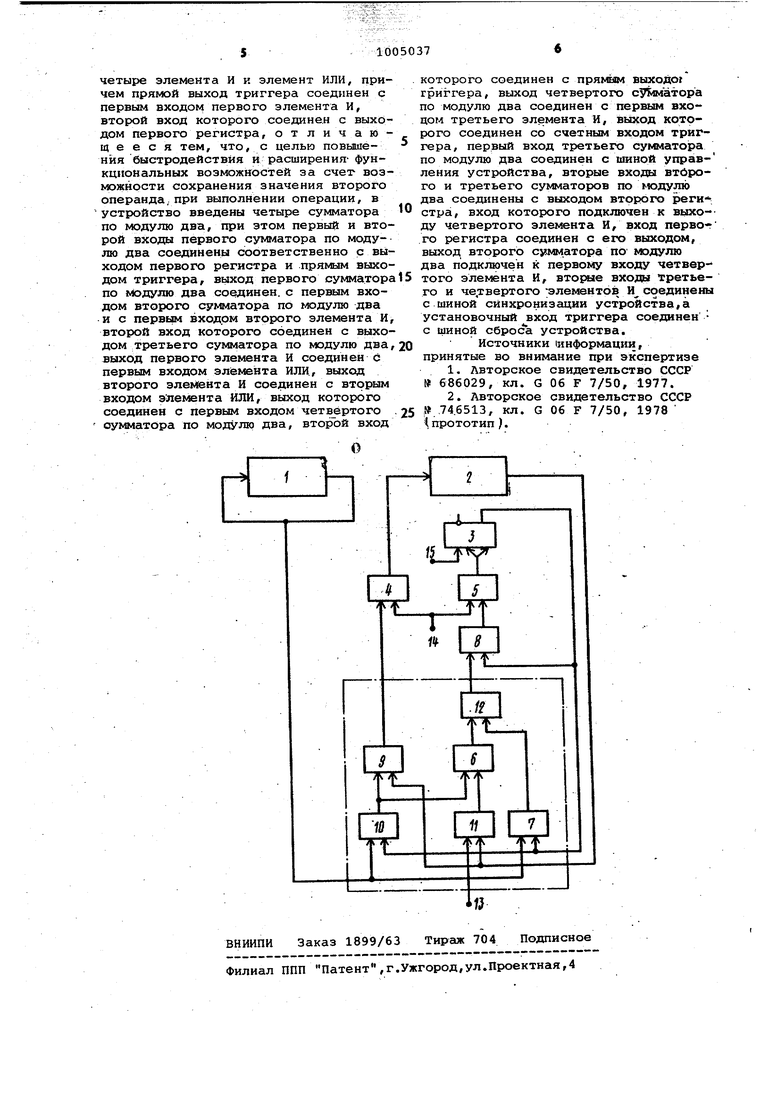

На чертеже изображена структурная схема устройства для сложения-вычитания.

Устройство содержит два регистра 1 и 2, триггер 3, элементы И 4-7, сумматоры 8-11 по модулю два, элемент ИЛИ 12, шину 13 управления, шину 14 синхронизации и шину 15 сброnav

Устройство работает следующим образом.

При операции Сложение в регистр ры 1 и 2 по синхронизирую1цим импульсак тактовой частоты последовательно начиная с младших разрядов, записываются двоичные коды слагаемых X (Х-,

Х2, ..,, Х) и У ;(Х|;/2 пЬ при операции Вычитание в регистр 1 записываются двоичный код вычитаемого X (К, X2f ...f Xr,)f а в регистр 2 - уменьшаемого У (.У-,, У2, ...,УП. При этом на шину 14 синхронизации подается запирающий потенциал, а на мину 15 - импульс Сброс, который устанавливает триггер 3 в исходное нулевое состояние.

Рассмотрим работу устройства в режиме Вычитание, при котором на управляюадую шину 13 подается потенциал логическая единица. Двоичные коды вычитаемого и уменьшаемого считываются синхронно последовательно, начиная с младших разрядов, и поступают на вход комбинационного сумматора-вычитателя, образованного элементами б, 7, 9 - 11 и 12. На вход комбинацион- кого сумматора поступает также с единичного вьахода триггера 3 значение заема, образовавшегося в предыдущем тактё считывания.

При этом на каждом -м такте считывания на выходе сумматора 9 формируется значение разности Р , а на выходе элемента ИЛИ 12 - значение заема 2.

Синхронно со считывающими импуль:сами по шине 14 на входы элементов И 4 и 5 поступают импульсы, передний фронт которых задержан относительно переднего фронта считывающих

импульсов на время установления пере ходных процессов в комбинационном сумматоре-вычитателе, вызванных очередным поступлением считываемых кодов.

При этом на каждом i-м такте считывания значение разности Р с выхода элемента И 4 поступает на вход регистра 2, а в триггере 3 через элемент И 5 записывается значение заема.

Операция записи или стирания единицы заема в триггере 3 реализуется на элементе И 4. При несовпадении (совпадении) значения заема i-ro такта и значения, записанного в триггере 3. на 4i-l -м такте, на выходе элемента И 4 формируется сигнал логическая единица (логический , который поступает на вход элемента И 5. В зависимости от сигнала на выходе элемента 4 синхроимпульс либо проходит через элемент И 5 на счетный вход триггера 3 и перебрасывает его, либо элемент И 5 запирается и триггер сохраняет свое состояние. Процесс вычисления заканчивается после считывания старших разрядов уменье шаемого и вычитаемого. Если уменьшаемое меньше вычитаемого, разность получается в дополнитнльном коде.

Операция Сложение отличается от операции Вычитание только подачей на управляющую шину 13 потенциала логический нуль.

Как при сложении, так и при вычитании записанный в регистре 1 код числа сохраняется.

Данное устройство выгодно отличается от прототипа, так как позволяет производить операции сложения и вычитания двух чисел, представленных в прямых кодах с сохранением информации об одном из слагаемых или вычитаемом после операции Сложение или Вычитание. Эта особенность расширяет функциональные возможности устройства и позволяет эффективно использовать его при многократных вычислениях суммы или разности двух чисел в случаях, когда один из операндов не меняется, например, в устройствах, выполняющих операции Умножение или Деление методом многократного суммирования или вычитания, в интеграторах систем сбора и обработки информаг ции и для других целей, где требуется производить повторные вычисления.

Кроме того, по-сравнению с прототипом, данное устройство обладает повышенным быстродействием, так как операции и сложения, .и вычитания осуществляются за один цикл.

формула изобретения

Устройство для сложения-вычитания, содержащее два регистра, триггер.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Арифметико-логическое устройство связного процессора | 1978 |

|

SU765808A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

Авторы

Даты

1983-03-15—Публикация

1981-06-19—Подача