со

ю ел ел

Изобретение относится к вычисли- тельной технике и может быть использовано в быстродействующих арифметических устройствах для выполнения операции деления.

Целью изобретения является уменьшение аппаратурных затрат.

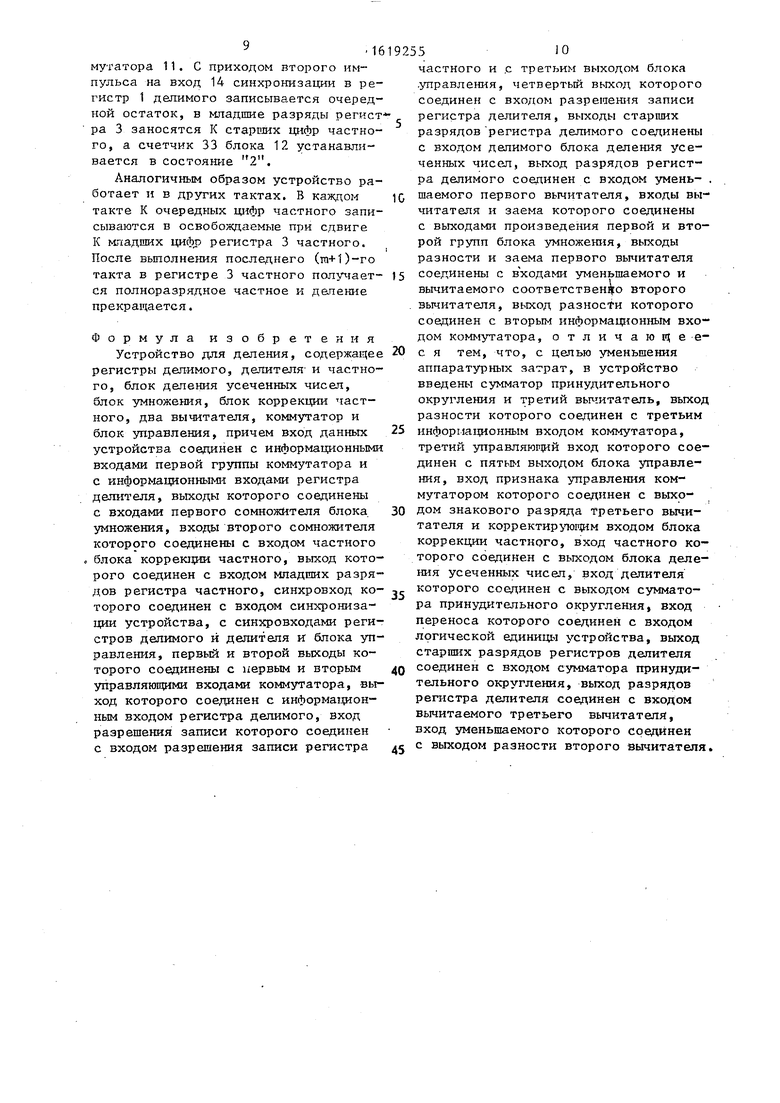

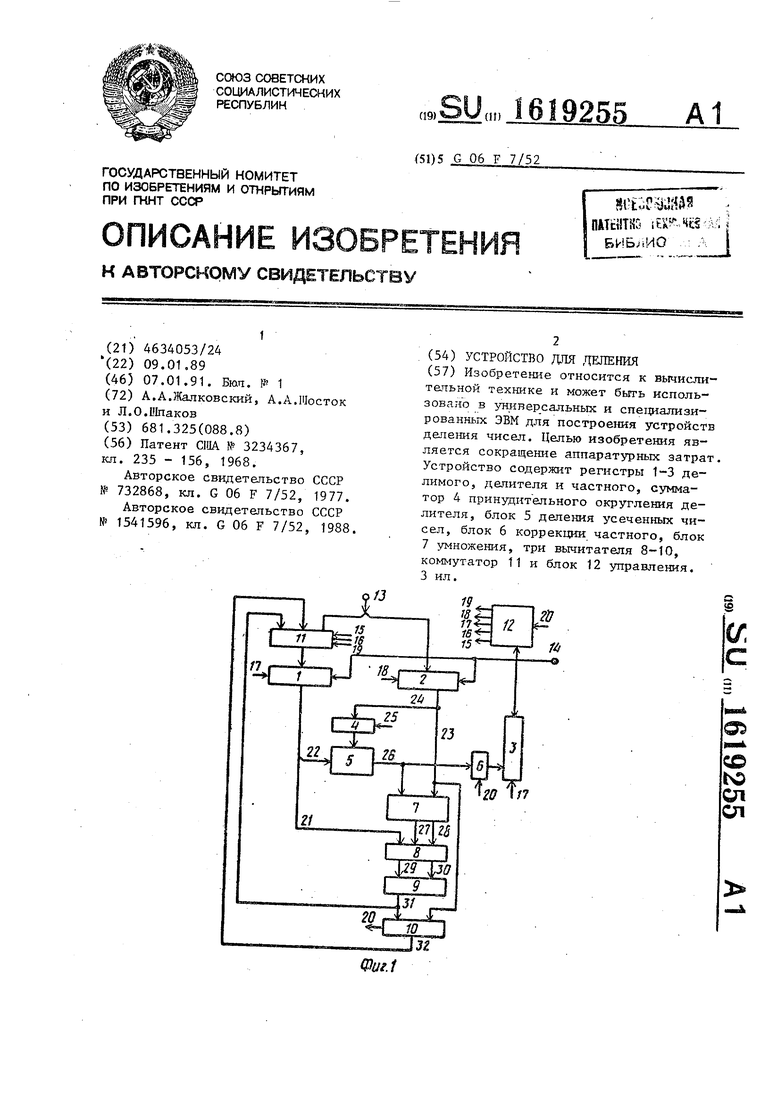

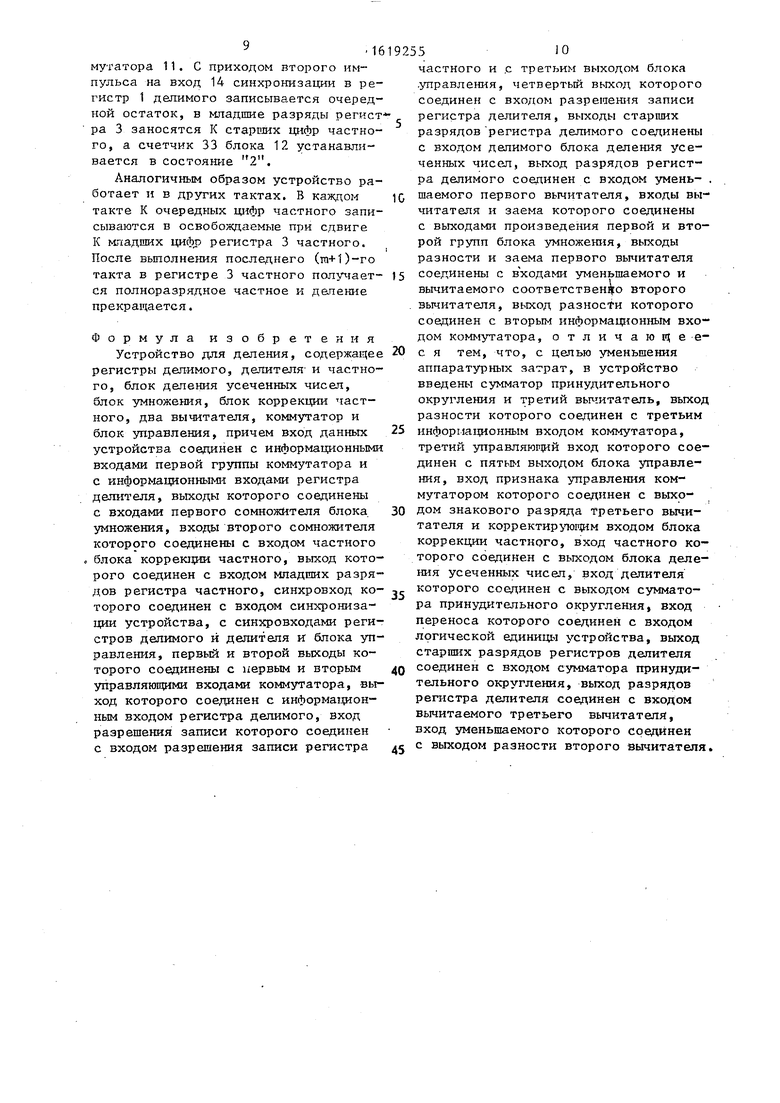

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - струк- турная схема блока управления; на фиг . 3 график-схема алгоритма работы блока управления.

Устройство для деления (фиг. 1) содержит регистры 1-3 соответст- зетчю делимого, делителя и частного, сумматор 4 принудительного округления .делителя, блок 5 деления усеченных чисел, блок б коррекции частного, блок 7 умножения, вычитатели 8-10 с первого по третий соответственно, коммутатор 11 и блок 12 управления, вход 13 данных устройства, вход 14 синхронизации устройства, выходы 15- 19 с первого по пятый блока 12 управ™ лепия соответственно, выход 20 знакового разряда третьего вычитателя 10, выходы 21 разрядов регистра 1 делимого, выходы 22 старших разрядов регистра 1 делимого, выходы 23 разрядов регистра 2 делителя, выходы 24 старших разрядов регистра 2 делителя, вход 25 логической единицы устройства, выходы 26 блока 5 деления усеченных чисел, выходы 27 первой и 28 вто- рой групп блока 7 умножения, выходы 29 разности и выходы 30 заема первого вычитателя 89 выходы 31 второго вычитателя 9} выходы 32 третьего вычитателя 10.

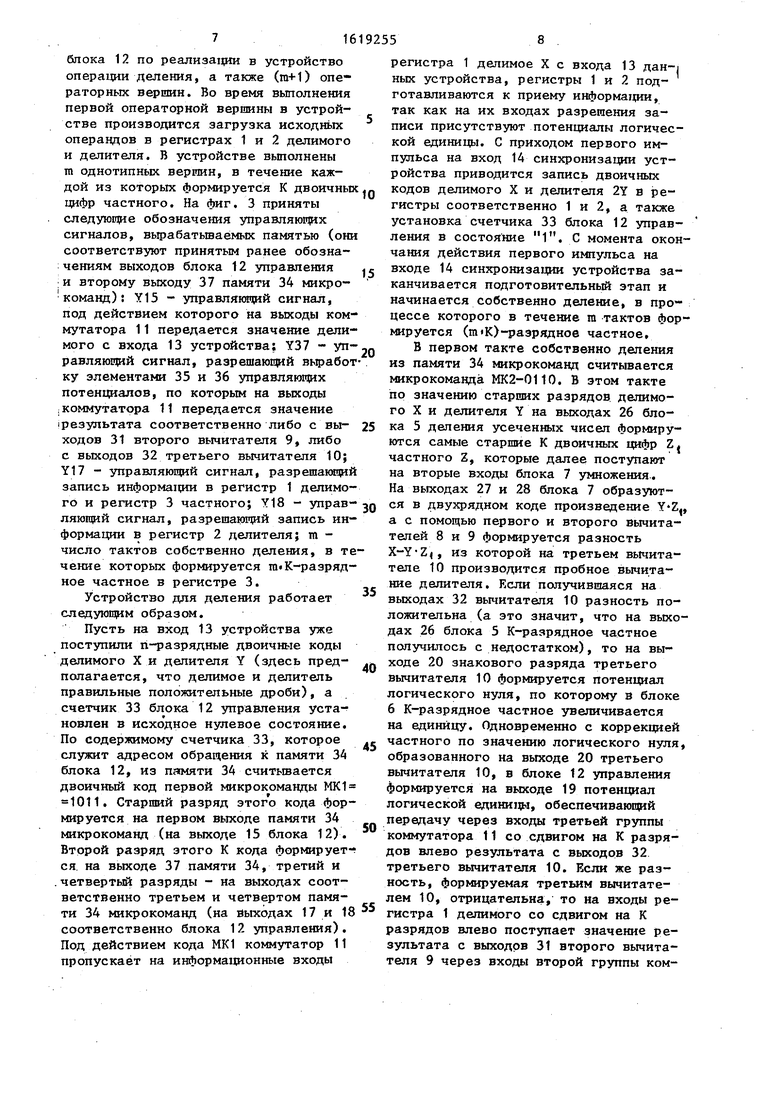

Блок 12 управления (фиг. 2) содержит счетчик 333 память 34 микрокоманд элемент И 35Э. элемент запрета 36, второй выход 37 памяти микрокоманд.

Регистры 1 и 2 делимого и делителя соответственно предназначены для временного хранения двоичных кодов делимого (остатков) и делителя. Регистр 1 делимого (п-М)-разрядный, из которых один разряд расположен слева от запя- той и п разрядов - справа от запятой Регистр 2 делителя содержит п разрядов, которые все расположены справа от запятой. В первом такте деления в эти регистры загружаются двоичные коды делимого и делителя, которые являются правильными положительными дробями. Регистры могут быть реали- зованы на основе двухтактных синхронных DV-триггеров. Запись информации в регистры производится по синхроимпульсу при наличии разрешающего потенциала на их V-входах.

Регистр 3 частного предназначен для хранения цифр частного. Он выполнен на основе двухтактных синхронных DV-триггеров, соединенных между собой цепями однотактного сдвига на К разрядов.

Сумматор 4 принудительного округления делителя и блок 5 деления усеченных (малоразрядных) чисел непосредственно участвуют в формировании в устройстве очередных К двоичных цифр частного. В блоке 5 осуществляется деление значения определенного числа старших разрядов делимого на увеличенное на. единицу младшего разряда в сумматоре 4 значение определенного числа старших разрядов делителя. К цифр частного на выходах 26 блока 5 формируются либо точно, либо с недостатком на единицу младшего разряда,

Число старших разрядов операндов, обрабатываемых в сумматоре 4 и блоке 5 деления усеченных чисел, определяется в зависимости от диапазонов значений делимого и делителя. В данном устройстве предполагается, что делимое X и делитель Y есть нормализованные положительные двоичные дроби. В ходе деления в роли делимого выступают промежуточные остатки и возможно нарушение нормализации делимого как влево, так и вправо. В общем случае делимое X в устройстве может изменяться в пределах О .

При принятых допущениях для получения на выходах 26 блока 5 деления усеченных чисел К двоичных цифр частного с точностью до единицы-их младшего разряда достаточно обрабатывать (К+2) старших разрядов делимого X (один разряд слева от запятой и (К+1) разряд справа от запятой и (К+2) старших разрядов делителя Y (все разряды находятся справа от запятой). При этом, значение К-разрядного частного, получаемого на выходе 26 блока 5, может быть либо равно значению старших К разрядов частного, получаемого при делении n-разрядных чисел, либо меньше его на единицу младшего разряда с весом 2-(К-1),

Блок -5 может быть реализован самыми различными способами. При малых значениях К блок 5 деления усеченных

5161

чисел может быть разработан по соответствующей таблице истинности либо в виде быстродействующего логического шифратора, либо в виде быстрой поисковой таблицы, реализованной на ПЗУ. В этом случае целеобразна совместная реализация блока 5 и сумматора 4. При больших значениях К более предпочтительной является реализация блока 5 в виде быстродействующей одно- тактной матричной схемы деления, использующей алгоритмы с восстановлением или без восстановления остатков и все известные средства ускоренной реализации этих алгоритмов.

В блоке 6 осуществляется коррекция частного путем прибавления единицы в его младший разряд в случае, если значение знакового разряда третьего вычитателя 10 равно логическому нулю (предполагается, что в этом случае разность на выходе вычитателя 10 положительная). Блок 6 может быть реализован на основе К-разрядного сумматора и инвертора, вход которого является корректирующим входом блока 6.

В блоке 7 осуществляется перемножение п-разрядного делителя, хранимого в регистре 2 и поступающего на первую группу входов блока 7 с выхо- дов 23 регистра 2, и К-разрядного частного, сформированного на выходах 26 блока 5 и поступающего на вторую группу входов блока 7. На выходах 27 и 28 первой и второй групп блока 7 образуется произведение в двухрядном коде (в виде двух чисел).

Блок 7 умножения комбинационного типа и может быть реализован, например, в виде совокупности из п/К К-разрядных двоичных умножителей.

С помощью первого вычитателя 8 производится вычитание из содержимого регистра 1 делимого произведения, сформированного на выходах 27 и 28 блока 7 умножения в двухрядном коде. Результат вычитания образуется на выходах 29 и 30 разности и заема первого вычитателя 8 в двухрядном коде. Первый вычитатель 8 является вычита- телем без распространения заема и может быть реализован на одноразрядных двоичных вычитателях.

Второй вычитатель 9 производит вычитание из значения разности, сформированной на выходах 29 первого вычитателя 9, значения заема, образован2556

ного на выходах 30 первого вычитателя 8. Второй вычитатель 9 комбинацион-, ного типа с ускоренным распространением заема. Он может быть заменен быстродействующим сумматором, если информацию, поступающую на его вход вычитаемого, проинвертировать, а на вход переноса сумматора подать сиг-

Q нал логической единицы.

Третий вычитатель 10 осуществляет пробное вычитание из значения результата, полученного на выходах 31 второго вычитателя 9, значения делителя,

5 поступающего с выходов 23 регистра 2 делителя. Если сформированная разность положительна, то на выходе 20 знакового разряда вычитателя 10 формируется логический ноль.

0 С помощью коммутатора 11 осуществляется передача значения делимого на информационные входы регистра 1 с входа 13 устройства, когда на первом выходе 15 блока 12 управления форми-

5 руется сигнал логической единицы,

либо результата, образованного на выходах 31 второго вычитателя 9, когда на втором выходе 16 блока 12 формируется сигнал логической единицы,

0 либо результата, образованного на выходах 32 третьего вычитателя 10, когда на пятом выходе 19 блока 12 устанавливается сигнал логической единицы. Коммутатор 11 может быть реализован на элементах 2И-ЗИЛИ.

Блок 12 управления координирует работу узлов и блоков устройства при выполнении на нем операции деления двух чисел. На фиг. 2 приведена реаQ лизация блока 12 управления на основе счетчика 33, памяти 34 микрокоманд, элемента И 35 и элемента 36 запрета. Счетчик 33 накапливающего типа и предназначен для естественной адресации

с микрокоманд. Вход счета счетчика соединен с входом 14 синхронизации устройства. В качестве памяти 34 микрокоманд может, быть применена быстродействующая постоянная память емкосQ тью е«4, где е - число тактов работы устройства. В самом начале работы устройства счетчик 33 устанавливается в некоторое исходное состояние, например сбрасывается в нуль (фиг. 2,

$ цепь установки счетчика 33 в исходное состояние не показана).

График-схема (фиг. 3) алгоритма работы блока 12 управления содержит вершины начала и окончания работы

5

71619255

блока 12 по реализации в устройство операции деления, а также (га+1) операторных вершин. Во время выполнения первой операторной вершины в устройстве производится загрузка исходных операндов в регистрах 1 и 2 делимого и делителя. В устройстве выполнены m однотипных вершин, в течение каж

8

регистра 1 делимое X с входа 13 дан-i ных устройства, регистры 1 и 2 подготавливаются к приему информации, так как на их входах разрешения записи присутствуют потенциалы логической единицы. С приходом первого импульса на вход 14 синхронизации устройства приводится запись двоичных

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Устройство для деления | 1989 |

|

SU1709301A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

| Устройство для деления | 1990 |

|

SU1803913A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных ЭВМ для построения устройств деления чисел. Целью изобретения является сокращение аппаратурных затрат. Устройство содержит регистры 1-3 делимого, делителя и частного, сумматор 4 принудительного округления делителя, блок 5 деления усеченных чисел, блок 6 коррекции частного, блок 7 умножения, три вычитателя 8-10, коммутатор 11 и блок 12 управления. 3 ил.

дои из которых формируется К двоичных,,, кодов делимого X и делителя 2Y в рецифр частного. На фиг. 3 приняты следующие обозначения управляющих сигналов, вырабатываемых памятью (они соответствуют принятым ранее обозначениям выходов блока 12 управления j- и второму выходу 37 памяти 34 микро- команд): Y15 - управляющий сигнал, под действием которого на выходы коммутатора 11 передается значение делимого с входа 13 устройства; Y37 - Vn-jg равляющий сигнал, разрешающий выработку элементами 35 и 36 управляющих потенциалов, по которым на выходы .коммутатора 11 передается значение (результата соответственно либо с вы- 25 ходов 31 второго вычитателя 9, либо с выходов 32 третьего вычитателя 10; Y17 - управляющий сигнал, разрешающий запись информации в регистр 1 делимогистры соответственно 1 и 2, а также установка счетчика 33 блока 12 управления в состояние 1. С момента окон чания действия первого импульса на входе 14 синхронизации устройства заканчивается подготовительный этап и начинается собственно деление, в процессе которого в течение m тактов фор мируется (т«К)-раэрядное частное,

В первом такте собственно деления из памяти 34 микрокоманд считывается микрокоманда МК2-0110. В этом такте по значению старших разрядов делимого X и делителя Y на выходах 26 блока 5 деления усеченных чисел формируются самые старшие К двоичных цифр Zj частного Z, которые далее поступают на вторые входы блока 7 умножения. На выходах 27 и 28 блока 7 образуютго и регистр 3 частного; Y18 - управ- 30 ся в двухрядном коде произведение ,

35

40

ляющий сигнал, разрешающий запись информации в регистр 2 делителя; т - число тактов собственно деления, в течение которых формируется га К-раэряд- ное частное в регистре 3.

Устройство для деления работает следующим образом.

Пусть на вход 13 устройства уже поступили n-разрядные двоичные коды делимого X и делителя Y (здесь предполагается, что делимое и делитель правильные положительные дроби), а счетчик 33 блока 12 управления установлен в исходное нулевое состояние. По содержимому счетчика 33, которое служит адресом обращения к памяти 34 блока 12, из памяти 34 считывается двоичный код первой микрокоманды МК1 1011. Старший разряд этого кода формируется на первом выходе памяти 34 микрокоманд (на выходе 15 блока 12). Второй разряд этого К кода формируется на выходе 37 памяти 34, третий и . четвертый разряды - на выходах соответственно третьем и четвертом памяти 34 микрокоманд (на выходах 17 и 18 соответственно блока 12 управления). Под действием кода МК1 коммутатор 11 пропускает на информационные входы

45

50

а с помощью первого и второго вычита- телей 8 и 9 формируется разность X-Y Zi, из которой на третьем вычита- теле 10 производится пробное вычитание делителя. Если получившаяся на выходах 32 вычитателя 10 разность положительна (а это значит, что на выходах 26 блока 5 К-разрядное частное получилось с недостатком), то на выходе 20 знакового разряда третьего вычитателя 10 формируется потенциал логического нуля, по которому в блоке 6 К-разрядное частное увеличивается на единицу. Одновременно с коррекцией частного по значению логического нуля, образованного на выходе 20 третьего вычитателя 10, в блоке 12 управления формируется на выходе 19 потенциал логической единицы, обеспечивающий передачу через входы третьей группы коммутатора 11 со сдвигом на К разрядов влево результата с выходов 32 третьего вычитателя 10. Если же разность, формируемая третьим вычитате- лем 10, отрицательна, то на входы регистра 1 делимого со сдвигом на К разрядов влево поступает значение результата с выходов 31 второго вычитателя 9 через входы второй группы комгистры соответственно 1 и 2, а также установка счетчика 33 блока 12 управления в состояние 1. С момента окончания действия первого импульса на входе 14 синхронизации устройства заканчивается подготовительный этап и начинается собственно деление, в процессе которого в течение m тактов формируется (т«К)-раэрядное частное,

В первом такте собственно деления из памяти 34 микрокоманд считывается микрокоманда МК2-0110. В этом такте по значению старших разрядов делимого X и делителя Y на выходах 26 блока 5 деления усеченных чисел формируются самые старшие К двоичных цифр Zj частного Z, которые далее поступают на вторые входы блока 7 умножения. На выходах 27 и 28 блока 7 образуют5

0

5

0

а с помощью первого и второго вычита- телей 8 и 9 формируется разность X-Y Zi, из которой на третьем вычита- теле 10 производится пробное вычитание делителя. Если получившаяся на выходах 32 вычитателя 10 разность положительна (а это значит, что на выходах 26 блока 5 К-разрядное частное получилось с недостатком), то на выходе 20 знакового разряда третьего вычитателя 10 формируется потенциал логического нуля, по которому в блоке 6 К-разрядное частное увеличивается на единицу. Одновременно с коррекцией частного по значению логического нуля, образованного на выходе 20 третьего вычитателя 10, в блоке 12 управления формируется на выходе 19 потенциал логической единицы, обеспечивающий передачу через входы третьей группы коммутатора 11 со сдвигом на К разрядов влево результата с выходов 32 третьего вычитателя 10. Если же разность, формируемая третьим вычитате- лем 10, отрицательна, то на входы регистра 1 делимого со сдвигом на К разрядов влево поступает значение результата с выходов 31 второго вычитателя 9 через входы второй группы коммугатора 11. С приходом второго импульса на вход 14 синхронизации в регистр 1 делимого записывается очередной остаток, в младшие разряды тэегист ра 3 заносятся К старших цифр частного, а счетчик 33 блока 12 устанавливается в состояние 2.

Аналогичным образом устройство работает и в других тактах. В каждом такте К очередных цифр частного записываются в освобождаемые при сдвиге К младших цифр регистра 3 частного. После выполнения последнего (га+1)-го такта в регистре 3 частного получается полноразрядное частное и деление прекращается.

Формула изобретения

Устройство для деления, содержащее регистры делимого, делителя и частного, блок деления усеченных чисел, блок умножения, блок коррекции частного, два вычитателя, коммутатор и блок управления, причем вход данных устройства соединен с информационными входами первой группы коммутатора и с информационными входами регистра делителя, выходы которого соединены с входами первого сомножителя блока умножения, входы второго сомножителя которого соединены с входом частного блока коррекции частного, выход которого соединен с входом младших разрядов регистра частного, синхровход ко- 5 которого соединен с выходом суммато- торого соединен с входом синхрониза-Ра принудительного округления, вход

ции устройства, с синхровходами реги- переноса которого соединен с входом стров делимого и делителя и блока уп- логической единицы устройства, выход

равления, первый и второй выходы которого соединены с первым и вторым управляющими входами коммутатора, выход которого соединен с информационным входом регистра делимого, вход разрешения записи которого соединен с входом разрешения записи регистра

9255Ю

частного и с третьим выходом блока управления, четвертый выход которого соединен с входом разрешения записи регистра делителя, выходы старших разрядов регистра делимого соединены с входом делимого блока деления усеченных чисел, выход разрядов регистра делимого соединен с входом умень- .

IQ шаемого первого вычитателя, входы вычитателя и заема которого соединены с выходами произведения первой и второй групп блока умножения, выходы разности и заема первого вычитателя

15 соединены с входами уменьшаемого и вычитаемого соответственно второго зычитателя, выход разности которого соединен с вторым информационным входом коммутатора, отличаю щее20 с я тем, что, с целью уменьшения аппаратурных затрат, в устройство введены сумматор принудительного округления и третий вычитатель, выход разности которого соединен с третьим

25 информационным входом коммутатора,

третий управляющий вход которого соединен с пятым выходом блока управления, вход признака управления коммутатором которого соединен с выхо30 дом знакового разряда третьего вычитателя и корректирующим входом блока коррекции частнрго, вход частного которого соединен с выходом блока деления усеченных чисел, вход делителя

старших разрядов регистров делителя соединен с входом сумматора принудительного округления, выход разрядов регистра делителя соединен с входом вычитаемого третьего вычитателя, вход уменьшаемого которого соединен с выходом разности второго вычитателя.

(начало У У15,УП,УЮ

г

туп

I

/77#/ ф

У17,У37

С Коне ц У Щиг.З

Фиг. 2

т

| Патент США № 3234367, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Устройство для деления п-раздельных чисел | 1977 |

|

SU732868A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-07—Публикация

1989-01-09—Подача