Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1989 |

|

SU1709301A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления чисел | 1985 |

|

SU1429109A1 |

| Устройство для деления чисел | 1985 |

|

SU1247862A1 |

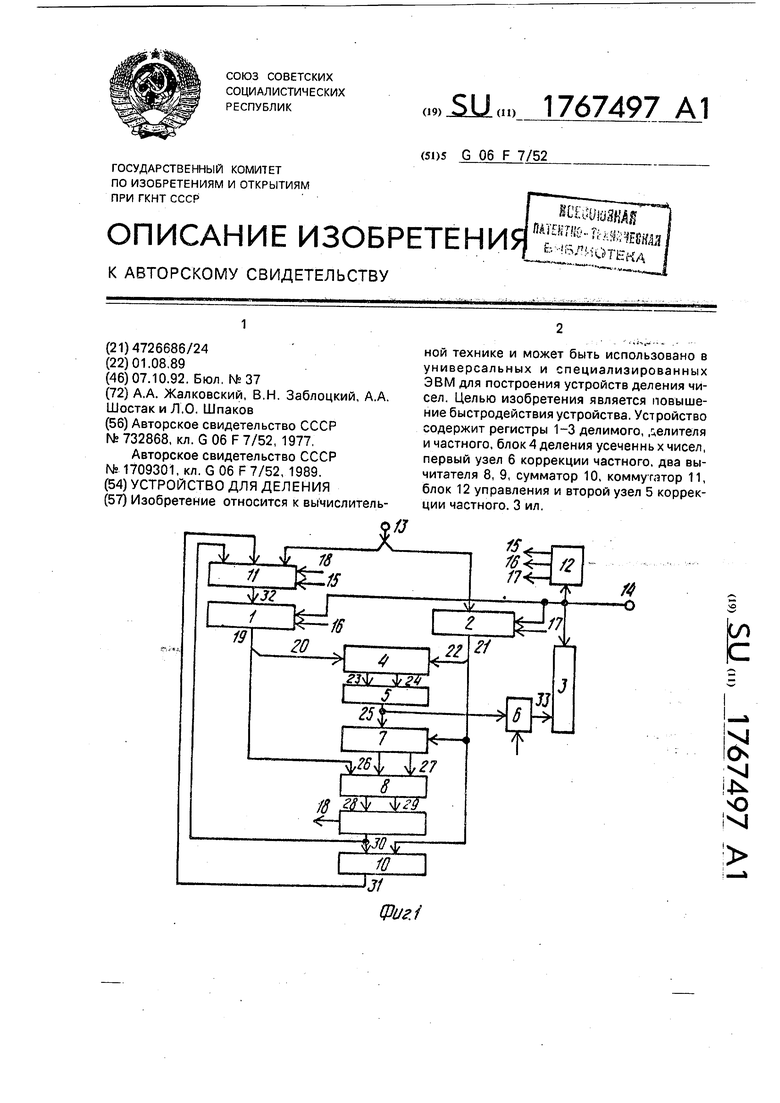

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных ЭВМ для построения устройств деления чисел. Целью изобретения является повышение быстродействия устройства. Устройство содержит регистры 1-3 делимого, делителя и частного, блок 4 деления усеченнь х чисел, первый узел 6 коррекции частного, два вы- читателя 8, 9, сумматор 10, коммутатор 11, блок 12 управления и второй узел 5 коррекции частного. 3 ил.

S

.2

О ixj

ЦЗиг.1

Изобретение относится к области вычислительной техники и может быть использовано в быстродействующих арифметических устройствах для выполнения операции деления.

Целью изобретения является повышение быстродействия устройства.

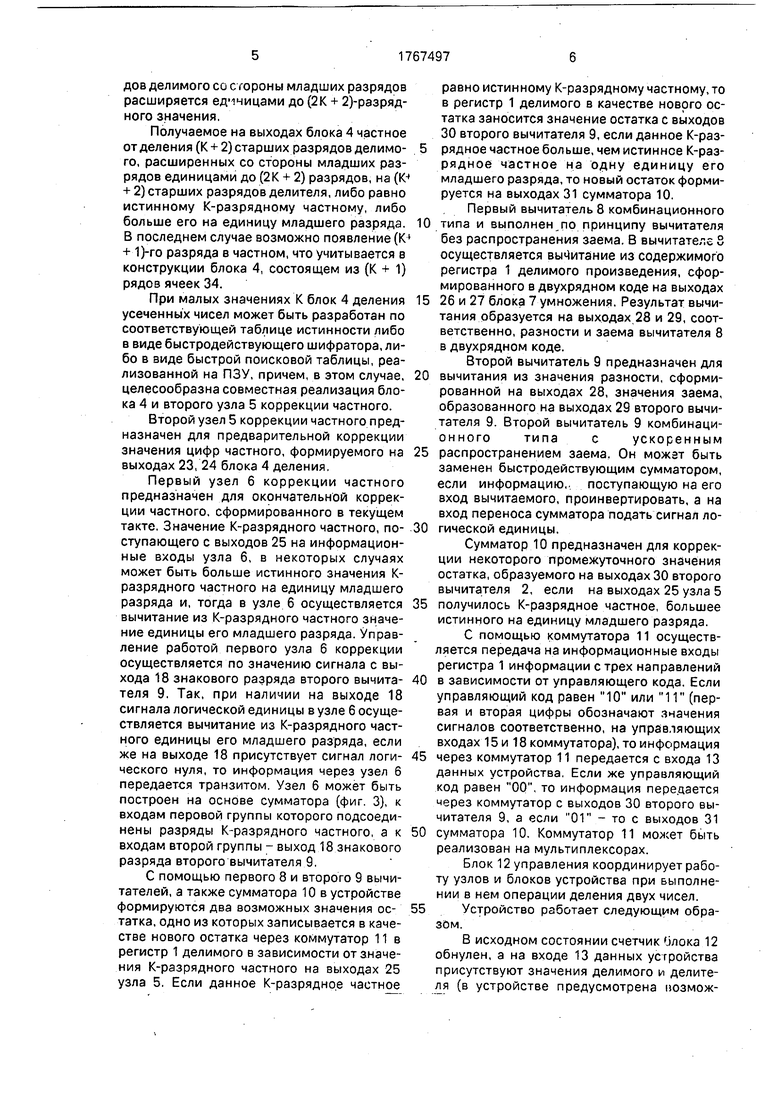

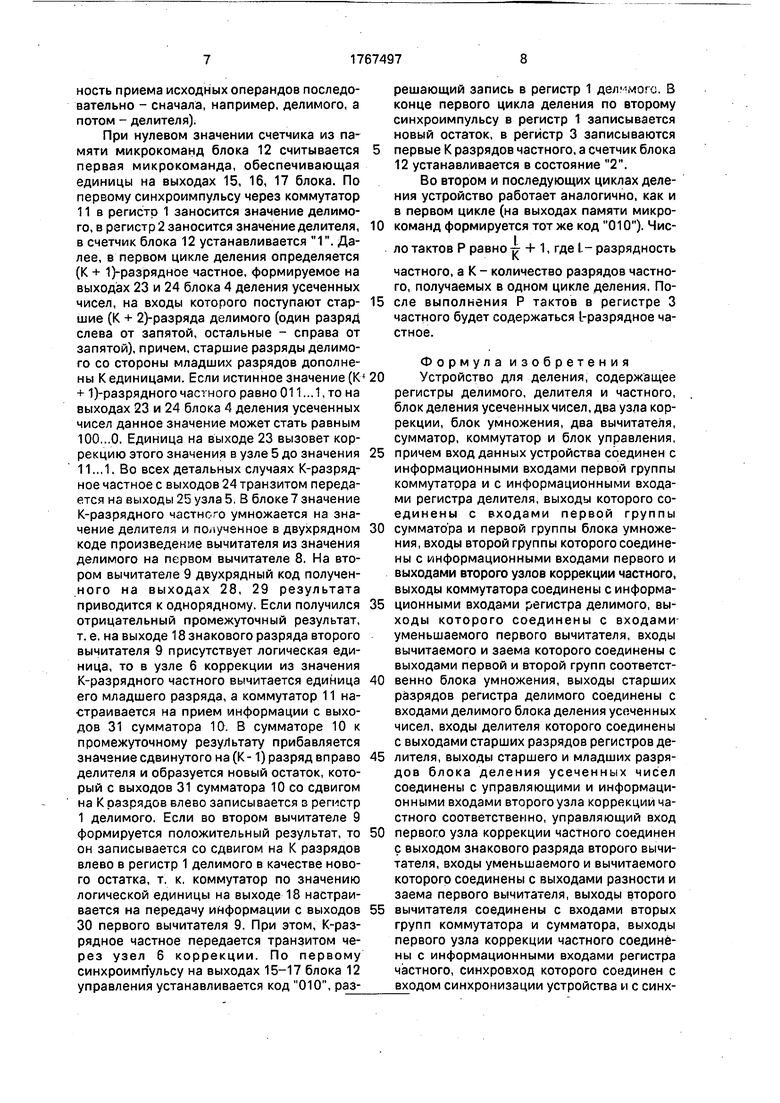

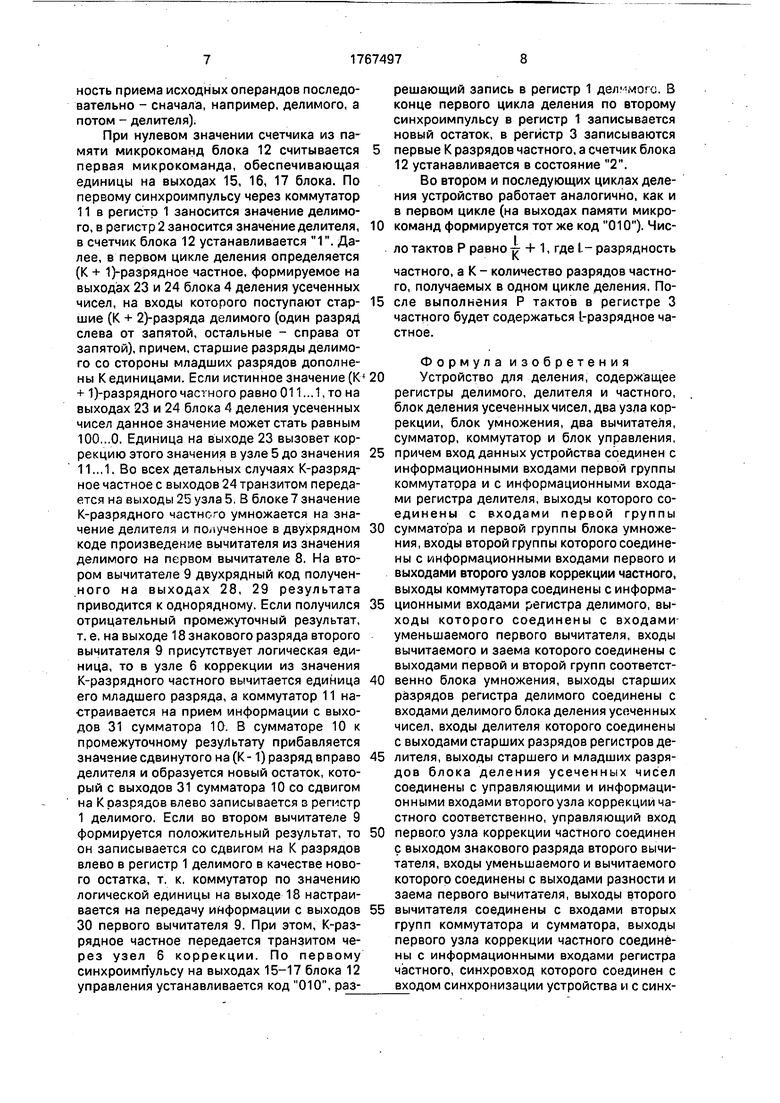

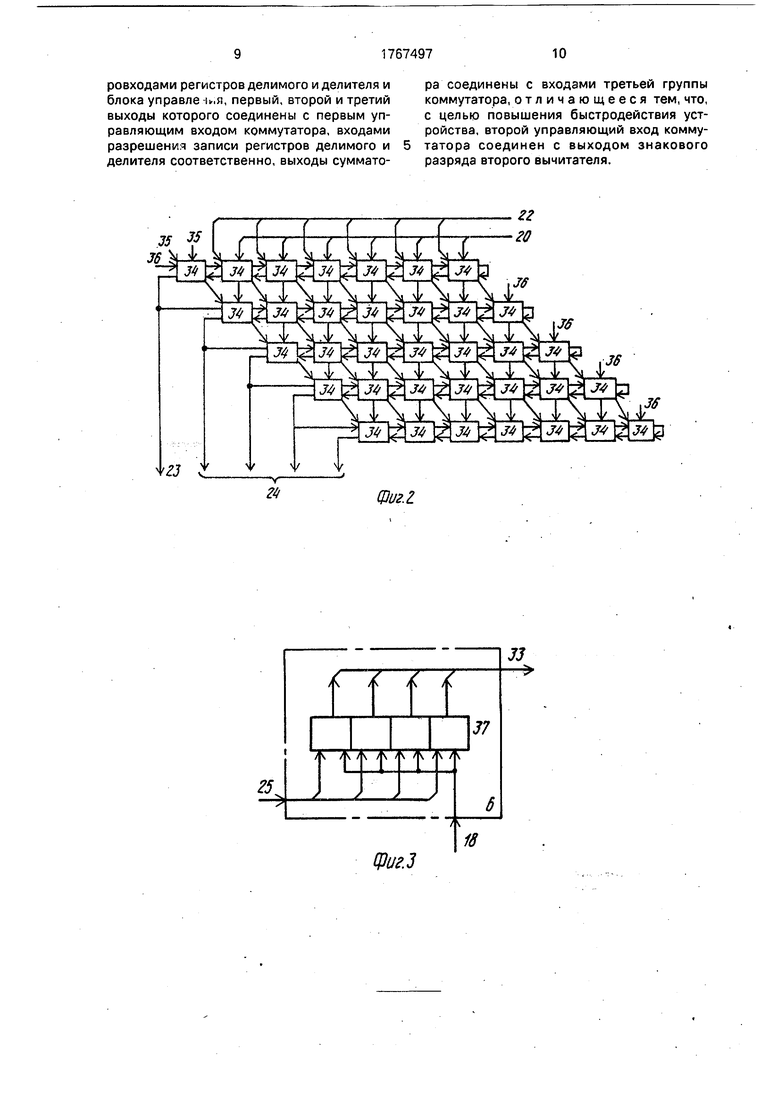

На фиг. 1 приведена структурная схема устройства; на фиг.2 - для К 4 показана реализации блока деления усеченных чисел в виде итеративной сети; на фиг. 3 - функциональная схема первого узла коррекции частного.

Устройство для деления содержит (фиг. 1) регистры 1, 2, 3, соответственно, делимого, делителя и частного, блок 4 деления усеченных чисел, второй и первый узлы 5, 6 коррекции частного, блок 7 умножения, первый, второй вычитатели 8, 9, сумматор 10, коммутатор 11, блок 12 управления, вход 13 данных устройства, вход 14 синхронизации устройства, выходы 15-17 с первого по третий блока 12 управления, соответственно, выход 18 знакового разряда второго вычи- тателя 9, выходы 19 разрядов регистра 1 делимого, выходы 20 старших разрядов регистра 1 делимого, выходы 21 разрядов регистра 2 делителя, выходы 22 старших разрядов регистра 2 делителя, выход 23 старшего разряда блока 4 деления усеченных чисел, выходы 24 младших разрядов блока 4 деления усеченных чисел, выходы 25 второго узла 5 коррекции частного, выходы 26 первой и 27 второй групп блока 7 умножения, выходы 28 разности и 29 заема первого вычитателя 8, выходы 30 второго вычитателя 9, выходы 31 сумматора 10, выходы 32 коммутатора, выходы 33 первого узла 6 коррекции частного. Блок 4 деления усеченных чисел содержит (фиг. 2) матрицу ячеек 34, вход 35 логического нуля, вход 36 логической единицы.

Ячейка 34 содержит элемент сложения по модулю два и одноразрядный двоичный сумматор.

Второй узел 5 коррекции частного содержит группу из К двухвходовых элементов ИЛИ.

Первый узел 6 коррекции частного содержит К-разрядный двоичный сумматор 37.

Блок 12 управления содержит счетчик и память микрокоманд.

Рассмотрим функциональное назначение и реализацию основных узлов и блоков устройства для деления.

Регистры 1, 2 делимого и делителя, соответственно, предназначены для временного хранения двоичных кодов делимого (остатков) и делителя. Регистр 1 делимого

(п+1)-разрядный из которых один разряд расположен слева от запятой и п-разрядов - справа от запятой. Регистр 2 делителя содержит n-разрядов, которые все расположены справа от запятой. В начале деления в эти регистры загружаются двоичные коды делимого и делителя (делимое загружается в п младших разрядов регистра 1), которые являются правильными положительными

0 дробями. Регистры могут быть реализованы на основе двухтактных синхронных DV- триггеров. Запись информации в регистры производится по синхроимпульсу при наличии разрешающего потенциала на их V-BXO5 дах. V-входы всех триггеров регистра 1 делимого объединены и подключены к выходу 16, в V-входы всех триггеров регистра 2 делителя - к выходу 17 блока 12 управления. Регистр 3 частного предназначен для

0 хранения частного и реализован в виде регистра с возможностью однотактного сдвига на К-разрядов в сторону старших разрядов. Входы К его младших разрядов соединены с выходами 33 первого узла 6

5 коррекции частного. Он может быть построен на основе двухтактных синхронных D- триггеров, причем, выход 1-го триггера (1 1,

2, 3(f - К), где I- разрядность частного

(соединен с информационным входом (i +

0 К)-го триггера. Запись информации в регистр 3 производится по синхроимпульсу, поступающему с входа 14 синхронизации устройства.

Блок 4 деления усеченных чисел пред5 назначен для получения (К + 1)-разрядного частного от деления старших (К + 2) разрядов делимого, поступающих с выходов 20 регистра 1 и дополненных К единицами со стороны младших разрядов, и старших (К +

0 2) разрядов делителя, поступающих с выходов 22 регистра делителя. Блок 4 может быть построен самыми различными способами. При больших значениях К более предпочтительным является построение блока 4

5 в виде быстродействующего однотактного матричного делителя, использующего алгоритмы с восстановлением или без восстановления остатков и все известные средства ускоренной реализации этих алго0 ритмов. На фиг. 2 для К 4 изображен конкретный вариант реализации блока 4 в виде однотактного матричного делителя, представленного итеративной сетью.

На первый ряд ячеек 34 поступгют no(Kv

5 + 2) старших разрядов делимого и делителя с выходов 20, 22. На входе разрядов делимого самых младших ячеек 34 (см. фиг. 2, 3) с второго по пятый ряд матрицы поступает значение логической единицы с входа 36. Этим самым значение (К+ 2) старших разрядов делимого со с гороны младших разрядов расширяется единицами до (2К + 2)-разряд- ного значения.

Получаемое на выходах блока 4 частное отделения (К + 2) старших разрядов делимо- го, расширенных со стороны младших разрядов единицами до (2К + 2) разрядов, на (К+ 2) старших разрядов делителя, либо равно истинному К-разрядному частному, либо больше его на единицу младшего разряда. В последнем случае возможно появление (К + 1)-го разряда в частном, что учитывается в конструкции блока 4, состоящем из (К + 1) рядов ячеек 34.

При малых значениях К блок 4 деления усеченных чисел может быть разработан по соответствующей таблице истинности либо в виде быстродействующего шифратора, либо в виде быстрой поисковой таблицы, реализованной на ПЗУ, причем, в этом случае, целесообразна совместная реализация блока 4 и второго узла 5 коррекции частного.

Второй узел 5 коррекции частного предназначен для предварительной коррекции значения цифр частного, формируемого на выходах 23, 24 блока 4 деления,

Первый узел 6 коррекции частного предназначен для окончательной коррекции частного, сформированного в текущем такте. Значение К-разрядного частного, по- ступающего с выходов 25 на информационные входы узла 6, в некоторых случаях может быть больше истинного значения К- разрядного частного на единицу младшего разряда и, тогда в узле 6 осуществляется вычитание из К-разрядного частного значение единицы его младшего разряда. Управление работой первого узла 6 коррекции осуществляется по значению сигнала с выхода 18 знакового разряда второго вычита- теля 9. Так, при наличии на выходе 18 сигнала логической единицы в узле 6 осуществляется вычитание из К-разрядного частного единицы его младшего разряда, если же на выходе 18 присутствует сигнал логи- ческого нуля, то информация через узел 6 передается транзитом. Узел 6 может быть построен на основе сумматора (фиг. 3), к входам перовой группы которого подсоединены разряды К-разрядного частного, а к входам второй группы - выход 18 знакового разряда второго вычитателя 9.

С помощью первого 8 и второго 9 вычи- тателей, а также сумматора 10 в устройстве формируются два возможных значения ос- татка, одно из которых записывается в качестве нового остатка через коммутатор 11 в регистр 1 делимого в зависимости от значения К-разрядного частного на выходах 25 узла 5. Если данное К-разрядное частное

равно истинному К-разрядному частному, то в регистр 1 делимого в качестве нового остатка заносится значение остатка с выходов 30 второго вычитателя 9, если данное К-разрядное частное больше, чем истинное К-разрядное частное на одну единицу его младшего разряда, то новый остаток формируется на выходах 31 сумматора 10.

Первый вычитатель 8 комбинационного типа и выполнение принципу вычитателя без распространения заема. В вычитатег.с S осуществляется вычитание из содержимого регистра 1 делимого произведения, сформированного в двухрядном коде на выходах 26 и 27 блока 7 умножения. Результат вычитания образуется на выходах 28 и 29, соответственно, разности и заема вычитателя 8 в двухрядном коде.

Второй вычитатель 9 предназначен для вычитания из значения разности, сформированной на выходах 28, значения заема, образованного на выходах 29 второго вычитателя 9. Второй вычитатель 9 комбинационного типа с ускоренным распространением заема. Он можат быть заменен быстродействующим сумматором, если информацию,, поступающую на его вход вычитаемого, проинвертировать, а на вход переноса сумматора подать сигнал логической единицы.

Сумматор 10 предназначен для коррекции некоторого промежуточного значения остатка, образуемого на выходах 30 второго вычитателя 2, если на выходах 25 узла 5 получилось К-разрядное частное, большее истинного на единицу младшего разряда.

С помощью коммутатора 11 осуществляется передача на информационные входы регистра 1 информации стрех направлений в зависимости от управляющего кода. Если управляющий код равен 10 или 11 (первая и вторая цифры обозначают значения сигналов соответственно, на управляющих входах 15 и 18 коммутатора), то информация через коммутатор 11 передается с входа 13 данных устройства, Если же управляющий код равен 00, то информация передается через коммутатор с выходов 30 второго вычитателя 9, а если 01 - то с выходов 31 сумматора 10. Коммутатор 11 может быть реализован на мультиплексорах.

Блок 12 управления координирует работу узлов и блоков устройства при выполнении в нем операции деления двух чисел.

Устройство работает следующим образом.

В исходном состоянии счетчик Олока 12 обнулен, а на входе 13 данных устройства присутствуют значения делимого и делителя (в устройстве предусмотрена иозможность приема исходных операндов последовательно - сначала, например, делимого, а потом - делителя).

При нулевом значении счетчика из памяти микрокоманд блока 12 считывается первая микрокоманда, обеспечивающая единицы на выходах 15, 16, 17 блока. По первому синхроимпульсу через коммутатор 11 в регисто 1 заносится значение делимого, в регистр 2 заносится значение делителя, в счетчик блока 12 устанавливается 1. Далее, в первом цикле деления определяется (К + 1)-разрядное частное, формируемое на выходах 23 и 24 блока 4 деления усеченных чисел, на входы которого поступают стар- шие (К + 2)-разряда делимого (один разряд слева от запятой, остальные - справа от запятой), причем, старшие разряды делимого со стороны младших разрядов дополнены К единицами. Если истинное значение (К + 1)-разрядногочастного равно 011...1, то на выходах 23 и 24 блока 4 деления усеченных чисел данное значение может стать равным 100,..0. Единица на выходе 23 вызовет коррекцию этого значения в узле 5 до значения 11...1. Во всех детальных случаях К-разряд- ное частное с выходов 24 транзитом передается на выходы 25 узла 5. В блоке 7 значение К-разрядного частного умножается на значение делителя и полученное в двухрядном коде произведение вычитателя из значения делимого на первом вычитателе 8. На втором вычитателе 9 двухрядный код полученного на выходах 28, 29 результата приводится к однорядному. Если получился отрицательный промежуточный результат, т. е. на выходе 18 знакового разряда второго вычитателя 9 присутствует логическая единица, то в узле 6 коррекции из значения К-разрядного частного вычитается единица его младшего разряда, а коммутатор 11 настраивается на прием информации с выходов 31 сумматора 10. В сумматоре 10 к промежуточному результату прибавляется значение сдвинутого на (К-1) разряд вправо делителя и образуется новый остаток, который с выходов 31 сумматора 10 со сдвигом на К разрядов влево записывается з регистр 1 делимого. Если во втором вычитателе 9 формируется положительный результат, то он записывается со сдвигом на К разрядов влево в регистр 1 делимого в качестве нового остатка, т, к, коммутатор по значению логической единицы на выходе 18 настраивается на передачу информации с выходов 30 первого вычитателя 9. При этом, К-раз- рядное частное передается транзитом через узел 6 коррекции. По первому синхроимпульсу на выходах 15-17 блока 12 управления устанавливается код 010, разрешающий запись в регистр 1 . В конце первого цикла деления по второму синхроимпульсу в регистр 1 записывается новый остаток, в регистр 3 записываются первые К разрядов частного, а счетчик блока 12 устанавливается в состояние 2.

Во втором и последующих циклах деления устройство работает аналогично, как и в первом цикле (на выходах памяти микрокоманд формируется тот же код 010). Число тактов Р равно тт + 1, где L- разрядность

частного, а К - количество разрядов частного, получаемых в одном цикле деления, После выполнения Р тактов в регистре 3 частного будет содержаться 1-разрядное частное.

Формула изобретения Устройство для деления, содержащее регистры делимого, делителя и частного, блок деления усеченных чисел, два узла коррекции, блок умножения, два вычитателя, сумматор, коммутатор и блок управления, причем вход данных устройства соединен с информационными входами первой группы коммутатора и с информационными входами регистра делителя, выходы которого соединены с входами первой группы сумматора и первой группы блока умножения, входы второй группы которого соединены с информационными входами первого и выходами второго узлов коррекции частного, выходы коммутатора соединены с информационными входами регистра делимого, выходы которого соединены с входами уменьшаемого первого вычитателя, входы вычитаемого и заема которого соединены с выходами первой и второй групп соответственно блока умножения, выходы старших разрядов регистра делимого соединены с входами делимого блока деления усеченных чисел, входы делителя которого соединены с выходами старших разрядов регистров делителя, выходы старшего и младших разрядов блока деления усеченных чисел соединены с управляющими и информационными входами второго узла коррекции частного соответственно, управляющий вход первого узла коррекции частного соединен с выходом знакового разряда второго вычитателя, входы уменьшаемого и вычитаемого которого соединены с выходами разности и заема первого вычитателя, выходы второго вычитателя соединены с входами вторых групп коммутатора и сумматора, выходы первого узла коррекции частного соединены с информационными входами регистра частного, синхровход которого соединен с входом синхронизации устройства и с синхровходами регистров делимого и делителя и блока управле-ь.я, первый, второй и третий выходы которого соединены с первым управляющим входом коммутатора, входами разрешения записи регистров делимого и делителя соответственно, выходы суммато35 УI

36 У..У-.. У- X ,

1± Л ± лТ± 34 ± 34 ± J4 ± М

ггп

41

ра соединены с входами третьей группы коммутатора, отличающееся тем, что, с целью повышения быстродействия устройства, второй управляющий вход коммутатора соединен с выходом знакового разряда второго вычитателя.

.гг

-го

,jff

Фиг. Z.

JJ

37

i

| Устройство для деления п-раздельных чисел | 1977 |

|

SU732868A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-10-07—Публикация

1989-08-01—Подача