рого соединен с грегьи-м входом первого эпеменга ИЛИ и с вторым входом треть его блока элементов И, выход которогч) соединен с вторым входом первого блока элементов ИЛИ, третий и четвертый Входы блока стековой памяти соединены соответственно с восьмым и девятым выходами шифратора, выход блока стеко Вой памяти соединен с пятым входом первого дешифратора, вход второго элемента задержки соединен с шсодом синхронизации устройства, первый, второй и третий входы блока обработки соедине соответственно с выходами второго, тре тьего и четвертого блоков элементов ИЛИ,выходы второгобпока элементов ИЛИ Соединены с выходами каждого (2п + 2) го ( п .1,2) блока элементов И, вход третьего блока элементов ИЛИ соединены с выходами каждого (2п+ 3)-го ( п 1,К )блока элементов И, i -и ысо ( i Л, Е ) четвертого блока элементов ИЛИ соединен с выходом j-ro блока элементов И ( j 2 + 4, 3 Е + 3), первый вход которого соединен с выходо Второго дешифратора, второй вход соединен с выходом 1-го регистра еиераций, вход синхронизации которого соединен с выходом Второго блока эле /1ентов И, Информационный вход соединен с входом операций устройства, выход первого блока элементов И соединен с входом синхронизацииm-го регистра операндов, выход первого регистра операндов соеди нен с первым входом четвертого блока элементов И, второй вход которого подключен к выходу второго дешифратора, выход i-ro ( 1 2, Е ) регистра операн дов соединен с первыми входами (2 i + + 1)-го. и (2 { + 2)-го блоков элементов И, вторые входы которых соединены с выходом второго дешифратора, выход второго дешифратора соединен с первым входом (22+ 3)-го блока элементов И, второй вход которого подключен к выходу ( 2 1) -го регистра операндов, выход четвертого элемента ИЛИ соединен с четвертым входом блока обработ132 ки, причем блок обработки содержит регистр адреса, узел памяти микропрограмм, регистр микрокоманд, коммутаторы, сдвигатель, регистр суммы., сумматор, группу элементов И-ИЛИ и регистр, выход которого является вькодом блока обработки, выход регистра адреса соединен с входом узла памяти микропрограмм, Выход которого соединен с входом регистра микрокоманд, первый выход которого под1шючен к первому входу первого коммутатора, первый и второй ЕКОДЫ которого соединены соответственно с первым и вторым входами группы элементов И-ИЛИ, с первым и вторым входами сумматора, выход которого соединен с первым Входом сдвигателя, выход которого соединен с вторым выходом регистра Микрокоманд , третий выход которого соединен с управляющим входом регистра, выход второго коммутатора Соединен о первым входом третьего коммутатора, первый выход которого соединен с информационным входом регистра. Второй выход третьего коммутатора соединен с первым входом первого коммутатора, третий и четвертый входы которого являются соответственно первым и вторым входами обработки, второй вход третьего коммутатора соединен с третьим выходом регистра микрокоманд, третий выход подключен к первому выходу регистра суммы, второй выход которого соединен с первым входом регистра адреса, четвертый выход регистра микрокоманд Соединен с вторым входом регистра адреса, пятый выход соединен с управляюшим входом второго коммутатора, шестой выход соединен с третьим входом сумматора, седьмой выход подключен к Второму Входу сдвигателя, третий и четвертый входы регистра адреса явЛЯЮ7-СЯ соответственно третьим и четвертым вкодами блока обработки, выходы группы элементов И-ИЛИ со- едине11Ы соответственно с информационными вхоцами второго коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Процессор | 1981 |

|

SU962964A1 |

| Процессор параллельной обработки | 1990 |

|

SU1797126A1 |

| Процессорный модуль | 1985 |

|

SU1343421A1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| Устройство для перевода выражений в польскую инверсную запись | 1982 |

|

SU1130879A1 |

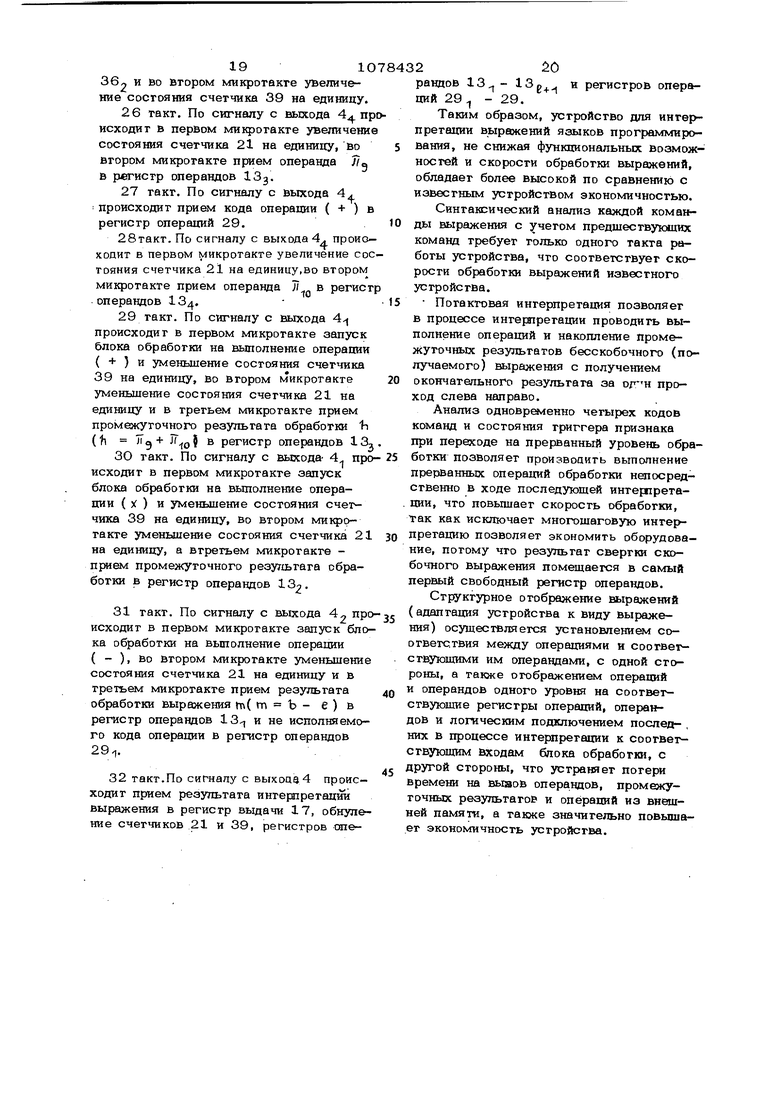

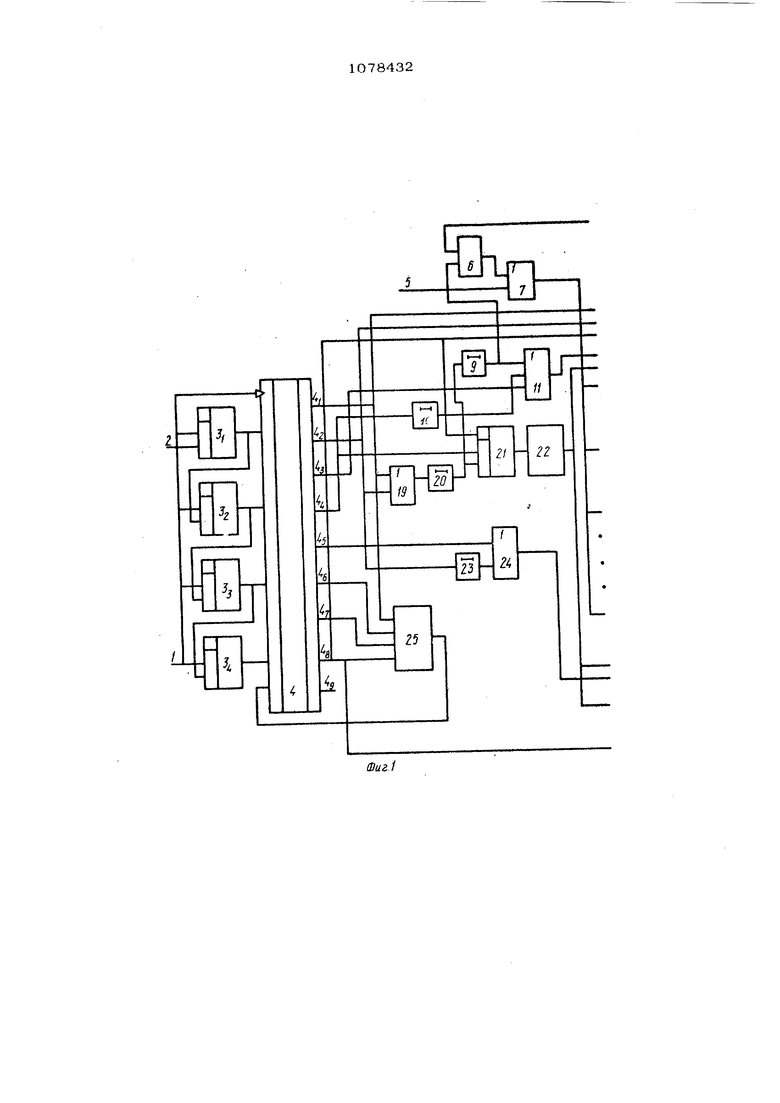

УСТРОЙСТВО ДНЯ ИНТЕРПРЕТАЦИИ ВЫРАЖЕНИЙ ЯЗЫКОВ ПРОГРАММИРОВАНИЯ, содержащее элементы И, ИЛИ, первый, второй, третий к четвертьШ регистры команд, входы ситронизащпкоторых соединены с входом синхронизации устройства, информационный вход первого регистра команд соединен с входом команд устройства, выход первого регисгра команд соединен с информационным входом Второго регистра команд, выход которого соединен с информационным входом третьего регистра команд, выход которого подключен к информационному Входу четвертого регистра команд, выходы регистров команд подключены соответственно к первому. Второму , третьему и четвертому входам первого дешифратора, первый выход шифратора соединен с первым входом первого элемента ИЛИ, выход которого соединен с первьЕч1 входом первого блока элементов И, второй вход которого соединен с выходом второго дешифратора, вход которого подключен к выходу счетчика операндов, выход второго дешифратора соединен с первым входом второго блока элементов И, второй вход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с вторым выходом шифратора, третий выход которого соединен с первым входом третьего элемента ИЛИ, четвертый выход соединен с входами установки в нулевое состояние решсгров операШ1Й, регистров операндов, счетчика операндов, с первым входом блока стековой памяти и с входом синхронизации решстра Вьщачи, выход которого является выходом данных устройства, информационный вход регистра выдачи подключен к выходу блока обработки, соединенному с первым входом третьего блока элементов И, пятый вьпсод шифратора через элемент НЕ подключен к выходу синтак синеской ошибки устройства, шестой выход соединен с суммирующим входом S счетчика операндов и через первый элемент задержки - с вторым входом первого элемента ИЛИ, вход операндов устройства подключен к первому входу первого блока элементов ИЛИ, выход которого подключен к информационным входам регистров операндов, управляющий вход шУ1фратора подключен к выходу второго эле мента задержки, выходы первого дешиф эо ратора подключены соответственно к информационным входам шифратора, от со ю личающееся тем, что, с целью упрошешм, в нем первый вход четвертого элемента ИЛР1 соединен с третьим выходом шифратора, который через трютий элемент задержки соединен с вторым входом Второго элемента ИЛИ, второй вход четвертого элемента ИЛИ, второй вход блока стековой памяти и второй вход третьего элемента ИЛИ соединены с седьмым выходом шифратора, выход третьего элемента ИЛИ через четвертый элемент задержки соединен с вычитающим входом счетчика операндов и с входом пятого элемента задержки, выход кото-

1

Изобретение относится к вычислительной технике и может быть использовано

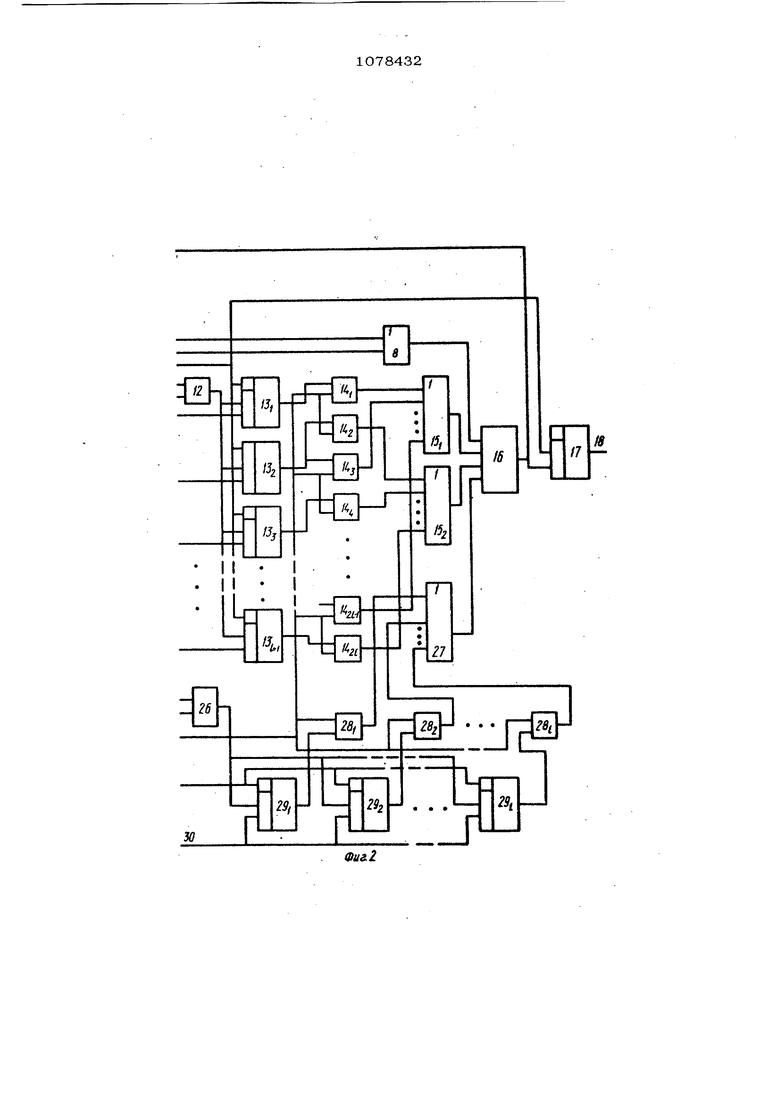

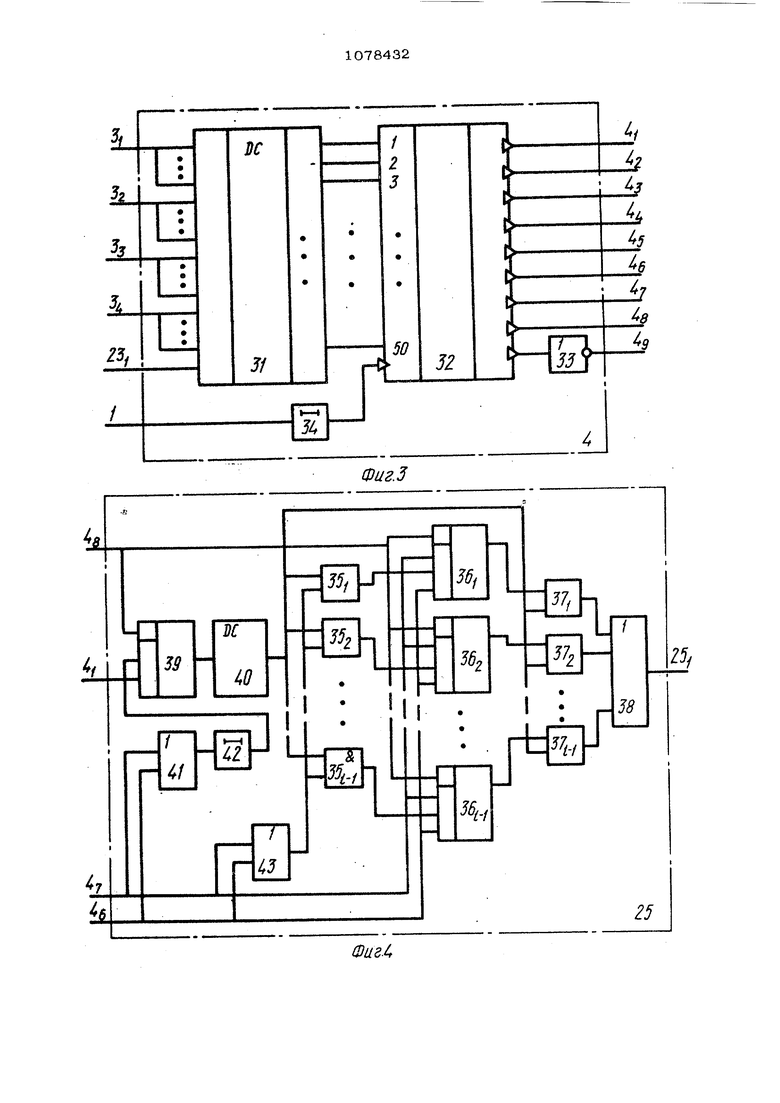

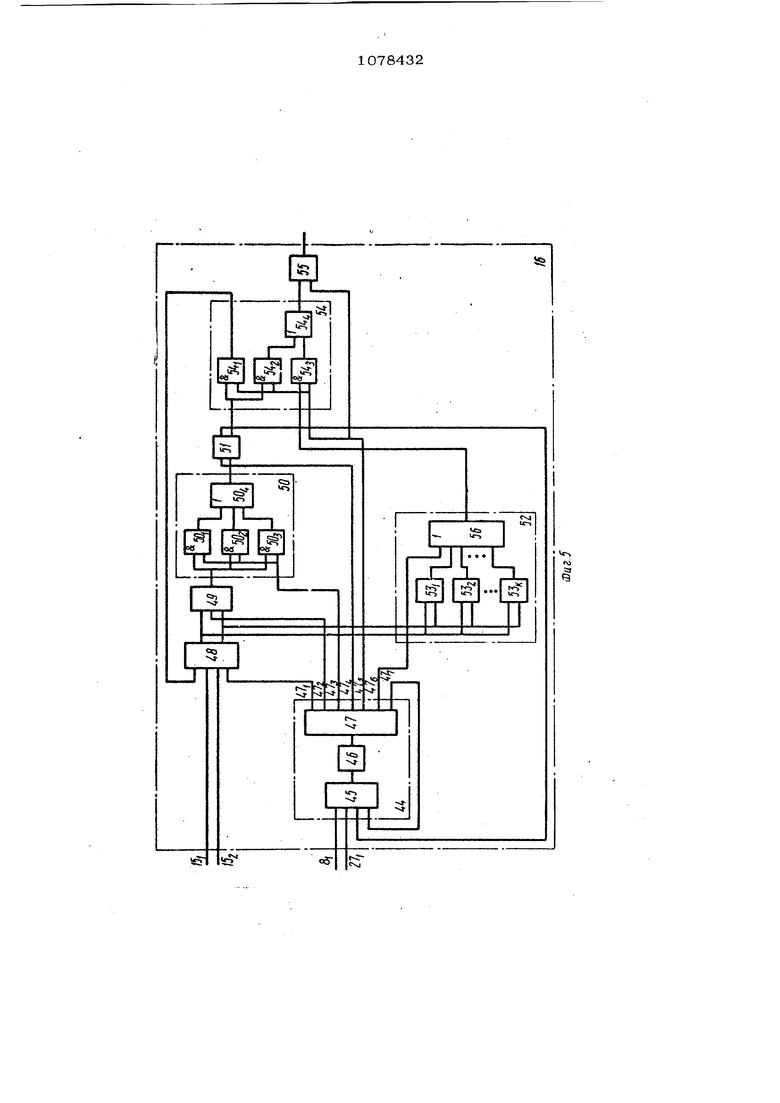

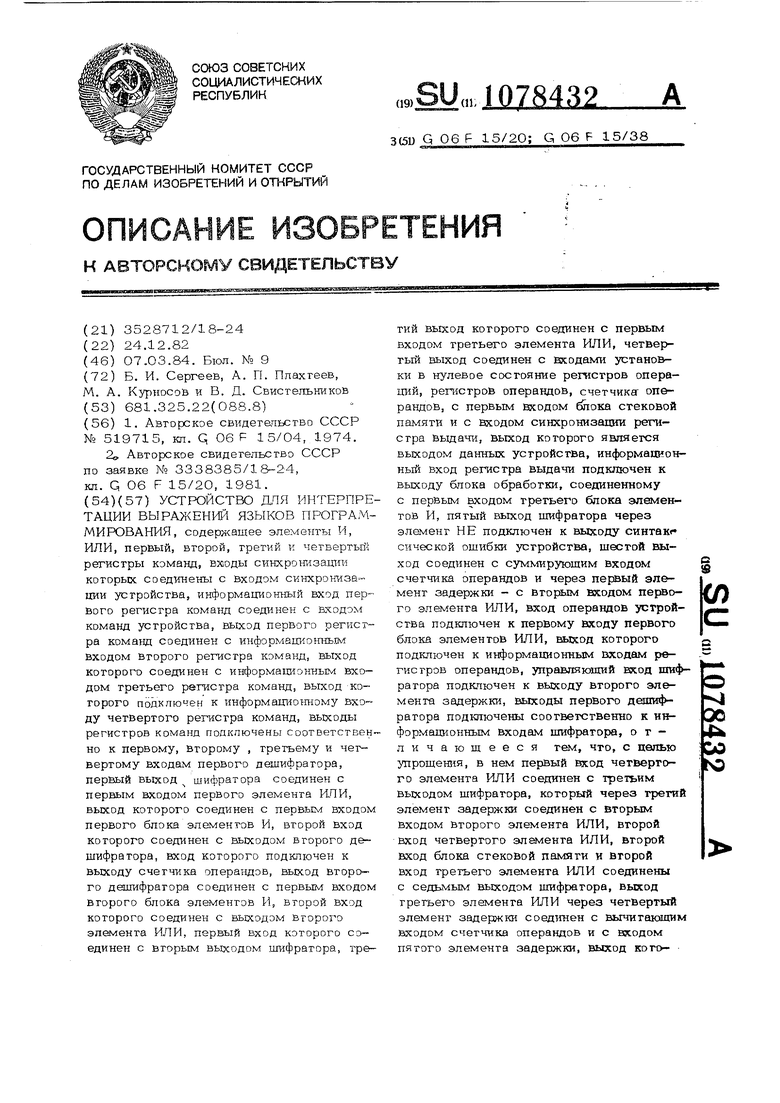

в быстродействующих операционньос системах обработю информации, в частности а системах с диалоговым режимом разра ки, отладки и вьтолнения программ, в электронных вычислительных машинах с языком высокого уровня. Известно устройство для обработки выра кений языков программирования, содержащее регистры операндов, формирова тель управляющих сигналов, блок стековой памяти, счетчик операндов, дещифрагор, арифметико-логический блок, выходной регистр Cl. Недостатком данного устройства является орагнизация стека, в который заносится вся вычислительная формула, что снижает экономичность устройства. Наиболее близким по технической сущ ности и достигаемому результату к пред лагаемому является устройство для обра ботки выражений языков программирования, содержащее вход синхронизаш1И, соединенный с входами синхронизации первого, второго, третьего и четвертого регистров команд, информационный вход первого из которых соединен с входом команд устройства, а выход - с информа ционным входом второго регистра команд выход которого соединен с информационным входом третьего регистра команд, выход которого подключен к информацион ному ВХОДУ четвертого регистра команд, вькод i-ro ( i 1,4) регистра команд подключен соответственно к i-y входу формирователя управляющих сигналов, первый выход Которого соединен с первы входом первого элемента ИЛИ, выход ко торого соединен с первыми входами первого блока элементов И, вторые входы которого соединены с соответствующими выходами дещифрагора, вход которого подключен к выходу счетчика операндов, выходы дещифратора соединены с первым входами второго блока элементов И, Вторые входы которого соединены с выходом второго элемента ИЛИ, первый Вход которого соединен с вторым выходо формирователя управляющих сигналов, третий вькод которого соединен с первы входом третьего элемента ИЛИ, четвертый выход - со входам установки в нулевое состояние регистров- операции, регистров операндов, счетчика операндов, первым входом блока стековой памяти и входом синхронизации регистра выдачи, выход которого является выходом данных устройства, информационный вход регистра вьщачи подключен к выходу блока обработки, соед шенному также с первым входом третьего блока элементов И, пятый выход формирователя управляющих сигналов является выходом синтаксической ошибки, шестой вькод формирователя соединен с суммирующим входом счетчика операндов и через первый элемент задержки с вторьп входом первого элемента ИЛИ, вход операндов устройства подключен к первому входу первого блока элементов ИЛИ, выходы которого подключены к информационным входам регистров операндов 2J. Недостатком данного устройства является его сложность, вызванная необходимостью реализации 2 блоков обработки, ( 2 К + 1) элементов выборочного сброса регистров операндов и операций, 2 блоков трехвчоцовык элементов И, восьми блоков элементов И коммутации выходов дещифратора на управляющие входы и входы установки в нуль регистров операндов и операций через четьфе блока элементов ИЛИ, блока стековой памяти, управляемого распределителя импульсов и обусловленных ими связей. Цель изобретения - упрощение yci ройства. Поставленная цель достигается тем, что в устройство, содержащее элементы И, ИЛИ, первый второй, третий и четвертый регистры команд, входы синхронизации которых соединены с входом синхронизации устройства, информационный вход первого регистра команд соединен с входом команд устройства, выход первого регистра команд соединен с иформационным входом второго регистра команд, вькод которого соединен с информашюнHBDvi входом третьего регистра команд, выход которого подключен к информапионному входу четвертого регистра команд, выходы регистров команд подключены соответственно к первому, второму, третьему и четвертому входам первого дещифратора, первый выход щифратора соединен с первьол входом первого элемента ИЛИ, выход которого соединен с первым входом первого блока элементов И, второй Вход которого соединен с BBRI ходом второго дещифратора, вход которого подключен к вькоду счетчика операндов, вькод второго дещифратора соединен с первым входом второго блока элементов; И,второй вход которого соединен с выходом торого элемента ИЛИ, первый вход ко- l oporo соединен с вторым входом шифрат тора, третий выход которого соединен с первым входом третьего элемента ИЛИ, четвертый выход соединен с установки в нулевое состоят{е регистров операций, регистров операндов, счетчика операвдов, с первым входом блока сгеко вой памяти и с входом синхронизапии ре гистра вьздачи, выход которого является выходом устройства, информационный вхо регистра выдачи подключен к выходу блока обработки, соединенному с первым входом третьего блока элементов И, пятый выход шифратора через элемент НЕ подключен к выходу синтаксической ошибки устройства, шестой выход соединен с суммирующим Входом счетчика операндов и через первый элемент задер ки с вторым входом первого элемента ИЛИ, вход операндов устройства подключен к первому входу первого блока элементов ИЛИ, выход которого подключен к информационным входам регистров операндов, управляюший вход ш;ифратора подключен к выходу второго элемента ЗЕщержки, выходь первого дешифратора подключены соответственно к информацио ным входам шифратора, первый вход четвертого элемента ИЛИ соединен с третьим выходом шифратора, который через третий элемент задержки соединен с Вторым входом второго элемента ИЛИ второй вход четвертого элемента ИЛИ, второй вход блока стековой пимяти и второй вход третьего элемента ИЛИ соединены с седьмым выходом шифратора, выход третьего элемента ИЛИ через чет вертый элемент задержки соединен с вы читающим Входом счетчика операндов и входом пятого элемента задержки, выход которого Соединен с третьим входом первого элемента ИЛИ и с вторым вход третьего блока элементов И, выход которого соединен с вторым входом первог блока элементов ИЛИ,третий и четвертый входы блока стековой памяти соединены соответственно с восьмым и девятым выходами шифратора, выход блока стековой памяти соединен с пятым входом первого дешифратора, вход второго элемента задержки соединен с входом синхронизации устройства, первый, второй и третий входы блока обработки соединены соответственно с выходами ьторого, третьего и четвертого блоков элементов ИЛИ, входы второго блока элементов ИЛИ соединены с выходами каждого {2п+ 2)-го ( п 1, ) блока элементов И, входы третьего блока элементов ИЛИ соединены с выходами каждого .(2п+ 3)-го ( п 1, Ё) блока элементов И, i й вход ( i 1, П четвертого блока элеь еигов ИЛИ соодянот с илходом j-ro блока элеменгов { j 10 326 4, 3), первый вход которогосовдинен с выходом второго дешифратора, второй вход соединен с выходом регистра операций,вхоп синхронизации которого соединен с выходом второго блока, элементов И, информационный вход соединен с входом операций устройства, выход первого блока элементов И соединен с входом синхронизации т-го регистра операндов, выход первого регистра опе рандов соединен с первым входом четвертого блока элементов И, второй вход которого подключен к выходу второго дешифратора, выход i-ro ( i 2, )регистра операндов соединен с первыми входами {2i+ 1)-го и (2i 2)-го блоков элементов И, вторые входы которых соединены с вьпсодом второго дешифратора, выход второго дешифратора соединен с первым входом (2 + 3)-го блока элементов И, второй вход которого подключен к выходу { + 1)-го регистра операндов, выход четвертого элемента ИЛИ соединен с четвертым входом блока обработки, причем блок обработки содержит регистр адреса, узел памяти микропрограмм, регистр микрокоманд, коммутаторы, сдвигатепь, регистр гуммы, сумматор, группу элементов И-ИЛИ и регистр суммы, выход которого является выходом блока обработки, выход регистра адреса соединен с входом узла памяти микропрограмм, выход которого соединен с входом регистра микрокоманд, первый выход которого подключен к первому входу первого коммутатора, первый и второй выходы которого соединены соответственно с первым и вторым входами группы элементов И-ИЛИ, с первым и вторым входами сумматора, выход которого соединен с первым входом сдвигателя, выход которого соединен с ин}зормационным входом регистра суммы, управляющий вход которого соединен с вторым выходом регистра микрокоманд, третий выход которого соединен с управляюшим входом регистра, выход второго коммутатора соединен с первым входом третьего коммутатора, первый выход которого соединен с информационным входом регистра. Второй выход третьего коммутатора соединен с первым входом первого коммутатора, третий и четвертый входы которого являются соответственно первым и вторым Входами блока обработки. Второй вход третьего коммутатора соединен с третьим выходом регистра микрокоманд, трегнй вход подключен к первому выходу penicrpa cjTviMU, второй выход кг торого соединен с первым входом регистра адреса, четвертый выход регистра микрокома1Щ соединен с вторым входом регистра адреса, пятый выход соединен с управляющим входом второго коммутатора,шестой выход соединен с третьим входом сумматора, седьмой выход подключен к второк у входу сдвига теля, третий и четвертый входы регистра адреса являются соответственно третьим и четвертым входами блока обработки, выходы группы элементов И-ИЛИ соединены соответственно с информационными входами второго коммутатора, третий элемент ИЛИ с входом блока обработ ки позволяет запускать блок обработки для выполнения очередной оиерамии. На фиг. 1 и 2 прецставпена блок-схема устройства; на фиг. 3 - блок-схема формирователя управляющих сигналов; на фиг. 4 - блок-схема блока стековой памяти; на фиг. 5 - блок-схема блока обработки; на фиг. 6 - временная диаграмма работы устройства. Устройство для интерпретации выражений языков программирования (фиг. 1, 2) содержит вход 1 синхронизации устройства вход 2 команд, регистры команд 3,, формирователь 4 управляющих сигналов с выходами 4 -|- 49, вход 5 операндов, блок элементов И 6, блок элементов ИЛИ 7, элемент ИЛИ 8, элементы задержки 9 и 10, элемент ИЛИ 11, блок элементов И 12, регистры операндов 13 1 3 +- -f , блоки элементов И 14- 14 л блоки элементов ИЛИ 152 блок обработки 16, регистр выдачи 17, выход 18 данных устройства, элемент ИЛИ 19, элемент задержки 20, счетчик операндов 21, дешифратор 22, элемент задержки 23, элемент ИЛИ 24, блок стековой памяти 25, блок элементов И 26, блок элементов ИЛИ 27, блоки элементов И 28,- 28g, регистры операций 29.29g, вход 30 устройства, дешифратор 31 шифратор 32, элемент НЕ 33, элемент задержки 34, элементы И 35 - 35 р, триггеры признака 36 - 36 --f, элемен ты И 37-1 - 37g-f, элемент ИЛИ 38, счетчик уровня 39, дешифратор 4О, элемент ИЛИ 41, элемент задержки 42, элемент 14ЛИ 43, микропрограммное устройство 44 управления, регистр 45 адреса, узел 46 памяти микропрограмм, регистр 47 микрокоманд, коммутатор 48 сумматор 49, сдвигатель 5О, регистр 51 суммы, узел 52 логических операций, включающий группу элементов И-ИЛИ 53 х| - 53,, коммутатор 54, регистр 55, коммутатор 56. Коды команд с выходов регистров команд и разряд признака с выхода блока стековой памяти 25 поступают на входы дешифратора 31, вследствие чего на его выходах формируется унитарный код, поступающий далее на входы шифратора 32, вызьюая появление положительното импульса на одном из его выходов. Единичный сигнал на выходе 4 фориирователя вырабатывается лишь в случае недопустимой кодовой комбинации на Входах дешифратора 31, что ведет к формированию нулевого кода на его выходах. Сигнал, поступающий с входа 1 синхронизации устройства через элемент задержки 34 на синхронизирующий вход шифратора 32, обеспечивает стробирование работы щифратора лицц, после завершения переходных процессов в реш- страх команд 3 -3, и дешифраторе 31. Блок стековой памяти 25 работает следующим образом. В исходном состоянии счетчик уровня 39 и триггеры признака 36.- 36g.j находятся в нулевом состоянии, причем на первом выходе дещифратора 4О установлен единичный сигнал. По сигналу на входе 4, , соединенном с одноименным выходом формирователя управляющих сигналов, происход11т установка нулевого состояния в триггере признака 36, так как этот сигнал поступает на входы записи нулевого состояния всех триггеров признака одновременно, а также через элемент ИЛИ 43, элемент И 35, выбранный единичным сигналом с первого выхода дещифратора 4О - на управляющий вход триггера признака 36 . Сит нал состояния триггера признака 36 через элемент И 37, выданный единичным сигналом с первого выхода дещифратора 40, и элемент ИЛИ 38 поступает на выход блока стековой памяти 25. Сиг нал с Входа, соединенного выходом 46 формирователя управляющих сигналов через элемент ИЛИ 41 и элемент задерж жки 42, поступает на суммт{рующий вход счетчика уровня 39, увеличивая его состояние на единицу, сигнал появляется на Втором выходе дешифратора 40, соединенном с входами элe eнтoв И 352 и вызывая коммутацию выхода триггера признака 362 через элемент ИЛИ 38 с выходом блока стековой памяти 25, а также разрешая запись нулевого или единичного состояния в триггер при,-: накй 362- Таким образом зафиксируется отсутствие HGFM шолненной операции в первом уровне обработки и осуществляете: переход на второй уровень . В общем случае происходит фиксация отсутствия невьшолиенной операции в прерываемом уровне обработки выражения и переход на более высокий уровень. Аналогично действует и сигнал на входе блока стековой памяти, соединенно выходом 4-. формирователя управляющих сигналов с той разницей, что он поступа на входы записи единичного состояния триггеров признака, вызывая запись единичного состояния в один из триггеров признака и фиксируя, тем самым, наличи невыполненной операции в прерываемом уровне обработки. Сигнал с входа блока стекоВой памят соединенного с выходом 4 формировател управляющих сигналов, поступает на вычитающий вход счетчика уровня 39, вызы вая уменьшение его состояния на единицу. Вследствие этого единичный сигнал появляется на том выходе дешифратора 4О, который через соответсгвующ 1й элемент И 35 соединен с управляющим входом триггера признака, соответствующег последнему прерванному уровню обработки выражения, а также на вход элемента И 37, второй вход которого соединен с выходом триггера признака, а выход через элемент ИЛИ 38 - с выходом бло ка стековой памяти 25. Таким образом фиксируется завершение интерпретации текущего уровня обработки выражения и переход на предшеств ющий прерванный уровень обработки. Сигнал с входа блока стековой памят соединенного с выходом 4g формирователя управляющих сигналов, поступает на Вход асинхронной установки в нулевое состояние счетчика уровня 39 и на вход асинхронной установки в нулевое состояние триггеров признака, вызывая их обнуление. В исходном состоянии блок обработки находится в ждущем режиме (сигнал на входе, запускающий блок обработки, отсутствует). При поступлении на вход блока обработки единичного-сигнала прои ходит прием кода операции с соответству ющего регистра 29 операций в регистр 45 адреса и запуск микропрограммного устройства управления 44. Микрокоманды, считываемые из узла 46 в регистр 47 микрокоманд, имеют семь управляющих полей 47- - 47-J. Код на выходе 47 управляет подаче операндов и промежуточных результатов на входы сумматора 49 и узла 52. Код 47, управляет работой сумматора при реализации арифметических операций (сложения, вычитания, умножения, деления). Для реализации сложных арифметических операций по итерационным алгоритмам используется сдвигатель 5О, осуществляющий передачу кода без сдвига с выхода сумматора 49 на вход регистра 51 суммы или передачу со сдвигом Вправо, или со сдвигом влево под дествием соответствующего управляющего кода с вьпсода 47j регистра микрокоманд 47. Прием промежуточного кода с выхода сдвига теля 50 в регистр 51 осуществляется под действием управляющего кода с выхода 47. Управляющий код с выхода 47g- управляет коммутатором 54, который производит передачу окончательного результата с выхода регистра 51 суммы или узла логических операций на вход регистра 55 или передачу кода промежуточного результата арифметических операций с выхода регистра суммы 51 на вход коммутатора 48. Управляющий код с выхода 47 управ ляет коммутатором 53, который осуществляет передачу результата логической операции на коммутатор 54. Код адреса следующей микрокоманды с выхода 47-, поступает на вход регистра 45 адреса и управляет ходом выполнения микропрограммы операций. Сигналы переполнения, знака и другие, поступающие с регистра 51 суммы на вход регистра адреса 45, используются для проверки логических условий и ветвлений в микропрограммах. После выполнения микропрограммы операции над заданными операндакта результат через коммутатор 54 записывается в выходной рргистр 55 и микропро граммное устройство управления 44 пере ходит в режим ожидания до поступления очередного сигнала на Вход. Основой языка программироваш1Я устройства являются элементарные записи, которые В определениях языка Бэкуса записываются следующим образом: запись : : разделитель выражение разд&аитель ; разделитель : : ; :БЫражение : : выражение операция выражение команда заверщения ; выраже1ше : ; скобка открывающая выражение) скобка закрывающая/. выражение : : операнд ) операция) операнд ; операция : ; f ; команда завершения : : j ; скобка открывающая : : ( ; скобка закрывающая ; : ) ; : операнд : : 7Т ; бр .ц - множесгво операций реализуемых блоком обработки. Скобки предназначены для изменения порядка вычислений (выделения участ ков выражения с более высоким уровнем При этом под уровнем выражения при нимается часть выражения, заключенная между открывающей и соответствующей закрывающей скобками одной степени вложенности. Под степенью вложенности понимаетс , указывающее количество открыты скобок в последовательности открывающи скобок в выражении при условии равенст числа открывающих и закрывающтих скобок. При нулевой степени вложенности скобки отсутствуют. Обработка очередного уровня может прерьшаться появлением старщего по сте ни Вложенности уровня. При этом результат обработки прерванного и незавершенг ного уровня запоминается в регистре опе рандов данного уровня. Обеспечивается коммутация цепей для приема операндов и промежуточных результатов прерьсвающ го (старшего ) уровня на регистры операндов этого уровня и их подачи на вход блока обработки. По завершении обработки высшего уровня осуществляется переход на обработку низшего (прерванного) уровня. Пер ход с одного уровня на другой сопрово } дается изменением состояния счетчика уровня в блоке стековой памяти. Обработ ка заканчивается командой завершения, по которой окончательный результат помещается в первый регистр операнаов. Элементарные записи могут обьепинятьс В последовательности записей: последовательность записей : : (запись) ; последовательность записей : : запись) последовательность записей «i запись ; Команда ( ) обеспечивает прием результата обработки предыдущей записи в регистр вьщачи и сброс схем устройства перед началом обработки следующей Записанные указанным образом выражения в случае использования устройств в пиапоговых системах отладки и выпопне ния программ кодируются позначно и вводятся в блок внешней памяти (не показан). В случае использования устройства в ЭВМ с аппарагно реализованньЫ языком высокого уровня к указанному виду выражения приводятся на этапе преобразования исходного текста программы к внутреннему представлению, которое помешается в оперативную память (не показана). Выборка комайд, операций обработки и операндов из памяти и подача их на соответствующие входы устройства интерпретации осуществляется внещним устройством управления (не показано). Период слеаования импульсов синхронизации устройства рассчитывается на длительность интерпретации самой длинной команды, которая в основном определяется длительностью реализации самой продолжительной операции обработки операндов в блоке обработки. Диаграмма работы устройства при вьшолнении различных команд показана на фиг. 6, где обозначены следукадие Временные зависимости сигналов: СИ - на входе синхронизации устройства;Ф С - на одном из рыходов формирователя управляющих сигналов; CPG . - на входе синхронизации 1-го peiTiCTpa операндов; на вьсходе элемента ИЛИ 8; на входе синхронизации i -го регистра операций; на входе синхронизации регистра 17; на Входе асинхронной установки нулевого состояния 1 ( 2 + 1 ) регистров операндов; R R Ь - на входе асинхронной установки нулевого состояния 1 регистров сзпераций; на входе установки нулевого ) состояния счетчика операндов 21 (счетчтка уровня 39); на входе асинхронной установки нулевого состояния триггеров признака 1 - (Р - 1); Y36- на входе записи единичного (K3fo. . (нулевого) состояния j -го триггера признака; на суммирующем входе счетчика операндов 21 (счетчика уровня 39); - на вычитающем входе счетчика ) 21 (счетчмка 39). Диагра.1мы - соответствуют работе устройства при появлении сигналов 131 на выходах 4 , - 4g фврмировагеля управляющих сигналрв. Разрешенные комбинации команд сведены в табл. 1. Соответствие комбинаций команд управляющим сигналам на выходах 4 - 4д формирователя управляющих сигналов 4 представлено в табл. 2, где введ ны следующие обозначения: C-fij - состояние счетчика операндов;i.C -fjM; - ссютояние счетчика уровня блока стековой памяти; j C,2jM; Сл - сигнал запуска блока обработки;Vgg - выход блока обработки; RG, - 1-й регистр операндов; RGii - i-й регистр операций; П- - j-и триггер признака блок стековой памяти; - время задержки, равное длительности реализации самой продолжительной операции В блоке обработк fj - время задержки, равное длительности распростране ния управляющего сигнала при установке схем устрой ства; предназначено для разнесения во времени нес местимых микроопераций; С - комбинация на входах 1формирователя управляющи сигналов 4. Интерпретация выражений осуществля ется следующим образом. Сигнал синхронизации, поступающий на вход 1 синхронизации устройства и далее на входы синхронизации регистров 3 - 3. от внещнего устройства управл ния, ;вызывает сдвиг кодов команд в регистрах команд 3 - 3. . Состояние регистра 3 переписывается в регистр состояние регистра 32 переписывается в регистр 3 , состояние регистра 32 переписывается в регистр 3 и код оче редной команды с входа 2 записывается в регистр 3. На Входы формирователя 4 управляющих сигналов поступает комбинация четырех кодов команд с выходов регист ров 3 - 3. и разряд признака из блок стековой памяти 25. При этом по сигн синхронизации, поступакшему через время задержки на синхронизирующий вход формирователя, на одном из его в 3214 ходов 4 4д появляется положитепьный импульс. Задержка прохождетгля синхросигнала на синхронизирующий вход формирователя, на одном из его вьгходов 4 4 о появляется положителы-сый импульс. Задержка прохождения синхросигнала на синхронизирующий вход формироватапя исключает возможную неоднозначность срабатывания формирователя при неодновременном срабатывании двухтактных трипперов в регистрах команд. Положительный сигнал на одном vi3 выходов формирователя обеспечивает выполнение микроопераций в одном такте работы устройства, определяемом периодом следования синхронизирующих импульсов. Такт в схемах устройства посредством введет-гия временных задержек делится на микротакты, в которых вьшол1шются несовместимые микрооперации. СигнЕШ с выхода 4 о приводит к приему результата вычисден югэ вз ражетшя с выходов регистра 55 блока обработки 1G в регистр 17, обнулению счетчика операндов 21, счетчикв УРОВ1-1Я 39 и триггеров признака 3G - ЗС « . в блоке стековой памяти 25, регистров операндов о g 4- и регистров операций 20 - 29 (осуществляется подготовка схем устройства к началу интерпретации новой записи) . Сигнал с выхода 4 через элемент ИЛИ 11 разрешает прохождение сигнала с выхода дещифратора 22 через блок элементов И 12 на вход сит-кронизации регистра операндов 13 , вызывая прием операнда с входа 5 через блок элеMetiTOB ИЛИ 7. Сигнал с выхода 4 вызывает увеличение состояния счетчика 21 на еди1-лщу и, следовательно, изменение кода via выходе дешифратора 22, далее через элемент задержки 10 элемент ИЛИ 11 разрешает прохождение сигнала с ( i + 1 )-го выхода дещифратора 22 через блок элементов И 12 на вход синхронизации регистра операндов 13 , разрешая прием операнда с входа 5 через блок элементов ИЛИ 7. Сигнал с выхода 4 через элемент ИЛИ 24 разрещает прохождеш-1е сигнала с i го выхода дещифратора 22 чьрез блок элементов И 26 tia вход син фонизации регистра операций 29 j , ВызывбЫ приам кода операц1- И с вчппа :;Ю -.операций. Сигнал с выхода 4 / вызывает устаHofjKV триггера признака п Глсже 2о гтеко- Вой памяти в нулевое состояние, иденги фицируюшее отсутствие невыполненной операции в данном уровне вложенности, далее через элемент ИЛИ 41, элемент задержки 42 вызывает увеличение соетояния счетчика 39 блока 25 стековой памяти на единицу , обеспечивая формирование сигнала разрешения синхронизации на ( J+ 1 )-м выходе дешифратора 4О (осуществляется переход к обработк старшего уровня вложенности). Сигнал с выхода 4 , вызывает установку триггера признака 36 j в блоке 25 стековой .памяти в единичное состоя ние, идентифицирующее наличие невьтолненной операции в данном уровне вложен ности, далее через элемент ИЛИ 41, элемент задержки 42 вызывает увеличение состояния счетчика 39 блока 25 стековой памяти на еаиницу,чго свидетель ствует о переходе к обработке старшего уровня вложенности. Сигнал с выхода 4 через элемент ИЛИ 8 вызывает запуск блока обработки, на входах которого установлены коды операндов с выходов регистров операндов и 13 j через блок элементов И 142 i-t блок элементов И 142(1-(I соответственно посредством разрешающего сигнала с -(-го выхода дешифратора 22 на входы элемен тов И данных блоков, а на входе операций установлен код операции с выхода регистра операции 29 |. через блок элементов И 28 посредством разрешающего сигнала с i-ro выхода дешифратора 22 на входы элементов И данного блока, и одновременно вызывает уменьшение состояния счетчика 39 уровня на единицу, далее сигнал через элемент ИЛИ 19, элемент задержки 20 (задержки на Время вьтолнения самой длинной операции блоком обработки) вызывает уменьшение состояния счетчика 21 опер дов на единицу, далее через элемент задержки 9 поступает на вход блока элементов И 6 и через элемент ИЛИ 11 на вход блока элементов И 12, разреша ет прохождение кода промежуточного результата с выхода блока 16 обработки через блок элементов И 6, блок элементов Р1ЛИ 7 на информационные входы регистра операндов 13 j и обес чивает синхронизацию приема результата в данный регистр. Сигнал с выхода 4, , не осуществляя уменьшения состояния счетчика 39 блока стековой памяти в первом микротакте, действует аналогично сигналу с выхода 4, кроме того, в третьем микротакте одновременно с приемом результата промежуточной операции & регистр операндов 13,- происходит прием кода операции с входа 30 операций в регистр операций 29 .. Сигнал с выхода 4о является сигналом семантической ошиёки во входном выражении. Работу устройства рассматривают по тактам. При этом под тактом понимают последовательность действий, выполняемых между последовательными приемами кодов команд. Рассмотри функционирование предлагаемого устройства на следующем примере. Пусть на вход команд устройства последовательно поступает элементарная запись ((sЛ))(,)) При рассмотрении примера опускают обший для каждого такта этап приема очередного кода команды в регистр 3 и сдвиг информации в регистрах 32 3 тл начинают с момента появления единичного сигнала на одном из выходов формирователя управляющих сигналов. 1такт. По сигналу с выхода 4д формирователя управляющих сигналов происходит прием результата интерпретации предьщущего выражения с выхода блока обработки в регистр выдачи 17, обнуление счетчиков 21 и 39, регистров операндов 13 - 13 и регистров операций 29 - 29 g. 2такт. По сигналу с выхода 4 , происходит прием операнда J с входа операндов устройства в регистр операндов 13-. 3такт. По сигналу с выхода 4т про исходит прием кода операции ( + ) с входа операций устройства в регистр операций 29. 4такт. По сигналу с выхода 4 происходит в первом микротакте запись одиночного значения в триггер признака 36.J, а во втором микротакте - увеличение состояния счетчика 39 на единицу. 5такт. По сигналу с выхода 4, происходит в первом микротакте увеличение состояния счетчика 21 на единицу и во втором микротакте прием операнда JT в регистр операндов 13, с входа операнд дов устройства. 6такт. По сигналу с выхода 4 происходит прием кода операции (х) с юсода устройства в регистр операций 2927такт. По сигналу с выхода 4 . происходит в первом NraKpoTaKTe увеличе1гае

состояния счетчика 21 на единицу и во втором микротакге прием операнда JA с входа операндов в регистр отеравдов 13 .

8такт. По сигналу с выхода 4,, проис- 5 ходит в первом микротакте запуск блока обработки на вьшопнение операции (X)

и уменьшение состояния счетчика 39 на единицу, во втором микротакте уменьшение состояния счетчика 21 на единицу 10 и в третьем микротакте - прием пpo яeжyточного результата обработки с( { сх Ло J ) с выхода блока обработки в регистр операндов 1329такт. По сигналу с выхода 4 у проис-15 ходит в первом микротакге запуск бпока обработки на вьшолнение операции (+,

во втором микротакте уменьшение состояния счетчика 21 на единицу , а в третьйи микротакте - прием промежуточ- 20 ного результата обработки в ( b - ) с выхода блока обработки в регастр операндов 13-1 кода операции (-) в регистр операций 29.

10такт. По сигналу с выхода 4 про-25 исходит в первом микротакте запись единичного значения в триггер признака 36, во втором микротакте увеличение состояния счетчика 39 на единицу.

11такт. По сигналу с выхода 4 про-зо исходит в первом микротакге запись нулевого состояния в триггер признака

362 , а во втором микротакте - увеличение состояния счетчика 39 на единицу,

12такт. По сигналу с выхода 4 про-35 исходит в первом микротакте запись нулевого состояния в триггер признака Зб, во втором микротакте увеличение состояния счетчика 39 на единицу.

13такт. По сигналу с выхода 4 исходит в первом микротакте увеличение состояния счетчика 21 на единицу иво втором микротакте прием операнда Л

в регистр операвдов 13214такт. По сигналу с выхода 4 про- исходит прием кода операции ( х) в регистр операции 292.

15такт. По сигналу с выхода 4 происходит в первом микротакте увеличение состояния счетчика 21 на единицу к во втором микротакге прием операнда

в регистр операндов 13з.

1Q такт. По сигналу с вьпсода 4 происходит в первом микротакте запуск блока обработки на выполнение операции (/), втором микротакте уменьшение состояния счетчика 21 на единицу, а в третьем микротакте - приа промежуточного результата обработки с выхода блока обработки С( с JL / Fg-) в регистр операндов 13 2 и прием кода операции ( + ) в регистр операций 292.

17такт. По сищалу с выхода 4, происходит в первом микротакте увеличение состояния счетчика 21 на единицу, во втором микротакте - прием операнда л

в регистр операндов 13з.

18такт. По сигналу с выхода 4 происходит в первом микротакте запуск блока обработки на вьшолнение операции ( + ) и уменьшение состояния счетчика 39 на единицу, во втором микротакте уменьшение значения счетчика 21 на единицу, а в третьем микротакте прием промежуточного результата обработки сС( 0 с+ It ) в регистр операндов 13219такт. По сигналу с выхода 4г происходит прием кода операции ( х ) в регистр операций 292.

20такт. По сигналу с выхода 4. происходит в первом микротакге увеличение состояния счетчика 21 на единицу и во втором микротакте прием операнда Л -,

в регистр операндов ISg.

21такт. По «сигналу с выхода 4 . происходит в первом микрогакге запуск блока обработки на выполнение операции ( х), во вгором микрогакге уменьшение состояния счетчика 21 на единицу и в третьем микротакте - прием промежуточного результата обработки е ( е о х х5Г-) в регистр операндов 13 2 и прием кода операции ( - ) в регистр операций 29.

22такт. По сигналу с выхода 4 происходит в первом микрогакге увеличение сосгояния счетчика 21 на единицу, во Втором микротакте прием операнда JL в регистр операндов 13223гакг. По сигналу с выхода 4происходит в первом микротакге запуск блока обработки на вьшолнение операции ( - ) и уменьшение состояния счетчика 39 на единицу, во втором микротакте уменьшение состояния счетчика 21 на единицу и в третьем ми крот акте прием промежуточного результата обработки2( е -JTg)B регистр операндов 13

24гакг. По сигналу с выхода 4 g происходит прием кода операции ( х ) в регистр операций 202.

25такт. По сигналу с выхода 4 происходит в первом микрогакте запись единичного состояния в триггер признака

Збр и во втором микротакте увеличение состояния счетчика 39 на единицу.

26такт. По сигналу с выхода 4ц. происходит в первом микротакте увеличение состояния счетчика 21 на единицу, во втором микротакте прием операнда Лд

в регистр операндов ХЗд.

27такт. По сигналу с выхода 4

: происходит прием кода операции ( + ) в регистр операций 29.

28такт. По сигналу с выхода 4. происзходит в первом микротакте увеличение состояния счетчика 21 на единицу,во втором микротакте прием операнда Л в регистр операндов 134.

29такт. По сигналу с выхода 4 происходит в первом микротакте запуск блока обработки на вьшолнение операции ( + ) и уменьшение состояния счетчика

39 на единицу, во втором микротакте

уменьшение состояния счетчика 21 на единицу и в третьем микротакте прием промежуточного результата обработки h (t TTg + в регистр операндов 13

30такт. По сигналу с выхода- 4 происходит в первом микротакте запуск

блока обработки на вьшолнение операции ( у ) и уменьшение состояния счетчика 39 на единицу, во втором микротакте уменьшение состояния счетчика 21 на единицу, а втретьем микротакте прием промежуточного резугштата обработки в регистр операндов 132.

31такт. По сигналу с выхода 4 происходит в первом микротакте запуск блока обработки на вьшолнение операции

( - ), во втором микротакте уменьшение состояния счетчика 21 на единицу и в третьем микротакте прием результата обработки выражения (п(т Ъ- е) в регистр операндов 13 и не исполняемого кода операции в регистр операндов 29.

32такт.По сигналу с выхоаэ4 происходит прием результата интерпретации выражения в регистр выдачи 17, обнуление счетчиков 21 и 39, регистров операндов 13 - I3g . и регистров операций 29 - 29.

Таким образом, устройство для интерпретации выражений языков программирования, не снижая функциональных возможностей и скорости обработки выражений, обладает более высокой по сравнению с известным устройством экономичностью.

Синтаксический анализ каждой команды выражения с учетом предшествумцих команд требует только одного такта работы устройства, что соответствует скорости обработки выражений известного устройства.

Потактовая интерпретация позволяет в процессе интерпретации проводить выполнение операций и накопление промежуточных результатов бесскобочного (получаемого) выражения с получением окончательного результата за од-н проход слева направо.

Анализ одновременно четырех кодов команд и состояния триггера признака при переходе на прерванный уровень обработки позволяет производить выполнение прерванных операций обработки непосредственно в ходе последующей интерпретации, что повышает скорость обработки, так как исключает многошаговую инте{ претацию позволяет экономить обсчэудова- ние, потому что резутштат свертки скобочного выражения помещается в самый первый свободный регистр операндов.

Структурное отображение выражений (адаптация устройства к виду выражения) осуществляется установлением соответствия между операциями и соотвв ствуюшими им операндами, с одной стороны, а также отображением операций и операндов одного уровня на соответствующие регистры операций, операндов и логическим подключением послед- , них в процессе интерпретации к соответствующим входам блока обработки, с другой стороны, что устраняет потери времени на вьаов операндов, промежуточных результатов и операций из внешней памяти, а также значительно повышает экономичность устройства.

S

rt «2 П

4ra

25

f

/7

//y

/5,

7

Э гтЭ30

1

p

Фиг.

r4J

Фиг.З

V:

//2.4

д;г// р|б)фусri.

в,

f Oj

аесгЦ:т: г

decrfCrff;

с . -Гг.

п

п

д)С .j е)

&-п

С R&i

ж) с щ, Л

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обработки выражений языков программирования | 1974 |

|

SU519715A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-03-07—Публикация

1982-12-24—Подача