данных, второй вход которого соедине с управляклцими входами регистров передачи данных и с четвертым входом устройства, выход блока выдачи данны связан со вторыми входами группы элементов И, со входом счетчика, парный выход которого является третьим выходом устройства, а второй выхо счетчика соединен с третьим входом блока блокировки Г23.

Недостаток указанного устройства заключается в ограниченной области применения, так как оно может быть использовано только в тех ЦВМ, вся память которых, включая регистровую и память на управляющих триггерах, реализована в виде блока оперативной пaмяти. Поскольку ЦВМ вьшолняют

операции, изменяя содержимое информационных регистров и состояние триггеров управления, а также содержимое регистров арифметического устройства, блокирования записи в оперативную память по сбою совершенно не достаточно. Неверно выполненная команда может изменить содержимое регистров своих исходных операндов и тем самым исключить принципиальную возможность повторения. Таким образо отказ ЦВМ происходит и в том случае, когда сбой возникает на команде, при выполнении которой изменяются состояния триггеров управления или регистров устройства центрального управления, регистров арифметическог устройства, не имегацих входов в регистры передачи данных. Кроме того, сбой, происходящий в самой аппаратуре устранения сбоев, также приводит к отказу ЦВМ и полной поте1ре диагностической информации.

Цель изобретения - расширение области применения устройства за счет

расширения множества устраняемых сбойных ситуаций, а также возможности его

: работы с ЦВМ разного типа и поколения

Поставленная цель достигается тем, что в устройство, содержащее М блоков памяти, первые входы которы подключены к соответствующим выходам дешифратора и выходам первой выходов устройства, а выходы - к соответствующим выходам второй группы выходов устройства, и счетчик, выходом соединенный со входом дешифратора и выходом устройства, а входом - со входом устройства, введены М шифраторов адреса и блок фиксации фаз выполнения команды, причем

вторые и третьи входы блоков памяти соединены с соответствующими входами первой и второй групп входов устройства, первая группа выходов блока фиксации фаз выполнения команды подключена к группам входов шифраторов адреса, группа входов - ко второй группе входов устройства, а вторая группа выходов - к первым входам соответствующих шифраторов адреса, второй вход и выход каждого из которых соединены соответственно с первым и четвертым входами одноименного блока памяти.

Блок фиксации фаз вьпюлнения команды содержит счетчик, М дешифраторов и М групп триггеров, причем вход i-го дешифратора ,M) соединен с 1 -ым входом группы входов блока, группа входов - с выходами триггеров (i -1) -ой группы, а у-ый вь1ход группы выходов (,т). - с первым входом j-ro триггера -той группы и вторым входом j -го триггера (i - -fj -ой группы, второй вход j -го триггера lM-ой группы соединен с первым входом (j +1)го триггера той же группы, второй вход m -го триггера М-ой группы соединен с первым входом первого триггера той же группы, выходы дешифраторов являются второй группой выходов блока, вход и группа выходов счетчика подключена соответственно ко входу и группе входов первого дешифратора;

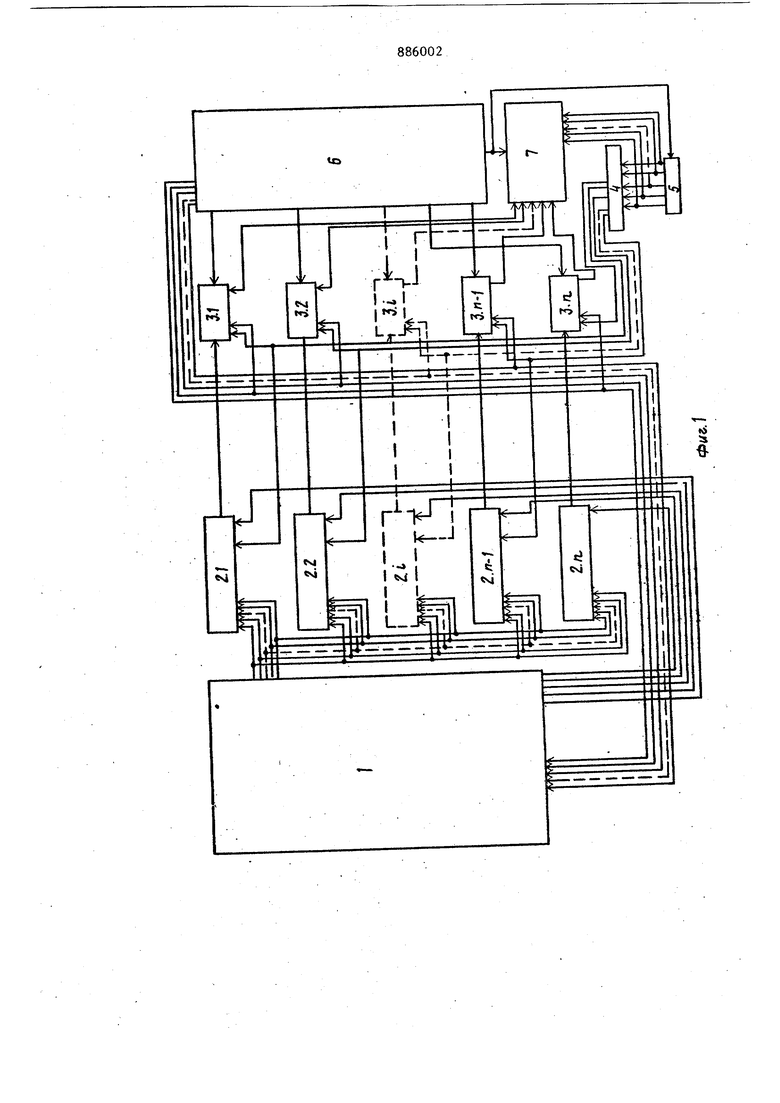

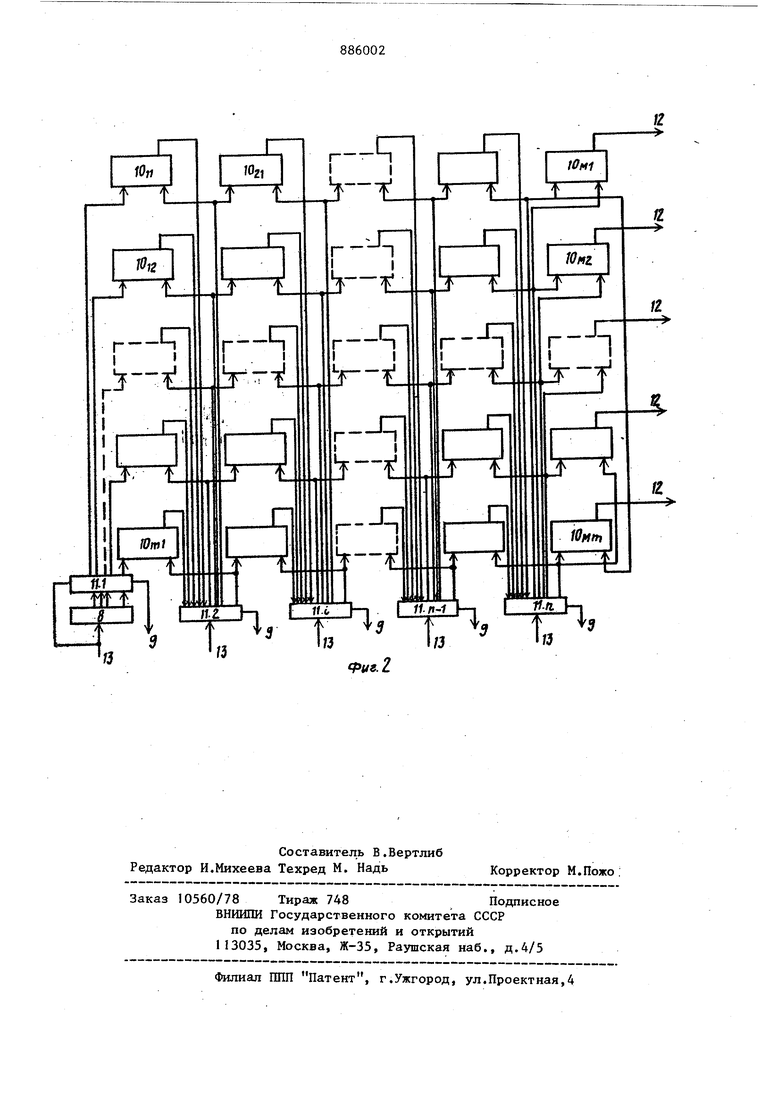

На фиг.1 представлена блок-схема предлагаемого устройства) на фиг.2 схема блока фиксации фаз вьтолнения команды.

Устройство содержит (фиг.) блок фиксации фаз выполнения команды, шифраторы 2 адреса, блоки 3 памяти, дешифратор 4 и счетчик 5. На фиг.1 также показаны центральный процессор (ЦП) 6 и оперативное запоминающее устройство (ОЗУ 7.

БЛОК I фиксации фаз выполнения команды содержит счетчик 8, выходы 9 второй группы выходов блока, триггеры 10, дешифраторы II, выходы 12 первой группы выходов блока и входы 13 блока.

Устройство работает следующим образом.

ЦП 6 работает с уп кратным совмещением выполнения команд во времени. Все информационные регистры и триггеры управления ЦП 6 разбиты на р группы по признаку одновремзнного изменения информации в данной группе. Поэтому в каждый данный момент времени в память записывается р групп. Запись групп производится в блоке 3 и хранится до полного окончания обработки в устройстве центрального управления и арифметическом устройстве ЦП 6. Адреса записи формируются шифраторами 2. В качестве приз-to наков записи используются сигналы фа выполнения команды, поступающие на вход блока 1. Запись информации в блоки 3 осуществляется одновременно с изменением информации в группах Запись информации в блоки 3 производится по W уровням одновременно, так что в блоках памяти имеется полная информация состояния регистров устройства центрального управления и арифметического устройства ЦП 6 для всех m команд, находящихся в обработке в ЦП 6. При фиксации сбоя аппаратурой кон роля ЦП 6 работа последнего блокируется и вырабатывается сигнал запуска счетчика 5, сигнал с выхода которого одновременно используется как призна записи в ОЗУ 7. Счетчик 5 формирует адрес записи. В матрице триггеров 10 имеющей размерность tn х М , где m глубина совмещения выполнения команд |во времени, М - число раз обработки команд, производится выделение признаков записи, соответствукнщх каждой группе, записываемой в блоки 3, а также формирование признаков последней бессбойно завершенной команды. На входь 13 поступают из ЦП 6 сигналы фаз выполнения команд, которые с помощью дешифраторов 11 и счетчика 12 фиксируются в триггерах 10, а затем поступают .с выходов 9 в качест ве признаков записи групп в блоки 3. Начальные фазы команд фиксируются в первом столбце триггеров блока 1, последующие - в других столбцах триггеров 10. Сигнал, характеризующий окончанне обработки команды на уровне устройства центрального управления, фиксируется в последнем столбце триггеров 10 и используется в качестве признака бессбойно завершенной коман ды, этот сигнал с выходов 12 формиру ет адрес блока памяти, в котором хранится информация, соответствующая бессбойно завершенной команде. Информация из блоков памяти переписы82 .«. вается в ОЗУ 7, блокировка ЦП 6 снимается и производится программное восстановление информации регистров и триггеров управления информацией, соответствующей последней бессбойно завершенной команде. Затем производится повторное выполнение сбойного участка и, если сбой на зафиксирован, управление передается прерванной программе, а в случае наличия сбоя управления передается системным средствам восстановления. Таким образом, предлагаемое устройство позволяет определить последнюю бессбойно завершенную команду, а также сформировать с помощью шифраторов адресов сигналы, необходимые для записи информации, соответствующей командам, одновременно находящимся в обработке ЦП 6, в отдельные блоки памяти, и тем самым обеспечить возможность его применения в ЦВМ как второго, так и третьего поколения, а также осуществлять большой процент исправления ошибок, вызванных случайными сбоями, возникающими в процессе работы ЦВМ. Формула изобретения 1. Устройство для устранения последствий случайных сбоев, содержащее М блоков памяти, первые входы которых подключены к соответствующим выходам дешифратора и выходам первой группы выходов устройства, а выходы - к соответствующим выходам второй группы выходов устройства, и счетчик, выходом соединенный со входом дешифратора и выходом устройства, а входом-; со входом устройства, отличающееся тем,- что, с целью расширения области применения, в него введены М шифраторов адреса и блок фиксации фаз выполнения команды, причем вторые и третьи входы блоков памяти соединены с соответствующими входами первой и второй групп входов устройства, первая группа выходов блока фиксации фаз выполнения команды подключена к группам входов шифраторов адреса, группа входов - ко второй группе входов устройства, а вторая группа выходов - к первым входам соответствукмцих шифраторов адреса, второй вход и выход каждого из которых соединены соответственно с первым и четвертым входами одноименного блока памяти.

2. Устройство по п.I, отличающееся тем, что блок фиксации фаз выполнения команды содержит счетчик, М дешифраторов и М групп триггеров, причем вход i-го дешифратора (f -j, м; соединен с 1-ым входом группы входов блоки, группа входов - с выходами триггеров (-1)-ой группы, а (j-ый выход группы выходов (j с первым входом j -го триггера ) -ой группы и вторым входом j -го триггера () - -(/ -ой группы, второй вход j -го триггера М-ой группы соединен с первым входом J +1)-го триггера той же группы.

второй вход гп -го триггера М-ой группы соединен с первым входом первого триггера той же группы, выходы дешифраторов являются второй группой

выходов блока, вход и группа выходов счетчика подключены соответственно ко входу и группе входов первого дешифратора.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 544968, кл. G Об F 11/00, 1975.

2.Авторское свидетельство СССР Я 552608, кл, G 06 F 11/00, 1975

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Устройство для контроля следования модулей программы | 1985 |

|

SU1249521A1 |

| Устройство для сопряжения дисплея с цифровой вычислительной машиной (цвм) | 1983 |

|

SU1179353A1 |

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

Авторы

Даты

1981-11-30—Публикация

1980-02-11—Подача