Знак

г

fe/ eoctneeiM и мимудм- tatiHtut

(Л

с

sl

:л

/«.J

«.(

14 f

Miff

На

МЛ.

м

стью отводами, первую группу элементов И 3.1-3.N, элемент РШИ 4, RS- триггер 5, элементы И 6, 7 и 16, кольцевой регистр 8 сдвига, блок 9 управления, -N дополнительных групп элементов И 10,1-10.N, сумматор 11, цифро- аналоговый преобразователь 12, фильтр 13, N формирователей 14.1-14.N, генератор 15 сдвига, шины 17.1-17.2 уп-. равления Знак и выходную шину 18 фазовращателя. Работа блока 9 при отрицательном сдвиге фаз происходит

аналогично его работе при положительном сдвиге фаз. При этом с шин 17.1- и 17.2 знака RS-триггер 5 устанавливается в состояние 1. При отрицательном сдвиге обеспечивается обрат- ньш по отношению к положительному сдвигу порядок перехода от одной формы ступенчатого сигнала на выходе ци- фроаналогового преобразователя 12 .к другой его форме, т.е. происходит соответствующий сдвиг фазы. 1 з.п. ф-лы, 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Устройство для измерения параметров трехфазной сети | 1985 |

|

SU1307396A1 |

| Фазовращатель дискретного действия | 1981 |

|

SU1005272A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1365345A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

| Способ сдвига частоты @ сигнала | 1987 |

|

SU1383459A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

| Формирователь сложной функции | 1985 |

|

SU1287135A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах контролй, управления, синхронизации путем прецизионного изменения фазы сигнала. Целью изобретения является повьшение точности цифрового фазовращателя. Фазовращатель содержит задаюпщй генератор 1, линию 2 задержки, например, с ше

1

Изобретение относится к импульсной технике и предназначено для устройств контроля, управления и синхронизации путем прецизионного изменения фазы сигнала.

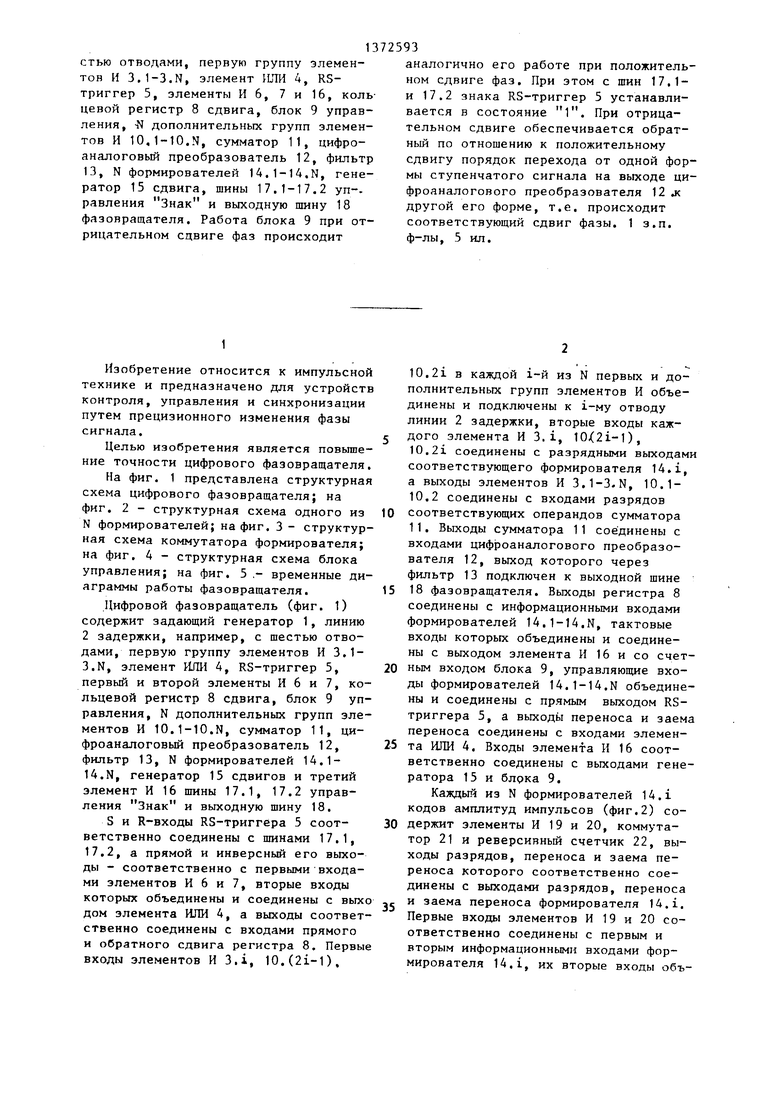

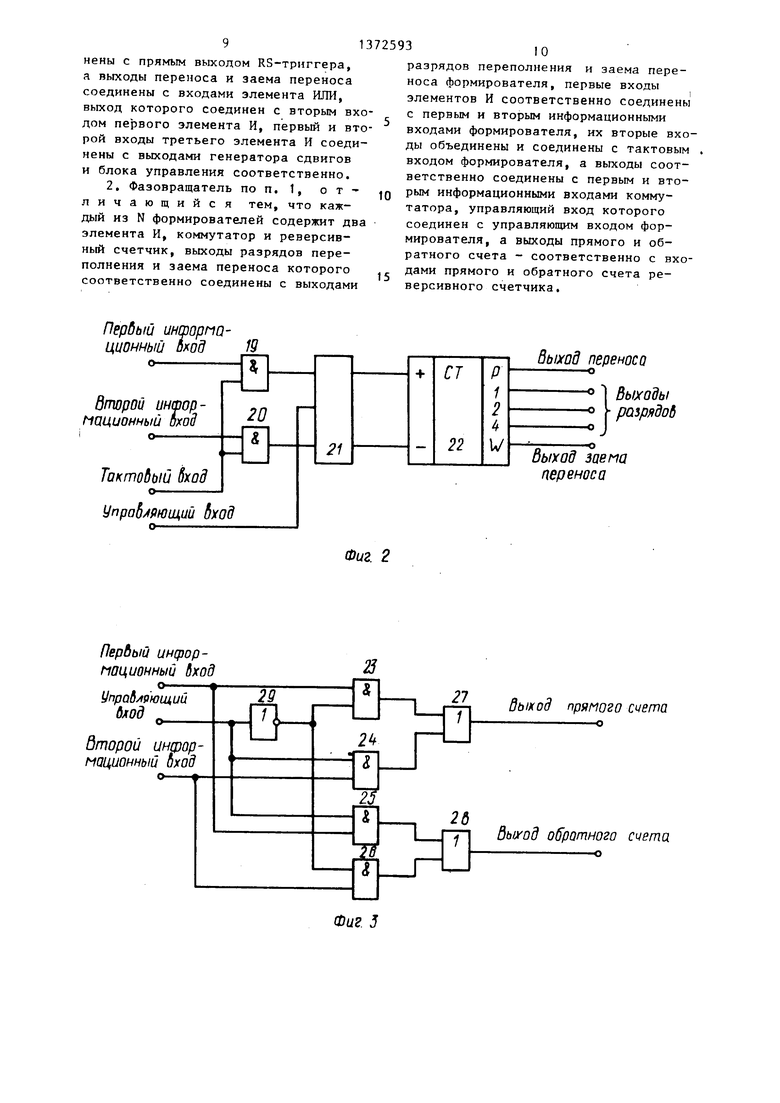

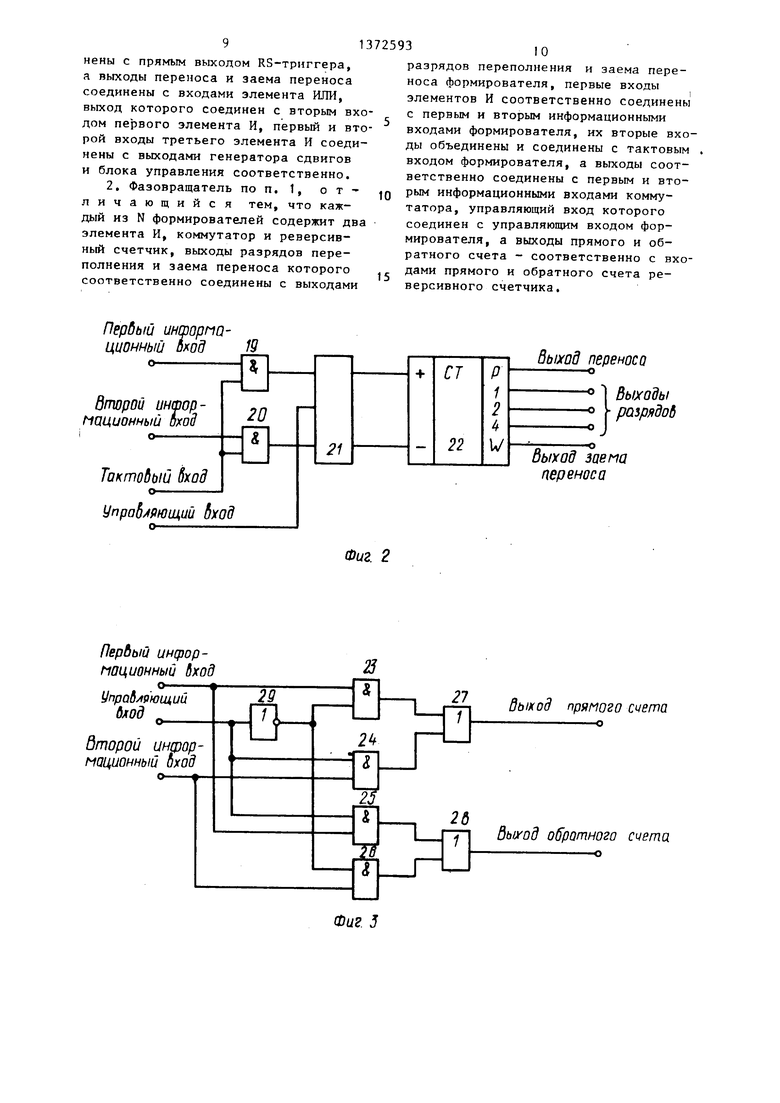

Целью изобретения является повьше- ние точности цифрового фазовращателя. На фиг. 1 представлена структурная схема цифрового фазовращателя; на фиг. 2 - структурная схема одного из N формирователей; на фиг. 3 - структурная схема коммутатора формирователя; на фиг. 4 - структурная схема блока управления; на фиг. 5 ,- временные диаграммы работы фазовращателя.

Цифровой фазовращатель (фиг. 1) содержит задающий генератор 1, линию 2 задержки, например, с шестью отводами, первую группу элементов И 3.1- 3.N, элемент ИЛИ 4, RS-триггер 5, первый и второй элементы И 6 и 7, кольцевой регистр 8 сдвига, блок 9 управления, N дополнительных групп элементов И 10.1-10.N, сумматор 11, ци- фроаналоговый преобразователь 12, фильтр 13, N формирователей 14.1- 14.N, генератор 15 сдвигов и третий элемент И 16 шины 17.1, 17.2 управления Знак и выходную шину 18.

S и R-входы RS-триггера 5 соответственно соединены с шинами 17.1, 17.2, а прямой и инверсный его выходы - соответственно с первыми входами элементов И 6 и 7, вторые входы которых объединены и соединены с вых дом элемента ИЛИ 4, а выходы соответственно соединены с входами прямого и обратного сдвига регистра 8. Первы входы элементов И 3.i, 10.(2i-1),

18 фазовращателя. Выходы регистра 8 соединены с информационными входами формирователей 14.1-14.N, тактовые входы которых объединены и соединены с выходом элемента И 16 и со счетным входом блока 9, управляющие входы формирователей 14.1-14.N объединены и соединены с прямым выходом RS- триггера 5, а вьгеоды переноса и заема переноса соединены с входами элемента ИЛИ 4. Входы элемента И 16 соответственно соединены с вькодами генератора 15 и блрка 9.

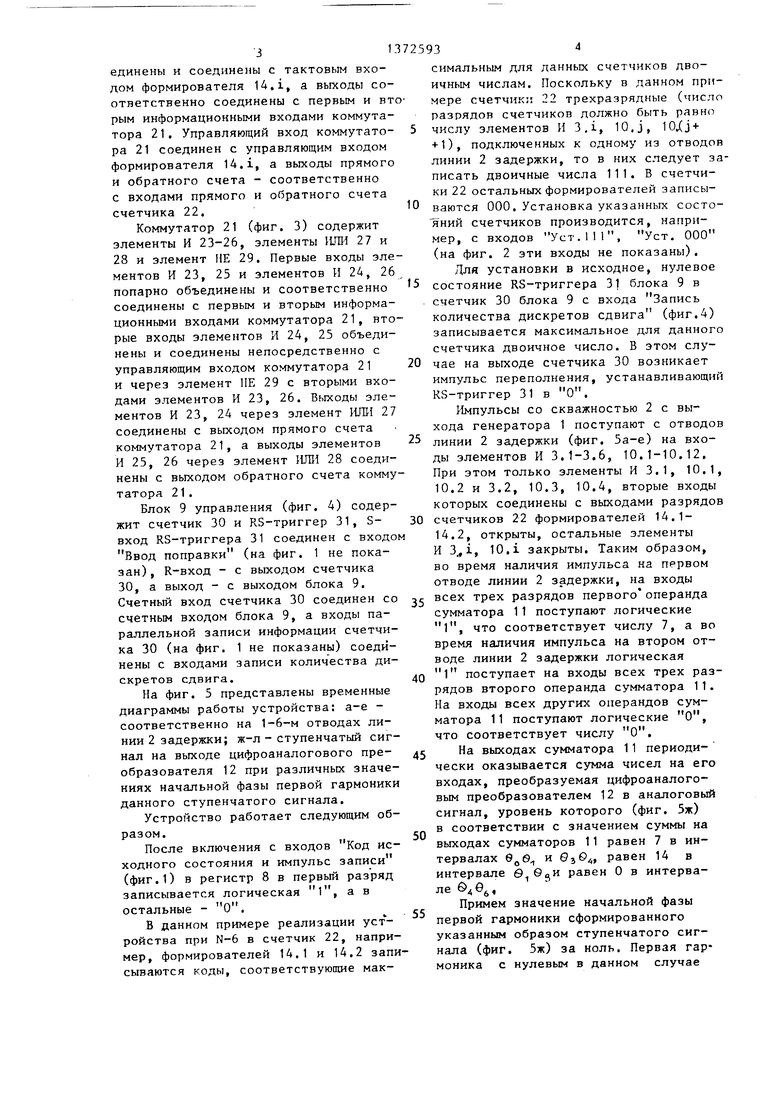

Каждьй из N формирователей 14.1 кодов амплитуд импульсов (фиг.2) содержит элементы И 19 и 20, коммутатор 21 и реверсивный счетчик 22, выходы разрядов, переноса и заема переноса которого соответственно соединены с выходами разрядов, переноса

и заема переноса формирователя 14.1. Первые входы элементов И 19 и 20 соответственно соединены с первым и вторым информационными входами формирователя 14.1, их вторые входы объ

единены и соединены с тактовым входом формирователя 14.i, а выходы соответственно соединены с первым и вт рым информационными входами коммутатора 21, Управляющий вход коммутатора 21 соединен с управляющим входом формирователя 14.1, а выходы прямого и обратного счета - соответственно с входами прямого и обратного счета счетчика 22,

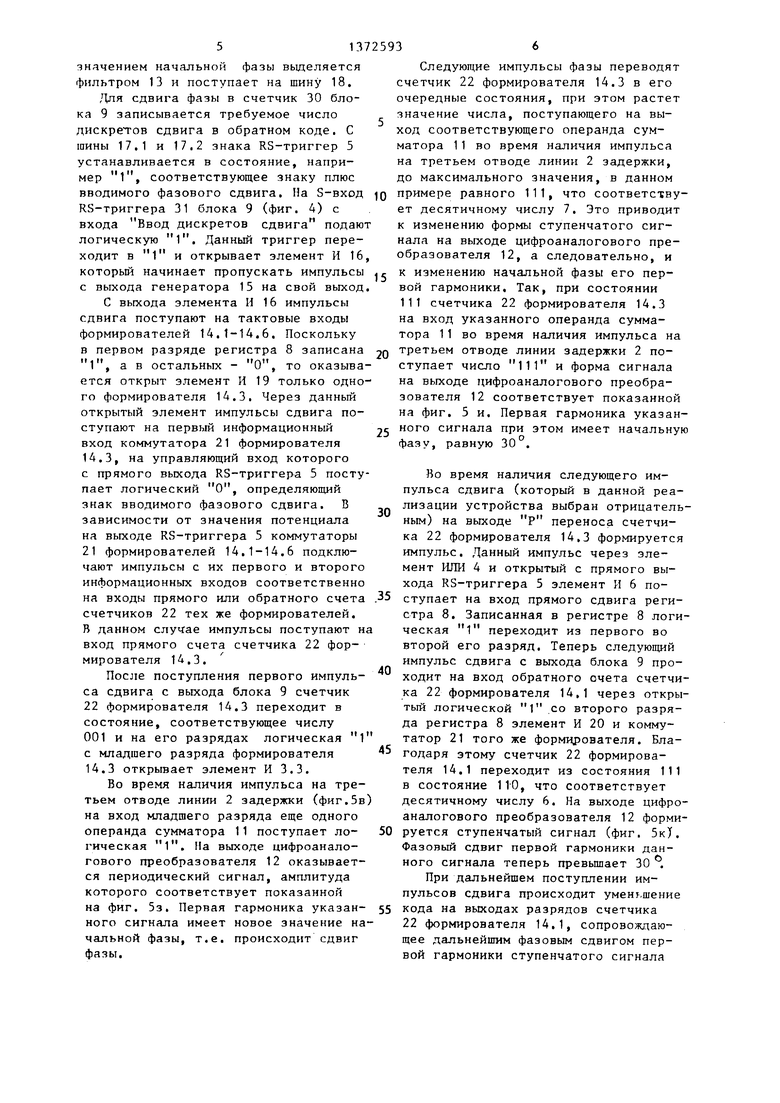

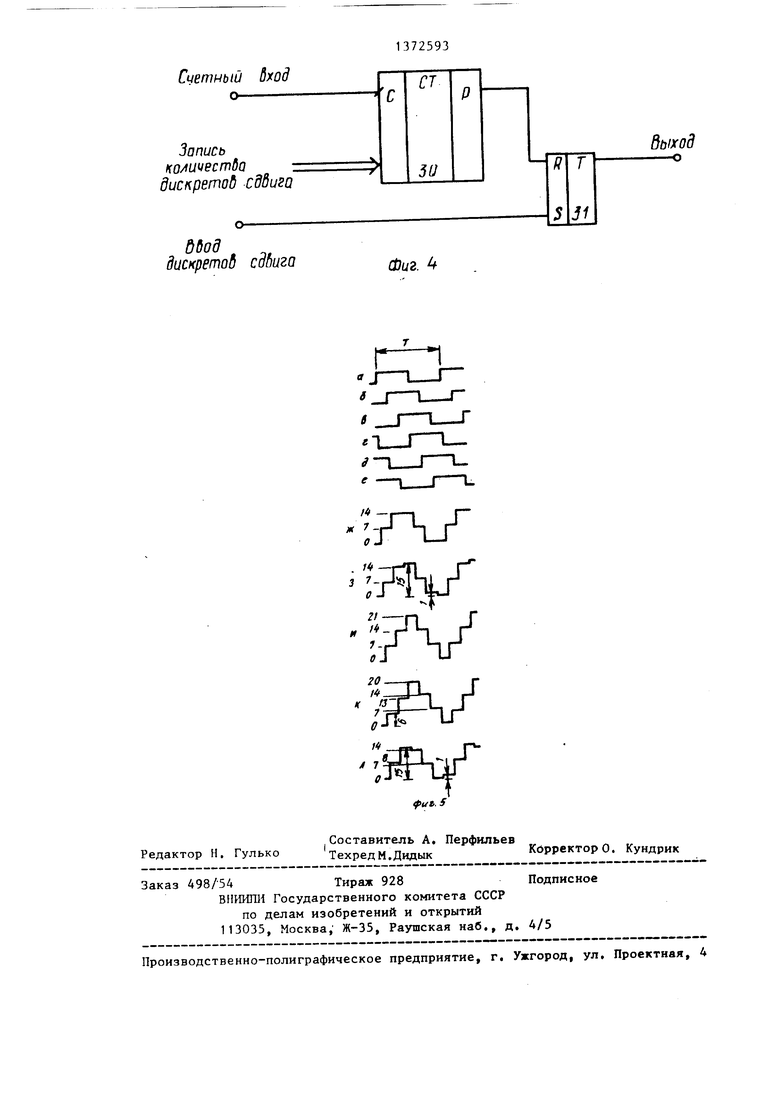

Коммутатор 21 (фиг, 3) содержит элементы И 23-26, элементы ИЛИ 27 и 28 и элемент НЕ 29, Первые входы элементов И 23, 25 и элементов И 24, 26 попарно объединены и соответственно соединены с первьм и вторым информационными входами коммутатора 21, вторые входы элементов И 24, 25 объединены и соединены непосредственно с управляющим входом коммутатора 21 и череэ элемент НЕ 29 с вторыми входами элементов И 23, 26, Выходы элементов И 23, 24 череэ элемент ИЛИ 27 соединены с выходом прямого счета коммутатора 21, а выходы элементов И 25, 26 через элемент ИЛИ 28 соединены с выходом обратного счета коммутатора 21 ,

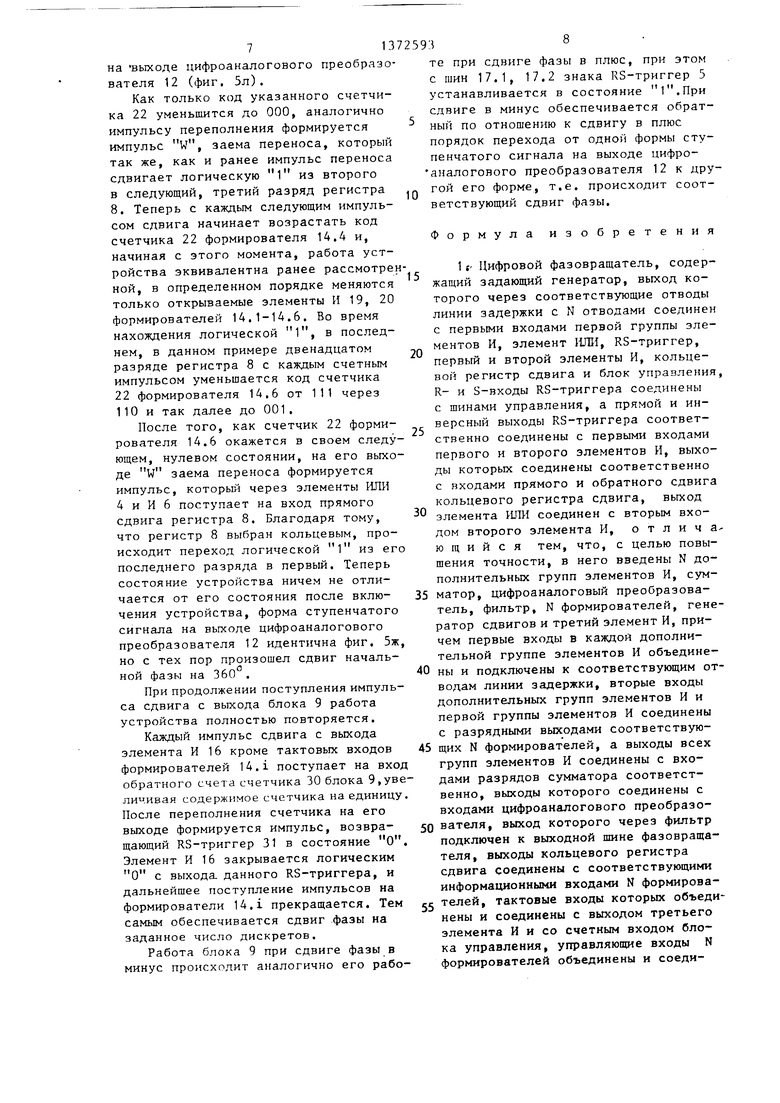

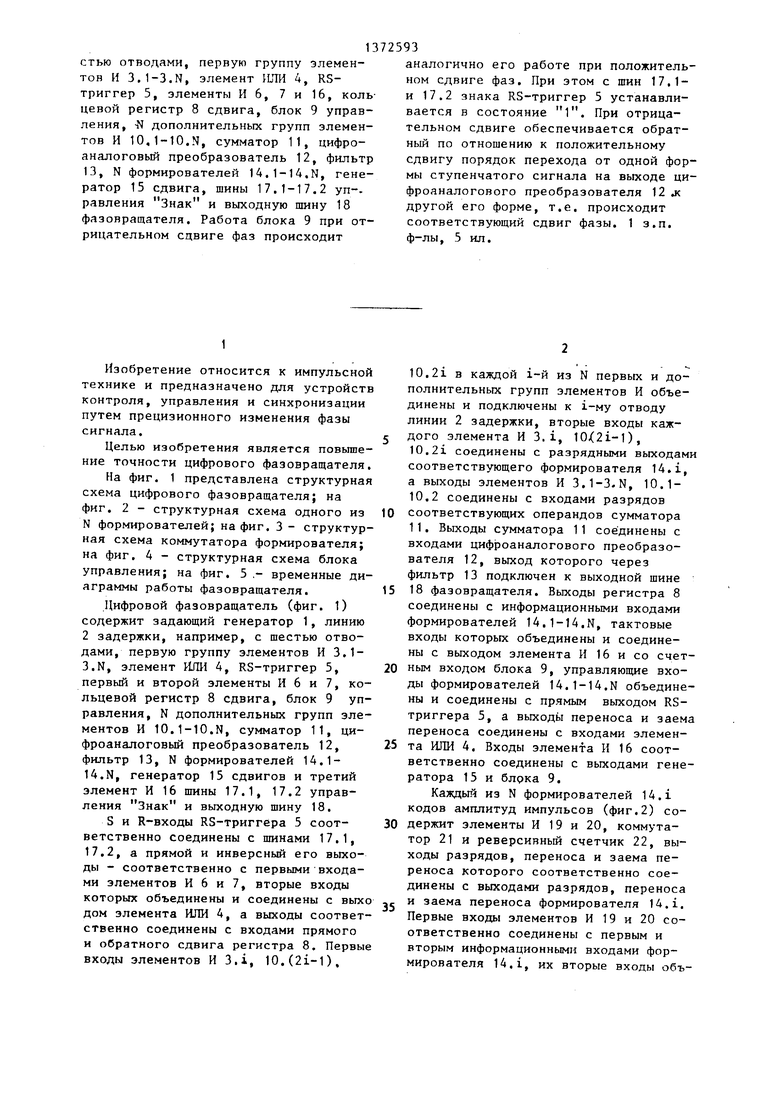

Блок 9 управления (фиг, 4) содержит счетчик 30 и Ру.5-триггер 31, S- вход RS-триггера 31 соединен с входо Ввод поправки (на фиг, 1 не показан) , R-вход - с выходом счетчика 30, а выход - с выходом блока 9, Счетный вход счетчика 30 соединен со счетньм входом блока 9, а входы параллельной записи информации счетчика 30 (на фиг, 1 не показаны) соединены с входами записи количества дискретов сдвига.

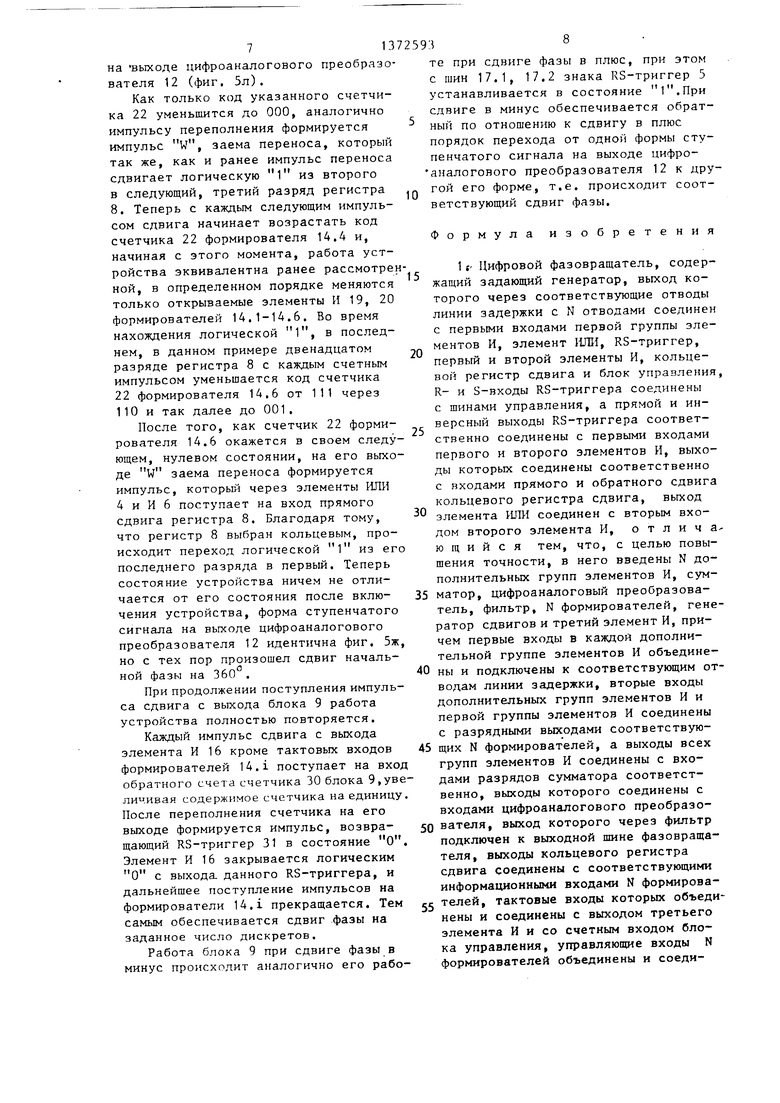

На фиг, 5 представлены временные диаграммы работы устройства: а-е - соответственно на 1-6-м отводах линии 2 задержки; ж-л - ступенчатый сигнал на выходе цифроаналогового преобразователя 12 при различных значениях начальной фазы первой гармоники данного ступенчатого сигнала.

Устройство работает следующим образом.

После включения с входов Код исходного состояния и импульс записи (фиг,1) в регистр 8 в первый разряд записывается логическая 1, а в остальные - О,

В данном примере реализации уст - ройства при N-6 в счетчик 22, например, формирователей 14,1 и 14,2 записываются коды, соответствующие мак

0

5

0

5

0

5

0

5

0

5

симальным для данных счетчиков двоичным числам. Поскольку в данном примере счетчик:: 22 трехразрядные (число разрядов счетчиков должно быть равно числу элементов И 3,1, 10.J, +1), подключенных к одному из отводов линии 2 задержки, то в них следует записать двоичные числа 111, В счетчики 22 остальных формирователей записываются 000, Установка указанных состо- яний счетчиков производится, например, с входов Уст. 111, Уст. 000 (на фиг, 2 эти входы не показаны),

Для установки в исходное, нулевое состояние RS-триггера 31 блока 9 в счетчик 30 блока 9 с входа Запись количества дискретов сдвига (фиг,4) записывается максимальное для данного счетчика двоичное число. В этом случае на выходе счетчика 30 возникает импульс переполнения, устанавливающий RS-триггер 31 в О,

Импульсы со скважностью 2 с выхода генератора 1 поступают с отводов линии 2 задержки (фиг, 5а-е) на входы элементов И 3,1-3,6, 10,1-10,12, При этом только элементы И 3,1, 10,1, 10,2 и 3,2, 10,3, 10,4, вторые входы которых соединены с выходами разрядов счетчиков 22 формирователей 14,1- 14,2, открыты, остальные элементы И , 10,1 закрыты. Таким образом, во время наличия импульса на первом отводе линии 2 задержки, на входы всех трех разрядов первого операнда сумматора 11 поступают логические 1, что соответствует числу 7, а во время наличия импульса на втором отводе линии 2 задержки логическая 1 поступает на входы всех трех разрядов второго операнда сумматора 11. На входы всех других операндов сумматора 11 поступают логические О, что соответствует числу О,

На выходах сумматора 11 периодически оказывается сумма чисел на его входах, преобразуемая цифроаналого- вым преобразователем 12 в аналоговый сигнал, уровень которого (фиг, 5ж) в соответствии с значением суммы на выходах сумматоров 11 равен 7 в интервалах и , равен 14 в интервале равен О в интервале ©,е.

Примем значение начальной фазы первой гармоники сформированного указанным образом ступенчатого сигнала (фиг, 5ж) за ноль. Первая гармоника с нулевым в данном случае

значением начальной фазы выделяется фильтром 13 и поступает на шину 18.

Лия сдвига фазы в счетчик 30 блока 9 записывается требуемое число дискретов сдвига в обратном коде. С шины 17.1 и 17.2 знака RS-триггер 5 устанавливается в состояние, например 1, соответствующее знаку плюс

вводимого фазового сдвига. На S-вход ю примере равного 111, что соответству- RS-триггера 31 блока 9 (фиг. 4) с ет десятичному числу 7. Это приводит входа Ввод дискретов сдвига подают к изменению формы ступенчатого сиг- логическую 1. Данный триггер пере- нала на выходе цифроаналогового преходит в 1 и открывает элемент И 16, образователя 12, а следовательно, и который начинает пропускать импульсы г к изменению начальной фазы его пер- с выхода генератора 15 на свой выход.

С выхода элемента И 16 импульсы сдвига поступают на тактовые входы формирователей 14.1-14.6. Поскольку

вой гармоники. Так, при состоянии 111 счетчика 22 формирователя 14.3 на вход указанного операнда сумматора 11 во время наличия импульса на

в первом разряде регистра 8 записана 20 третьем отводе линии задержки 2 по1

а в остальных - О , то оказываступает число 111 и форма сигнала на выходе цифроаналогового преобразователя 12 соответствует показанно на фиг. 5 и. Первая гармоника указа 25 ного сигнала при этом имеет начальну фазу, равную 30°.

ется открыт элемент И 19 только одного формирователя 14.3. Через данный открытый элемент импульсы сдвига поступают на первый информационный вход коммутатора 21 формирователя 14.3, на управляющий вход которого с прямого выхода RS-триггера 5 поступает логический О, определяющий знак вводимого фазового сдвига. В зависимости от значения потенциала на выходе RS-триггера 5 коммутаторы 21 формирователей 14.1-14.6 подключают импульсы с их первого и второго информационных входов соответственно

ступает число 111 и форма сигнала на выходе цифроаналогового преобразователя 12 соответствует показанной на фиг. 5 и. Первая гармоника указан- 25 ного сигнала при этом имеет начальную фазу, равную 30°.

30

Во время наличия следующего импульса сдвига (который в данной реализации устройства выбран отрицательным) на выходе Р переноса счетчика 22 формирователя 14.3 формируется импульс. Данный импульс через элемент ИЛИ 4 и открытый с прямого выхода RS-триггера 5 элемент И 6 по- на входы прямого или обратного счета .35 ступает на вход прямого сдвига реги- счетчиков 22 тех же формирователей. стра 8. Записанная в регистре 8 логи- В данном случае импульсы поступают на вход прямого счета счетчика 22 формирователя 14.3.

После поступления первого импульса сдвига с выхода блока 9 счетчик 22 формирователя 14.3 переходит в состояние, соответствующее числу 001 и на его разрядах логическая 1 с младшего разряда формирователя 14.3 открьгаает элемент И 3.3.

Во время наличия импульса на третьем отводе линии 2 задержки (фиг.5в) на вход младшего разряда еще одного операнда сумматора 11 поступает логическая 1. На выходе цифроаналогового преобразователя 12 оказывается периодический сигнал, амплитуда

40

ческая 1 переходит из первого во второй его разряд. Теперь следующий импульс сдвига с выхода блока 9 проходит на вход обратного счета счетчика 22 формирователя 14,1 через открытый логической 1 со второго разряда регистра В элемент И 20 и коммутатор 21 того же формирователя. Бла45 годаря этому счетчик 22 формирователя 14.1 переходит из состояния 111 в состояние 1VO, что соответствует десятичному числу 6. На выходе цифро- аналогового преобразователя 12 форми50 руется ступенчатый сигнал (фиг. 5кТ. Фазовый сдвиг первой гармоники данного сигнала теперь превьшает 30 ,

которого соответствует показанной

При дальнейшем поступлении импульсов сдвига происходит уменьшение на фиг. 5з. Первая гармоника указан- 55 кода на выходах разрядов счетчика ного сигнала имеет новое значение на- 22 формирователя 14.1, сопровождаю- чальной фазы, т.е. происходит сдвиг щее дальнейшим фазовым сдвигом пер- фазы.вой гармоники ступенчатого сигнала

25936

Следующие импульсы фазы переводят счетчик 22 формирователя 14.3 в его очередные состояния, при этом растет значение числа, поступающего на выход соответствующего операнда сумматора 11 во время наличия импульса на третьем отводе линии 2 задержки, до максимального значения, в данном

примере равного 111, что соответству- ет десятичному числу 7. Это приводит к изменению формы ступенчатого сиг- нала на выходе цифроаналогового преобразователя 12, а следовательно, и к изменению начальной фазы его пер-

вой гармоники. Так, при состоянии 111 счетчика 22 формирователя 14.3 на вход указанного операнда сумматора 11 во время наличия импульса на

третьем отводе линии задержки 2 поступает число 111 и форма сигнала на выходе цифроаналогового преобразователя 12 соответствует показанной на фиг. 5 и. Первая гармоника указан- ного сигнала при этом имеет начальную фазу, равную 30°.

Во время наличия следующего импульса сдвига (который в данной реализации устройства выбран отрицательным) на выходе Р переноса счетчика 22 формирователя 14.3 формируется импульс. Данный импульс через элемент ИЛИ 4 и открытый с прямого выхода RS-триггера 5 элемент И 6 по- 5 ступает на вход прямого сдвига реги- стра 8. Записанная в регистре 8 логи-

0

ческая 1 переходит из первого во второй его разряд. Теперь следующий импульс сдвига с выхода блока 9 проходит на вход обратного счета счетчика 22 формирователя 14,1 через открытый логической 1 со второго разряда регистра В элемент И 20 и коммутатор 21 того же формирователя. Бла5 годаря этому счетчик 22 формирователя 14.1 переходит из состояния 111 в состояние 1VO, что соответствует десятичному числу 6. На выходе цифро- аналогового преобразователя 12 форми0 руется ступенчатый сигнал (фиг. 5кТ. Фазовый сдвиг первой гармоники данного сигнала теперь превьшает 30 ,

на выходе цифроаналогового преобразователя 12 (фиг. 5л).

Как только код указанного счетчика 22 уменьшится до 000, аналогично импульсу переполнения формируется импульс W, заема переноса, который так же, как и ранее импульс переноса сдвигает логическую 1 из второго в следующий, третий разряд регистра 8. Теперь с каждым следующим импульсом сдвига начинает возрастать код счетчика 22 формирователя 14.4 и, начиная с этого момента, работа устройства эквивалентна ранее рассмотреной, в определенном порядке меняются только открываемые элементы И 19, 20 формирователей 14.1-14.6. Во время нахождения логической 1, в последнем, в данном примере двенадцатом разряде регистра 8 с каждым счетным импульсом уменьшается код счетчика 22 формирователя 14.6 от 111 через 110 и так далее до 001.

После того, как счетчик 22 формирователя 14.6 окажется в своем следующем, нулевом состоянии, на его выходе W заема переноса формируется импульс, который через элементы ИЛИ 4 и И 6 поступает на вход прямого сдвига регистра 8. Благодаря тому, что регистр 8 выбран кольцевым, происходит переход логической 1 из ег последнего разряда в первый. Теперь состояние устройства ничем не отличается от его состояния после включения устройства, форма ступенчатого сигнала на выходе цифроаналогового преобразователя 12 идентична фиг. 5ж но с тех пор произошел сдвиг начальной фазы на 360 .

При продолжении поступления импульса сдвига с выхода блока 9 работа устройства полностью повторяется.

Каждый импульс сдвига с выхода элемента И 16 кроме тактовых входов формирователей 14.i поступает на вход обратного счета счетчика 30 блока 9,увеличивая содержимое счетчика на единицу После переполнения счетчика на его выходе формируется импульс, возвращающий RS-триггер 31 в состояние О Элемент И 16 закрывается логическим О с выхода, данного RS-триггера, и дальнейшее поступление импульсов на

формирователи 14.1 прекращается. Тем « телей, тактовые входы которых объедисамым обеспечивается сдвиг фазы на заданное число дискретов.

Работа блока 9 при сдвиге фазы в минус происходит аналогично его рабонены и соединены с выходом третьего элемента И и со счетным входом блока управления, управляющие входы N формирователей объединены и соеди

5

0

5

те при сдвиге фазы в плюс, при этом с шин 17.1, 17.2 знака RS-триггер 5 устанавливается в состояние 1.При сдвиге в минус обеспечивается обратный по отношению к сдвигу в плюс порядок перехода от одной формы ступенчатого сигнала на выходе цифро- аналогоного преобразователя 12 к другой его форме, т.е. происходит соответствующий сдвиг фазы.

Формула изобретения

1 { Цифровой фазовращатель, содержащий задающий генератор, выход которого через соответствующие отводы линии задержки с N отводами соединен с первыми входами первой группы элементов И, элемент ИЛИ, RS-триггер, первый и второй элементы И, кольцевой регистр сдвига и блок управления, R- и S-входы RS-триггера соединены с шинами управления, а прямой и инверсный выходы RS-триггера соответственно соединены с первыми входами первого и второго элементов И, выходы которых соединены соответственно с входами прямого и обратного сдвига кольцевого регистра сдвига, выход элемента ИЛИ соединен с вторым входом второго элемента И, о т л и ч а ю щ и и с я тем, что, с целью повышения точности, в него введены N дополнительных групп элементов И, сум5 матор, цифроаналоговый преобразователь, фильтр, N формирователей, генератор сдвигов и третий элемент И, причем первые входы в каждой дополнительной группе элементов И объедине0 ны и подключены к соответствующим отводам линии задержки, вторые входы дополнительных групп элементов И и первой группы элементов И соединены с разрядными выходами соответствую5 щих N формирователей, а выходы всех групп элементов И соединены с входами разрядов сумматора соответственно, выходы которого соединены с входами цифроаналогового преобразо0 вателя, выход которого через фильтр подключен к выходной шине фазовращателя, выходы кольцевого регистра сдвига соединены с соответствующими информационными входами N формирова0

нены и соединены с выходом третьего элемента И и со счетным входом блока управления, управляющие входы N формирователей объединены и соеди913

нены с прямым выходом RS-трнггера, а выходы переноса и заема переноса соединены с входами элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, первый и второй входы третьего элемента И соединены с выходами генератора сдвигов и блока управления соответственно.

Пербый инторпоПербый инсрор- национный бход

Упраб р ющий блод

дторой информационный Ь)сод

Фиг. J

0

5

10

разрядов переполнения и эаема переноса формирователя, первые входы элементов И соответственно соединены с первым и вторым информационными входами формирователя, их вторые входы объединены и соединены с тактовым входом формирователя, а выходы соответственно соединены с первым и вторым информационными входами коммутатора, управляющий вход которого соединен с управляющим входом формирователя, а выходы прямого и обратного счета - соответственно с входами прямого и обратного счета реверсивного счетчика.

Фиг. 2

Выход прямого

о

дыуод оборотного счета

о

ввод дискретов coftuza

Редактор Н. Гулько

W ,я

ut.f

Составитель А, Перфильев

Техред М.ДидыкКорректор О. Кундрик

Фиг. 4

W ,я

ut.f

| Смолов В.Б | |||

| Функциональные преобразователи информации.-Л.: Энерго- издат, 1981 | |||

| Устройство ввода поправок в хранительВРЕМЕНи | 1979 |

|

SU824118A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-02-07—Публикация

1986-06-10—Подача