Область техники, к которой относится изобретение

Настоящее изобретение относится к технике генерирования электрических колебаний, а именно к измерительным генераторам парных сигналов произвольной формы с программируемой задержкой между ними.

Уровень техники

Генераторы парных сигналов заданной формы, разделенных определенным интервалом времени, находят применение в измерительной технике, системах передачи информации, устройствах управления вращающимися трансформаторами, системах квадратурной обработки сигналов. Схемотехника таких генераторов сочетает аналоговые и цифровые способы обработки сигналов.

Известен генератор двухфазных гармонических сигналов [1], содержащий триггер, инвертор, формирователь импульсных последовательностей, пару сумматоров, первый, фильтры нижних частот, повторители напряжения, первый, элементы отрицательной обратной связи, усилители мощности и блок ограничителей тока. Данное устройство способно генерировать несколько квадратурных гармонических сигналов в заданном фазовом отношении. Недостатком этого устройства заключается в невозможности получения произвольной формы сигналов и изменения фазового сдвига между ними.

Аналогом настоящего изобретения является также двухфазный генератор гармонических сигналов [2], состоящий из задающего частоту мультивибратора, распределителя импульсов, нагруженного на два блока ключей, соединенных с многоуровневым источником постоянных напряжений, и выходных фильтров нижних частот. Блоки ключей, соединенные с многоуровневым источником постоянных напряжений представляют собой, по сути, аналого-цифровые преобразователи. В данном аналоге предусмотрена возможность регулирования фазового сдвига между генерируемыми сигналами. Однако функциональные возможности устройства ограничены, поскольку оно рассчитано на генерирование исключительно гармонических сигналов.

Общим недостатком известных двухфазных генераторов является низкая точность частоты вырабатываемых сигналов, отсутствие возможности ее электронной перестройки и выработки сигналов произвольной формы.

Указанные недостатки в значительной мере смягчаются в устройствах, принцип действия которых основан на цифровом синтезе сигналов.

Известен генератор двухфазных гармонических сигналов [3], содержащий триггер, инвертор, формирователь импульсных последовательностей, первый и второй сумматоры, первый, второй, третий и четвертый активные фильтры нижних частот второго порядка, первый и второй повторители напряжения, первый, второй, третий и четвертый элементы отрицательной обратной связи, первый, второй, третий и четвертый усилители мощности, блок ограничителей тока, первый, второй, третий и четвертый элементы частотной коррекции, первую, вторую, третью и четвертую снабберные цепочки. Данное устройство обеспечивает высокую точность частоты и фазового отношения генерируемых синусно-косинусных пар сигналов. Однако, данное устройство не способно генерировать сигналы произвольной формы и не допускают регулирования фазовых отношений между сигналами.

Известен также цифровой синтезатор многофазных сигналов [4], содержащий последовательно соединенные первый регистр памяти, первый цифровой накопитель, второй цифровой накопитель, первый преобразователь кодов, первый цифроаналоговый преобразователь, первый фильтр низких частот; последовательно соединенные второй регистр памяти и делитель частоты с переменным коэффициентом деления; последовательно соединенные генератор тактовых импульсов и блок задержки; последовательно соединенные первый инвертор, второй цифроаналоговый преобразователь, второй фильтр низких частот; причем выход делителя частоты с переменным коэффициентом деления подключен к входу первого цифрового накопителя, выходы блока задержки подсоединены к тактовому входу делителя частоты с переменным коэффициентом деления, к тактовому входу первого и к тактовому входу второго цифровых накопителей, к тактовому входу первого и к тактовому входу второго цифроаналоговых преобразователей; старший разряд второго цифрового накопителя подключен к входу управления инверсией первого преобразователя кодов, при этом с выхода первого преобразователя кодов сигналы старших разрядов через инвертор поступают на информационные входы второго цифроаналогового преобразователя; первым и вторым входами цифрового синтезатора многофазных сигналов являются входы первого и второго регистров памяти, а первым и вторым выходами цифрового синтезатора многофазных сигналов - выходы первого и второго фильтров низких частот. Для расширения функциональных возможностей устройства в него введены дополнительно последовательно соединенные третий регистр памяти, сумматор, второй преобразователь кодов, третий цифроаналоговый преобразователь, третий фильтр низких частот; последовательно соединенные второй инвертор, четвертый цифроаналоговый преобразователь, четвертый фильтр низких частот; кроме того, выход второго цифрового накопителя подключен к входу сумматора, а старший разряд сумматора подключен к входу управления инверсией второго преобразователя кодов; выход второго преобразователя кодов подключен к входу второго инвертора, выходы блока задержки подсоединены к тактовому входу третьего и тактовому входу четвертого цифроаналоговых преобразователей, причем вход третьего регистра памяти является третьим входом цифрового синтезатора многофазных сигналов, а третьим и четвертым выходами цифрового синтезатора многофазных сигналов являются выходы третьего и четвертого фильтров низких частот.

Недостатком данного аналога является его сложность и отсутствие возможности регулировать время задержки между генерируемыми сигналами.

Наиболее близкой по технической сущности к предполагаемому изобретению является базовая схема прямого цифрового синтезатора частоты, представленная в многочисленных публикациях, в частности, приведенная на рисунке 4 в статье Л. Ридико «DDS: прямой цифровой синтез частоты / Компоненты и технологии. - 2001, № 7» [5]. Устройство-прототип содержит последовательно соединенные многоразрядный сумматор, регистр хранения, постоянное запоминающее устройство, цифроаналоговый преобразователь и фильтр нижних частот, выход которого является выходом сигнала, причем цифровой выход регистра хранения, у которого тактовый вход соединен с выходом тактового генератора, подключен к цифровому входу первого слагаемого многоразрядного сумматора, второй цифровой вход которого является входом кода управления частотой сигналов. Многоразрядный сумматор с обратной связью по первому цифровому входу через регистр хранения образует накапливающий сумматор (аккумулятор). Данное устройство отличается высокой точностью и быстродействием при установлении частоты, и благодаря возможности программирования постоянного запоминающего устройства имеет возможность генерировать сигналы произвольной формы.

Устройство-прототип имеет единственный выход сигнала и не способно генерировать пару сигналов одинаковой формы, смещенных друг относительно другу на заданный интервал времени. Это является его недостатком.

Раскрытие сущности изобретения

Целью настоящего изобретения является расширение функциональных возможностей путем генерирования двух сигналов произвольной формы с заданной задержкой между ними, перестраиваемой цифровым способом.

Указанная цель достигается введением в устройство прямого цифрового синтеза частоты, состоящее из последовательно соединенных первых многоразрядного сумматора, регистра хранения, постоянного запоминающего устройства, цифроаналогового преобразователя и фильтра нижних частот, выход которого является выходом первого сигнала, причем цифровой выход первого регистра хранения, у которого тактовый вход соединен с выходом тактового генератора, подключен к цифровому входу первого слагаемого первого многоразрядного сумматора, второй цифровой вход которого является входом кода управления частотой сигналов, дополнительных вторых последовательно соединенных многоразрядного сумматора, регистра хранения, постоянного запоминающего устройства, цифроаналогового преобразователя и фильтра нижних частот. При этом выход фильтра нижних частот служит выходом второго сигнала, цифровой вход первого слагаемого второго многоразрядного сумматора подключен к цифровому выходу первого многоразрядного сумматора, а его цифровой вход второго слагаемого - к цифровому входу кода задержки между сигналами, тактовый вход второго регистра хранения соединен с выходом тактового генератора.

По существу, устройство-прототип дополнено вторым каналом формирования сигнала той же формы, что и в основном канале, в котором нет аккумулятора - нет обратной связи второго регистра хранения с цифровым входом второго многоразрядного сумматора. Назначение второго многоразрядного сумматора состоит в добавлении к содержимому первого многоразрядного сумматора цифрового кода, определяющего время задержки первого сигнала относительно второго сигнала.

Краткое описание чертежей

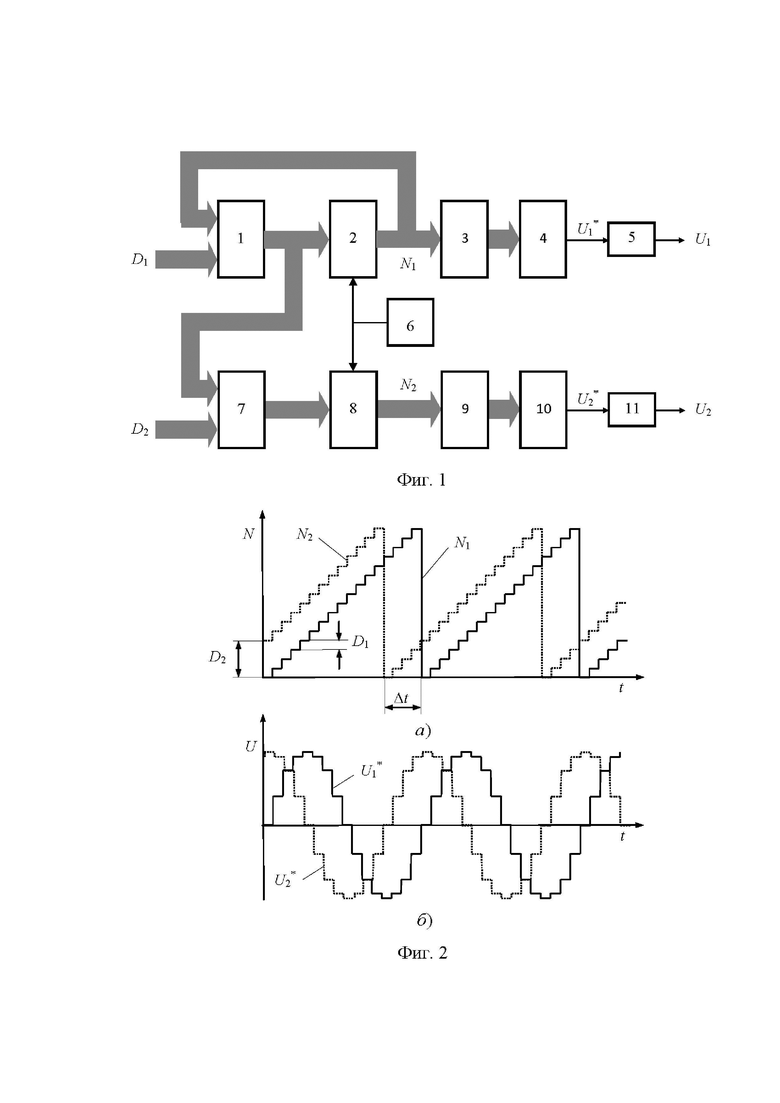

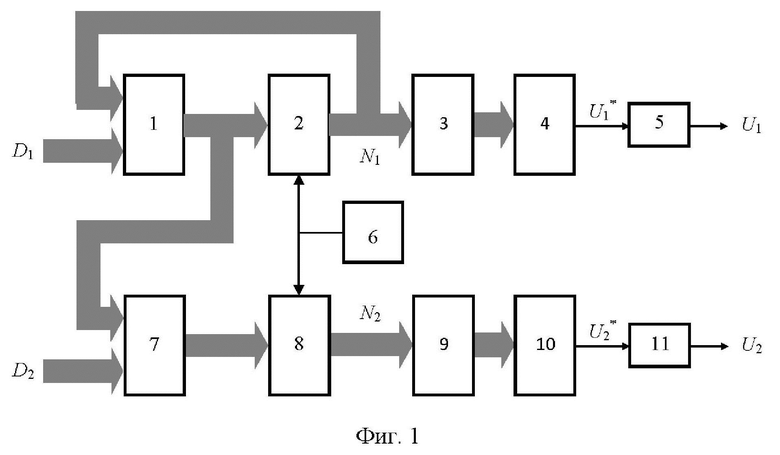

На фиг. 1 представлена функциональная электрическая схема генератора парных сигналов произвольной формы в соответствии с настоящим изобретением.

На фиг. 2 изображены временные диаграммы сигналов в характерных узлах генератора парных сигналов произвольной формы.

Осуществление изобретения

Представленная на фиг. 1 функциональная схема генератора парных сигналов произвольной формы содержит два составленных из идентичных узлов канала формирования сигнала.

Первый канал включает последовательно соединенные первый многоразрядный сумматор 1, первый регистр 2 хранения, первое постоянное запоминающее устройство (ПЗУ) 3, первый цифроаналоговый преобразователь (ЦАП) 4 и первый фильтр нижних частот (ФНЧ) 5, выход которого является выходом первого из генерируемых сигналов. Тактовый вход первого регистра 2 хранения подключен к выходу тактового генератора 6, а его цифровой выход - к входу первого слагаемого первого многоразрядного сумматора, второй цифровой вход которого служит входом кода управления частотой сигналов. Первый многоразрядный сумматор 1 и первый регистр 2 хранения с описанными связями образуют в совокупности накапливающий сумматор (аккумулятор).

Второй канал сдержит последовательно соединенные второй многоразрядный сумматор 7, второй регистр 8 хранения, второе ПЗУ 9, второй ЦАП 10 и второй ФНЧ 11, выход которого является выходом второго генерируемого сигнала. Тактовый вход второго регистра 8 хранения подключен к выходу тактового генератора 6. Цифровой вход первого слагаемого второго многоразрядного сумматора 7 соединен с цифровым выходом первого многоразрядного сумматора 1, а его второй цифровой вход служит входом кода задержки между сигналами.

Все цифровые узлы устройства являются n-разрядными: многоразрядные сумматоры 1 и 7 имеют n-разрядные первый и второй цифровые входы и n-разрядные цифровые выходы; регистры 2 и 8 хранения состоят из n разрядов, ПЗУ 3 и 9 имеют по n адресных входов и, следовательно, по 2n ячеек памяти, причем содержимое соответствующих ячеек памяти обоих ПЗУ идентично и отражает цифровые образы генерируемых сигналов, которые путем программирования ПЗУ могут задаваться произвольно.

Показанные на фиг. 2, а и 2, б временные диаграммы сигналов иллюстрируют работу устройства. Обозначения внутренних сигналов устройства имеют индексы 1 и 2, соответствующие номеру канала формирования сигнала. Фиг. 2, а иллюстрирует динамику линейного нарастания содержимого первого 2 (N1) и второго 8 (N2) регистров хранения, которое происходит ступеньками в моменты их тактирования. На фиг. 2, б представлены формы напряжений, образующихся на выходах первого 4 (U1*) и второго 10 (U2*) ЦАП. Сигналограммы второго канала показаны точечными линиями. Для примера форма генерируемых сигналов выбрана синусоидальной.

Первый канал устройства работает абсолютно так же, как работает устройство-прототип. Аккумулятор в составе первого многоразрядного сумматора 1 и первого регистра 2 хранения в каждом такте, задаваемом тактовым генератором 6, добавляет к текущему двоичному числу N1 инкремент D1 с входа кода управления частотой сигнала. В результате увеличения адреса первого ПЗУ 3 на его выход выводится хранящееся по этому адресу содержимое ячейки памяти, соответствующее цифровому эквиваленту точки синусоиды, которое с помощью первого ЦАП 4 преобразуется в ступенчато изменяющееся напряжение U1*. Полученное напряжение далее сглаживается первым ФНЧ 5 и выводится в качестве первого генерируемого сигнала. Частота следования сигналов равна частоте переполнения первого многоразрядного сумматора 1 и определяется выражением

,

,

где n - разрядность сумматора и регистра хранения,  - частота импульсов тактового генератора 6,

- частота импульсов тактового генератора 6,  - входной код управления частотой.

- входной код управления частотой.

Формирование сигнала во втором канале устройства происходит в том же порядке, однако адрес второго ПЗУ 9 формируется путем добавления к содержимому первого многоразрядного сумматора 1 N1 кода задержки между сигналами  , т.е. этот адрес оказывается равным

, т.е. этот адрес оказывается равным  . Поскольку содержимое обоих ПЗУ 4 и 10 идентично, то из ячейки памяти второго ПЗУ 9 на второй ЦАП 10 выводится число, которое соответствует точке синусоиды, сдвинутой в сторону опережения на

. Поскольку содержимое обоих ПЗУ 4 и 10 идентично, то из ячейки памяти второго ПЗУ 9 на второй ЦАП 10 выводится число, которое соответствует точке синусоиды, сдвинутой в сторону опережения на  тактов, т.е. во времени на

тактов, т.е. во времени на  .

.

Таким образом, предлагаемое устройство генерирует пару сигналов одинаковой формы, назначаемой прошивкой ПЗУ, смещение во времени между которыми можно регулировать, изменяя цифровой код задержки между сигналами. Пол сравнению с прототипом эта возможность означает расширение функциональных возможностей устройства.

Литература

1. Генератор двухфазных гармонических сигналов. Патент РФ 2737004, МПК Н03В 27/00, опубл. 24.11.2020.

2. Двухфазный генератор гармонических сигналов. Авторское свидетельство СССР 1084941, МПК Н03В 27/00, опубл. 7.04.1984.

3. Двухфазный генератор гармонических сигналов. Патент РФ 2761109, МПК Н03В 7/00, опубл. 06.12.2021.

4. Цифровой синтезатор многофазных сигналов. Патент РФ 2423782, МПК Н03L 27/00, опубл. 10.07.2011.

5. Леонид Ридико. DDS: прямой цифровой синтез частоты / Компоненты и технологии. - 2001. - № 7. - Рисунок 4 [Электронный ресурс]. - Режим доступа URL: http://ra3ggi.qrz.ru/UZLY/dds.htm (дата обращения 2.08.2022) - прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИЗМЕРИТЕЛЬНЫЙ ГЕНЕРАТОР ПАРНЫХ ИМПУЛЬСОВ | 2022 |

|

RU2788980C1 |

| Калибратор фазы | 1982 |

|

SU1027640A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТЫ | 2022 |

|

RU2793776C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1681375A1 |

| ГЕНЕРАТОР СЛУЧАЙНОГО ПРОЦЕССА | 1991 |

|

RU2050585C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО- И ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2007 |

|

RU2358384C2 |

| Цифровой вычислительный синтезатор частотно-модулированных сигналов | 2019 |

|

RU2718461C1 |

| Цифровой синтезатор фазоманипулированных сигналов | 2019 |

|

RU2701050C1 |

| Цифровой вычислительный синтезатор для адаптивных систем связи с ППРЧ | 2020 |

|

RU2757413C1 |

Изобретение относится к измерительным генераторам парных сигналов произвольной формы с программируемой задержкой между ними. Техническим результатом является расширение функциональных возможностей за счет генерирования пары сигналов произвольной формы с программируемой задержкой между ними. Устройство содержит два составленных из идентичных узлов канала формирования сигнала, каждый из которых состоит из последовательно соединенных многоразрядного сумматора, регистра хранения, постоянного запоминающего устройства, цифроаналогового преобразователя и фильтра нижних частот, выход которого служит выходом соответствующего сигнала. Первый канал благодаря обратной связи по первому входу многоразрядного сумматора через свой регистр хранения, образующей аккумулятор, представляет собой устройство прямого цифрового синтеза частоты, значение которой задается кодом по второму входу многоразрядного сумматора. Один вход многоразрядного сумматора во втором канале подключен к выходу многоразрядного сумматора первого канала, а второй вход является входом кода задержки между сигналами. 2 ил.

Генератор парных сигналов произвольной формы, содержащий последовательно соединенные первые многоразрядный сумматор, регистр хранения, постоянное запоминающее устройство, цифроаналоговый преобразователь и фильтр нижних частот, выход которого является выходом первого сигнала, причем цифровой выход первого регистра хранения, у которого тактовый вход соединен с выходом тактового генератора, подключен к цифровому входу первого слагаемого первого многоразрядного сумматора, второй цифровой вход которого является входом кода управления частотой сигналов, отличающийся тем, что в него дополнительно введены вторые последовательно соединенные многоразрядный сумматор, регистр хранения, постоянное запоминающее устройство, цифроаналоговый преобразователь и фильтр нижних частот, выход которого служит выходом второго сигнала, при этом цифровой вход первого слагаемого второго многоразрядного сумматора подключен к цифровому выходу первого многоразрядного сумматора, а его цифровой вход второго слагаемого – к цифровому входу кода задержки между сигналами, тактовый вход второго регистра хранения соединен с выходом тактового генератора.

| Леонид Ридико, DDS: прямой цифровой синтез частоты, Компоненты и технологии, 7 2001, 91 c., c | |||

| Способ сужения чугунных изделий | 1922 |

|

SU38A1 |

| ГЕНЕРАТОР ДВУХФАЗНЫХ ГАРМОНИЧЕСКИХ СИГНАЛОВ | 2020 |

|

RU2737004C1 |

| ГЕНЕРАТОР ДВУХФАЗНЫХ ГАРМОНИЧЕСКИХ СИГНАЛОВ | 2021 |

|

RU2761109C1 |

| US 4525795 A, 25.06.1985. | |||

Авторы

Даты

2023-05-02—Публикация

2022-11-09—Подача