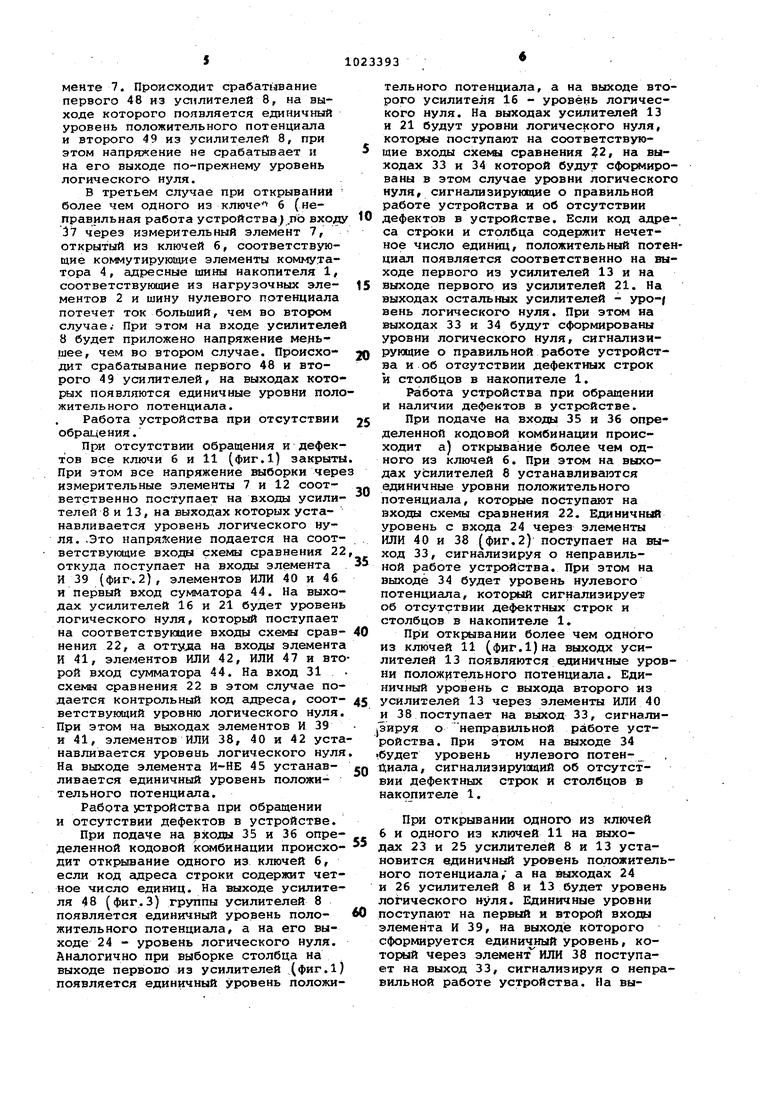

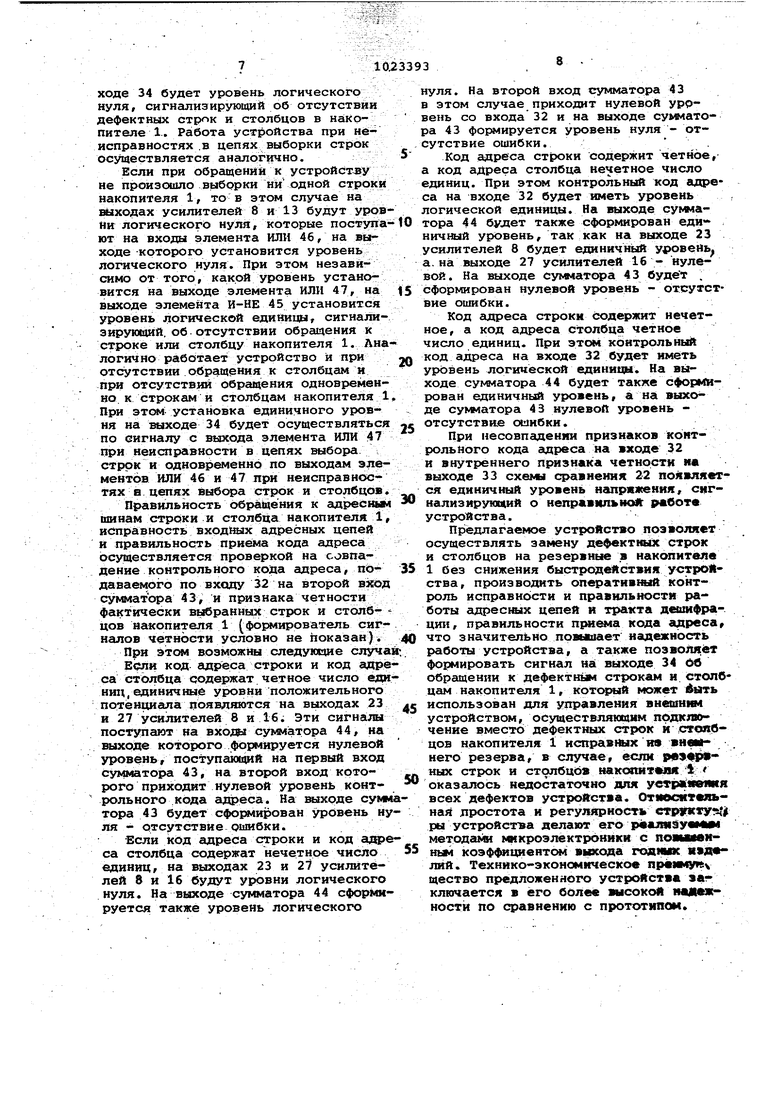

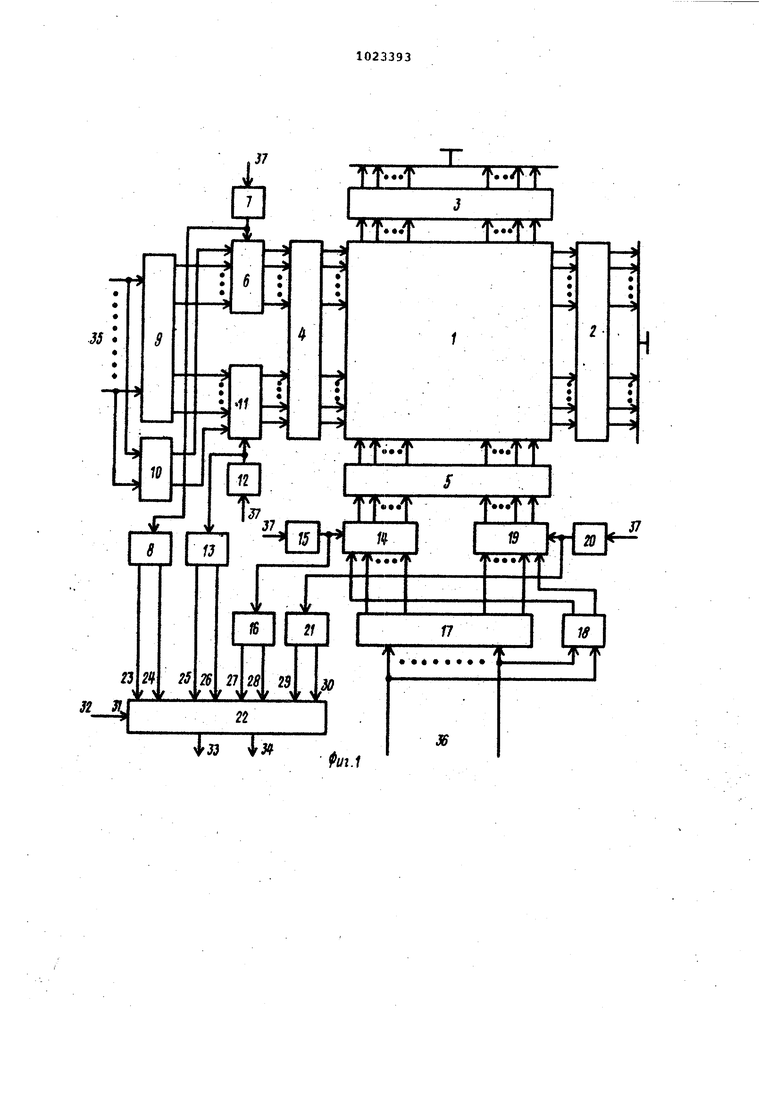

Изобретение относится к вычисли тельной технике, в частности к зап минающим устройствам, и может быть использовано в системах дискретной обработки информации с повышенной надежностью. Известно запоминающее устройств 3 котором применяется метод контро ля тракта дешифрации выбранных адресных шин в контрольный код адрес с последующим сравнением с внешним контрольным кодом адреса l . Недостатками устройства являются большая избыточность и малое бы родействие, являкяциеся следствием сложности шифратора. Наиболее близким техническим решением к данному изобретению является запоминающее устройство, содержащее накопитель, состоящий из основных и резервных запоминающих элементов, ключи выборки основных и резервных строк и столбцов, дешифраторы основных строк и столбцов формирователь запрета выборки основ ных столбцов, программируемую логическую матрицу, общую шину устрой ства, входные и выходные шины устркэйства 2 , Недостатками устройства являются отсутствие контроля правильности работы адресных цепей и тракта дешифрации, усложнение электроники обрамления накопителя и логики ввода-вывода, кррме того, необходимость адресации Кс1ждого дефектного запоминающего элемента усложняет структуру ПЛМ и увеличивает ее аппа ратурный объем, что снижает надежность запоминающего устройства. Цель изобретения - повышения надежности запоминающего устройства. Поставленная цель достигается тем, что в запоминающее устройство, содержащее матричный накопитель, группы ключей, дешифраторы и первую программируемую логическую матрицу, причем входы первого и второго дешифраторов являются соответственно адресными-.: в ходами устройства, введены вторая программируемая логическая матрица, .схема сравнения, коммутаторы, группы пороговых усилителей, измерительные элементы и группы нагрузочных элементов, выхода которых соединены с шиной нулевого потенциала, причем входы нагрузочных элементов первой группы подключены к гщресным выходам строк матричного накопителя, адресные входы строк которого соединены с выходами первого коммутатора, входы которого подключены соответственно к выходам ключей первой и второй гру первые входы ключей первой группы п ключены к выходу первого измеритель ного элемента и.входам пороговых ус лителей первой группы, первые входы ключей второй группы соединены с выходом второго измерительного элемента и входами пороговых усилителей, второй группы, вторые входы одних из ключей первой и второй групп, подключены к выходам первого дешифратора, вторые входы другах ключей первой и второй групп соединены соответственно с выходами первой программируемой логической матрицы, входы которой подключены к входам первого дешифратора, первые входы ключей третьей и четвертой групп соединены соответственно с выходом третьего измерительного элемента и входами порюговых усилителей третьей группы и с выходом четвертого измерительного элемента и входами пороговых усилителей четвертой группы, вторые входы одних из ключей третьей и четвертой групп ; подключены к выходам второго дешифратора, а BTOixje входы других ключей третьей и четвертой групп - к выходам второй программируемой логической матрицы, входы которой соединены с вхо|Дами второго дешифратора,выходы клм;чей третьей и четвертой групп подключены к входам второго коммутатора, выходы которого соединены с адресными входами столбцов матричного накопителя, адресные выходы столбцов которого подключены к входам нагрузочных элементов второй группы, выходы пороговых усилителей соединены с одними из входов схемы сравнения, выходы и другой вход которой и входы измерительных элементов являются соответственно выходами, входом контрольного кода адреса и входами напряжения выборки устройства, На фиг.1 приведена функциональная схема предложенного устройства; на фиг.2 - функциональные схемы наиболее предпочтительных вариантов выполнения схемы сравнения и групп пороговых усилителей соответственно. Предложенное запоминающее устройство содержит матричный накопитель 1, состоящий из основных и резервных запоминающих элементов, первую 2 и вторую 3 группы нагрузочных элементов, первый 4 и второй 5 коммутаторы, первую группу ключей б, предназначенных для выборки строк накопителя, первый измерительный элемент 7, например резистор, первую группу пороговых усилителей 8, первый дешифратор 9, первую программируемую логическую матриу 10, вторую группу ключей 11, предназначенных для выборки строк накопиеля, второй измерительный элемент 12, например резистор, вторую группу ороговых усилителей 13, третью групу ключей 14, предназначенную, для выорки столбцов накопителя, третий змерительный элемент 15, например, езистор, третью группу пороговых усилителей 16, второй дешифратор 177 вторую программируемую логическую матрицу 18, четвертую группу ключей 19, предназначенных для выборки ст.ол цов накопителя, четвертый измеритель ныЯ элемент 2.0, например резистор, четвертую группу пороговых усилителей 21 и схему сравнения 22 с входам 23-31. На фиг.1 обозначено; вход конт рольного кода адреса 32 устройства, выходы 33 и 34, адресные входы 35 и 36 и вход напряжения выборки 37 устройства. Схема 22 сравнения содержит (фиг. первый элемент ИЛИ 38, первый элемент И 39, второй элемент ИЛИ 40, второй элемент И 41, третий элемент ИЛИ 42, первый 43 и второй 44 сумматоры по модулю два, элемент И-НЕ 45, четвертый 46 и пятый 47 элементы ИЛИ Каждая из групп пороговых усилителей содержит (фиг.З) первый 48 к второй 49 пороговые усилители с разныют порогами срабатывания. Коммутаторы 4 и 5 могут .быть выполнены на основе коммутирующих элементов , которые могут быть удалены П5гтем например, механического разрушения, пережигания лучсяи лазера и т. Программируемые логические матрицы 10 и 18 могут быть выполнены, например, на основе элементов ИЛИ-НЕ и ключей с коммутирующими перекмчками, которые могут устраняться механическим способом, пережиганием лучом лазера и т.п. Устройство работает следуюишм образом.. Коррекция постоянных неисправностей., После изготовления устройства производится его контроль и дйагностй ка с целью обнаружения и локализации всех неисправностей. В случае обнаружения неисправностей, приводящих к неправильной работе дешифраторов, не исправностей запоминающих элементов накопителя 1, ключей 6,11,14 и 19 .. .И и т.д. производится удаление соответствующего коммутирующего эле мента в коммутаторах 4 и 5 соответст вуьощих строке и.столбцу, в которы-: обнаружен дефект. Адрес дефектной строки записывается в матрицу 10, а адрес дефектного столбца - в матрицу 18. ,В процессе работы устрбйства при обращении по адресу, содержащему дефектные элементы в строке и столбце накопителя 1, происходит выборка исправной строки столбца из резервных строк и столбцов накопителя 1, При этом дефектные строки и столбцы не выбираются, так как цепи их выборки разомкнуты путем удаления соответствующих коммутирующих элементов в коммутаторах 4 и 5. Рассмотрим три режима работы устройства в период эксплуатации; пр отсутствии обращения, обращение при отсутствии дефектов в устройстве, об ращение при Наличии дефектов в устройстве, при следующих условиях. . При подаче на входы 36 определенной комбинации кода адреса строки и столбца соответственно формируется положительный потенцигш на одном из выходов ключей 6 и 11 и на одном из выходов ключей 14 и 19, а остальные выходы имеют нулевой потенциал. Положительные потенциалы с-выходов выбранных ключей 6,11,14 и 19 через коммутаторы 4 и 5 подаются на адресные входы накопителя 1, с которого по адресным шинам передаются на входы нагрузочных элементов 2 и 3 соответственно. При подаче на входы 35 кода адреса, содержащего четное число единиц, происходит выборка одной из строк накопителя 1, подключенных к ключам 6 (если нечетное, то выбирается одна из строк, подключенных к ключам 11) При подаче на входы 36 кода адреса, содержащего четное число единиц, происходит выборка одного из столбцов накопителя, подключенных к ключам 14 (если нечетное, то выбирается столбец, подключенный к ключам 19). При подаче на входы 35 и 36 кода адреса, содержащего четное число единиц, на входе 32 формируется уровень |логического нуля, при нечетном числе единиц - единичный уровень положительного потенциала. Работа групп пороговых усилителей возможна в трех случаях: при отсутствии обращения, при выборе одного КЗ ключей 6,11,14 и 19, при выборе более чем одного иэ ключей 6,11,14 и 19. В первом случае при отсутствии обращения все ключи 6 и 11 эакрыты. При этом все напряжение выборки, подаваемое на вход 37 через измерительный, элемент 7, будет приложено к входу усилителей 8. Пороги первого 48 и второго 49 (фиг.З) пороговых усилителей 8 выбраны так, что в этом случае ни один из ник не срабатывает и на их выходах будет напряжение, соответствующее уровню логического нуля. Во втором случае при открывании одного иэ ключей 6 от внешнего источника напряжения выборки (на фиг.1 не показано ) по входу 37 через измерительный элемент 7, открытый из ключей 6, соответствующий коммутирукнций элемент коммутатора 4, адресную шину накопителя 1, соответствующий из нагрузочных элементов .2 и общую шину нулевого потенциала потечет ток. При этом на вход усилителей 8 поступает напряжение меньшее, чем в первом случае, на.величину падения напряжения на измерительном элементе 7. Происходит срабатывание первого 48 из уа1лителей 8, на выходе которого появляется единичный уровень положительного потенциала и второго 49 из усилителей 8, при этом напряжение не срабатывает и на его выходе по-прежнему уровень логического нуля. В третьем случае при открывания более чем одного из ключе 6 (неправ1ильная работа устройства) .по вход 37 через измерительный элемент 7, открытый из ключей б, соотбетствующие коммутирующие элегленты коммутатора 4, адресные шины накопителя 1, соответствующие из нагрузочных элементов 2 и шину нулевого потенциала потечет ток больший, чем во вторснл случае,- При этом на входе усилителе 8 будет приложено напряжение меньшее, чем во втором случае. Происходит срабатывание первого 48 и второго 49 усилителей, на выходах кото E&jx появляются единичные уровни поло жительного потенциала. Работа устройства при отсутствии обрацения. При отсутствии обращения и дефектов все ключи б и 11 (фиг.1) закрыты При этом все напряжение выборки чере измерительные элементы 7 и 12 соответственно поступает на входы усилителей 8 и 13, на выходах которых устанавливается уровень логического нуля. .Это напряжение подается на соответствующие входы схемы сравнения 22 откуда поступает на входы элемента и 39 (фиг.2), элементов ИЛИ 40 и 46 и первый вход сумматора 44. На выходах усилителей 16 и 21 будет уровень логического нуля, который поступает на соответствующие входы схемы сравнения 22, а оттуда на входы элемента И 41, элементов ИЛИ 42, ИЛИ 47 и вто рой вход сумматора 44. На вход 31 схемы сравнения 22 в этом случае подается контрольный код адреса, соответствуювдий уровню логического нуля При этом на выходах элементов И 39 и 41, элементов ИЛИ 38, 40 и 42 уста навливается уровень логического нуля На выходе элемента И-НБ 45 устанавливается единичный уровень положительного потенциала. Работа устройства при обращении и отсутствии дефектов в устройстве. При подаче на входы 35 и 36 определенной кодовой комбинации происходит открывание одного из ключей б, если код адреса строки содержит четное число единиц. На выходе усилителя 48 (фиг.3) группы усилителей 8 появляется единичный уровень положительного потенциала, а на его выходе 24 - уровень логического нуля. Аналогично при выборке столбца на выходе первопо из усилителей (фиг.1 появляется единичный уровень положительного потенциала, а на выходе второго усилителя 16 - уровень логического нуля. На выходах усилителей 13 и 21 будут уровни логического нуля, которые поступают на соответствующие входы схекш сравнения 22, на выходах 33 и 34 которой будут сформированы в этом случае уровни логического нуля, сигнализирующие о правильной работе устройства и об отсутствии дефектов в устройстве. Если код адреса строки и столбца содержит нечетное число единиц, положительный потенциал появляется соответственно на выходе первого из усилителей 13 и на выходе первого из усилителей 21. На выходах остальных усилителей - уро-/ вень логического нуля. При этом на выходах 33 и 34 будут сформированы уровни логического нуля, сигнализирующие о правильной работе устройства и об отсутствии дефектных строк и столбцов в накопителе 1. Работа устройства при обращении и наличии дефектов в устрюйстве. При подаче на входы 35 и 36 определенной кодовой комбинации происходит а) открывание более чем одного иэ ключей 6. При этом на выходах усилителей 8 устанавливаются единичные уровни положительного потенциала, которые поступают на входы cxeNEbi сравнения 22. Единичный уровень с входа 24 через элементы ИЛИ 40 и 38 |фиг,2) поступает на выход 33, сигнализируя о неправильной работе устройства. При этом на выходе 34 будет уровень нулевого потенциала, который сигнализирует об отсутствии дефектных строк и столбцов в накопителе 1. При открывании более чем одного из ключей 11 (фиг.1)на выходх усилителей 13 появляются единичные уровни положительного потенциала. Единичный уровень с выхода второго из усилителей 13 через элементы ИЛИ 40 H 38 поступает на выход 33, сигнали3ируя о неправильной работе устройства. При этом на выходе 34 будет уровень нулевого потенциала, сигнализиру1эдий об отсутствии дефектных строк и столбцов в накрпителё 1. При открывании одного из ключей 6 и одного из ключей 11 на выхоДс1Х 23 и 25 усилителей 8 и 13 установится единичный уровень положительного потенциала/ а на выходах 24 и 26 усилителей 8 и 13 будет уровень логического нуля. Единичные уровни поступают на первый и второй входы элемента И 39, на выходе которого сформируется единичный уровень, который через элемент ИЛИ 38 поступает на выход 33, сигнализируя о неправильной работе устройства. На выходе 34 будет уровень логического нуля, сигнализируюидай об отсутствии дефектньлх строк и столбцов в накопителе 1.. Работа устройства при неисправностях .в цепях выборки строк осуществляется аналогично. Если при обращений к устройству не произошло выборки ниодной строки накопителя 1, то в этом случае на выходах усилителей 8 и 13 будут уров нк логического нуля, которые поступа ют на входы элемента ИЛИ 46, на выходе которого установится уровень логического нуля. При этом неэавйсимо от того, какой уровень установится на выходе элемента ИЛИ 47, на выходе элемента И-НЕ 45 установится уровень логической единицы, сигнализирующий, об отсутствии обращения к строке или столбцу накопителя 1. Ана логично работает устройство и при отсутствии обращения к столбцам и при отсутствий обращения одновременно к строкам и столбцам накопителя 1 При этом установка единичного уровня на выходе 34 будет осуществляться по сигналу с выхода элемента ИЛИ 47 при неисправности в цепях выбора строк и одновременно по выходам элементов ИЛИ 46 и 47 при неисправностях в цепях выбора строк и столбцов Правильность обращения к адресным шинам строки и столбца накопителя 1 исправность входных адресных цепей и правильность приёма кода адреса осуществляется проверкой на совпадение контрольного кода адреса, подаваеА4ого по входу 32 на второй вход сумматора 43, и признака четности фактически выбранных строк и столбцов накопителя 1 (формирователь сигналов четности условно не показан). При этом возможны следующие случа ЕСЛИ код адреса строки и код адре са столбца содержат четное число еди нш;,едивич ныё уров ни положитель ного потенциала появляются на выходах 23 и 27 усилителей 8 и 16; Эти сигналы поступают на входа: сумм;атора 44, на выходе которого формируется нулевой уровень, поступ ощий на первый вход су14матора 43, на второй вход которого приходит нулевой уровень контрольного кода адреса. На шлхрде сукм тора 43 будет сфО1Я4ирован уровень ну ля - отсутствие ошибки. Если код адреса строки и код адре са столбца содержат нечетное число единиц, на выходах 23 и 2t усилителей 8 и 16 будут уровни логического нуля. На выходе сумматора 44 сформируется также уровень логического нуля. На второй вход сумматора 43 а этом случае приходит нулевой уровень со входа 32 и на выходе сумматора 43 формируется уровень нуля - отсутствие ошибки. Код адреса СТ|ЕЮКИ содержит четное, а код адреса столбца нечетное число единиц. При этом контрольный код адреса на входе 32 будет иметь уровень логической единицы. На выходе сумматора 44 будет также сформирован единичный уровень, так как на выходе 23 усилителей 8 будет единичный уровень а. на выходе 27 усилителей 16 - нулевой. На выходе сумматсфа 43 будет ; сформирован нулевой уровень - отсутствие ошибки. Код адреса строки содержит нечетное , а код адреса столбца четное число единиц. При этом контрольный код адреса на входе 32 будет иметь уровень логической единицы. На выходе сумматора 44 будет также сформирован единичный уровень, а на выхо де сумматора 43 нулевой уровень отсутствие ошибки. При несовпаден1ш признаков контрольного кода адреса на входе 32 и внутреннего признака четности на выходе 33 схемы сравиеиия 22 появляется единичный уровень напряжения, сигнал из ирукций о неправильно работе устройства. Предлагаемое устройство позволяет осуществлять замену дефектных строк и столбцов на резервною в накопителе 1 без снижения быстродействия устройства, производить оперативный контроль исправности и правильности работы адресных цепей и тракта дешифрации, правильности приема кода адресаг что значительно повышает надежность работы устройства, а также позволяет формировать сигнал на выходе 34 Об обращении к дефектным строкам и столб цам накопителя 1, может батъ использован для управления выешию устройством, осуществляющим подключение вместо дефектных строк и ,столбцов накопителя 1 исправных ив ви«м- , него резерва, в случае, если строк и столбцЬв иакопнтшм i оказалось недостаточно для у«тр|1«юямя всех дефектов устройства. Отмеситеяьная лрюстота и регуляриость ( ры устройства делают его реаляэуемм метрданш микроэлектроники с пгмиггHfcM коэффициенте выхода гояннх нвде ЛИЙ. Технико-экономическое прёммукч щество предложенного устройства эаг ключается в его более высокой ШЯКК нести по сравнению с прототипом.

37

1

.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970477A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU959168A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU949721A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| Постоянное запоминающее устройство с перезаписью информации | 1983 |

|

SU1278978A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1987 |

|

SU1494785A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Репрограммируемое постоянное запоминающее устройство | 1989 |

|

SU1695384A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее матричный накопитель, группы ключей, дешифраторы и первую программируемую логическую матрицу, причем входы первого и второго дешифраторов являются соответственно адрестными входами устрой :тва, отличающееся тем, что, с целью повышения надежности устройства, в него введены вторая программируемая логическая матрица, схема сравнения, коммутаторы, группы пороговых усилителей, измерительные элементы и группы нагрузочных элементов, выходы которых соединены с шиной нулевого потенциала, причем входы нагрузочных элементов первой группы подклюЧены к адресным выходам строк матричного накопителя, адресные входы строк которого соединены с выходами первого коммутатора, входы которого подключены соответственно к выходам ключей первой и второй групп, первые входы ключей первой группы подключены к выходу первого измерительного элемента и входам пороговых усилителей первой группы, первые входы ключей второй, группы соединены с. выходом . второго измерительного элемента и входами пороговых усилителей второй группы, вторые входы одних из,ключей первой и второй групп подключены к I выходам первого дешифратора, вторые I входы других ключей первой и второй групп соединены соответственно с выходами первой программируемой логической матрицы, входы которой подключены к входам первого дешифратора, первые входы ключей третьей и четвертой групп соединены соответственно с выходом третьего измерительного элемента и входами пороговых усилителей третьей группы и с выходе чет (Л вертого измерительного Элемента и входами пороговых усилителей четвертой группы, вторые входы одних из , ключей третьей и четвертой групп подключены к выходам второго дешифратора, а вторые входы других ключей третьей, и четвертой групп - к выходам второй программируемой логической матрицы, входы которой соединены с входами второго дешифратора, выю ходы ключей третьей и четвертой групп со со со со подключены к входам второго кс 1мутатора, выходы которого соединены с адресными входами столбцов матричного накопителя, адресные выходы столбцов которого подключены к входам нагрузочных элементов второй группы, выходы пороговых усилителей соединены с одними Из входов схемы сравнения, выходы и другой вход которой и вхо.ды измерительных элементов являются соответственно выходами, входом контрольного кода адреса и входами напряжения выборки устройства.

.35

л

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Самофалов К.Г., Корнейчук В.И, Городний А.В | |||

| Структурно-логические методы повышения надежности запоминающих устройств | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент ОНА № 4051354, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

Авторы

Даты

1983-06-15—Публикация

1982-01-07—Подача