Изобретение относится к области автоматики и вычислительной техники и может быть использовано в дискретных автоматах для сложения-вычитания чисел, кодируемых трехуровневыми сигналами по ортогональным составляющим функций Попова.

Известен способ кодирования трехзначных чисел троичных систем счисления (С. 0. Мкртчян, Проектирование логических устройств ЭВМ на нейронных элементах, М. , "Энергия", с. 81-83). При таком способе кодирования трехуровневый биполярный сигнал представляется отрицательной полярностью сигнала число "0", нулевым уровнем - число "1", сигналом положительной полярности - число "2".

Такой способ кодирования обеспечивает представление троичных чисел и не обеспечивает кодирование q-ричных чисел, при q больше трех.

Известно устройство сложения-вычитания неизбыточного и избыточного аргументов в двоичной системе счисления (СССР, авт. св. N 407308, G 06 F 7/50, Бюл. N 46, 1973 г.), которое содержит блоки формирования суммы и переноса, выполненные на логических элементах. Каждый из блоков формирования суммы и переноса содержит две схемы формирования соответственно логического дополнения и действительного значения суммы и переноса, состоящей из трех элементов "И", и подключенных к их выходам элементов "ИЛИ", связанных выходом с усилителем-инвертором. Первые два входа первых элементов "И" каждой схемы формирования соединены с шинами логического дополнения положительного и отрицательного значений избыточного аргумента. Третьи входы первых элементов "И" схем формирования дополнения суммы и переноса блоков формирования суммы и переноса соединены с шиной действительного значения неизбыточного аргумента. Третьи входы элементов "И" схем формирования действительного значения суммы и переноса - с шиной логического дополнения неизбыточного аргумента. Первые входы вторых и третьих элементов "И" соединены с шинами действительных положительного и отрицательного значений избыточного аргумента соответственно. Другие входы второго и третьего элементов "И" схемы формирования дополнения суммы соединены с шинами логического дополнения неизбыточного аргумента. Другие входы второго и третьего элементов "И" схемы формирования действительного значения суммы - с шинами действительного значения неизбыточного аргумента. Другие входы второго и третьего элементов "И" схемы формирования дополнения переноса соединены с шиной действительного значения (при сложении) и шиной логического дополнения (при вычитании) управляющего сигнала соответственно. Другие входы второго и третьего элементов "И" схемы формирования действительного значения переноса соединены с шиной логического дополнения и шиной действительного значения управляющего сигнала соответственно. Выход инвертора схемы формирования дополнения суммы данного разряда и выход инвертора схемы формирования действительного значения переноса блока формирования переноса предшествующего разряда соединены с выходными шинами положительного значения суммы. Выход инвертора схемы формирования действительного значения суммы данного разряда и выход инвертора схемы формирования дополнения переноса предшествующего разряда соединены с выходными шинами отрицательного значения суммы.

Избыточное кодирование осуществляется введением в каждый разряд отрицательной единицы, т.е. один из аргументов кодируется в двоичной системе с цифрами -1, 0, 1: сумма в каждом разряде принимает значение, равное 0 или -1, а перенос - 0, при этом окончательная сумма в i-ом разряде, получаемая в двоичной системе с цифрами -1, 0, 1, имеет либо положительное, либо отрицательное значение и является простым объединением истинного значения суммы в i-м разряде и логического дополнения переноса из i-го разряда для отрицательного значения окончательной суммы и простым объединением дополнения суммы в i-ом разряде с истинным значением переноса из (i - 1)-го разряда для положительного значения окончательной суммы (под простым объединением понимается то, что каждое значение окончательной суммы в i-ом разряде выдается двумя шинами: соответствующими шинами суммы из i-го разряда и переноса из (i - 1)-го разряда).

Устройство сложения-вычитания неизбыточного и избыточного аргументов работает только в двоичной системе счисления.

Известен троичный комбинационный сумматор и способ его работы, принятый за прототип изобретения (СССР, авт.св. N 416691, G 06 F 7/50, Бюл. N 7, 1974 г. ). Сумматор содержит три пороговых элемента, пять входных и четыре выходные шины. Первый пороговый элемент имеет порог +3 и пять входов с весами +2, +1, +1, +2, +1. Второй пороговый элемент имеет порог +5 и шесть входов с весами +2, +1, +1, +2, +1, +3. Третий пороговый элемент имеет порог +6 и семь входов с весами +2, +1, +1, +2, +1, +3, +2. Первые и вторые входы всех пороговых элементов подключены к шине старшего члена разряда первого слагаемого, вторые входы всех пороговых элементов подключены к шине младшего члена разряда первого слагаемого. Третьи входы всех пороговых элементов подключены к шине младшего члена разряда второго слагаемого. Четвертые входы всех пороговых элементов подключены к шине старшего члена разряда второго слагаемого. Пятые входы пороговых элементов подключены к шине переноса из предыдущего разряда сумматора. Шестые входы второго и третьего пороговых элементов подключены к инверсному выходу первого порогового элемента. Седьмой вход третьего порогового элемента подключен к инверсному входу второго порогового элемента.

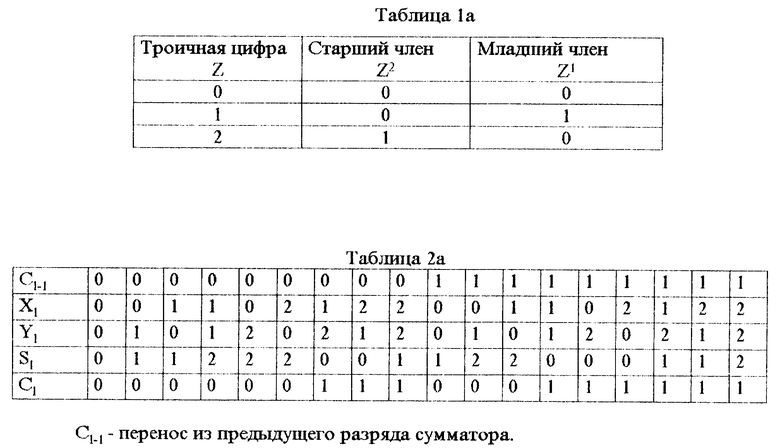

Цифры троичной системы закодированы согласно таблице 1а.

Работа троичного сумматора описывается таблицей 2a (таблицы 1а и 2а см. в конце описания)

С прямого выхода порогового элемента ПЭ1 снимается перенос C1 в следующий разряд сумматора, с прямого выхода порогового элемента ПЭ2 снимается старший член разряда троичной суммы S

Первые входы всех пороговых элементов соединены вместе и подключены к шине x

Троичный сумматор работает только в трехзначной - троичной системе счисления.

Техническим результатом изобретения является расширение функциональных возможностей способа сложения-вычитания. Расширение функциональных возможностей предусматривает кодирование чисел трехуровневыми сигналами, их сложение и вычитание в системах счисления с основаниями q = 4 и q = 8.

Трехуровневые волновые функция Попова

Для кодирования чисел трехуровневыми сигналами, вводятся трехуровневые волновые функции Попова.

1. Дискретные волновые функции.

Для кодирования чисел автор изобретения ввел дискретные волновые трехуровневые, биполярные функции popq(2 π k/q), различные для разных оснований q систем счисления и назвал их своим именем - функции Попова. Эти функции представляют парой ортогональных составляющих:

popq(2πk/q) = copq(2πk/q)+i•sipq(2πk/q), (1)

где q - основание системы счисления, которое может принимать значения от q = 3 до q = 8;

k - число-цифра, которая для одного разряда может принимать значения, равные 0, 1, ..., (q-1).

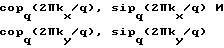

При этом каждую цифру k представляют фазой волновой функции Попова ϕkq= 2πk/q, a каждую фазу ϕkq кодируют сочетанием значений ортогональных составляющих cop(ϕkq) и sipq(ϕkq).

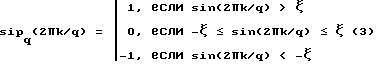

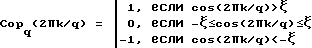

Значения ортогональных составляющих copq(2πk/q) и sipq(2πk/q) определяют через значения соответствующих им тригонометрических функций косинус и синус: cos(2πk/q) и sin(2πk/q). Для этого период 2π делят на q равных частей и назначают одинаковые по абсолютному значению положительный и отрицательный пороги ±ξ. Пример такого квантования по фазе для q = 7 приведен на фиг. 1. Значения тригонометрических функций в точках аргумента ϕkq= 2πk/q сравнивают с порогами. Если значение тригонометрической функции превышает положительное пороговое значение +ξ, то соответствующей ей трехуровневой ортогональной составляющей приписывают значение +1, если значение тригонометрической функции меньше отрицательного порогового значения -ξ, то соответствующей функции copϕkq или sipϕkp приписывают значение -1, если значение тригонометрической функции находится между пороговыми значениями +ξ и -ξ, то соответствующей трехуровневой ортогональной составляющей приписывают значение 0. Таким образом, значения ортогональных составляющих трехуровневых волновых функций можно определить, как:

Значения порогов ±ξ определяют из условия однозначного кодирования всех q фаз сочетаниями значений функций copq(ϕkq) и sipq(ϕkq), для всех оснований q от q = 3 до q = 8. При этом наихудшим случаем кодирования, с точки зрения допустимого уровня порога, является случай квантования периода для q = 7. Для этого случая (фиг. 1) в точках ϕ2,7= 4π/7 и ϕ5,7= 10π/7 значение cosϕkp= -sinπ/14 ≅ -0,22, а в точках ϕ3,7= 6π/7 и ϕ4,7= 8π/7 значение sinϕ = ±sinπ/7 ≅ ±0,433, и для однозначного кодирования семи фаз уровнями ортогональных составляющих абсолютное значение порогов ξ должно быть больше sinπ/14 и в то же время меньше sinπ/7, то есть для однозначного кодирования q фаз для всех q от q = 3 до q =8 значение модуля порога ξ при определении значений дискретных функций copq(2πk/q) и sipq(2πk/q) можно выбирать любым в пределах:

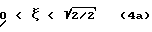

sinπ/7 > ξ > sinπ/14. (4)

При таком определении дискретных волновых функций, используя сочетания значений ортогональных составляющих copq(2πk/q) и sipq(2πk/q), обеспечивается однозначное кодирование q фаз функций popq(2πk/q) и, следовательно, q цифр k = 0, 1, ..., (q-1).

Для кодирования чисел в системах счисления, с основаниями q = 4 и q = 8 ограничение на выбор значения порога (4) менее жестко, а именно:

Функции popq(2πk/q), примененные для представления чисел в системе счисления с основанием q, могут быть использованы и для представления чисел в системе счисления с основанием (q + 1). При этом для кодирования (q + 1) цифр множество значений волновых функций дополняют сочетаниями значений ортогональных составляющих "0,0", когда обе ортогональные составляющие принимают нулевое значение. Например, для кодирования чисел в девятеричной системе счисления (q = 9) сочетания значений ортогональных составляющих волновых функций для q = 8 дополняют сочетанием "0,0", соответствующим цифре k = 0, а способ кодирования остальных цифр аналогичен описанному выше с той разницей, что при таком способе кодируют цифры k1 = k + 1.

В таблицах 1 - 7 (см. в конце описания) представлены значения фаз ϕkq= 2πk/q и соответствующие им фазо-волновые коды цифр для разных q от q = 3 до q = 8, а в таблице 7 представлены фазо-волновые коды цифр девятеричной системы счисления.

2. Непрерывные трехуровневые биполярные функции Попова

Трехуровневые биполярные функции непрерывного аргумента ϕVVVV, который изменяется в пределах 0 ≤ ϕ < 2π, представленные ортогональными составляющими:

popq(ϕ) = copq(ϕ)+i•sipq(ϕ), (5)

определяют через дискретные трехуровневые функции popq(2πk/q), принимая k = [ϕq/2π], где k[•] - означает целую часть аргумента ϕq/2π. То есть ортогональные составляющие непрерывных функций copq(ϕ) и sipq(ϕ) сохраняют значения соответствующих им дискретных функций, которые они имели в точках ϕkp= 2πk/q, в секторе аргумента ϕ:

2πk/q ≤ ϕ < 2π(k+1)/q (6)

Правила сложения-вычитания чисел по модулям q = 4 и q = 8, представленных фазо-волновыми кодами popq(ϕ)

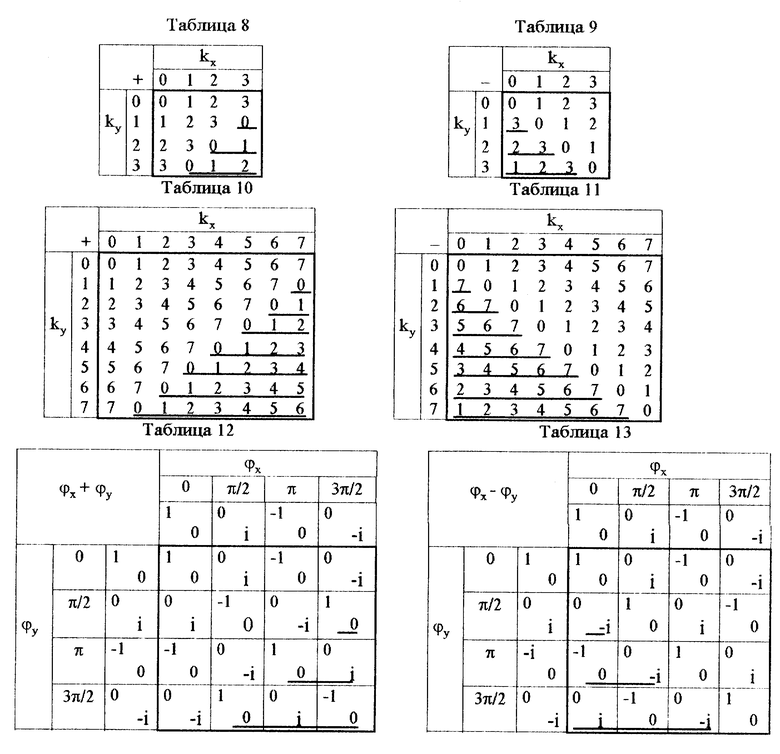

Правила сложения чисел по модулю q = 4 определяются таблицей 8, а правила вычитания чисел по модулю q = 4 - таблицей 9. Правила сложения чисел по модулю q = 8 определяются таблицей 10, а правила вычитания чисел по модулю q = 8 определяются - таблицей 11.

В тех случаях, когда сумма равна или больше основания системы счисления q по модулю, формируют число "1" - переноса в старший разряд. При вычитании число переноса "-1" формируют, когда разность меньше нуля. В таблицах 8-11 эти значения сумм и разностей подчеркнуты.

Заменяя в таблицах 8 - 11 (см. в конце описания) цифры их фазо-волновыми кодами получаем таблицы истинности для операций сложения - вычитания чисел, представленных фазо-волновыми кодами таблиц 12-15 (см. в конце описания).

При наличии единицы переноса из младшего разряда осуществляют сдвиг фаз результатов сложения по модулю на π/2 при сложении или на -π/2 при вычитании для четверичной системы сложения и на π/4 при сложении или на -π/4 при вычитании для восьмеричной системы счисления. Этому случаю соответствуют таблицы истинности 16 - 19.

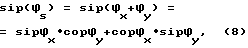

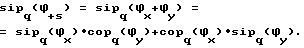

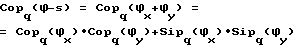

Поскольку коды чисел kx и ky (слагаемых или уменьшаемого и вычитаемого) представляют фазы ϕx= 2πkx/q и ϕy= 2πky/q волновых функций Попова, способ сложения или вычитания сводится к сложению или вычитанию фаз волновых функций слагаемых. Волновые функции Попова обладают свойствами, аналогичными свойствам синусоидальных волн. В частности, для них справедливо правило сложения фаз:

и правило вычитания фаз:

где ϕ±s= ϕx± ϕy, при этом 0 ≤ ϕ±s< 2π.

Описанный способ сложения - вычитания представляет принцип действия "полусумматора-вычитателя". Полный сумматор-вычитатель предполагает сложение-вычитание результатов сложения-вычитания по модулю с единицей переноса из предыдущего разряда, если таковая имеет место, а также формирование единицы переноса в следующий по старшинству разряд.

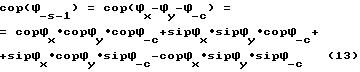

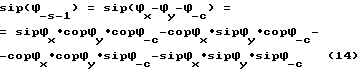

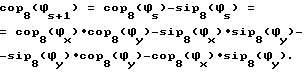

Для сложения-вычитания с единицей переноса используют формулы сложения трех фаз, аналогичные тригонометрическим соотношениям:

и формулы вычитания:

где ϕ±c/- фаза кода единицы переноса C = ±1, ϕ±c±1= ϕx± ϕy± ϕc. При этом 0 ≤ ϕ±c±1< 2π.

Для четверичной системы счисления ϕ±c= ±π/2. Этой фазе соответствует код: cop4ϕ±c= 0, а sip4ϕc= 1 - при сложении и sip4ϕ-c= -1 - при вычитании.

Для восьмеричной системы счисления ϕ±c= ±π/4 и код переноса cop8ϕ±c= 1, а sip8ϕc= 1 - при сложении и sip8ϕ-c= -1 - при вычитании.

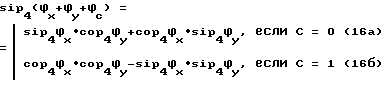

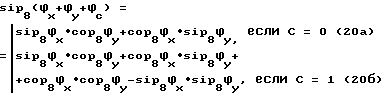

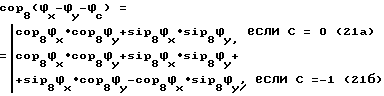

С учетом значений кодов единицы переноса формулы полного сложения (11) и (12) для четверичной системы счисления принимают вид:

а формулы полного вычитания (13) и (14):

Для восьмеричной системы счисления формулы полного сложения:

а формулы вычитания:

Из анализа соотношений (15) - (22) можно сделать следующий вывод - для реализации операций сложения и вычитания по модулю, а также для полного сложения и полного вычитания как в четверичной, так и в восьмеричной системах счисления достаточно получить четыре произведения фазо-волновых кодов  и путем комбинирования сумм - разностей этих произведений реализовать любую из операций по формулам (15) - (20). Это означает, что можно построить универсальное устройство для реализации операций сложения-вычитания, сдвига, сравнения в четверичной и восьмеричной системах счисления.

и путем комбинирования сумм - разностей этих произведений реализовать любую из операций по формулам (15) - (20). Это означает, что можно построить универсальное устройство для реализации операций сложения-вычитания, сдвига, сравнения в четверичной и восьмеричной системах счисления.

Правила формирования кода единицы переноса

Независимо от системы счисления код единицы переноса при сложении должен формироваться, если фаза кода суммы больше или равна 2π и код переноса "-1" - при вычитании, если фаза кода разности меньше -2π. Однако такое определение правила неоднозначно в силу периодичности фазо-волновых функций.

Из таблиц истинности 12, 14, 16 и 18 операций сложения видно, что независимо от значения кода переноса из предшествующего разряда, код единицы переноса формируется всегда, когда фазы кодов обоих слагаемых ϕx или ϕy больше или равны π ,а также когда фаза кода суммы ϕs и ϕs+1 лежит в пределах от 0 до π, и при этом фаза кодов хотя бы одного из слагаемых не меньше π. Таким образом, можно сформулировать следующее правило формирования единицы переноса C = 1 при сложении:

C = 1, если ϕx≥ π и ϕy≥ π, а также

При этом формируют код единицы переноса при сложении:

sipq(ϕc+1) = 1 (24)

Из таблиц истинности операций вычитания (таблицы 13, 15, 17 и 19) следует, что код единицы переноса, C = -1 формируется, если фаза ϕx кода уменьшаемого меньше π и фаза ϕy кода вычитаемого не меньше π, а также когда фаза ϕ-s или ϕ-s-1 кода лежит в пределах от π до 2π, и при этом либо фаза ϕx кода уменьшаемое меньше π, либо фаза ϕy кода вычитаемого не меньше π, то есть:

C = -1, если ϕx< π и ϕy≥, а также

При этом формируют код единицы переноса при вычитании:

sipq(ϕ-c-1) = -1 (26)

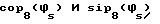

Сигнал кода переноса cop8(ϕ±c=1) = 1 в восьмеричной системе счисления формировать не обязательно, так как эта составляющая кода не изменяется при появлении единицы переноса. Аналогично в четверичной системе счисления сигнал кода переноса cop4(ϕ±c±1) не формируют, т.к. заведомо известно, что при наличии сигнала кода переноса sip4(ϕ±c±1) всегда сигнал cop4(ϕ±c±1) = 0, и этот факт можно учесть при сложении-вычитании с единицей переноса в следующий разряд.

Способ полного сложения-вычитания чисел в четверичной и восьмеричной системах счисления

Способ полного сложения-вычитания чисел основан на кодировании чисел-цифр kx и ky фазами ϕx= 2πkx/q и ϕy= 2πky/q сигналов copq(ϕx,y) и sipq(ϕx,y) по волновым функциям Попова, а также на сложении-вычитании фаз сигналов в соответствии с формулами (15) - (22) и формировании сигналов переноса по правилам (23) - (26).

Способ состоит в том, что формируют две пары трехуровневых сигналов:  по волновым функциям Попова

по волновым функциям Попова  которые представляют двумя ортогональными составляющими:

которые представляют двумя ортогональными составляющими:

popq(ϕ) = copq(ϕ)+i•sipq(ϕ), (5)

каждое число-цифру kx и ky от kx'y = 0 до kx'y = q -1, в системах счисления с основаниями q= 4 и q=8, представляют фазами ϕx,y= 2πkx,y/q, каждую фазу ϕx,y кодируют значениями copq(2πkx,y/q) и sipq(2πkx,y/q). Значения ортогональных составляющих функций Попова copq(ϕ) и sipq(ϕ) определяют путем сравнения с порогами ±ξ соответствующих тригонометрических функций cos(ϕ) и sin(ϕ) при значениях аргумента ϕ = 2πk/q, как

При этом значения модуля ξ можно выбрать любым в пределах  (4а).

(4а).

Для сложения-вычитания фаз предварительно формируют сигналы четырех произведений сигналов:

- сигналы первого произведения - copq(ϕx)•copq(ϕy);

- сигналы второго произведения - sipq(ϕx)•sipq(ϕy);

- сигналы третьего произведения - sipq(ϕx)•copq(ϕy);

- сигналы четвертого произведения - copq(ϕx)•sipq(ϕy),

а также используют сигнал sipq(ϕc) единицы переноса C = 1 при сложении и сигнал -sipq(ϕ-c) единицы переноса C = -1 при вычитании.

Затем для сложения чисел формируют два сигнала copq(ϕs) и sipq(ϕs), которые представляют коды суммы чисел слагаемых kx и ky', если единица переноса из предыдущего разряда равна нулю (C = 0). При этом сигнал copq(ϕs) формируют путем вычитания из сигналов первого произведения сигналов второго произведения, а сигнал sipq(ϕs) путем сложения сигналов третьего и четвертого произведений, в соответствии с формулами (15а), (16а), (19а) и (20а). При наличии единицы переноса из предыдущего разряда (C = 1) при сложении чисел формируют два сигнала copq(ϕs+1) и sipq(ϕs+1). При этом в четверичной системе счисления сигнал cop4(ϕs+1) формируют путем замены сигнала cop4(ϕs) инвертированным по полярности сигналом sip4(ϕs), a в восьмеричной системе счисления сигнал cop8(ϕs+1) - путем вычитания из сигналов cop8(ϕs) сигналов sip8(ϕs), в соответствии с формулами (15б) и (19б). Сигнал sip4(ϕs+1) в четверичной системе счисления формируют путем замены сигналов sip4(ϕs) сигналами cop4(ϕs), а сигнал sip8(ϕs+1) в восьмеричной системе счисления - путем суммирования сигналов cop8(ϕs) и sip8(ϕs), в соответствии с формулами (16б) и (20 б).

Для вычитания чисел формируют два сигнала copq(ϕ-s) и sipq(ϕ-s), которые представляют коды разности чисел kx и ky, если единица переноса из предыдущего разряда равна нулю (C = 0). При этом сигнал  формируют путем сложения сигналов первого и второго произведений, а сигнал sipq(ϕ-s) - путем вычитания из сигналов третьего произведения сигналов четвертого произведения в соответствии с формулами (17а), (18а), (21а) и (22а).

формируют путем сложения сигналов первого и второго произведений, а сигнал sipq(ϕ-s) - путем вычитания из сигналов третьего произведения сигналов четвертого произведения в соответствии с формулами (17а), (18а), (21а) и (22а).

При наличии единицы переноса из предыдущего разряда (C = -1) формируют два сигнала copq(ϕ-s-1) и sipq(ϕ-s-1). При этом в четверичной системе счисления сигнал cop4(ϕ-s-1) формируют путем замены сигналов cop4(ϕ-s) сигналами sip4(ϕ-s), a в восьмеричной системе счисления сигнал cop8(ϕ-s-1) формируют путем сложения сигналов cop8(ϕ-s) и sip8(ϕ-s), в соответствии с формулами (17б) и (21б).

Сигнал sip4(ϕ-s-1) в четверичной системе счисления формируют путем замены сигналов sip4(ϕ-s) инвертированными по полярности сигналами cop4(ϕ-s), а сигнал sip8(ϕ-s-1) в восьмеричной системе счисления формируют путем вычитания из сигналов sip8(ϕ-s) сигналов cop8(ϕ-s), в соответствии с формулами (18б) и (22б).

Вместе с формированием сигналов кодов суммы-разности чисел формируют сигналы кодов единицы переноса в следующий разряд. При этом в четверичной системе счисления формируют сигналы кодов единицы переноса при сложении:

sipq(ϕc+1) = 1,

если ϕx≥ π и ϕy≥ π, а также если 0 ≤ (ϕs; ϕs+1) < π и (ϕx≥ π или ϕy≥ π).

При вычитании формируют сигналы кода переноса:

sipq(ϕ-c-1) = -1,

если ϕx< π и ϕy≥ π, а также если 2π > (ϕ-s; ϕ-s-1) ≥ π и (ϕx< π или ϕy≥ π). В остальных случаях при сложении и при вычитании формируют коды переноса:

sipq(ϕ±c±1) = 0.

Отличительными признаками изобретения-способа полного сложения-вычитания чисел являются:

- кодирование чисел фазами трехуровневых фазо-волновых функций;

- кодирование фаз уровнями ортогональных составляющих фазо-волновых функций;

- сложение-вычитание фаз по аналогичным правилам сложения-вычитания фаз синусоидальных волн.

Устройство сложения-вычитания чисел по модулям 4 и 8 содержит: пять входных (первую, вторую, третью, четвертую и пятую) и две (первую и вторую) выходных шины, два (первый и второй) инвертора полярности, два (первый и второй) повторителя, два (первый и второй) дифференциальных усилителя-ограничителя, переключатель полярности сигналов, четыре (первый, второй, третий и четвертый) амплитудных детектора и восемь (первый, второй и т.д.) управляемых ключей.

Первая входная шина соединена через первый ключ с неинвертирующим входом первого дифференциального усилителя-ограничителя, а через второй ключ - с инвертирующим входом этого же усилителя, первая входная шина через седьмой ключ также подключена к инвертирующему входу второго дифференциального усилителя-ограничителя, а через восьмой ключ - к неинвертирующему входу этого же усилителя.

Вторая входная шина через третий ключ соединена с неинвертирующим входом первого дифференциального усилителя-ограничителя, а через четвертый ключ - с инвертирующим входом того же усилителя, вторая входная шина через шестой ключ также соединена с неинвертирующим входом второго дифференциального усилителя-ограничителя и через пятый ключ - с инвертирующим входом того же усилителя.

Третья входная шина соединена со входами первого инвертора полярности и первого повторителя. Выход первого повторителя через второй детектор соединен с управляющими входами первого и шестого ключей, а выход первого инвертора полярности через первый детектор соединен с управляющими входами второго и пятого ключей.

Четвертая входная шина через первый переключатель полярности соединена со входами второго повторителя и второго инвертора полярности.

Пятая входная шина соединена с управляющим входом первого переключателя полярности.

Выходы первого и второго дифференциальных усилителей-ограничителей соединены с выходными шинами соответственно.

Выход второго повторителя через третий детектор соединен с управляющими входами четвертого и восьмого ключей, а выход второго инвертора полярности, через четвертый детектор соединен с управляющими входами третьего и седьмого ключей.

Отличительными признаками устройства сложения-вычитания по модулям 4 и 8 являются: два инвертора полярности, два повторителя, два дифференциальных усилителя-ограничителя, переключатель полярности сигналов, четыре детектора и восемь управляемых ключей, а также связи, обусловленные введением новых элементов схемы.

Устройство сложения-вычитания с единицей переноса содержит: четыре (первую, вторую, третью и четвертую) входные шины и две (первую и вторую) выходные шины, инвертор полярности, повторитель, элемент "ИЛИ-НЕ", первый и второй дифференциальные усилители-ограничители, элемент "НЕ", элемент "ИЛИ", два (первый и второй) детектора и семь (первый, второй и т.д.) управляемых ключей.

Первая входная шина через пятый ключ соединена с неинвертирующим входом первого дифференциального усилителя-ограничителя через третий ключ с неинвертирующим входом второго дифференциального усилителя-ограничителя и через четвертый ключ с инвертирующим входом этого усилителя.

Вторая входная шина соединена через шестой ключ с неинвертирующим входом второго дифференциального усилителя-ограничителя, через первый ключ с неинвертирующим входом первого дифференциального усилителя-ограничителя и через второй ключ - с инвертирующим входом того же усилителя.

Третья входная соединена со входами инвертора полярности и повторителя. Выход инвертора полярности соединен через пятый детектор с управляющими входами первого и четвертого ключей и первым входом элемента "ИЛИ-НЕ", а выход повторителя соединен через шестой детектор с управляющими входами второго и третьего ключей и вторым входом элемента "ИЛИ-НЕ". Выход элемента "ИЛИ-НЕ" через седьмой ключ соединен с первым входом элемента "ИЛИ", выход которого соединен с управляющими входами пятого и шестого ключей.

Четвертая входная шина соединена с управляющим входом седьмого ключа и через элемент "НЕ" со вторым входом элемента.

Выходы первого и второго дифференциальных усилителей-ограничителей соединены с первой и второй выходными шинами, соответственно.

Отличительными признаками устройства сложения-вычитания с единицей переноса являются: инвертор полярности, повторитель, элемент "ИЛИ-НЕ", два дифференциальных усилителя-ограничителя, элемент "НЕ", элемент "ИЛИ", два детектора и семь управляемых ключей, а также связи, обусловленные введением новых элементов схемы.

Способ полного суммирования-вычитания чисел, представленных фазо-волновыми кодами, и устройства для его осуществления поясняются чертежами.

На фиг. 1 а, б представлены соответственно графики косинуса и синуса дискретного ϕkq= 2πk/q (сплошные ординаты) и непрерывного ϕ (пунктир) аргументов.

На фиг. 1 в, г представлены соответственно графики дискретных ортогональных составляющих cop7(2πk/q) и sip7(2πk/q) (сплошные ординаты) функции Попова и составляющих сигналов cop7(ϕ) и sip7(ϕ) непрерывной функции Попова при q = 7.

На фиг. 2 представлена структурная электрическая схема преобразователя четырехразрядного унитарного кода в одноразрядный четырехзначный фазо-волновой код pop4(ϕ).

На фиг. 3 представлены эпюры напряжений преобразователя четырехразрядного унитарного кода в одноразрядный четырехзначный фазо-волновой код pop4(ϕ).

На фиг. 4 представлена структурная электрическая схема преобразователя восьмиразрядного унитарного кода в одноразрядный четырехзначный фазо-волновой код pop8(ϕ).

На фиг. 5 представлены эпюры напряжений преобразователя восьмиразрядного унитарного кода в одноразрядный восьмизначный фазо-волновой код pop8(ϕ).

На фиг. 6 представлена структурная электрическая схема устройства полного сложения-вычитания в четверичной и восьмеричной системах счисления.

На фиг. 7 представлена структурная электрическая схема устройства сложения-вычитания по модулям 4 и 8.

На фиг. 8 представлена структурная электрическая схема устройства сложения-вычитания с единицей переноса.

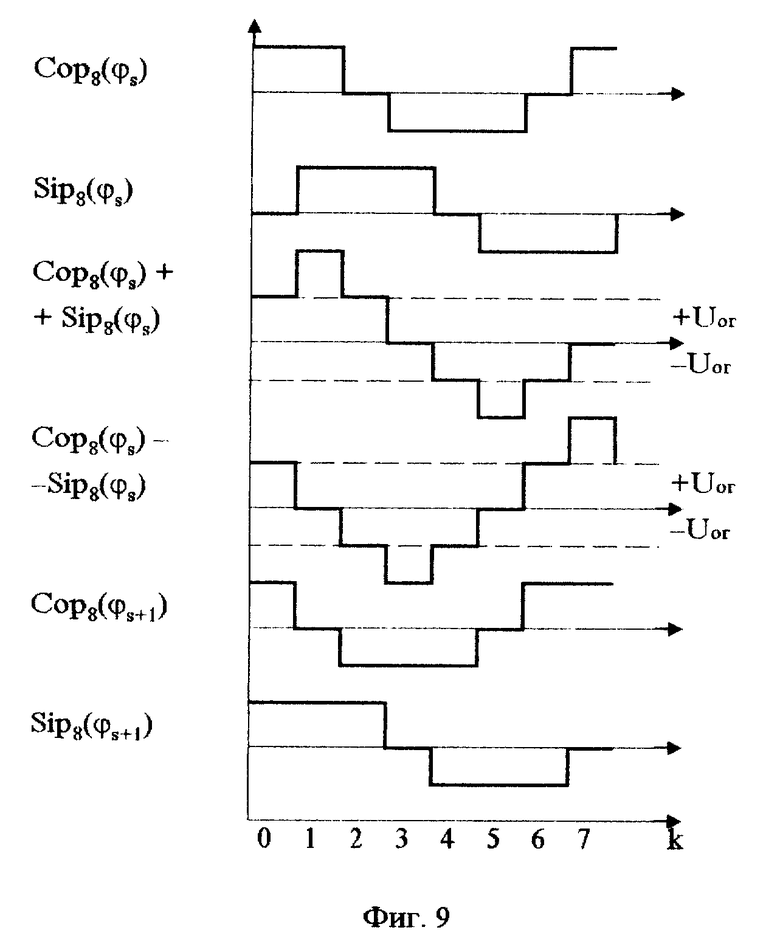

На фиг. 9 представлены эпюры напряжений формирования кодов, сдвинутых на +1.

На фиг. 10 представлена структурная электрическая схема устройства формирования кода единицы переноса.

На фиг. 11 представлены эпюры примера формирования сигналов взвешенной суммы;

На фиг. 12 представлена принципиальная электрическая схема переключателя полярности.

На фигурах введены обозначения:

1, 2, 3, 4, 5 - входные шины (первая, вторая и т.д.);

6 - устройство сложения-вычитания по модулям 4 и 8;

7 - устройство сложения-вычитания с единицей переноса;

8 - устройство формирования кода единицы переноса;

9, 12 и 20 - инверторы полярности сигналов (первый, второй и третий);

10, 11 и 21 - повторители (первый, второй и третий);

13, 14, 23, 24 и 33 - дифференциальные усилители (первый, второй и т.д. );

15 и 16 - выходные шины устройства сложения-вычитания по модулям 4 и 8 (первая и вторая);

17 и 29 - переключатель полярности сигналов (первый и второй);

18 и 19 - входные шины устройства сложения-вычитания с единицей переноса;

22 - элемент "ИЛИ-НЕ";

25, 26 и 34 - выходные шины (первая, вторая и третья);

27 - элемент "НЕ";

28-элемент "ИЛИ";

30, 31 и 32 - сумматоры-ограничители взвешенной суммы (первый, второй и третий);

35 - операционный усилитель;

D1 - D8 - детекторы (первый, второй и т.д.);

K1 - K16 - управляемые ключи (первый, второй и т.д.)

R - резистор;

Uупр(±) - управляющее напряжение переключателя полярности сигналов.

Переключатель 17 полярности сигналов может быть выполнен на операционном усилителе по схеме фиг. 12.

Инверторы полярности 9, 12 и 20 и повторители 10, 11 и 21 могут быть выполнены на операционных усилителях.

Дифференциальные усилители-ограничители 13, 14, 23, 24 и 33 и сумматоры-ограничители 30, 31 и 32 взвешенной суммы могут быть выполнены на операционных усилителях, работающих в режиме ограничения амплитуды сигналов.

Во всех случаях в качестве операционного усилителя может быть использована микросхема К40УД7.

В качестве элемента "ИЛИ-НЕ" 22 может быть применена микросхема К501ЛЕ5, элемент 27 "НЕ" - микросхема К561ЛИ2, а элемент 28 "ИЛИ" может быть собран путем последовательного соединения этих микросхем.

Ключи К1 - К16 могут быть выполнены на микросхеме 590КИ2.

Устройство для кодирования чисел k = 0, 1, 2, 3 четверичной системы счисления может быть выполнено по схеме фиг. 2. Оно содержит: четыре входные шины 1, 2, 3, 4, две выходные шины 25 и 26 и два дифференциальных усилителя - первый 13 и второй 14.

Первая входная шина 1 через резистор R1 соединена с неинвертирующим входом первого дифференциального усилителя 13, вторая входная шина 2 через резистор R2 соединена с инвертирующим входом этого усилителя, третья входная шина 3 через резистор R3 соединена с неинвертирующим входом второго дифференциального усилителя 14, а четвертая входная шина 4 - через резистор R4 с инвертирующим входом этого усилителя. Выходы дифференциальных усилителей 13 и 14 соединены соответственно с выходными шинами 25 и 26.

Устройство работает следующим образом. На первую 1 и вторую 2 входные шины подают сигналы первого U0 и третьего U2 разряда унитарного кода, а на третью 3 и четвертую 4 входные шины - сигналы второго U1 и четвертого U3 разрядов. Сигналы унитарного кода U0, U1, U2 и U3 принимают значение "1" при кодировании соответствующего числа 0, 1, 2, 3, в остальных случаях их значение равно "0". Через дифференциальные усилители 13 и 14 сигналы U0 и U1, проходят без изменения полярности, а сигналы U2 и U3 - изменяют полярность. В результате на входе первого дифференциального усилителя 13 формируется сигнал cop4(ϕ), а на выходе второго усилителя 14 - сигнал sip4(ϕ), как показано на эпюрах фиг. 3.

Устройство для кодирования чисел k = 0, 1, 2, 3, 4, 5, 6, 7 восьмеричной системы счисления может быть выполнено по схеме фиг. 4. Оно содержит: восемь входных шин (1, 2, . .. 8) и два дифференциальных усилителя - первый 13 и второй 14.

Неинвертирующий вход первого дифференциального усилителя 13 через резисторы R1, R2 и R3 соединены с первой 1, второй 2 и третьей 3 входными шинами, соответственно. Инвертирующий вход этого усилителя через резисторы R4, R5 и R6 - с входными шинами 4, 5, 6. Неинвертирующий вход второго дифференциального усилителя 14 через резисторы R7, R8 и R9 соединены с входными шинами 2, 7, 4, соответственно, а инвертирующий вход этого усилителя через резисторы R10, R11 и R12 с входными шинами 6, 8 и 3 соответственно. Выход первого дифференциального усилителя 13 соединен с первой выходной шиной 25, а выход второго усилителя 14 со второй выходной шиной 26.

Устройство работает следующим образом. На входные шины 1-8 подают сигналы восьмиразрядного унитарного кода U0 - U7. Сигналы принимают значение "1" при кодировании соответствующего числа k = 0, 1 ... 7, в остальных случаях сигналы унитарного кода принимают значения "0", как показано на фиг. 5. При этом на первую 1 и вторую 2 входные шины подают сигналы первого U0 и U1 второго разрядов, на третью 3 входную шину - сигнал восьмого разряда U7, на четвертную 4, пятую 5, и шестую 6 входные шины подают сигналы четвертого U3, пятого U4 и шестого U7 разрядов, соответственно. На седьмую 7 шину подают сигнал третьего разряда U2, а на восьмую - сигнал седьмого разряда U7. Сигналы унитарного кода суммируют на дифференциальных усилителях 13 и 14 с полярностью, соответствующей фазо-волновому коду. Таким образом, на выходе первого дифференциального усилителя 13 формируют сигнал cop8(ϕ), а на выходе второго усилителя 14 - сигнал sip8(ϕ) (фиг. 4 и 5).

Устройство полного сложения-вычитания чисел может быть выполнено по схеме фиг. 6. Оно содержит: семь 1-5, 18 и 19 (первую, вторую, третью, четвертую, пятую, шестую и седьмую) входных шин, три 25, 26 и 34 (первую, вторую и третью) выходные шины, устройство 6 сложения-вычитания по модулю 4 и 8 с пятью входами и двумя выходами, устройство 7 сложения-вычитания с единицей переноса с четырьмя входными и двумя выходными шинами (фиг. 8) и устройство 8 формирования кода единицы переноса с семью входными и одной выходной шиной (фиг. 10).

Первые пять входных шин 1 - 5 соединены с соответствующими входами устройства 6 сложения-вычитания по модулям 4 или 8, и соответствующими входами устройства 8 формирования кода единицы переноса. Входные шины 18 и 19 соединены со входами сигнала единицы переноса sipq(ϕ±c) устройства 7 сложения-вычитания с единицей переноса, а его выходы с первой и второй выходными шинами 25 и 26. Два выхода сигналов суммы-разности по модулю 15 и 16 устройства 6 сложения-вычитания по модулю 4 или 8 соединены с двумя входами устройства 7 сложения-вычитания с единицей переноса. Первый и второй выходы устройства 7 сложения-вычитания с единицей переноса соединены с первым и вторым входами сигналов полной суммы-разности устройства 8 формирования единицы переноса, выходы которого соединены с третьей выходной шиной 34.

Устройство полного сложения-вычитания чисел (фиг. 6) работает следующим образом. Сигналы кодов чисел первого слагаемого или уменьшаемого -copq(ϕx), sipq(ϕx) подают на первую 1 и вторую 2 входные шины, а сигналы кодов чисел второго слагаемого или вычитаемого -copq(ϕy), sipq(ϕy) подают на третью 3 и четвертую 4 входные шины. На пятую входную шину 5 подают сигнал управления Uупр(±) режимами "сложения", "вычитания". По этим пяти сигналам в устройстве 6 сложения-вычитания формируют на входах 15, 16 сигналы кодов суммы-разности по модулю (mod4), (mod8)  которые подают на входы устройства 7 сложения-вычитания с единицей переноса. При этом сигнал кода единицы переноса -sipq(±ϕc) подают на вход устройства 7 через входную шину 18. По сигналам copq(ϕ±s), sipq(ϕ±s) и sipq(±ϕc) в устройстве сложения-вычитания 7 с единицей переноса формируют сигналы кодов полной суммы-разности чисел copq(ϕ±s±1) и sipq(ϕ±s±1), которые подают на выходные шины 25, 26. Кроме того сигналы и copq(ϕx), sipq(ϕx), copq(ϕy), sipq(ϕy) и Uупр(±) с входных шин 1 - 5 и выходных шин 25, 26 подают на входы устройства 8 формирования сигналов кода единицы переноса в следующий по старшинству разряд. По этим сигналам в устройстве 8 формируют сигнал ±sipq(ϕ±c±1) кода единицы переноса, который подают на выходную шину 34. В устройстве 7 сложения-вычитания с единицей переноса предусмотрено переключение режимов сложения-вычитания для различных систем счисления с основаниями q = 4 и q = 8. Для этого на вход 19 устройства 7 подают сигнал U(q).

которые подают на входы устройства 7 сложения-вычитания с единицей переноса. При этом сигнал кода единицы переноса -sipq(±ϕc) подают на вход устройства 7 через входную шину 18. По сигналам copq(ϕ±s), sipq(ϕ±s) и sipq(±ϕc) в устройстве сложения-вычитания 7 с единицей переноса формируют сигналы кодов полной суммы-разности чисел copq(ϕ±s±1) и sipq(ϕ±s±1), которые подают на выходные шины 25, 26. Кроме того сигналы и copq(ϕx), sipq(ϕx), copq(ϕy), sipq(ϕy) и Uупр(±) с входных шин 1 - 5 и выходных шин 25, 26 подают на входы устройства 8 формирования сигналов кода единицы переноса в следующий по старшинству разряд. По этим сигналам в устройстве 8 формируют сигнал ±sipq(ϕ±c±1) кода единицы переноса, который подают на выходную шину 34. В устройстве 7 сложения-вычитания с единицей переноса предусмотрено переключение режимов сложения-вычитания для различных систем счисления с основаниями q = 4 и q = 8. Для этого на вход 19 устройства 7 подают сигнал U(q).

Устройство сложения-вычитания чисел по модулям 4 и 8 выполняется по схеме фиг. 7 и содержит: пять входных (первую, вторую, третью, четвертую и пятую) 1 - 5 и две (первую и вторую) выходных 15 и 16 шины, два (первый и второй) инвертора 9 и 12 полярности, два (первый и второй) повторителя 10 и 11, два (первый и второй) дифференциальных усилителя-ограничителя 13 и 14, переключатель 17 полярности сигналов, четыре (первый, второй, третий и четвертый) детектора Д1 - Д4 и восемь (первый, второй и т.д.) управляемых ключей К1 - К8.

Первая входная шина 1 соединена через первый ключ К1 с неинвертирующим вводом первого дифференциального усилителя-ограничителя 13, а через второй ключ К2 с инвертирующим входом этого же усилителя, первая входная шина через седьмой ключ К7 также подключена к инвертирующему входу второго дифференциального усилителя-ограничителя 14, а через восьмой ключ К8 - к неинвертирующему входу этого же усилителя.

Вторая входная шина 2 через третий ключ К3 соединена с неинвертирующим входом первого дифференциального усилителя-ограничителя 13, а через четвертый ключ К4 - с инвертирующим входом того же усилителя, вторая входная шина через шестой ключ К6 также соединена с неинвертирующим входом второго дифференциального усилителя-ограничителя 14 и через пятый ключ К5 - с инвертирующим входом того же усилителя.

Третья входная шина 3 соединена со входами первого инвертора полярности 9 и первого повторителя 10. Выход первого повторителя 10 через второй детектор Д2 соединен с управляющими входами первого и шестого ключей К1 и К6, а выход первого инвертора полярности 9 через первый детектор Д1 соединен с управляющими входами второго и пятого ключей К2 и К5.

Четвертая входная шина 4 через первый переключатель полярности 17 соединена со входами второго повторителя 11 и второго инвертора полярности 12.

Пятая входная шина соединена с управляющим входом первого переключателя полярности 17.

Выходы первого 13 и второго 14 дифференциальных усилителей-ограничителей соединены с выходными шинами 15 и 16 соответственно.

Выход второго повторителя 11 через третий детектор Д3 соединен с управляющими входами четвертого и восьмого ключей К4 и К8, а выход второго инвертора полярности 12, через четвертый детектор Д4 соединен с управляющими входами третьего и седьмого ключей К3 и К7.

Устройство сложения-вычитания чисел работает следующим образом. На первую 1 и вторую 2 входные шины подают сигналы copq(ϕx) и sipq(ϕx) соответственно, которые представляют коды чисел первого слагаемого или уменьшаемого в четверичной (q = 4) или в восьмеричной (q = 8) системах счисления. На третью 3 и четвертую 4 шины подают сигналы copq(ϕy) и sipq(ϕy) второго слагаемого или вычитаемого соответственно.

По сигналу copq(ϕy) положительной полярности замыкается ключ К1, и сигнал copq(ϕx) передается через первый дифференциальный усилитель 13 на выходную шину 15 без изменения полярности. По сигналу copq(ϕy) отрицательной полярности замыкается ключ К2 и сигнал copq(ϕx) передается на выходную шину 15 через этот усилитель 13 с инверсией полярности. При нулевом уровне сигнала copq(ϕy) оба первый и второй ключи К1 и К2 разомкнуты и на выходе первого усилителя 13 сигнал copq(ϕx) отсутствует. Такая операция коммутации ключей эквивалентна перемножению сигналов copq(ϕx) и copq(ϕy).

По сигналу sipq(ϕy) положительной полярности замыкается четвертый ключ К4, и сигнал sipq(ϕx) подключается к инвертирующему входу первого дифференциального усилителя-ограничителя 13. В результате чего на первую выходную шину 15 передается сигнал sipq(ϕx) с инверсной полярностью.

По сигналу sipq(ϕy) отрицательной полярности замыкается третий ключ К3, и сигнал sipq(ϕx) передается через первый дифференциальный усилитель 13 на выходную шину 15 без изменения полярности. При нулевом уровне сигнала sipq(ϕy) сигнал sipq(ϕx) на выходную шину 15 не передается, так как третий и четвертый ключи К3 и К4 разомкнуты. Таким образом, на выходной шине 15 формируют сигнал произведения -sipq(ϕx)•sipq(ϕy).

В результате операции коммутации первых четырех ключей K1, K2, К3 и К4 сигналами copq(ϕy) и sipq(ϕy) на первой выходной шине 15 формируют сигнал:

Для формирования сигналов sipq(ϕ+s) = sipq(ϕx+ϕy) используют коммутацию остальных ключей К5, К6, К7 и К8.

По сигналу copq(ϕy) положительной полярности замыкается шестой ключ К6, а по сигналу отрицательной полярности - пятый ключ К5. В результате чего на выходе второго дифференциального усилителя-ограничителя 14 формируется сигнал sipq(ϕx)•copq(ϕy).

По сигналу sipq(ϕy) положительной полярности замыкается восьмой ключ К8, а при отрицательной полярности - седьмой ключ К7. При этом на выходе второго дифференциального усилителя-ограничителя 14 формируют сигнал copq(ϕx)•sipq(ϕy). Таким образом, в результате коммутации ключей К5, К6, К7 и К8 по описанному алгоритму на второй выходной шине 16 формируют сигнал:

Амплитуда сигналов на выходах дифференциальных усилителей при линейном суммировании сигналов восьмеричных кодов (q = 8) может принимать значения 0, ±1, ±2 (фиг. 9). Для получения нормированных сигналов cop8(ϕx+ϕy) и sip8(ϕx+ϕy) дифференциальные усилители 13 и 14 работают в режиме ограничения амплитуды на уровне Uor = ±1.

Описанный принцип действия устройства сложения-вычитания чисел относится к режиму сложения фаз. В этом режиме переключатель полярности 17 работает в режиме повторителя.

Для выполнения операции вычитания фаз сигналов на управляющий вход переключателя полярности 17 по пятой входной шине 5 подают сигнал Uупр(±) для инверсии полярности сигналов sipq(ϕy). В этом режиме устройство сложения-вычитания выполняет операцию вычитания фаз сигналов в соответствии с формулами (9) и (10):

а следовательно вычитание чисел, кодируемых фазами.

Устройство сложения-вычитания с единицей переноса выполняется по схеме фиг. 8 и содержит: четыре (первую, вторую, третью и четвертую) входные шины 15, 16, 18 и 19 и две (первую и вторую) выходные шины 25 и 26, инвертор полярности 20, повторитель 21, элемент "ИЛИ-НЕ" 22, первый и второй дифференциальные усилители-ограничители 23 и 24, элемент "НЕ" 27, элемент "ИЛИ" 28, два (первый и второй) детектора Д5 и Д6 и семь (первый, второй и т.д.) управляемых ключей К9 - К15.

Первая входная шина 15 через пятый ключ К13 соединена с неинвертирующим входом первого дифференциального усилителя-ограничителя 23 через третий ключ К11 с неинвертирующим входом второго дифференциального усилителя-ограничителя 24 и через четвертый ключ К12 с инвертирующим входом этого усилителя.

Вторая входная шина 16 соединена через шестой ключ К14 с неинвертирующим входом второго дифференциального усилителя-ограничителя 24, через первый ключ К9 с неинвертирующим входом первого дифференциального усилителя-ограничителя 23 и через второй ключ К10 - с инвертирующим входом того же усилителя.

Третья входная 18 соединена со входами инвертора полярности 20 и повторителя 21. Выход инвертора полярности 20 соединен через пятый детектор Д5 с управляющими входами первого и четвертого ключей К9 и К12 и первым входом элемента "ИЛИ-НЕ" 22, а выход повторителя 21 соединен через шестой детектор Д6 с управляющими входами второго и третьего ключей К10 и К11 и вторым входом элемента "ИЛИ-НЕ" 22. Выход элемента "ИЛИ-НЕ" 22 через седьмой ключ К15 соединен с первым входом элемента "ИЛИ" 28, выход которого соединен с управляющими входами пятого и шестого ключей К13 и К14.

Четвертая входная шина 19 соединена с управляющим входом седьмого ключа К15 и через элемент "НЕ" 27 со вторым входом элемента "ИЛИ" 28.

Выходы первого 23 и второго 24 дифференциальных усилителей-ограничителей соединены с первой 25 и второй 26 выходными шинами, соответственно.

Собственно операция сложения-вычитания с единицей переноса осуществляется в восьмеричной системе счисления с помощью ключей К9 - К12 и двух дифференциальных усилителей, а в четверичной системе используют дополнительно ключи К13 и К14. Элементы 20, 21, 22 и детекторы служат для управления ключами, а элементы 27 и 28 и ключ К15 - для переключения системы счисления (q = 4 - 8).

Устройство работает следующим образом. На первую 15 и вторую 16 входные шины подают сигналы кодов суммы или разности чисел по модулям с выхода устройства сложения-вычитания по модулям copq(ϕ±s) и sipq(ϕ±s) соответственно. На третью шину 18 подают сигнал переноса из предыдущего разряда sipq(ϕc) = 1 при сложении, sipq(ϕ-c) = -1 при вычитании и sipq(ϕo) = 0 при отсутствии единицы переноса. На четвертую шину 19 подают сигнал U(q) переключения системы счисления, при этом сигнал низкого уровня U(q) = 0 соответствует восьмеричной системе счисления, а сигнал высокого уровня U(q) = 1 - четверичной системе счисления.

1. Режим восьмеричной системы счисления

В этом режиме U(q) = 0 и ключ К15 разомкнут, на выходе элемента "НЕ" - потенциал высокого уровня, который через элемент "ИЛИ" передается на управляющие входы ключей К13 и К14, при этом эти ключи постоянно замкнуты, независимо от состояния сигнала переноса sipq(ϕ±c). При C = 0 - отсутствие единицы переноса, сигнал sipq(ϕ±c) = 0, ключи К9 - К12 разомкнуты и сигналы суммы или разности по модулю cop8(ϕ±c) и sip8(ϕ±c) передаются через дифференциальные усилители 23 и 24 на выходные шины 25 и 26 без изменения в соответствии с формулами (19а), (20а) (21а) и (22а), то есть при сложении:

а при вычитании:

При наличии единицы переноса C = 1 в режиме сложения сигнал sip8(ϕc) = 1. Этот сигнал через повторитель 21 и детектор положительной полярности Д6 подается на управляющие входы ключей К10 и К11, и эти ключи замыкаются, сигнал sip8(ϕs) подключается к инвертирующему входу первого дифференциального усилителя-ограничителя 23, а сигнал cop8(ϕs) подключается к неинвертирующему входу второго дифференциального усилителя-ограничителя 24. При этом на выходе первого дифференциального усилителя-ограничителя 23 в соответствии с формулой (19б) формируется сигнал:

На выходе второго дифференциального усилителя-ограничителя 24 в соответствии с формулой (20б) формируется сигнал:

При наличии единицы переноса C = -1 при вычитании сигнал sip8(ϕ-c) = -1. Этот сигнал через инвертор 20 и детектор положительной полярности Д5 подается на управляющие входы ключей К9 и К12, и эти ключи замыкаются, сигнал sip8(ϕ-s) подключается к неинвертирующему входу первого дифференциального усилителя-ограничителя 23, а сигнал cop8(ϕ-s) подключается к инвертирующему входу второго дифференциального усилителя-ограничителя 24. При этом на выходе первого дифференциального усилителя-ограничителя 23 в соответствии с формулой (21б) формируется сигнал:

а на выходе второго дифференциального усилителя-ограничителя 24 в соответствии с формулой (22б) формируется сигнал:

Таким образом, коммутация ключей К9 - К12 по описанному алгоритму обеспечивает сдвиг фаз суммы или разности по модулю кодов на ±π/4, следовательно, сдвиг на +1 чисел, кодируемых фазами сигналов. Процесс сдвига фазы на ϕ = π/4 при сложении иллюстрируют эпюры фиг. 9. Эпюры показывают, что при линейном суммировании или вычитании сигналов  амплитуды выходных сигналов могут принимать значения U(s) = 0, ±1, ±2. Для нормирования амплитуды дифференциальные усилители работают в режиме ограничения на уровне Uor = ±1.

амплитуды выходных сигналов могут принимать значения U(s) = 0, ±1, ±2. Для нормирования амплитуды дифференциальные усилители работают в режиме ограничения на уровне Uor = ±1.

2. Режим четверичной системы счисления

В этом режиме на четвертую входную шину 19 подают сигнал высокого уровня U(q) = 1. При этом ключ К15 замыкается, а блокировка ключей К13 и К14 по цепи: элемент "НЕ" 27 и элемент "ИЛИ" 28 снимается.

При отсутствии единицы переноса C = 0 сигнал sip4(ϕ±c) = 0. В этом случае на обоих входах элемента "ИЛИ-НЕ" 22 присутствует потенциал низкого уровня, а на его выходе - потенциал высокого уровня "1". Этот потенциал через замкнутый ключ К15 и элемент "ИЛИ" 28 подается на управляющие входы ключей К13 и К14 и замыкая их. В таком режиме сигналы суммы или разности кодов сумматора-вычитателя по модулю передаются через дифференциальные усилители 23 и 24 на выходные шины без изменения в соответствии с формулами (15а), (16а), (17а) и (18а):

При наличии единицы переноса C = 1 в режиме сложения чисел сигнал sip4(ϕc) = 1. Этот сигнал через повторитель 21 и детектор Д6 подается на управляющие входы ключей К10 и К11 и замыкает их, и на второй вход элемента "ИЛИ-НЕ" 22. При этом на выходе элемента "ИЛИ-НЕ" 22 появляется потенциал низкого уровня, который через замкнутый ключ К15 и элемент "ИЛИ" 28 подается на управляющие входы ключей К13 и К14 размыкая их. Таким образом, сигнал cop4(ϕs) первой выходной шине 25 заменяется сигналом -sip4(ϕc), а сигнал sip4(ϕs) заменяется на второй выходной шине 26 сигналом cop4(ϕs) в соответствии с формулами (15б) и (16б).

При наличии единицы переноса C = -1 в режиме вычитания чисел сигнал sip4(ϕ-s) = -1. Этот сигнал через инвертор полярности 20 в качестве положительного потенциала после детектора Д5 подается на ключи К9 и К12, замыкая их, и на первый вход элемента "ИЛИ-НЕ" 22. При этом на выходе элемента "ИЛИ-НЕ" 22 появляется потенциал низкого уровня, который через замкнутый ключ К15 и элемент "ИЛИ" 28 подается на управляющие входы ключей К13 и К14 размыкая их. Таким образом, сигнал cop4(ϕ-s) заменяется на первый выходной шине 25 сигналом +sip4(ϕ-s), a сигнал sip4(ϕ-s) заменяется на второй выходной шине 26 сигналом - cop4(ϕ-s) соответствии с формулами (17б) и (18б):

Таким образом, коммутация ключей К9 - К14 по описанному алгоритму обеспечивает сдвиг фаз суммы или разности по модулю на ±π/2, а следовательно, сдвиг на ±1 чисел, кодируемых фазами сигналов.

Устройство формирования кода единицы переноса может быть выполнено по схеме фиг. 10. Оно содержит семь входных 1 - 5, 25 и 26 (первую, вторую и т. д.) и одну выходную 34 шины, первый 29 и второй 17 переключатели полярности, первый 30, второй 31 и третий 32 сумматоры сигналов с весом 1:2 - ограничители, дифференциальный усилитель-ограничитель 33, переключатель К16, первый Д7 и второй Д8 детекторы.

Первая входная шина 1 соединена с первым входом второго сумматора-ограничителя 31, а вторая входная шина 2 соединена со вторым входом этого сумматора. Выход сумматора 31 соединен с инвертирующим входом дифференциального усилителя-ограничителя 33.

Третья входная шина 3 через первый переключатель полярности 29 соединена с первым входом третьего сумматора-ограничителя 32, а четвертая входная шина 4 через второй переключатель полярности 17 соединена со вторым входом этого сумматора. Выход сумматора 32 соединен с инвертирующим входом дифференциального усилителя 33.

Пятая входная шина 5 соединена с управляющими входами переключателей полярности 17 и 29 и переключателя К16.

Шестая входная шина 25 соединена с первым входом первого сумматора-ограничителя 30, а седьмая входная шина 26 соединена со вторым входом этого сумматора. Выход первого сумматора-ограничителя 30 соединен с неинвертирующим входом дифференциального усилителя-ограничителя 33.

Выход дифференциального усилителя-ограничителя 33 соединен со входом переключателя К16, выход которого подключен ко входам либо первого Д7, либо второго Д8 детекторов. Выходы детекторов соединены с выходной шиной 34.

Устройство работает следующим образом. На первую 1 и вторую 2 входные шины подают сигналы copq(ϕx) и sipq(ϕx) соответственно, которые представляют коды чисел первого слагаемого или уменьшаемого. На третью 3 и четвертую 4 входные шины подают сигналы copq(ϕy) и sipq(ϕy) соответственно, представляющие коды чисел второго слагаемого или вычитаемого. На пятую 5 входную шину подают управляющий сигнал Uупр(±) переключателя режима "сложение-вычитание". На шестую 25 и седьмую 26 входные шины подают сигналы copq(ϕ±s±1) и sipq(ϕ±s±1) соответственно с выходов 25 и 26 устройства 7 сложения-вычитания чисел с учетом единицы переноса из предыдущего разряда.

Задача состоит в том, чтобы сформировать сигналы ±sipq(ϕ±c±1) кодов единицы переноса, которые принимали бы значения в зависимости от значений кодов ϕx и ϕy в четверичной системе счисления при сложении чисел в соответствии с таблицей 32 при отсутствии переноса из предыдущего разряда и с таблицей 33 при наличии единицы переноса. При вычитании чисел значения сигналов -sip4(ϕ-c) и -sip4(ϕ-c-1) должны соответствовать таблицам 34 и 35. В восьмеричной системе счисления необходимо сформировать сигналы sip8(ϕc) и sip8(ϕc+1) при сложении чисел в соответствии с таблицами 36 и 38 и при вычитании чисел сигналы -sip8(ϕ-c) и -sip8(ϕ-c-1) в соответствии с таблицами 37 и 39. Эти требования вытекают непосредственно из правил сложения-вычитания (таблицы 12 -19 см. в конце описания).

Поставленная задача достигается следующим образом. Сигналы кодов суммы-разности copq(ϕ±s±1) и sipq(ϕ±s±1) с выходов 25 и 26 устройства сложения-вычитания чисел подают на сумматор 30, при этом сигнал sipq(ϕ±s±1) удвоенной амплитуды 2sipq(ϕ±s±1) суммируют с сигналом copq(ϕ±s±1), то есть вес первого входа сумматора W1=1, а вес второго W2=2. При линейном суммировании амплитуда выходного сигнала сумматора в восьмеричной системе счисления может принимать значения  0, ±1, ±2, ±3, как показано на эпюре фиг. 11. Для формирования сигнала единичной амплитуды сумматор работает в режиме ограничения на уровне Uor = ±1. При этом формируют сигнал U8(±cs±1). На фиг. 11 для примера показан подобный сигнал U8(c) для случая сложения при ϕy= 0 и при отсутствии единицы переноса из предыдущего разряда. Для значений фазы ϕy от ϕy= 0 до ϕy= 7π/4 при отсутствии единицы переноса в режиме сложения чисел формируются сигналы U4(cs) в четверичной системе счисления и сигналы U8(cs) - в восьмеричной системе счисления при суммировании сигналов copq(ϕs) и sipq(ϕs) c весами W1/W2 = 1/2 в соответствии с таблицами 20 и 24. В этом не трудно убедится непосредственным сложением сигналов copq(ϕs) и 2sipq(ϕs) в таблицах 12 и 14 с учетом ограничения амплитуды выходного сигнала. Аналогично, в режиме вычитания чисел формируются сигналы U4(-cs) и U8(-cs) в соответствии с таблицами 21 и 25, соответственно, которые получаются при сложении с весом сигналов copq(ϕ-s) и sipq(ϕ-s) по таблицам 13 и 15 с ограничением амплитуды.

0, ±1, ±2, ±3, как показано на эпюре фиг. 11. Для формирования сигнала единичной амплитуды сумматор работает в режиме ограничения на уровне Uor = ±1. При этом формируют сигнал U8(±cs±1). На фиг. 11 для примера показан подобный сигнал U8(c) для случая сложения при ϕy= 0 и при отсутствии единицы переноса из предыдущего разряда. Для значений фазы ϕy от ϕy= 0 до ϕy= 7π/4 при отсутствии единицы переноса в режиме сложения чисел формируются сигналы U4(cs) в четверичной системе счисления и сигналы U8(cs) - в восьмеричной системе счисления при суммировании сигналов copq(ϕs) и sipq(ϕs) c весами W1/W2 = 1/2 в соответствии с таблицами 20 и 24. В этом не трудно убедится непосредственным сложением сигналов copq(ϕs) и 2sipq(ϕs) в таблицах 12 и 14 с учетом ограничения амплитуды выходного сигнала. Аналогично, в режиме вычитания чисел формируются сигналы U4(-cs) и U8(-cs) в соответствии с таблицами 21 и 25, соответственно, которые получаются при сложении с весом сигналов copq(ϕ-s) и sipq(ϕ-s) по таблицам 13 и 15 с ограничением амплитуды.

При наличии единицы переноса из предыдущего разряда формируют сигналы U4(cs+1) и U8(cs+1) в соответствии с таблицами 22 и 26 (см. в конце описания) при сложении чисел и сигналы U4(-cs-1) и U8(-cs-1) по таблицам 23 и 27 соответственно (см. в конце описания) при вычитании чисел.

С выхода первого сумматора-ограничителя 30 сигналы Uq(±cs) и Uq(±cs±1) подают на неинвертирующий вход дифференциального усилителя-ограничителя 33.

Сигналы Uq(±cs) и Uq(±cs±1), как видно из таблиц 20 - 23 и 24 - 27 (см. в конце описания), обладают неоднозначностью в области всех значений аргументов ϕx и ϕy. Так, в секторе углов 0 ≤ ϕx< π и 0 ≤ ϕy< π сигналы Uq(cs) и Uq(cs±1) при сложении имеют такие же значения, какие необходимы для формирования кода единицы переноса. При вычитании неоднозначность проявляется при π ≤ ϕx≤ 7π/4 и при 0 ≤ ϕy< π.

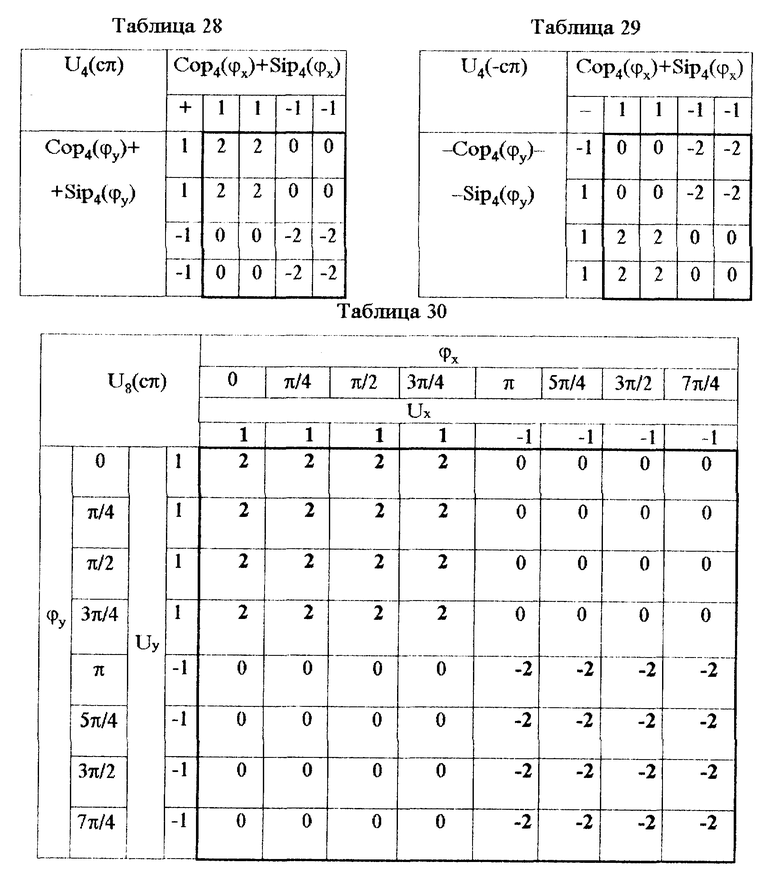

Для устранения неоднозначности формируют дополнительные сигналы Uq(±cπ).

Предварительно формируют сигнал Ux путем суммирования сигналов copq(ϕx) и sipq(ϕx) на втором сумматоре 31 с весом W1/W2 = 1/2 и последующим ограничением, аналогично тому, как это выполнялось с сигналами copq(ϕ±s±1) и sipq(ϕ±s±1) нa первом сумматоре-ограничителе 30. Кроме того формируют сигналы ±Uy путем суммирования с весом 1/2 сигналов copq(ϕy) и sipq(ϕy) c последующим ограничением амплитуды на третьем сумматоре-ограничителе 32. Сигналы copq(ϕy) и sipq(ϕy) подают на сумматор-ограничитель 32 через переключатели полярности 29 и 17, которые работают как повторители в режиме сложения чисел и как инверторы полярности - в режиме вычитания чисел. Переключение режимов сложения-вычитания осуществляется сигналом Uупр(±). Сигналы Ux и ±Uy суммируют на инвертирующем входе дифференциального усилителя-ограничителя 33. В результате такого суммирования формируют сигналы в четверичной системе счисления U4(cπ) в соответствии с таблицей 28 в режиме сложения чисел и сигналы U4(-cπ) в соответствии с таблицей 29 - в режиме вычитания чисел. В восьмеричной системе счисления при сложении чисел формируют сигналы U8(cπ) по таблице 30 и сигналы U8(-cπ) по таблице 31 - при вычитании чисел (табл. 30 и 31 см. в конце описания).

При вычитании сигналов Uq(±cπ) из сигналов Uq(±c) или Uq(±c±1) устраняется неоднозначность кодов, а выходные сигналы единичной амплитуды получают за счет того, что дифференциальный усилитель 33 работает в режиме ограничения. Однако выходные сигналы дифференциального усилителя получаются биполярными как в режиме сложения чисел, так и в режиме вычитания чисел.

Для получения однозначных по полярности сигналов кода единицы переноса 0- +sipq(ϕ+c+1) при сложении чисел и 0 - -sipq(ϕ-c-1) при вычитании чисел используют детекторы Д7 и Д8. При этом в режиме сложения чисел выход дифференциального усилителя-ограничителя 33 с помощью переключателя К16 подключается к детектору положительной полярности Д7, а в режиме вычитания чисел к детектору отрицательной полярности Д8.

Таким образом, на выходной шине 34 формируют сигналы кода единицы переноса при сложении и вычитании чисел в четверичной, в соответствии с таблицами 32 - 35, и восьмеричной системах счисления в соответствии с таблицами 36 - 39, которые составлены по правилам арифметики (табл. 32-39 см. в конце описания).

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1997 |

|

RU2109325C1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА ВО МНОГОЗНАЧНЫЙ КОД (ВАРИАНТЫ) | 1997 |

|

RU2109400C1 |

| ЛОГИЧЕСКОЕ УСТРОЙСТВО "И" | 2004 |

|

RU2281605C2 |

| ЛОГИЧЕСКОЕ УСТРОЙСТВО "ИЛИ" | 2004 |

|

RU2278469C1 |

| ЛОГИЧЕСКОЕ УСТРОЙСТВО "ОТРИЦАНИЕ" (ВАРИАНТЫ) | 2004 |

|

RU2287895C2 |

| Аналоговое запоминающее устройство | 1977 |

|

SU723686A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU750569A1 |

| Устройство для деления | 1976 |

|

SU598075A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU866577A2 |

| Многоразрядное суммирующее устройство | 1976 |

|

SU602967A1 |

Способ сложения-вычитания чисел основан на формировании двух трехуровневых сигналов copq(2πkx/q), sipq(2πky/q), copq(2πky/q), sipq(2πky/q), по волновым функциям Попова - popq(ϕ). Эти функции представляют двумя ортогональными составляющими: popq(ϕ) = copq(ϕ)+isipq(ϕ). Каждое число Kх и Ky от Kx,y = 0 до Kх,у = g -1, в системах счисления с основанием g = 4 и g =8, представляют фазами ϕx,y = 2πkx,y/q. Каждую фазу ϕx,y кодируют значениями уровней сигналов copq(2πkx,y/q) и sipq(2πkx,y/q). Значения ортогональных составляющих функций Попова copq(ϕ) и sipq(ϕ) определяют путем сравнения с порогами ±ξ соответствующих тригонометрических функций cosϕ и sinϕ при значении аргумента ϕ = 2πk/q. Техническим результатом изобретения является расширение функциональных возможностей, предусматривающих кодирование чисел трехуровневыми сигналами, их сложение и вычитание в системах счисления с основаниями g= 4 и g=8. Для сложения фаз формируют сигналы cорg (s) и sip g (s), а для вычитания - cорg (-s), sipg (-s), которые представляют коды суммы и разности чисел слагаемых Kх и Ky. Сложение и вычитание фаз производят в соответствии с известными формулами сложения и вычитания фаз синусоидальных волн. 3 с.п. ф-лы, 12 ил., 41 табл.

popq(ϕ) = copq(ϕ)+i•sipq(ϕ),

каждое число-цифру kx и ky, которые могут изменяться от kx,y = 0 до kx,y = q - 1 в системах счисления с основанием q = 4 и q = 8, представляют фазами ϕx,y= 2πkx,y/q, каждую фазу ϕx,y кодируют значениями уровней сигналов Copq(2πkx,y/q) и Sipq((2πkx,y/q), причем значения ортогональных составляющих функций Попова Copq(ϕ) и Sipq(ϕ) определяют путем сравнения с порогами ±ξ соответствующих тригонометрических функций cosϕ и sinϕ при значениях аргумента ϕ = 2πk/q, как

при этом значение порога может быть любым в пределах

затем формируют сигналы:

- первого произведения Copq(ϕx)•Copq(ϕy),

- второго произведения Sipq(ϕx)•Sipq(ϕy),

- третьего произведения Sipq(ϕx)•Copq(ϕy),

- четвертого произведения Copq(ϕx)•Sipq(ϕy),

после чего для сложения чисел kx и ky формируют сигналы первой разности:  и первой суммы:

и первой суммы:  которые представляют коды суммы чисел слагаемых kx и ky при отсутствии единицы переноса из предыдущего разряда, а при вычитании из уменьшаемого числа kx вычитаемого числа ky формируют сигналы второй суммы:

которые представляют коды суммы чисел слагаемых kx и ky при отсутствии единицы переноса из предыдущего разряда, а при вычитании из уменьшаемого числа kx вычитаемого числа ky формируют сигналы второй суммы:  и второй разности:

и второй разности:  которые представляют коды разности чисел слагаемых kx и ky при отсутствии единицы переноса из предыдущего разряда, и при наличии единицы переноса из предыдущего разряда при суммировании чисел в четверичной системе счисления сигнал первой разности заменяют инверсным по полярности сигналом первой суммы, сигнал первой суммы заменяют сигналом первой разности, при этом в восьмеричной системе счисления из сигналов первой разности вычитают сигнал первой суммы, а также сигнал первой разности суммируют с сигналом первой суммы, а при вычитании чисел и при наличии единицы переноса из предыдущего разряда в четвертичной системе счисления сигнал второй суммы заменяют сигналом второй разности, а сигнал второй разности заменяют инверсным по полярности сигналом второй суммы, при этом в восьмеричной системе счисления сигнал второй суммы суммируют с сигналом второй разности, а также из сигнала второй разности вычитают сигналы второй суммы и, кроме того, формируют сигнал единицы переноса в следующий разряд при суммировании, если фазы кодов обоих слагаемых ϕx и ϕy не меньше π, а также когда сумма фаз кодов чисел лежит в пределах от 0 до π и при этом фаза кодов хотя бы одного из слагаемых не меньше π, а при вычитании сигнал единицы переноса формируют, если фаза кода уменьшаемого ϕx меньше π и фаза кода вычитаемого не меньше π, а также, когда фаза кода разности чисел лежит в пределах от π до 2π, и при этом либо фаза кода уменьшаемого ϕx меньше π, либо фаза кода вычитаемого ϕy не меньше π.

которые представляют коды разности чисел слагаемых kx и ky при отсутствии единицы переноса из предыдущего разряда, и при наличии единицы переноса из предыдущего разряда при суммировании чисел в четверичной системе счисления сигнал первой разности заменяют инверсным по полярности сигналом первой суммы, сигнал первой суммы заменяют сигналом первой разности, при этом в восьмеричной системе счисления из сигналов первой разности вычитают сигнал первой суммы, а также сигнал первой разности суммируют с сигналом первой суммы, а при вычитании чисел и при наличии единицы переноса из предыдущего разряда в четвертичной системе счисления сигнал второй суммы заменяют сигналом второй разности, а сигнал второй разности заменяют инверсным по полярности сигналом второй суммы, при этом в восьмеричной системе счисления сигнал второй суммы суммируют с сигналом второй разности, а также из сигнала второй разности вычитают сигналы второй суммы и, кроме того, формируют сигнал единицы переноса в следующий разряд при суммировании, если фазы кодов обоих слагаемых ϕx и ϕy не меньше π, а также когда сумма фаз кодов чисел лежит в пределах от 0 до π и при этом фаза кодов хотя бы одного из слагаемых не меньше π, а при вычитании сигнал единицы переноса формируют, если фаза кода уменьшаемого ϕx меньше π и фаза кода вычитаемого не меньше π, а также, когда фаза кода разности чисел лежит в пределах от π до 2π, и при этом либо фаза кода уменьшаемого ϕx меньше π, либо фаза кода вычитаемого ϕy не меньше π.

2. Устройство сложения-вычитания чисел по модулям 4 и 8, содержащее пять входных (первую, вторую, третью, четвертую и пятую) и две (первую и вторую) выходных шины, отличающееся тем, что в него введены два (первый и второй) инвертора полярности, два (первый и второй) повторителя, два (первый и второй) дифференциальных усилителя-ограничителя, переключатель полярности сигналов, четыре (первый, второй, третий и четвертый) детектора и восемь (первый, второй и т.д.) управляемых ключей, причем первая входная шина соединена через первый ключ с неинвертирующим входом первого дифференциального усилителя-ограничителя, а через второй ключ - с инвертирующим входом этого же усилителя, и через седьмой ключ также подключена к инвертирующему входу второго дифференциального усилителя-ограничителя, а через восьмой ключ - к неинвертирующему входу этого же усилителя, вторая входная шина через третий ключ соединена с неинвертирующим входом первого дифференциального усилителя-ограничителя, а через четвертый ключ - с инвертирующим входом того же усилителя, а также через шестой ключ соединена с неинвертирующим входом второго дифференциального усилителя-ограничителя и через пятый ключ - с инвертирующим входом того же усилителя, третья входная шина соединена со входами первого инвертора полярности и первого повторителя, выход которого через второй детектор соединен с управляющими входами первого и шестого ключей, кроме того, выход первого инвертора полярности через первый детектор соединен с управляющими входами второго и пятого ключей, четвертая входная шина через первый переключатель полярности соединена со входами второго повторителя и второго инвертора полярности, причем пятая входная шина соединена с управляющим входом первого переключателя полярности, кроме того, выходы первого и второго дифференциальных усилителей - ограничителей соединены с первой и второй выходными шинами устройства соответственно, выход второго повторителя через третий детектор соединен с управляющими входами четвертого и восьмого ключей, а выход второго инвертора полярности через четвертый детектор соединен с управляющими входами третьего и седьмого ключей.

| 1972 |

|

SU416691A1 | |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ —ВЫЧИТАНИЯ | 0 |

|

SU407308A1 |

| US 4979141 A, 18.12.90 | |||

| СПОСОБ РАЗРАБОТКИ ПОЛОГОПАДАЮЩИХ УГОЛЬНЫХ ПЛАСТОВ | 0 |

|

SU353041A1 |

Авторы

Даты

1999-06-27—Публикация

1998-01-23—Подача