Изобретение относится к автоматическому регулированию технологических процессов, а именно к аналогоцифровым интегрирующим устройствам, снабженным входами логического управления и средствами для регулируемого ограничения выходного сигнала и индикации достижения выходным сигналом заданных верхнего и нижнего уровней, преимущественно входящим в виде отдельных конструктивных блоков в те или иные агрегатные комплексы электрических средств регулирования.

Известно интегрирующее устройство которое содержит аналого-цифровой интегратор, снабженный информационными аналоговыми входами и выходом, группой управляющих входов, два компаратора, первые входы которых соединены с информационным выходом интегратора, вторые входы - с задатчиками верхней и нижней уставок, выходы с соответствуквдими реле индикации и с соответствующими входами запрета увеличения и уменьшения выходного сигнала интегратора С I ,

Указанное интегрирующее устройств обладает недостаточно широкими функциональными возможностями, в частности оно не обеспечивает возможностей дистанционного реверсирования интегратора, дистанционных введения и сня. тия уровней ограничения, а также работы в бесконтактных следящих системах без использования внешнего компаратора, что ограничивает область. применения этого интегрирующего устройства.

Наиболее близким к предлагаемому по технической сущности является интегрирующее устройство, содержащее последовательно соединенные преобразователь напряжения в частоту, вход которого является информационным входом интегрирующего устройства, логический переключатель, реверсивный счетчик .и цифроаналоговый преобразователь, выход которого является информационным выходом интегрирующего устройства, выход генератора импульсов соединен с входом эталонного сигнала логического переключателя, первые входы первого и второго компараторов являются входом сравнения с уставками интегрирующего устройства, а вторые входы компараторов соединены с задатчиками верхней и нижней уставок, выходы компараторов подключены к первым входам первого и второго элементов И, вторые входы которых являются входами разрешения верхнего и нижнего ограничения интегрирующего устройства, а выходы соединены соответственно с первым и вторым управляющими входами логического переключателя, третий,четвертый, пятый и шестой управляющие входы которого являются соответственно входами разрешения прямого и- обратного интегрирования и принудительного увеличения и уменьшения выходного сигнала интегрирующего устройства, выходы первого и второго компараторов соединены также с управляющими входами первого и второго реле индикации соответственно 2,

Известное интегрирующее устройство обладает более широкимифункциональными возможностями, чем другие интегрирующие устройства, однако оно также не обеспечивает возможности работы в, бесконтактных следящих системах без использования внешнего компаратора, тогда как такая возможность является весьма желательной для обеспечения наибольших компактности и надежности систем автоматического регулирования и (или) управления, что также ограничивает область применения этого интегрирующего устройства.

Цель изобретений - расширение области применения интегрирующего устройства.

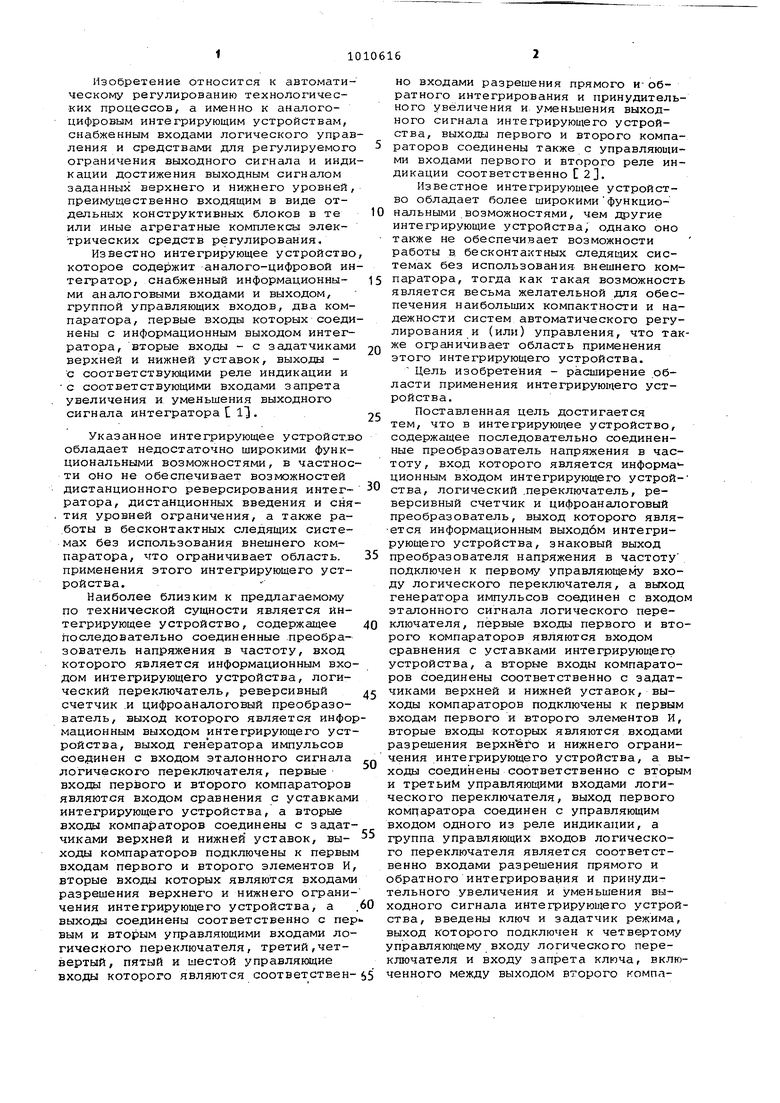

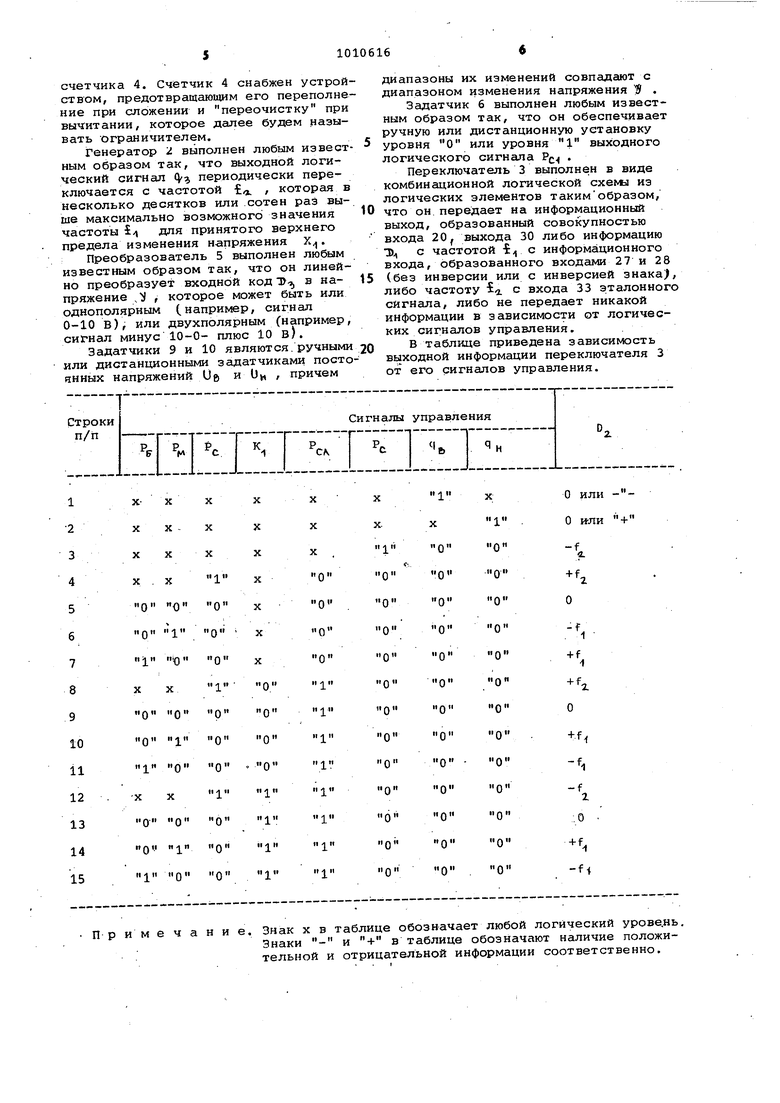

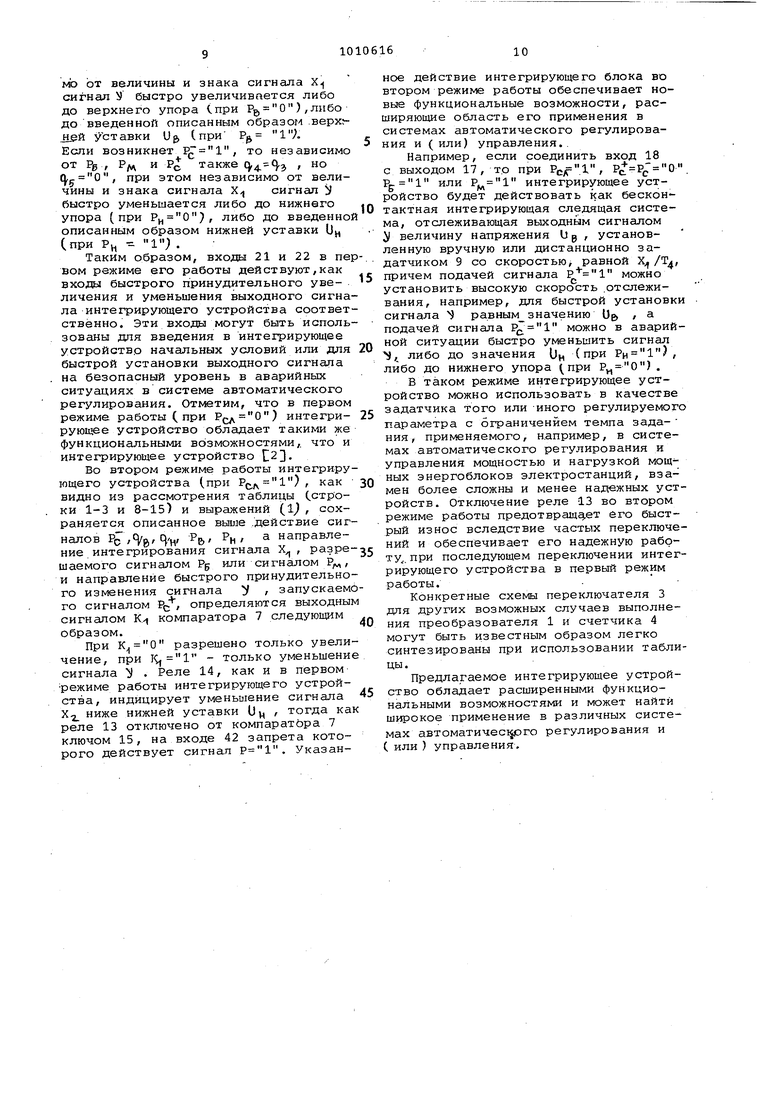

Поставленная цель достигается тем, что в интегрирующее устройство, содержащее последовательно соединенные преобразователь напряжения в частоту, вход которого является информа-ционным входом интегрирующего устройства, логический .переключатель, реверсивный счетчик и цифроаналоговый преобразователь, выход которого является информационным выходбм интегрирующего устройства, знаковый выход преобразователя напряжения в частоту подключен к первому управляющему входу логического переключателя, а выход генератора импульсов соединен с входо эталонного сигнала логического переключателя, первые входы первого и второго компараторов являются входом сравнения с уставками интегрирующего устройства, а вторые входы компараторов соединены соответственно с задатчиками верхней и нижней уставок, выходы компараторов подключены к первым входам первого и второго элементов И, вторые входы которых являются входами разрешения верхн о и нижнего ограничения интегрирующего устройства, а выходы соединены соответственно с вторы и третьим управляющими входами логического переключателя, выход первого комцаратора соединен с управляющим входом одного из реле индикации, а группа управляющих входов логического переключателя является соответственно входами разрешения прямого и обратного интегрирования и принудительного увеличения и Уменьшения выходного сигнала интегрирующего устройства, введены ключ и задатчик режима, выход которого подключен к четвертому управляющему входу логического переключателя и входу запрета ключа, включенного между выходом второго комплратора и управляющим входои другого реле индикации, причем выход второго компаратора соединен с пятым управля ющим входом логического переключател На фиг.1 приведена блок-схема интегрирующего устройства) на фиг.2 электрическая функциональная схема логического переключателя, входящего в интегрирующее устройство. Интегрирующее устройство содержит преобразователь 1 напряжения в частоту, генератор 2 импульсов, логичес кий переключатель 3, реверсивный счетчик 4, цифроаналоговый преобразо ватель 5, задатчик 6 режима, компа- . раторы 7 и 8, залатчики 9 и 10 уставок, элементы И 11 и 12, реле 13 и 1 индикации/ ключ 15, информационный вход 16, информационный выход 17, вход 18 сравнения с уставками, управляющие входы 19-24. Преобразователь 1, переключатель 3, счетчик 4, преобразователь 5 соединены последовательно, причем вход 16 интегрирующего устройства является входом преобразователя 1, выходы 25 и 26 которого соединены с информационными входами 27 и 28 соответственно переключателя 3, выхода 29 и 30 которого соединены с информационными входами 31 и 32 счетчика 4, а выход преобраэователя 5 является информационным выходом 17 интегрирующего устройства Выход генератора 2 соединен с вхо дом 33 эталонного сигнала переключателя 3, управляющие входы 34-37 кото рого соединены с выходами соответственно задатчика 6, компаратора 1, элементов 11 и 12, управляющие входы 38-41 - с входами 19-22 интегрирующе го устройства соответственно. Неинвертирующий вход компаратора 7 и инвертирующий вход компаратора 8 являются входом 18 интегрирующего устрой ства, другие входы компараторов 7 и соединены с задатчиками 9 и 10 соответственно. Выход компаратора 8 соединен с входом управления реле 14 и одним входом элемента 12, другой вхо которого является входом 24 интегрирующего устройства.. Выход компаратор 7 соединен с одним входом элемента 11/ другой вход которого является входом 23 интегрирующего устройства/ и с входом управления реле 13 через ключ 15, вход 42 запрета которого со единен с задатчиком 6 режима. Принимаем следующие условные обоз .начения электрических сигналов: Xi ,Ха и Y - аналоговые сигналы напряжения постоянного тока на входах 16 и 18 и на выходе 17 соответственно i Ug и UK - напряжения на выходах задатчиков 9 и 10 соответственноJ РВ Р( и Р„ - входные логические сигналы на вхолах 19-24 соответственно, Ч и Яг логические сигналы на выходах 25 и26 преобразователя 1 соответственно , Чзн логическийсигнал знака напряжения 5Ц , q - логический Сигнал на выходе генератора 2/ f - выходные частоты преобразователя 1 и генератора,2 соответственно/Яд и 5 логические сигналы на выходах 29 и 30 переключателя 3 соответ:;твенно/ . Чв Ян логические сигналы на выходах элементов 11 и 12 соответственно;К и К 2 - логические сигналы на выходах -компараторов 7 и 8 соответсг венно, РСМ - логический сигнал на выходе задатчика 6; D и D - входная информация преобразоватешя 1 и входная информация счетчика 4 соответственно Тф - постоянная времени интегриро вания. Преобразователь 1 выполнен любым известным образом так/ что он преобразует входное напряжение которой может иметь любой знак/ в частоту f переключений логических уровней, либр выходного логического сигнала q , тогда как выходной логический сигнал q. отображает своим уровнем знак напряжения либо того или другого из сигналов и зависимости от знака напряжения причем частота f 4 прямо пропорциональна абсолютной величине напряжения Х, а коэффициент преобразования может быть установлен вручную или дистанционно в определенгных пределах. Независимо от конкретного выполнения преобразойателя 1 его выходную информацию 3.j о величине и знаке напряжения Х( / представляемую совокупностью сигналов -С и 4fi, будем считать положите л при Х GI и отрицательной при Х О а абсолютную величину информации будем считать равной f , т.е. при О 1 1л при Х О Э - f. Счетчик 4 может быть применен как с раздельными счетными входами для сложения и Ш1читания, так и с общим счетным входом для сложения и вычитания и с входом управления направлением счета. Независимо от конкретного выполнения счетчика его входную информацию 3)г , представляемую совокупностью сигналов ч будем считать положительной и отрицательной в случаях/ когда она обеспечивает ее сложение и вычитание в счетчике с имеющимся в нем содержимым соответственно, абсолютную величину информации Э-з. будем считать равной частоте f переключения сигнала на счетном входе счетчика 4. Счетчик 4 снабжен устрой ством, предотвращающим его переполне ние при сложении и переочистку при вычитании, которое далее будем называть ограничителем. Генератор 2. выполнен любым извест ным образом так, что выходной логический сигнал (V периодически переключается с частотой ,х / которая в несколько десятков или .сотен раз выше максимально возможногб значения частоты для принятого верхнего предела изменения напряжения Х. Преобразователь 5 выполнен любым известным образом так, что он линейно преобразует входной код ,, в напряжение ,Л , которое может быть или однополярным (например, сигнал 0-10 в), или двухполярным (например, сигнал минус 10-0- плюс 10 в). Задатчики 9 и 10 являются.ручными или дистанционными задатчиками посто янных напряжений UB и U , причем диапазоны их изменений совпадают с диапазоном изменения напряжения 1У . Задатчик 6 выполнен любым известным образом так, что он обеспечивает ручную или дистанционную установку уровня О или уровня 1 выходного логического сигнала . Переключатель 3 выполнен в виде комбинационной логической схемы из логических элементов такимобразом, что он. передает на информационный выход, образованный совокупностью входа 20, выхода 30 либо информацию Т) с частотой , с информационного входа, образованного входами 27 и 28 (без инверсии или с инверсией знака, либо частоту i с входа 33 эталонного сигнала, либо не передает никакой информации в зависимости от логических сигналов управления. В таблице приведена зависимость выходной информации переключателя 3 от его сигналов управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система управления мощностью турбины | 1984 |

|

SU1227823A1 |

| Устройство контроля пламени | 1985 |

|

SU1285273A1 |

| Автоматическое устройство для формирования и испытания химического источника тока | 1983 |

|

SU1112446A1 |

| Интегрирующее устройство | 1983 |

|

SU1267439A1 |

| Устройство для управления многофазным тиристорным прерывателем постоянного тока | 1975 |

|

SU604111A1 |

| Фильтр-реле тока | 1991 |

|

SU1814131A1 |

| ЭЛЕКТРОННЫЙ ТЕРМОРЕГУЛЯТОР ДЛЯ ЭЛЕКТРОУТЮГА | 1992 |

|

RU2078371C1 |

| РЕЛЕ ЧАСТОТЫ ИЛИ ФАЗЫ | 1993 |

|

RU2056693C1 |

| Устройство для измерения экстремальных значений измеряемых размеров детали | 1983 |

|

SU1249311A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО, содержащее последовательно соединенвые преобразователь напряжения в частоту, вход которого является информа - ционным входом интепэируклдего устройства, логический переключатель, реверсивный счет-чик и цифроаналоговый преобразователь, выход которого является информационным выходом интегрирующего устройства, знаковый выход преобразователя напряжения в частоту подключен к первому управляющему входу логического переключателя, а выход генератора импульсов соединен с входом эталонного сигнгша логического переключателя, первые входы первого и второго компщ дторов являются входом сравнения с уставками интегрирующего устройства, а вторые входы компарато ров соединены соответственно с задатчиками верхней и нижней уставок, выходы компараторов подключены к первым входам первого и второго элементов И, вторые входы которых являются входами . разрешения верхнего и нижнего ограничения интегрирующего устройства, а выходы соединены cooTBetcTBeHHo с вторым и третьим управляющими входами логического переключателя, выход первого компаратора соединен с управ ляющим входом одного из релеиндика- g ции, а группа управляющих входов ло- 5 гического переключателя является соответственно входами разрешения пря мого и обратного интегрирования и принудительного увеличения и уменьшения выходного сигнала интетрир1пюще7 ч го устройства, о т л и ч а ю щ веся 5 тём,что,с целью расширения областиприменения, в него введены ключ и эадатчик режима, выход которого подключен к четвертому управляющему входу логического переключателя и входу запрета ключа,. включенного меж-ш ду выходом второго компаратора и уп- ( равляющим входом другого реле индика М ции, причем выход BTopcfro компаратора соединен с пятым управляющим входом логического переключателя. |ДЧ

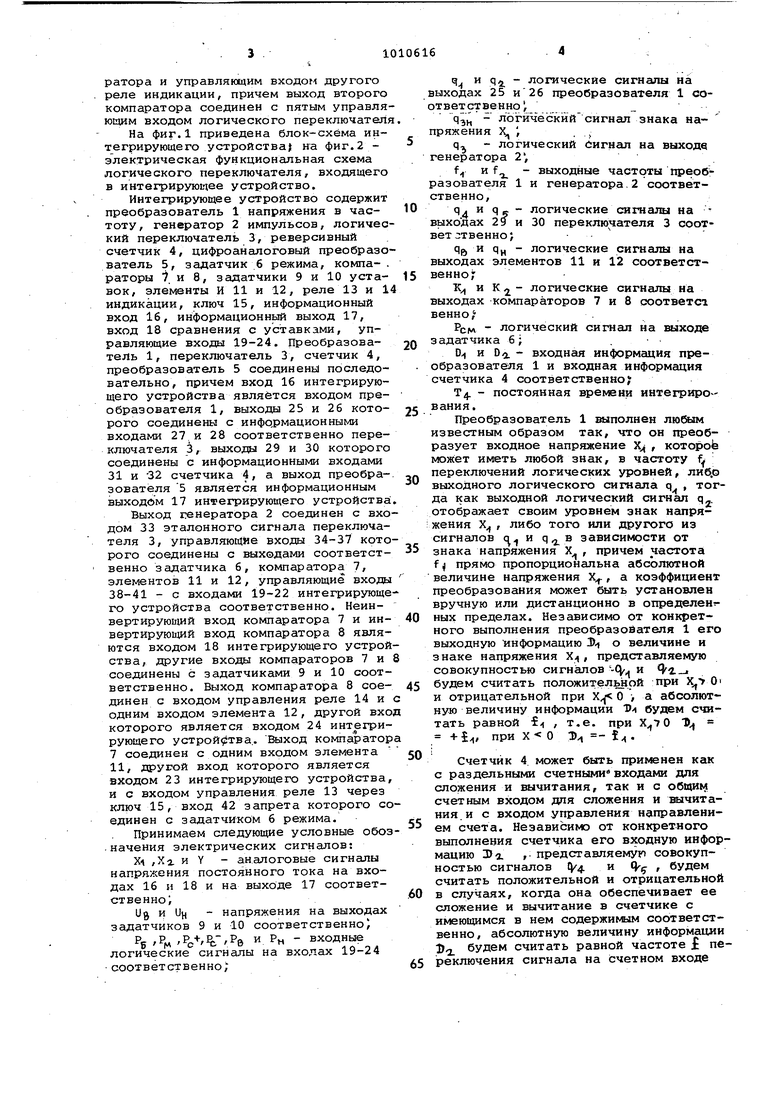

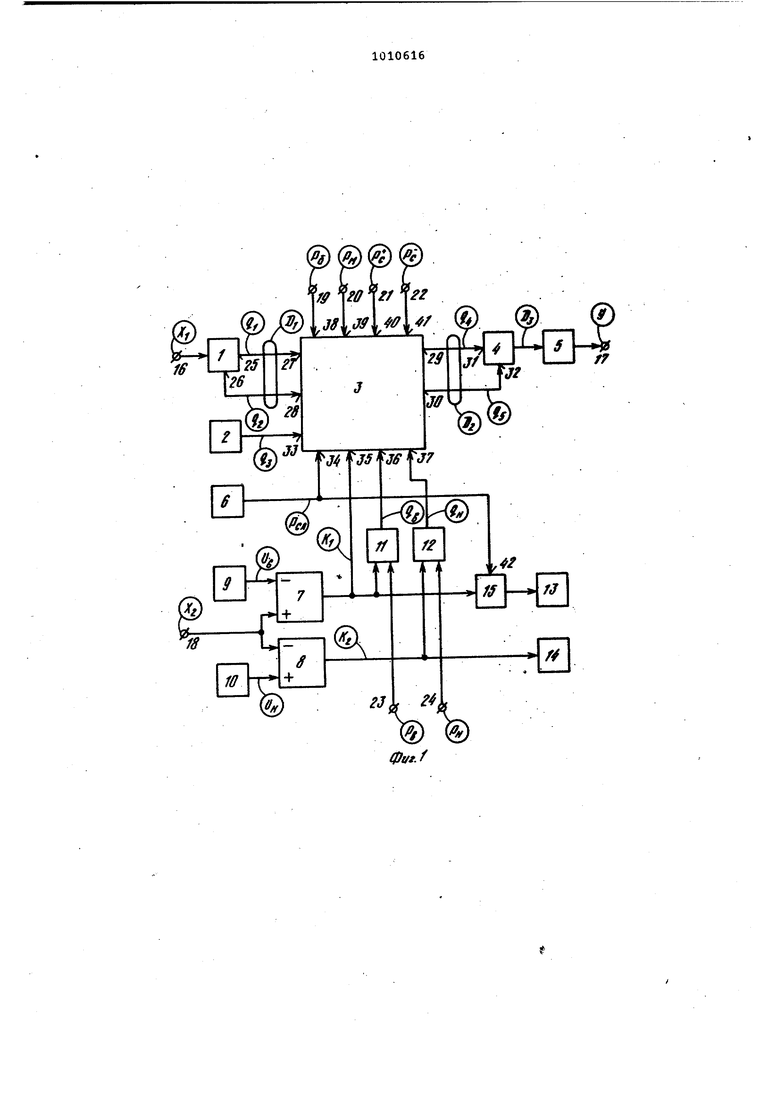

Примечание. Знак х в таблице обозначает любой логический урове.нь. Знаки - и + в таблице обозначают наличие положительной и отрицательной информации соответственно. В случае, когда преобразователь 1 выполнен с выходом 25 частоты(q,-f) и с выходом 26 логического сигнала знака (. 9,) счетчик 4 выполнен с общим счетным входом 31 и с входом 3.2 управления направлением счета, мо жет быть применен переключатель 3 ((Ьиг.2), содержащий элементы И-НЕ 43 57 и инверторы 58-65. Переключатель) (фиг.2) реализует следующие Булевы функции: PC )K V5Vft §5M V5ЧPc Ь«Pв Ън « Pe)Pc.ЗP; J Нетрудно убедиться, что выражения (1) ссэответствуют таблице. Интегрирующее устройство, в котором применены преобразователь 1 с вы ходом 25 частоты и с выходом 26 ло. гического сигнала знака, принимающего значение i при Х О, счетчик 4 с общим счетным входом 31 и с входом 32 управления направление счета, причем сигнал ( 1 устанавливает счетчик в режим сложения, и переключатель 3 (фиг.2) работает следующим образом. Компараторы 7 и 8 сравнивают вход ной си гнал X i с верхней и нижней уставками UB и Оц ,. . При. , , при X,, , при этом реле 14 индицирует уменьшение-Хг ниже значения Он .При К 0, при К, 1, пр этом реле 13 индицирует увеличение Xi выше значения U -/если ключ 15 закрыт сигналом . Таким образом, при компараторы 7 и 8, задатчики 9 и 10, реле 13, ключ 15 действуют, как канал сигнализации достижения Х заданных верхней и нижней уставок Ug и OH соответственно. При соединении входа 18с выходом 17 этот канал будет сигнализировать с помощью реле 13 и 14 о достижении ука ванных уставок выходным сигналом N интегрирующего устройства. При Рв 1 . , при , (VB при при помощью входных сигналов Pg, и Рц интегрирующего устройства может быть введена и снята логическая связь между компараторами 7 и 8 и переключателем 3. 3 адат чи ком 6 уст.анавливают( В1 учную или дистанционно) режим работы интегрирующего устройства: при первый режим, при Pj,l - второй режим. В первом работы интегрирующего устройства (при как видно из таблищл строки 1-7) и выражений .), действие переключателя 3 не зависит от сигнала К,, на входе 35. Если то V4 0 т.е. импульсы на счетный вход счетчи ка 4 не поступают, следовательно,е1Х7 выходной код t и соответствукицее значение выходного сигнала X .интегрирующего устройства не изменяются режим хранения). Если 0 и Vg, %, то при P5 i и на счетный вход 31 счетчика 4поступгшт импульсы с частотой i , прямо пропорционсшьной абсолютной величине входного напряжения X,( вход 32 управления направлением счета счеТ чика 4 поступает сигнал, равный сигналу знака напряжения }Ц ) т.а. выходная информация 7X2. переключателя 3 равна его входной информации BI . При этом в результате счета импульсов частоты i счётчиком интегрирую1цее устройство производит интегрирование по времени сигнала Х с постоянн и времени Тд,устаиовденной задатчиком коэффициента передачи пре образрвателя 1, до тех пор, пока счет импульсов счетчиком не будет прв крещен встроенным в него ограмичите г лем, а при Рр 0 и Р также %4. €, но Чг5 (V,,, (.т.е. Т))- при этом интегрирующее устройство производит обратное интетрирование по времани сигнала Х (т.е. с инверсией знака приращения интеграла отиоситель г но знака сигнала Х) также до тех пор, пока счет импульсов счетчикЪм не будет прекращен встроенным а .него ограничителем. Таким образом, входы 19 и 2Q интагрируюфся в первом режиме его работы действуют как входы разрешения пряк4ого и обратного интегрирования соот- ветственно сигнала Х,|. Если в npotxeciсе увеличения сигнгша У возникнет сур 0 (что возможно лишь, при Pg 1) , то увеличение прекратится на достигнутом уровне, что эквивалентно ограничению сигнала сверху ria про.межуточном ( между упораМи уровне, кото{Ж2й в случае, когда вход 18 соединен с выходом 17, установлен эадатчиком 9. Если затем будет подан ; сигнал , то указанное ограничение сигнала V сверху будет снято, и увеличение сигнала j может продолжаться до верхнего упора. Таким образом, вход 23 сигнала Рг является входом разрешения верхнего огранцчег ния выходного сигнала интегрирующего устройства на первом регулируемом {уровне. Аналогично вход 24 сигнала Рц является входом разрешения нижнего огрсшичения выходного сигнала интегрирующего устройства на втором регулнруекюм уровне. Если при возникнет , то независимо от Рр и Рщ на счетный вход 31 счетчика поступают импульсы высокой частоты f 1Чч-, з фв 1, при этом независиМО от величины и знака сигнала Х сигнал 5) быстро увеличивается либо до верхнего упора (при ),либо до введенной описанным образом уставки Ug, (при Р

Если возникнет Р 1, то независимо от Рр , Рдц и PC также (4--% ° q.p 0, при этом независимо от величины и знака сигнала Х сигнал быстро уменьшается либо до нижнего упора (при ), либо до введенно описанным образом нижней уставки U (при Pj .

Таким образом, входы 21 и 22 в пе вом режиме его работы действуют,как входы быстрого принудительного увеличения и уменьшения выходного сигнала интегрирующего устройства соответственно. Эти входы могут быть использованы дпя введения в интегрирующее устройство начальных условий или для быстрой установки выходного сигнала на безопасный уровень в аварийных ситуациях в системе автоматического регулирования. Отметим, что в первом режиме работы (при Р() интегрирую1дее устройство обладает такими же функциональными возможностями,, что и интегрирующее устройство 23.

Во втором режиме работы интегрирующего устройства (при P(), как видно из рассмотрения таблицы (.строки 1-3 и 8-15) и выражений (1, сохраняется описанное выше .действие сигналов РС,%% н S направление интегрирования сигнала Х , paspeшаемого сигналом Pg или сигналом Р, и направление быстрого принудительного изменения сигнала , запускаемого сигналом f, определяются выходным сигналом К.-1 компаратора 7 следующим образом.

При разрешено только увеличение, при - только уменьшение сигнала . Реле 14, как и в первом режиме работы интегрирующего устройства, индицирует уменьшение сигнала Х ниже нижней уставки Оц , тогда как реле 13 отключено от компаратора 7 ключом 15, на входе 42 запрета которого действует сигнал . Указанное действие интегрирующего блока во втором режиме работы обеспечивает новые функциональные возможности, расширяющие область его применения в системах автоматического регулирования и (или) управления..

Например, если соединить вход 18 с выходом 17, т.о при РСЛ., Р,Р(Г 0

Pg.l или интегрирующее устройство будет действовать как бесконтактная интегрирующая следящая система, отслеживающая выходным сигналом У величину напряжения Ug , установленную вручную или дистанционно задатчиком 9 со скоростью, равной , причем подачей сигнала можно установить высокую скорость .отслеживания, например, для быстрой установк сигнала 9 равным значению (Jg, , а подачей сигнала можно в аварийной ситуации быстро уменьшить сигнал , либо до значения Оц (при Рн 1) , либо до нижнего упора при ).

В таком режиме интегрирующее устройство можно использовать в качестве задатчика того или иного регулируемог параметра с ограничением темпа задания, применяемого, н.апример, в системах автоматического регулирования и управления мощностью и нагрузкой мощ ных энергоблоков электростанций, взамен более сложны и менее надежных устройств. Отключение реле 13 во втором режиме работы предотвращает его быстрый износ вследствие частых переключений и обеспечивает его надежную работу, при последующем переключении интегрирующего устройства в первый режим работы.

Конкретные схемы переключателя 3 для других возможных случаев выполнения преобразователя 1 и счетчика 4 могут быть известным образом легко синтезированы при использовании таблицы.

Предлагаемое интегрирующее устройство обладает расширенными функциональными возможностями и может найти широкое применение в различных системах автоматичес го регулирования и С или ) управления.

| Д | |||

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

| Рекламный проспект фирмы Hartmann und Braun, ФРГ | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Щидлович Л.Х | |||

| и др | |||

| Блоки динами ческих преобразований | |||

| - Механизация и автоматизация производства, 1979, № 5 (прототип). | |||

Авторы

Даты

1983-04-07—Публикация

1981-04-01—Подача