(54) УСТРОЙСТВО Д ТИРИСТО Изобретение относится к системам управления преобразователями постоянного напряжения в постоянное, работающими в режиме регулируемой частоты коммутации и времени включенного состояния. Оно может найти применение в транспортных установках. Известно устройство для управления многофазным тиристорным прерывателем постоянного тока с жестко заданным временем включенного состояния ,или наоборот при наличии регулирования времени включенного состояния с постоянной частотой коммутации 1. Однако для него характерно ограничение диапазона регулирования в областях очень малых и очень высоких коэффициентов нагрузки. Целью изобретения является расширение диапазона регулирования напряжения на нагрузке. Это достигается тем, что в устройстве, содержащем главный преобразователь «напряжение-частота , по крайней мере два дополнительных преобразователя напряжение-частота , источник симметричного отсчитывающего напряжения и мультистабильную счетную схему, к цепи управления подключены входы главного и дополнительных преобразователей,напряжение-частота, выход положительного полюса источника симметричного отсчитывающеПОСТОУПРАВЛЕНИЯ МНОГОФАЗНЫМ Л ПРЕРЫВАТЕЛЕМ ОГО ТОКА го напряжения подключен ко входам положительного отсчитывающего напряжения главного и дополнительных преобразователей напряжение-частота, выход отрицательного полюса источника симметричного отсчитывающего напряжения подключен к зажимам отрицательного входа напряжения глав ного и дополнительных преобразователей, напряжение-частота, и к зажимам дополнительного преобразователя напряжение-частота, выход главного преобразователя напряжение-частота связан с входом мультистабильной счетной схемы (с многими устойчивыми состояниями), выходы которой связаны с входами синхронизации дополнительного преобразователя напряжение-частота и вместе с тем заведены на предназначенные для коммутации вспомогательных тиристоров в каждой из фаз прерывателя постоянного тока вторые входные клеммы, причем выходы дополнительного преобразователя напряжение-частота заведены на предназначенные для коммутации главных тиристоров прерывателя постоянного тока первые выходные клеммы. Главный преобразователь напряжение-частота состоит из интегрирующей цепи ко.мнаратора и переключателя, причем выход интегрирующей цепи связан с входом компаратора. Вь,1ход компаратора с одной стороны связан с вхолом мультйстабильной схемы с многими устойчивыми сосгояниями, а. с другой стороны - с входом переключателя, выход которого соединен с входами обратной связи интегрирующей цепи и компаратора.

Дополнительный преобразователь напряжение-частота состоит из электронных ключей, интегрирующей цепи, компаратора, электронного переключателя и логической схемы. Первый электронный ключ, вход которого образует вход дополнительного преобразо.аателя напряжениечастота, своим выходом присоединен к первому входу интегрирующей цепи, выход которой соединен с первым входом компаратора, выход которого далее идет на включение главных тиристоров (зажигание тиристоров) задатчика постоянного тока через предназначенные для этого выходные клеммы, к входу электронного переключателя и ко второму входу логической схемы. Выход электронного переключателя связан с вторым входом компаратора и с входом второго электронного ключа, выход которого соединен со вторым входом интегрирующей цепи. Первый выход логической схемы связан с управляющим входом третьего электронного ключа, выход которого соединен с третьим входом интегрирующей цепи, причем второй выход логической схемы соединен с третьим входо.м компаратора, а третий выхсд логической схемы соединен с управляющими входами первого и второго электронного ключей. Первый вход логической схемы соединен с первым выхоДрм мультистабйльной схемы.

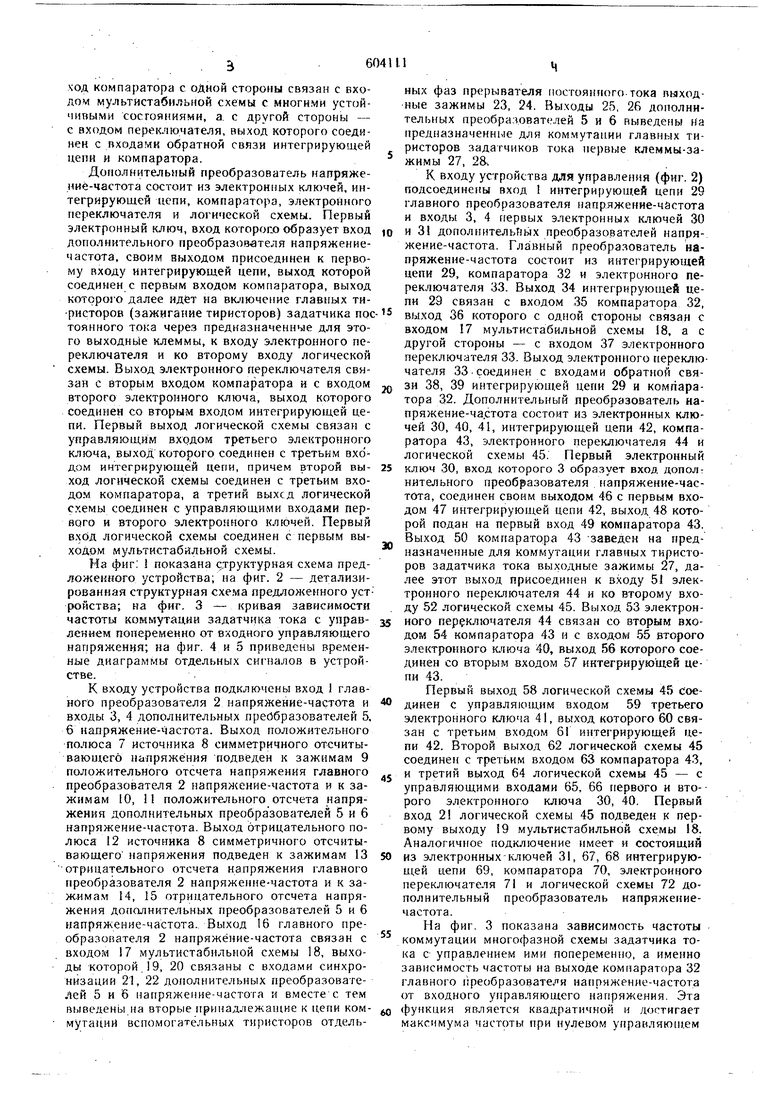

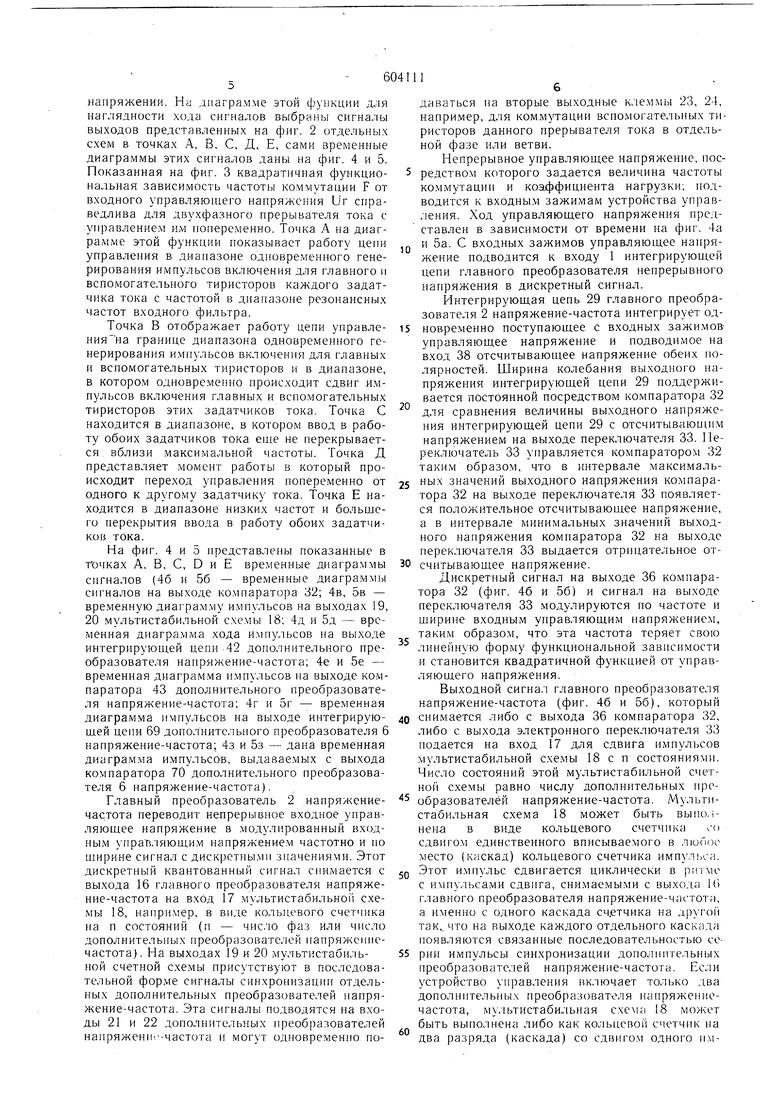

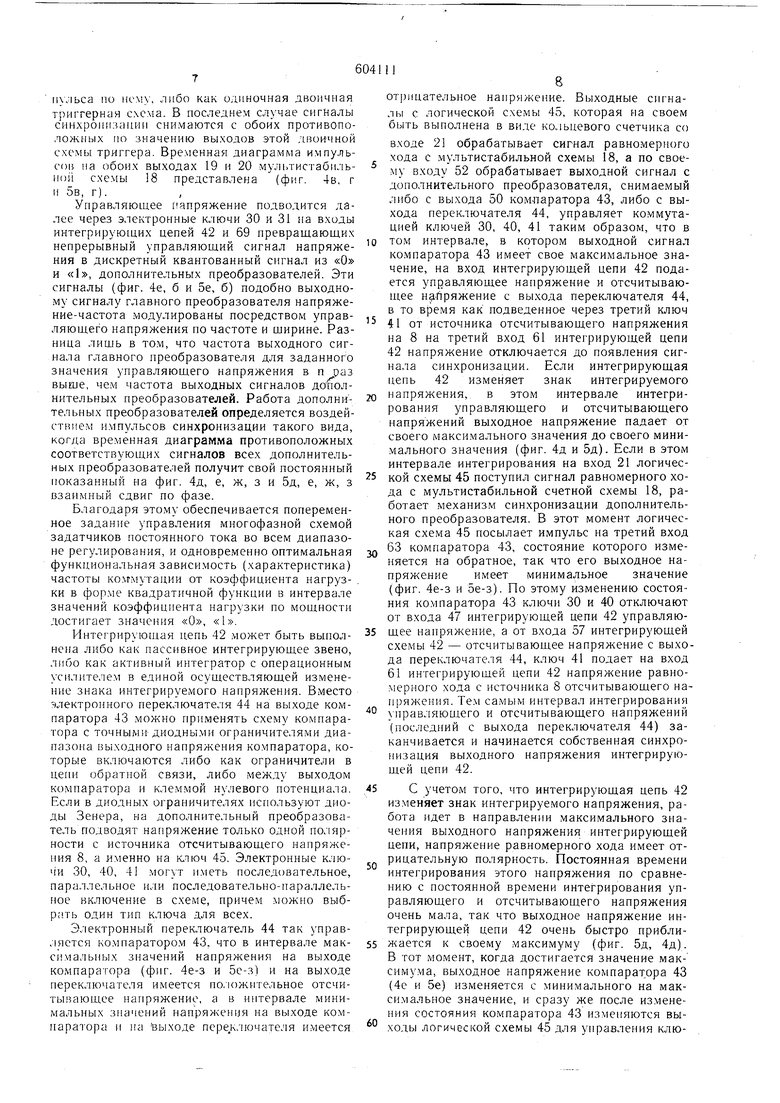

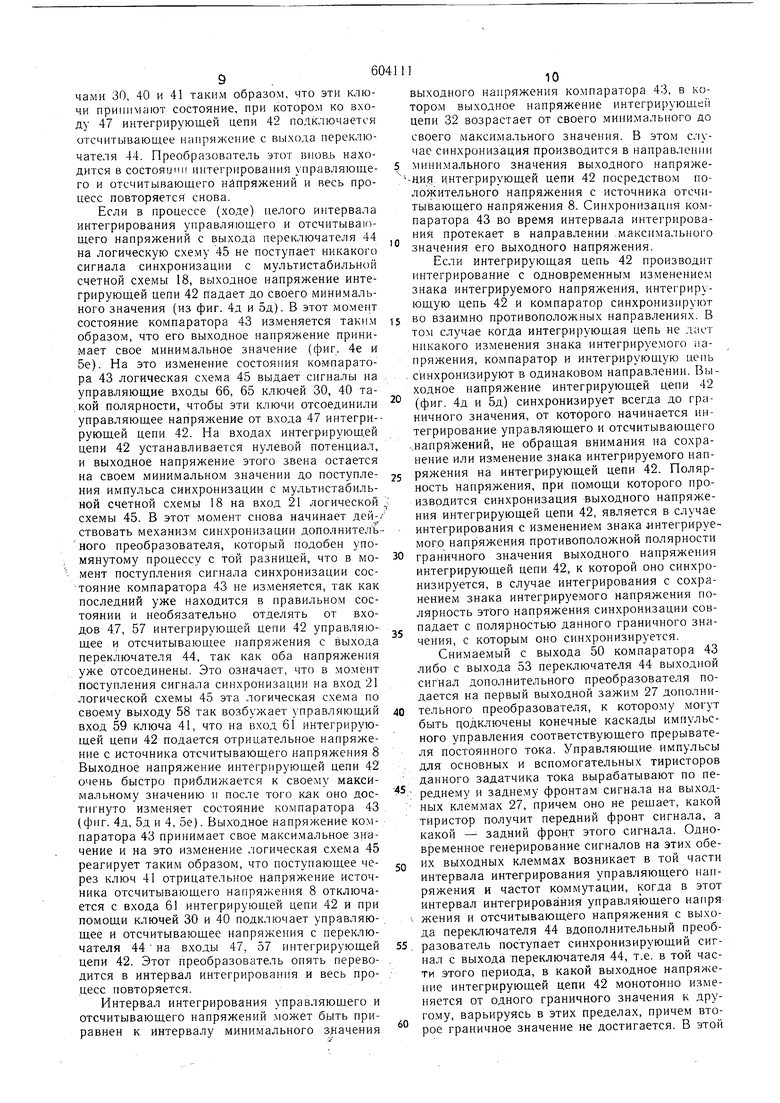

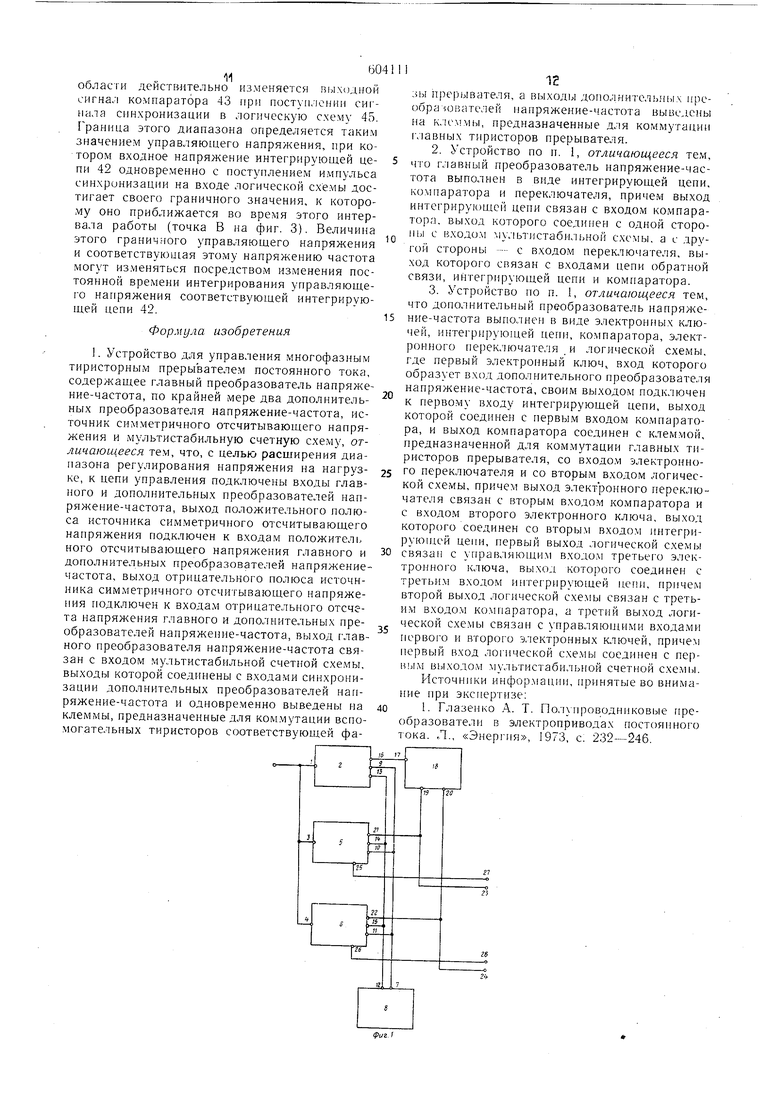

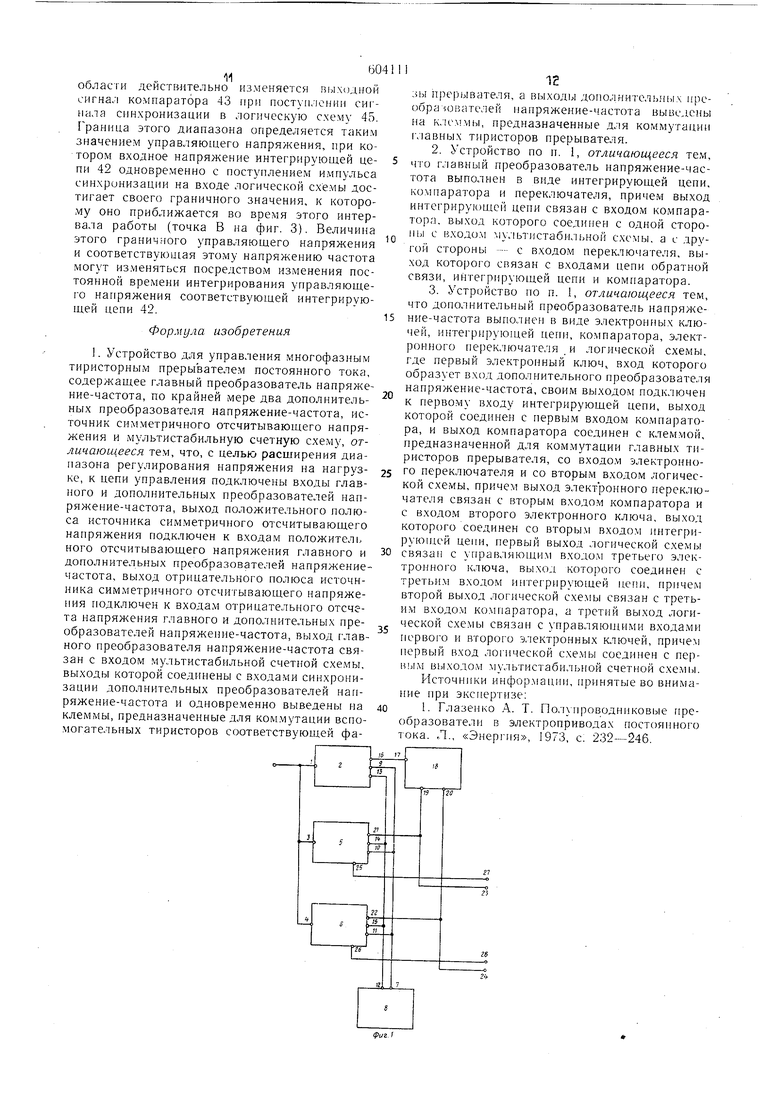

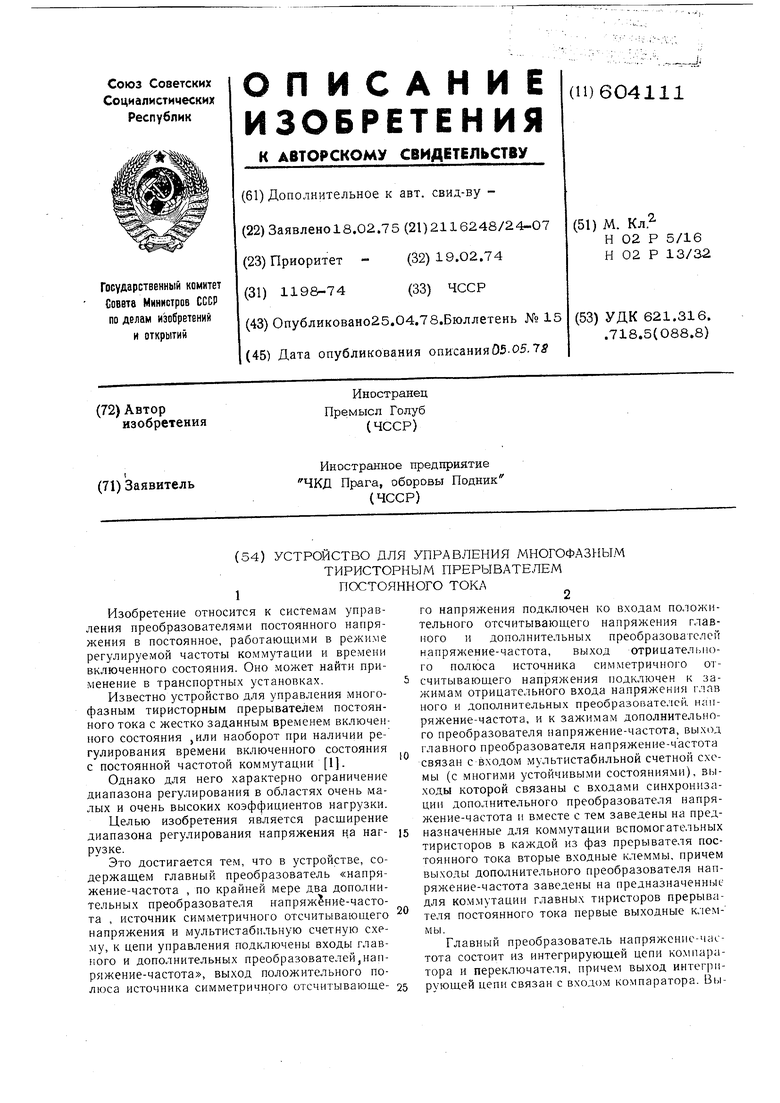

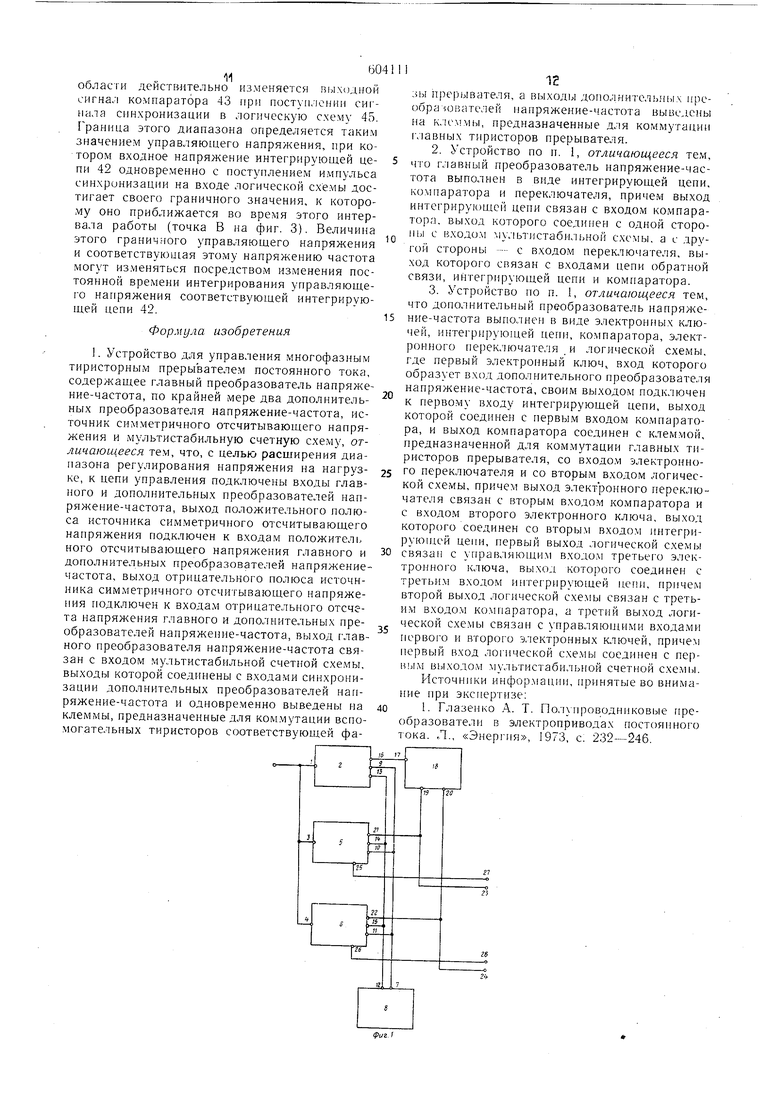

На фиг; 1 показана труктурная схема предложенного устройства; на фиг. 2 - детализированная структурная схема предложенного устpofscTBB; на фиг. 3 - кривая зависимости частоты коммутации задатчика тока с управлением попеременно от входного управляющего напряжения; на фиг. 4 и 5 приведены временные диаграммы отдельных сиг-налов в устройстве.

К входу устройства подключены вход 1 главного преобразователя 2 напряжение-частота и входы 3, 4 дополнительных преббразователей 5, б напряжение-частота. Выход положительного полюса 7 источника 8 симметричного отсчитывающего напряжения подведен к зажимам 9 положительного отсчета напряжения главного преобразователя 2 напряжение-частота и к зажимам 10, 1 положительного отсчета напряжения дополнительных преобразователей 5 и 6 напряжение-частота. Выход отрицательного полюса 12 источника 8 симметричного отсчитывающего напряжения подведен к зажимам 13 отрицательного отсчета напряжения главного преобразователя 2 напряжение-частота и к заж.имам 14, 15 отрицательного отсчета напряжения дополнительных преобразователей 5 и 6 напряжение-частота. Выход 16 главного преобразователя 2 напряжение-частота связан с входом 7 мультистабильной схемы 18, выходы которой 19, 20 связаны с входами синхронизации 21, 22 дополнительных преобразователей 5 и 6 напряжение-частота и вместе с тем выведены на вторые принадлежащие к цепи коммутации вспомогательных тиристоров отдельных фаз прерывателя юстоянгюго тока выходные зажимы 23, 24. Выходы 25, 26 дополнительных преобразователей 5 и 6 выведены на предназначенные для коммутации главных тиристоров задатчиков тока первые клеммы-зажимы 27, 2а.

К входу устройства для управления (фиг. 2) подсоединены вход 1 интегрирующей цепи 29 главного преобразователя напряжение-частота и входы 3, 4 первых электронных ключей 30 и 3 дополнительных преобразователей напряжение-частота. Главный преобразователь напряжение-частота состоит из интегрирующей цепи 29, компаратора 32 и электронного переключателя 33. Выход 34 интегрирующей цепи 29 связан с входом 35 компаратора 32, выход 36 которого с одной стороны связан с входом 17 мультистабильной схемы 18, а с другой стороны - с входом 37 электронного переключателя 33. Выход электронного переключателя 33-соединен с входами обратной связи 38, 39 интегрирующей цепи 29 и компаратора 32. Дополнительный преобразователь напряжение-ча.стота состоит из электронных ключей 30, 40, 41, интегрирующей цепи 42, компаратора 43, электронного переключателя 44 и логической схемы 45. Первый электронный ключ .30, вход которого 3 образует вход дополт нительного преобразователя напряжение-частота, соединен своим выходом 46 с первым входом 47 интегрирующ,ей цепи 42, выход 48 которой подан на первый вход 49 компаратора 43. Выход 50 компаратора 43 заведен на предназначенные для коммутации главных тиристоров задатчика тока выходные зажимы 27, далее этот выход присоединен к входу 51 электронного переключателя 44 и ко второму входу 52 логической схемы 45. Выход 53 электронного переключателя 44 связан со вторым входом 54 компаратора 43 и с входом 55 второго электронного ключа 40, выход 56 которого соединен со вторым входом 57 иктегрирующен цепи 43.

Первый выход 58 логической схемы 45 соединен с управляющим входом 59 третьего электронного ключа 41, выход которого 60 связан с третьим входом 61 интегрирующей цепи 42. Второй выход 62 логической схемы 45 соединен с третьим входом 63 компаратора 43, и третий выход 64 логической схемы 45 - с управляющими входами 65, 66 первого и второго электронного ключа 30, 40. Первый вход 2 логической схемы 45 подведен к первому выходу 19 мультистабильной схемы 18. Аналогичное подключение имеет и состоящий из электронных ключей 31, 67, 68 интегрирующей цепи 69, компаратора 70, электронного переключателя 71 и логической схемы 72 дополнительный преобразователь напряжениечастота.

На фиг. 3 показана зависимость частоты коммутации многофазной схемы задатчика тока с управлением ими попеременно, а именно зависимость частоты на выходе компаратора 32 главного преобразователя напряжение-частота от входного управляющего напряжения. Эта (fjyfiKHHH является квадратичной и достигает максимума частоты при нулевом управляющем напряжении. На диаграмме этой функции для наглядности хода сигналов выбраны сигналы выходов представленных на фиг. 2 отдельных схем в точках А, В, С, Д, Е, сами временные диаграммы этих сигналов даны на фиг. 4 и 5. Показанная на фиг. 3 квадратичная функциоиальная зависидмость частоты коммутации F от входного управляющего напряжения Ur справедлива для двухфазного прерывателя тока с управлением им попеременно. Точка А на диаграмме этой функции показывает работу цепи управления в диапазоне одновре.менпого генерирования импульсов включения для главного и вспомогательного тиристоров каждого задатчика тока с частотой в диапазоне резонансных частот входного фильтра. Точка В отображает работу цепи уиравленияна границе диапазона одновременного генерирования импульсов включения для главных и вспомогательных тиристоров и в диапазоне, в котором одновременно происходит сдвиг импульсов включения главных и вспомогательных тиристоров этих задатчиков тока. Точка С находится в диапазоне, в котором ввод в работу обоих задатчиков тока еще не перекрывается вблизи максимальной частоты. Точка Д представляет момент работы в который происходит переход управления попеременно от одного к другому задатчику тока. Точка Е находится в дианазоне низких частот и большего перекрытия ввода в работу обоих задатчиков тока. На фиг. 4 и 5 представлены показанные в Точках А, В, С, D и Е временные диаграммы сигналов (46 и 56 - временные диаграммы сигналов на выходе компаратора 32; 4в, 5в - временную диаграмму импульсов па вы.ходах 19, 20 мультистабильной схемы 18; 4д и 5д - временная диаграмма хода импульсов на выходе интегрирующей цепи 42 дополнительного нреобразователя напряжение-частота; 4е и 5е - временная диаграмма импульсов на выходе ко.мнаратора 43 дополнительного преобразователя напряжение-частота; 4г и 5г - временная диаграмма импульсов на выходе интегрирующей цепи 69 дополнительного преобразователя 6 напряжение-частота; 4з и 5з - дана временная диаграмма импульсов, выдаваемых с выхода компаратора 70 дополнительного преобразователя 6 напряжение-частота). Главный преобразователь 2 напряжениечастота переводит непрерывпое входное управляющее напряжение в модулированный входным упрат ляющим напряжением частотно и но щирине сигнал с дискретными значениями. Этот дискретный квантованный сигнал снимается с выхода 16 главного преобразователя напряжение-частота на вход 17 мультистабильноп схемы 18, например, в виде кольцевого счетчика на п состояний (а - чис.ю фаз или число дополнительных преобразователей напряжениечастота). На выходах 19 и 20 мультистабильной счетной схе.мы присутствуют в последовательной форме сигналы синхропизацин отдельных дополнительных преобразователей напряжение-частота. Эта сигналы подводятся на входы 21 и 22 дополнительных преобразователей напряжение-частота и могут одновременно подаваться на вторые выходные клеммы 23, 24, например, для коммутации вспомогательных тиристоров данного прерывателя тока в отдельной фазе или ветви. Непрерывное управляющее напряжение, посредством которого задается величина частоты ко.ммутацип и коэффициента нагрузки; подводится к входны.м зажимам устройства управления. Ход управляющего напряжения представлен в зависимости от времени на фиг. 4а и 5а. С входных зажимов управляющее напряжение подводится к входу 1 интегрирующей цепи главного преобразователя непрерывного панряжения в дискретный сигнал. Интегрирующая цепь 29 главного преобразователя 2 напряжение-частота интегрирует одновременно поступающее с входных зажимов управляющее напряжение и подводимое на вход 38 отсчитывающее напряжение обеих полярностей. Ширина колебания выходного напряжения интегрирующей цепи 29 поддерживается постоянной посредством компаратора 32 для сравнения величины выходного напряжения интегрирующей цепи 29 с отсчитывающим напряжением на выходе переключателя 33. Нереключатель 33 управляется компаратором 32 таким образом, что в интервале максимальных значений выходного напряжения компаратора 32 на выходе переключателя 33 появляется положительное отсчитывающее напряжение, а в интервале минимальных значений выходного напряжения компаратора 32 на выходе переключателя 33 выдается отрицательное отсчитывающее напряжение. Дискретный сигнал на выходе 36 компаратора 32 (фиг. 46 и 56) и сигнал на выходе переключателя 33 модулируются по частоте и щирине входным управляющим напряжением, таким образом, что эта частота теряет свою линейную форму функциональной зависимости и становится квадратичной функцией от управляюплего напряжения. Выходной сигнал главного преобразователя напряжение-частота (фиг. 46 и 56), который снимается либо с выхода 36 компаратора 32, либо с выхода электронного переключателя 33 подается на вход 17 для сдвига импульсов мультистабильной схемы 18 с п состояниями. Число состояний этой мультистабильной счетной схемы равно числу дополнительных преобразователей напряжение-частота. Мультистабильная схема 18 может быть выно. iненл в виде кольцевого счетчика со сдвиго.м единственного вписываемого в люГюс место (каскад) кольцевого счетчика импул1 оа. Этот импульс сдвигается циклически в ритме с импульсами сдвига, снимае.мыми с выхода К) главного преобразователя напряжение-частота, а именно с одного каскада сч.етчика на другой так,, что на выходе каждого отдельного каскада появляются связанные последовательностью серии импульсы синхронизации дополнительных преобразователей напряжение-частота. Если устройство управления включает только два дополнительных преобразователя напряжениечастота, мультистабильная схема 18 может быть выполнена либо как кольцевой счетчик на два разряда (каскада) со сдвиго.м одного импульса no ному, либо как одиночная двоичная триггерная схема. В последнем случае сигналы синхронизации снимаются с обоих противопо,пож11Ь)1х по значению выходов этой двоичной схемы триггера. Временная диаграмма импульсов иа обоих выходах 19 и 20 мультистаби-льи()1 схемы 18 представлена (фиг. 4в, г и 5в, г).,

Управляюи ее напряжение подводится далее через электронные ключи 30 и 31 на входы интегрирую цих цепей 42 и 69 превращающих непрерывный управляюилий сигнал напряжения в дискретный квантованный сигнал из «О и «1, дополнительных преобразователей. Эти сигналы (фиг. 4е, б и 5е, б) подобно выходно.му сигналу главного преобразователя напряжение-частота модулированы посредством управляющего напряжения по частоте и ширине. Разница лишь в то.м, что частота выходного сигнала главного преобразователя для заданного значения управляющего напряжения в п раз выще, чем частота выходных сигналов догГолнительных преобразователей. Работа дополнительных преобразователей определяется воздействием импульсов синхронизации такого вида, когда временная диаграмма противоположных соответствующих сигналов всех дополнительных преобразователей получит свой постоянный показанный на фиг. 4д, е, ж, з и 5д, е, ж, з взаимный сдвиг по фазе.

Благодаря это.му обеспечивается попеременное задание управления многофазной схемой задатчиков постоянного тока во всем диапазоне регулирования, и одновременно оптимальная функциональная зависимость (характеристика) частоты ко.гмутации от коэффициента нагруз- . ки в форме квадратичной функции в интервале значений коэффициента нагрузки по мощности достигает значения «О, «1.

Интегрирующая цепь 42 .может быть выполнена либо как пассивное интегрирующее звено, либо как активный интегратор с операционным усилителем в единой осуществляющей из.менение знака интегрируемого напряжения. В.место электронного переключателя 44 на выходе компаратора 43 .можно применять схему компаратора с точными диодны.ми ограничителями диапазона выходного напряжения компаратора, которые включаются либо как ограничители в цегщ обратной связи, либо .между выходом компаратора и кле.ммой нулевого потенциала. Если в диодных ограничителях используют диоды Зенера, на дополнительный преобразователь подводят напряжение только одной полярности с источника отсчитывающего напряжения 8, а именно на ключ 45. Электронные ключи 30, 40, 41 могут и.меть последовательное, параллельное или последовательно-параллельное включение в схеме, причем .можно выбрать один тип ключа для всех.

Электронный переключатель 44 так управляется ко.мпараторо.м 43, что в интервале максимальных значений напряжения на выходе компаратора (фиг. 4е-з и 5е-з) и на выходе переключателя имеется по.южительное отсчитывающее напряжение, а в интервале минимальных значений напряжения на выходе компаратора и па выходе пере.ключателя имеется

отрщхательное напряжение. Выходные сигналы с логической схемы 45, которая иа своем быть выполнена в виде кольцевого счетчика со входе 21 обрабатывает сигнал равномерного хода с мультистабильной схемы 18, а по своему входу 52 обрабатывает выходной сигнал с дополнительного преобразователя, снимаемый либо с выхода 50 компаратора 43, либо с выхода переключателя 44, управляет ко.ммутацией ключей 30, 40, 41 таким образом, что в

0 том интервале, в котором выходной сигнал компаратора 43 имеет свое максимальное значение, на вход интегрирующей цепи 42 подается управляющее на 1ряжение и отсчитывающее напряжение с выхода переключателя 44, в то время как подведенное через третий ключ

5 41 от источника отсчитывающего напряжения на 8 на третий вход 61 интегрирующей цепи 42 напряжение отключается до появления сигнала синхронизации. Если интегрирующая цепь 42 изменяет знак интегрируемого

напряжения, в это.м интервале интегрирования управляющего и отсчитывающего напряжений выходное напряжение падает от своего максимального значения до своего мини.мального значения (фиг. 4д и 5д). Если в этом интервале интегрирования на вход 21 логической схемы 45 поступил сигнал равномерного хода с мультистабильной счетной схемы 18, работает механизм синхронизации дополнительного преобразователя. В этот момент логическая схема 45 посылает импульс на третий вход 63 компаратора 43, состояние которого изменяется на обратное, так что его выходное напряжение имеет минимальное значение (фиг. 4е-з и 5е-з). По этому изменению состояния компаратора 43 ключи 30 и 40 отключают от входа 47 интегрирующей цепи 42 управляющее напряжение, а от входа 57 интегрирующей схемы 42 - отсчитывающее напряжение с выхода переключателя 44, ключ 41 подает на вход 61 интегрирующей цепи 42 напряжение равномерного хода с источника 8 отсчитывающего напряжения. Те.м самым интервал интегрирования

управляющего и отсчитывающего напряжений (последний с выхода переключателя 44) заканчивается и начинается собственная синхронизация выходного напряжения интегрирующей цепи 42.

5 С учетом того, что интегрирующая цепь 42 изменяет знак интегрируемого напряжения, работа идет в направлении макси.мального значения выходного напряжения интегрирующей цепи, напряжение равномерного хода имеет отрицательную полярность. Постоянная времени интегрирования этого напряжения по сравнению с постоянной времени интегрирования управляющего и отсчитывающего напряжения очень мала, так что выходное напряжение интегрирующей цепи 42 очень быстро приближается к своему .максимуму (фиг. 5д, 4д). В тот момент, когда достигается значение максиму.ма, выходное напряжение компаратора 43 (4е и 5е) изменяется с минимального на максимальное значение, и сразу же после изменения состояния компаратора 43 изменяются вы ходы логической схемы 45 для управления клю9чами 30, 40 и 41 таким образом, что эти ключи принимают состояние, при котором ко входу 47 интегрирующей цепи 42 подключается отсчитывающее напряжение с выхода переключателя 44. Преобразователь этот вновь находится в состояиии интегрирования управляющего и отсчитывающего напряжений и весь процесс повторяется снова. Если в процессе (ходе) целого интервала интегрирования управляющего и отсчитывающего напряжений с выхода переключателя 44 на логическую схему 45 не поступает никакого сигнала синхронизации с мультистабильной счетной схемы 18, выходное напряжение интегрирующей цепи 42 падает до своего минимального значения (из фиг. 4д и 5д). В этот момент состояние компаратора 43 изменяется таким образом, что его выходное напряжение принимает свое минимальное значение (фиг. 4е и 5е). На это изменение состояния компаратора 43 логическая схема 45 выдает сигналы на управляющие входы 66, 65 ключей 30, 40 та, кой полярности, чтобы эти ключи отсоединили управляющее напряжение от входа 47 интегрирующей цепи 42. На входах интегрирующей цепи 42 устанавливается нулевой потенциал, и выходное напряжение этого звена остается на своем минимальном значении до поступления импульса синхронизации с мультистабильной счетной схемы 18 на вход 21 логической схемы 45. В этот момент снова начинает дей-/ ствовать механизм синхронизации дополнительного преобразователя, который подобен упомянутому процессу с той разницей, что в момент поступления сигнала синхронизации состояние компаратора 43 не изменяется, так как последний уже находится в правильном состоянии и необязательно отделять от входов 4.7, 57 интегрирующей цепи 42 управляющее и отсчитывающее напряжения с выхода переключателя 44, так как оба напряжения уже отсоединены. Это означает, что в момент поступления сигнала синхронизации на вход 2 логической схемы 45 эта логическая схема по своему выходу 58 так возбужает управляющий вход 59 ключа 41, что на вход 61 интегрирующей цепи 42 подается отрицательное напряжение с источника отсчитывающего напряжения 8 Выходное напряжение интегрирующей цепи 42 очень быстро приближается к своему максимальному значению и после того как оно достигнуто изменяет состояние компаратора 43 (фиг. 4д, 5д и 4, 5е). Вы.ходное напряжение компаратора 43 принимает свое максимальное значение и на это изменение логическая схема 45 реагирует таким образом, что поступающее через ключ 41 отрицательное напряжение источника отсчитывающего напряжения 8 отключается с входа 61 интегрирующей цепи 42 и при помощи ключей 30 и 40 подключает управляющее и отсчитывающее напряжения с переключателя 44 на входы 47, 57 интегрирующей цепи 42. Этот преобразователь опять переводится в интервал интегрирования и весь продесс повторяется. Интервал интегрирования управляющего и отсчитывающего напряжений .может бь1ть приравнен к интервалу минимального значения выходного напряжения компаратора 43, в котором выходное напряжение интегрирующей цепи 32 возрастает от своего .мини.мального до своего максимального значения. В этом случае синхронизация производится в направлении минимального значения выходного напряжеНИЯ интегрирующей цепи 42 посредством положительного напряжения с источника отсчитывающего напряжения 8. Синхронизация компаратора 43 во время интервала интегрирования протекает в направлении .максимального значения его выходного напряжения. Если интегрирующая цепь 42 производит интегрирование с одновременным изменением знака интегрируемого напряжения, интегрирующую цепь 42 и компаратор синхронизируют во взаимно противоположных направлениях. Б том случае когда интегрирующая цепь не ласт никакого изменения знака интегрируемого папряжения, компаратор и интегрирующую иепъ синхронизируют в одинаковом направлении. Выходное напряжение интегрирующей цепи 42 (фиг. 4д и 5д) синхронизирует всегда до граничного значения, от которого начинается интегрирование управляющего и отсчитывающего .напряжений, не обращая внимания на сохранение или изменение знака интегрируемого напряжения на интегрирующей цепи 42. Полярность напряжения, при помощи которого производится синхронизация выходного напряжения интегрирующей цепи 42, является в случае интегрирования с изменением знака интегрируемого напряжения противоположной полярности граничного значения выходного напряжения интегрирующей цепи 42, к которой оно синхронизируется, в случае интегрирования с сохранением знака интегрирземого напряжения полярность этого напряжения синхронизации совпадает с полярностью данного граничного значения, с которым оно синхронизируется. Снимаемый с выхода 50 компаратора 43 либо с выхода 53 переключателя 44 выходной сигнал дополнительного преобразователя подается на первый выходной зажим 27 дополнительного преобразователя, к которому могут быть подключены конечные каскады импульсного управления соответствующего прерывателя постоянного тока. Управляющие импульсы для основных и вспомогательных тиристоров данного задатчика тока вырабатывают по переднему и заднему фронтам сигнала на выходных клеммах 27, причем оно не рещает, какой тиристор получит передний фронт сигнала, а какой - задний фронт этого сигнала. Одновременное генерирование сигналов на этих обеих выходных клеммах возникает в той части интервала интегрирования управляющего напряжения и частот коммутации, когда в этот интервал интегрирования управляющего напря жения и отсчитывающего напряжения с выхода переключателя 44 вдополнительный преобразователь поступает синхронизирующий сигнал с выхода переключателя 44, т.е. в той части этого периода, в какой выходное напряжение интегрирующей цепи 42 монотонно изменяется от одного граничного значения к друго.му, варьируясь в этих пределах, причем второе граничное значение не достигается. В этой области действительно изменяется гилходной сигнал компаратора 43 при постуилении сиг-нала синхронизации в логическую схему 45. Граница этого диапазона определяется таким значением управляющего напряжения, при котором входное напряжение интегрирующей цепи 42 одновременно с поступлением импульса синхронизации на входе логической схемы достигает своего граничного значения, к которому оно приближается во время этого интервала работы (точка В на фиг. 3). Величипа этого граничного управляющего напряжения и соответствующая этому напряжению частота могут изменяться посредством изменения постоянной времени интегрирования управляющего напряжения соответствующей интегрирующей цепи 42. Формула изобретения . Устройство для управления многофазным тиристорным прерывателем постоянного тока, содержащее главный преобразователь напряжение-частота, по крайней мере два дополнительных преобразователя напряжение-частота, источник симметричного отсчитывающего напряжения и мультиетабильную счетную схему, отличающееся тем, что, с целью расширения диапазона регулирования напряжения на нагрузке, к цепи управления подключены входы главного и дополнительных преобразователей напряжение-частота, выход положительного полюса источника симметричного отсчитывающего напряжения подключен к входам положитель ного отсчитывающего напряжения главного и дополнительных преобразователей напряжениечастота, выход отрицательного полюса источнника симметричного отсчитывающего напряжения подключен к входам отрицательного отсчета напряжения главного и дополнительных преобразователей напряжение-частота, выход главного преобразователя напряжение-частота связан с входом мультистабильной счетной схемы, выходы которой соединены с входами синхронизации дополнительных преобразователей напряжение-чаетота и одновременно выведены на клеммы, предназначенные для коммутации вспомогательных тиристоров соответствующей фа;и 1 нрер1 1вателя, а выходы допо.пнитель.чых преобра ователей напряжение-частота выведены на клеммы, предназначенные для коммутации лавных тиристоров прерывателя. 2.Устройство по п. 1, отличающееся тем, что главный преобразователь напряжение-частота выполнен в виде интегрирующей цепи, компаратора и переключателя, причем выход интегрирующей цепи связан с входом компараторл. выход которого соединен с одной стороны с входом мультистабильной схемы, а с другой стороны - с входом переключателя, выход которого связан с входами цепи обратной связи, интегрирующей цени и комггаратора. 3.Устройство но п. 1, отличающееся тем, что дополнительный преобразователь напряжение-частота выполнен в виде электрон |ых ключей, интегрируюалей цепи, компаратора, электронного переключателя и логической схемы, где первый электронный ключ, вход которого образует вход дополнительного преобразовате.ля напряжение-частота, своим выходом подключен к первому входу интегрирующей цепи, выход которой соединен е первым входом компаратора, и выход компаратора соединен с клеммой, предназначенной для коммутации главных тиристоров прерывателя, со входом электронного переключателя и со вторым входом логической схемы, причем выход электронного переключателя связан с вторым входом компаратора и с входо.м второго электронного ключа, выход которого соединен со вторым входом интегрирующей цени, первый выход логической ехем1я связан с управляющим входо.м третьего электронного ключа, выход которого соединен с третьим входо.м интегрирующей цепи, причем второй выход логической схе.мы связан с третьим входом ко.мпаратора, а третий выход логической схемы связан с управляющими входа.ми первого и второго электронных ключей, причем первый вход логической схемы соединен с первым выходом мультистабильной счетной cxeMiii. Источники инфор., принятые во внимание при эксиертизе: 1. Глазенко А. Т. Полупроводниковые преобразователи в электроприводах постоянного тока. Л., «Энергия, 1973, с. 232-246.

Фиг г. 1ГГ1ПГЛ-f fFlRRF ЛГЩППЛЛГ f-l-J-T-J- rt-TU-L. -tlJlJ |1-Гт п Цлл-т-г IJi-ru-b 4 U 4J-4J Ir----jj - r-. r. .. ki. Гч Гч к 5 2ES iTJplflflJirUl 4JUUULJL ГГ------ trUn-TLriJlt4lJ i-ri-n I k N.-tk.-tss-J. vlJhiJ vJ v O dHrzA . «I 1Ш-1-Г1 Г1-Г Jbzbdb ;ggsS. 4 A JL-1

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Устройство управления статическим преобразователем частоты | 1978 |

|

SU1148573A3 |

| Интегрирующее устройство | 1981 |

|

SU1010616A1 |

| Способ измерения линейных перемещений и устройство для его осуществления | 1989 |

|

SU1820198A1 |

| СПОСОБ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ ПРОИЗВОЛЬНОЙ ФОРМЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

RU2034302C1 |

| СХЕМА ИНТЕГРАТОРА С ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 1994 |

|

RU2144213C1 |

| Агрегат гарантированного питания | 1990 |

|

SU1742942A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

| Способ измерения линейных перемещений и устройство для его осуществления | 1988 |

|

SU1563729A1 |

Авторы

Даты

1978-04-25—Публикация

1975-02-18—Подача