входом первого счетчика и с первым входом восьмого регистра, второй, третий, четвертый и пятый входы шестого коммутатора соединены соответственно с девятым входом блока обмена, с выходом седьмого триггера, с выходом десятого регистра и с вторым выходом двунаправленного коммутатора, выход тринадцатого триггера 11 0 соединен с шестым выходом блока обмена, второй, третий и четвертый входы седьмого коммутатора соединены соответственно с двенадцатым входом блока обмена, вторым выходом двунаправленного коммутатора и В1 1ходом девятого триггера, второй выход девятого регистра соединен с третьим выходом блока обмена.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор ввода-вывода | 1980 |

|

SU934465A1 |

| МОДУЛЬ ДЛЯ ОРГАНИЗАЦИИ ОБМЕНА СООБЩЕНИЯМИ | 2007 |

|

RU2359320C2 |

| Устройство для обмена информацией | 1983 |

|

SU1142824A1 |

| Устройство для сопряжения источников информации с вычислительной машиной | 1984 |

|

SU1179358A1 |

| Многофункциональный логический модуль | 1983 |

|

SU1164693A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1267397A1 |

| Селекторный канал | 1974 |

|

SU525081A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1987 |

|

SU1515165A1 |

| Устройство для контроля | 1981 |

|

SU1072052A1 |

ПРОЦЕССОР ВВОДА-ВЫВОДА по авт. св. № 934465, о тличающийс я тем, что, с целью повьшения производительности, в него введены седьмой дешифратор, одиннадцатый и двенадцатый триггеры, причем первый вход одиннадцатого триггера соединен с выходом блока управления, второй выход первого блока регистров соединен через седьмой дешифратор с входом двенадцатого триггера, вьлюд которого соединен с вторым входом одиннадцатого триггера, выход которого соединен с восьмым входом каждого блока обмена группы, при этом п блоков обмена объединены попарно в К групп (где К р п/2), причем третий, четвертый, пятый и шестой выходы первого блока обмена -ой группы (где i 1-К) соединены соответственно с девятьм, десятым, одиннадцатым и двенадцатым входами второго блока обмена i-ой группы, третий, четвертый, пятый и шестой выходы которого соединены соответственно с девятым, десятым, одиннадцатым и двенадцатым входами первого блока обмена i-ой группы, а в каждый блок обмена группы введены шестой и седьмой коммутаторы, одиннадцатый, двенадцатый и тринадцатый триггеры и второй элемент И, причем в каждом блоке обмена восьмой вход блока соединен с первым входом одиннадцатого триггера, второй вход которого соединен с вторым выходом первого узла триггеров, выход одиннадцатого триггера соединен с четвертым входом пятого, вторым входом шестого, первыми входами двенадцатого и тринадцатого триггеров, с девятым входом первого коммутатора, с третьим входом десятого триггера, с первым входом шестого коммутатора, с третьим входом двунаправленного р коммутатора и с первым входом седьмого ко1«4утатора, выход которого соеди(Л нен с вторым входом первого регистра, десятым входом первого коммутатора, третьим входом девятого регистра и третьим входом пятого коммутатора, выход шестого триггера соединен с шестьм входом пятого триггера, выход которого соединен с третьим входом шестого триггера, третий выход СО второго узла триггеров соединен с вторым входом двенадцатого триггера, выход которого соединен с пятым выходом .блока обмена и первьа 1 входом второго элемента И, второй вход которого соедатен с однинадцатьм входом блока обмена, а выход соединен с четвертым входом второго узла триггеров, выход второго кo в yтaтopa соединен с четвертым выходом блока обмена, одиннадцатый вход первого коммутатора соединен с одиннадцатым входом блока обмена, выход шестого коммутатора соединен с вторым входом тринадцатого триггера, с третьим

Изобретение относится к вычислительной технике, а именно к процессам ввода-вывода, и может быть использовано для построения многопроцессорных вычислительных комплексов с разветвленной сетью внешних устройств. По основному авт.св. № 934465 известен процессор ввода-вьюода, содержащий блок управления, первый вход которого соединен с входом процессора, выход блока управления соединен с первыми входами первого блока регистров, стека регистров, арифметического блока, первого, второго третьего и четвертого регистров и через пятьй регистр - с первым входом шестого регистра, выход которого соединен с дервым входом каждого блока обмена группы, группа выходов шестого регистра через пятый деашфратор соединена с вторыми входами соответствующих блоков обмена группы, первый выход первого регистра через второй дешифратор соединен с вторым входом блока управления, третий вход которого соединен с первь выходом первого блока регистров, второй вход которого и второй вход второго регистра соединены с вторьм выходом первого регистра, второй вход которого и четвертый вход блока управления соединены с первым выходом седьмого регистра, вход которого и третий вход первого регистра соединены с выходами восьмого регистра выход второго регистра соединен с вторыми входами арифметического блок и стека регистров, выход последнего соединен с третьим входом второго ре гистра и пятым входом блока управления, второй вькод первого блока регистров соединен с третьим входом арифметического блока, выход которого через девятый регистр соединен с первым входом первого буферного регистра, выход последнего соединен с первым входом первого коммутатора, выход которого соединен с первым входом десятого регистра, группа выходов последнего является группой выходов процессора, группа входов которого соединена с группой входов логического коммутатора, первый выход которого соединен с первым входом первого приоритетного блока, выход которого соединен с вторыми входами четвертого, десятого и первого буферного регистров, шестым входом блока управления и первым входом одиннадцатого регистра, выход которого соединен с третьим входом каждого блока обмена группы, группа выходов одиннадцатого регистра через третий дешифратор соединена с четвертыми входами соответствующих блоков обмена группы, первьй выход каждого из которых соединен через второй приоритетный блок с группой входов двенадцатого регистра и первьм входом двенадцатого регистра, выход которого соединен с вторьм входом четвертого регистра, и через второй буферный регистр - с вторым входом первого коммутатора, второй, третий и четвертый входы двенадцатого регистра соединены с первым, вторым и третьим выходами каждого блока обмена группы, четвертые выходы которых Соединены через третий приоритетный блок с группой входов восьмого регистра , вход которого соединен с вторым выходом каждого блока обмена

группы, соединенного шиной обмена с внешними устройствами, группа входов процессора соединена с грулпой входов тринадцатого регистра, первый выход которого соединен с первым входом логического коммутатора и через четырнадцатый регистр - с вторым входом одиннадцатого регистра и четвертым входом первого регистра, второй выход тринадцатого регистра чере четвертьй дешифратор соединен с третим входом одиннадцатого регистра и седьмым входом блока управления, третий выход первого блока регистров через пятнадцатый регистр соединен с третьим входом.первого буферного регистра и вторым входом шестого регистра, третий вход которого соединен с выходом третьего регистра и первым входом пятого дешифратора, второй вход и выход которого соединены соответственно с вторым выходом седьмого регистра и третьим входом стека регистров, выходы четвертого регистра соединены с группой входов первого приоритетного блока, второй выход логического коммутатора соединен с первь м входом первого триггера, кроме того, в устройство также входят второй блок регистров, шестой дешифратор и девять триггеров, причем выход десятого регистра соединен с вторьм входом логического коммутатора и входом второго блока регистров, выход которого соединен с входом тринадцатого регистра и третьим входом логического коммутатора, второй и третий выходы которого соединены с первыми входами соответственно второго и третьего тригге ров, выход второго триггера через последовательно соединенные четвертый и пятый триггеры соединен с пяты входом каждого блока обмена группы, выход первого приоритетного блока соединен с первьо и входами шестого и седьмого триггеров,увходаа восьмого триггера соединены содним из выходов второго приоритетного блока и первым и пятым выходами каждого блока обмены группы, выход восьмого триггера через последовательно соединенные шестой и седьмой триггеры соединен с вторым входом третьего триггера, выход которого соединен с вторым входом первого триггера, выход последнего соединен с вторым входом второго триггера, четвертый

выход первого блока регистров соединен через шестой дешифратор с входом девятого триггера, выход которого через десятый триггер соединен с шестым входом каждого блока обмена группы, при этом каждый блок обмена содержит пять коммутаторов, три дешифратора, десять регистров, два узла триггеров, буферную память, три счетчика, десять триггеров, двунаправленный коммутатор и элемент И, причем выход первого коммутатора соединен с первым входом буферной памяти, выход которой соединен с первьм входом второго коммутатора, выхо последнего соединен с первыми входами третьего коммутатора и двунаправленного коммутатора и вторым выходом блока, первый вход которого соединен с первыми входами первого коммутатора и первого узла триггеров, второй вход которого соединен с вторым входом блока, третий вход последнего соединен с первыми входами первого и второго триггеров и вторым входом первого коммутатора, четвертый вход блока соединен с первыми входами первого регистра и третьего триггера и третьим входом первого коммутатора, пятый вход блока соединен с вторыми входами буферной памяти и третьего триггера, выход которого соединен с первыми входами второго, третьегоj четвертого, пятого и шестого регистров и вторыми входами второго и третьего коммутаторов, первый выход первого узла триггеров соединен с четвертым выходом блока, второй выход первого узла триггеров соединен с первыми входами четвертого триггера и второго узла триггеров, третьими входами буферной памяти, второго и третьего коммутаторов, четвертым входом первого коммутатора и вторыми входами второго, третьего, четвертого, пятого и шестого регистров, третьи входы которых соединены с соответствующими выходам третьего коммутатора, шестой вход блока соединен с вторым входом четвертого триггера, выход которого соединен с вторым входбм второго триггера, четвертым входом третьего коммутатора и первым входом пятого триггера, выход которого соединен с вторыми входами второго узла триггеров и двунаправленного коммутатора и с первьм входом элемента И, выход которого соединен с четвертым входом буферной памяти, пятым входом перво коммутатора, вторым входом пятого триггера и через шестой триггер - с пятым входом буферной памяти и шесты входом первого коммутатора, выход первого дешифратора соединен с вторы входом первого триггера, первым вход седьмого триггера и третьими входами второго и пятого триггеров, выход второго триггера соединен с первым входом седьмого регистра и через восьмой триггер - с первым входом четвертого коммутатора и пятыми выходами блока и входом третьего комму татора, выход первого триггера соеди нен с вторым входом седьмого регистра и первыми входами восьмого и девя того регистров, первого счетчика к пятого коммутатора, выход которого соединен с шестым входом третьего коммутатора и первым входом второго счетчика, вьпсод второго дешифратора соединен с третьим входом первого триггера, первым входом девятого триггера и четверть&ш входами второг и пятого триггеров, выходы третьего дешифратора соединены с вторыми вход ми седьмого и девятого триггеров, выход девятого триггера соединен с вторыми входами девятого регистра, пятого коммутатора, первого регистра первого счетчика и третьим входом седьмого регистра, выход .которого соединен с первым выходом блока, седьмым входим третьего коммутатора и первым входом третьего счетчика, первые выходы которого и второго счетчика соединены с восьмым и девятым входами третьего коммутатора, выход седьмого триггера соединен с вторым входом восьмого регистра, четвертыми входами первого триггера и седьмого регистра и третьими входа ми пятого коммутатора и первых регистров и счетчика, вь1ход первого регистра соединен с шестым входом бу ферной памяти и десятого регистра, выход первого счетчика соединен с четвертым входом второго ком мут&тора и через десятый регистр с третьим входом двунаправленного коммутатора, выход которого соединен с первьм входом.десятого триггера, вторЧ)1м входом элемента И седьмым входом первого коммутатора, третьими входами восьмого и девятого регистров и четвертыми входами пятого коммутатора и первых регистра и счетчика, выход шестого триггера и первый выход второго узла триггеров соединены с третьим и четвертьм входами первого узла триггеров, второй выход второго узла триггеров соединен с третьими входами седьмого и девятого триггеров, выходы восьмого регистра соединены с пятым входом первого триггера и первым входом второго дешифратора, выходы девятого регистра соединены с четвертым входом двунаправленного коммутатора и вторым входом второго дешифратора, третий выход второго узла триггеров соединен с вторым входом десятого триггера, выход которого соединен с третьим входом второго узла триггеров, пятым входом второго коммутатора и пятым входом двунаправленного коммутатора, соединенного с шиной обмена, вторые выходы второго и третьего счетчиков соединены с восьмым и девятым входами первого коммутатора, десятый вход которого соединен с выходом ветвертого регистра и вторым входом четвертого коммутатора, выход второго регистра через четвертый коммутатор соединен с третьим выходом блока и вторым входом третьего счетчика, выход третьего регистра соединен с пятыми входами второго и пятого триггера, выхода пятого и шестого регистров соединены с входами первого и третьего дешифраторов, выход девятого триггера соединен с шестым входом первого триггера fl3. Недостатком известного устройства является его низкая производительность, обусловленная ограниченными функциональными возможностями, не позволяющими производить обмен между двумя областями оперативной памяти без использования внешнего оборудования. Такой обмен информацией является необходюшм условием обеспечения мультипрограммного режима вычислительной системы. Целью изобретения является повышение производительности процессора ввода-вывода в режиме передачи информации между двумя областями оперативной памяти. Поставленная цель достигается тем, что в процессор ввода-вывода введены седьмой дешифратор, одиннадцатый и двенадцатый триггеры, причем первый вход одиннадцатого триггера

соединен с выходом блока управления, второй выход первого блока регистров соединен через седьмой дешифратор с входом двенадцатого триггера, выход которого, соединен с вторым входом одиннадцатого триггера, выход которого соединен с восьмым входом каждого блока обмена группы, при этом п блоков обмена объединены попарно в К групп (где К п/2), причем третий, четвертый, пятый и шестой выходы первого блока, обмена i-ой группы (где i 1-К) соединены соответственно с девятым,., десятым, одиннадцатым и двенадцатым входами второго блока обмена i-ой группы, третий, четвертый, пятый и шестой выходы которого соединены соответственно с девятым, десятым, одиннадцатым и двенадцатым входами первого блока обмена i-ой группы, а в каждый блок обмена группы введены шестой и седьмой коммутаторы, одиннадцатью, двенадцатый и тринадцатый триггеры и второй элемент И, причем в каждом блоке обмена восьмой вход блока соединен с первым входом одиннадцатого триггера, второй вход которого соединен с вторым выходом первого узла триггеров, выход одиннадцатого триггера соединен с четвертым входом пятого, вторым входом шестого, первыми входами двенадцатого и тринадцатого триггеров, с девятым входом первого коммутатора, с третьим входом двунаправленного коммутатора и с первым входом седьмого коммутатора, выход которого соединен с вторым входом первого регистра, десятым входом первого коммутатора, третьим входом девятого регистра и третьим входом пятого коммутатора, выход шестого триггера соединен с шестым входом пятого триггера, выход которого соединен с третьим входом шестого триггера, третий выход второго узла триг геров соединен с вторым входом двенадцатого триггера, выход которого соединен с пятым выходом блока обмена и первым входом второго элемента И, второй вход которого соединен с одиннадцатым входом блока обмена, а выход соединен с четвертым входом второго узла триггеров выход второго коммутатора соединен с четвертым выходом блока обмена, одиннадцатый вход первого коммутатора соединен с одиннадцатым входом блока обмена.

выход шестого коммутатора соединен с вторым входом тринадцатого триггера, с третьим входом первого счетчит

ка и с первым входом восьмого регистра, второй, третий, четвертый и пятый входы шестого коммутатора соединены соответственно с девятым входом блока обмена, с выходом седьмого триггера, с выходом десятого регистра и с вторым выходом двунаправленного коммутатора, выход тринадцатого триггера соединен с шестым выходом блока обмена, второй, третий и четвертый входы седьмого коммутатора соединены соответственно с двенадцатым входом блока обмена, вторым выходом двунаправленного коммутатора и выходом девятого триггера, второй выход девятого регистра соединен с третьим выходом блока обмена.

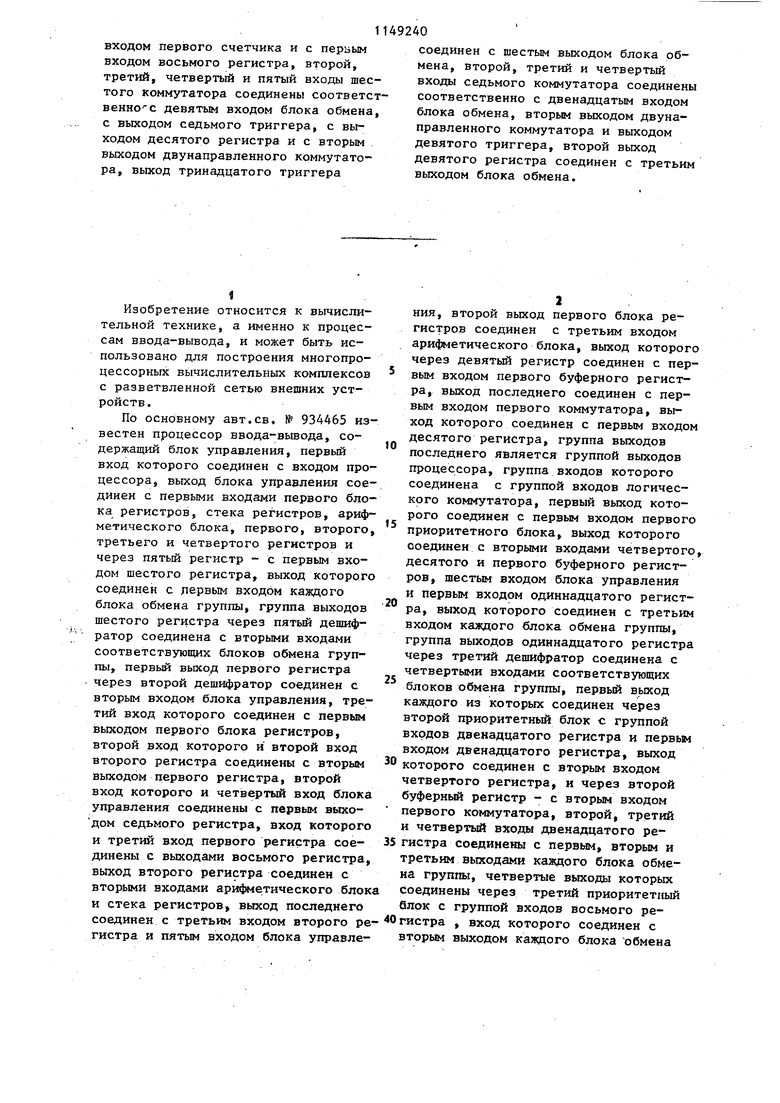

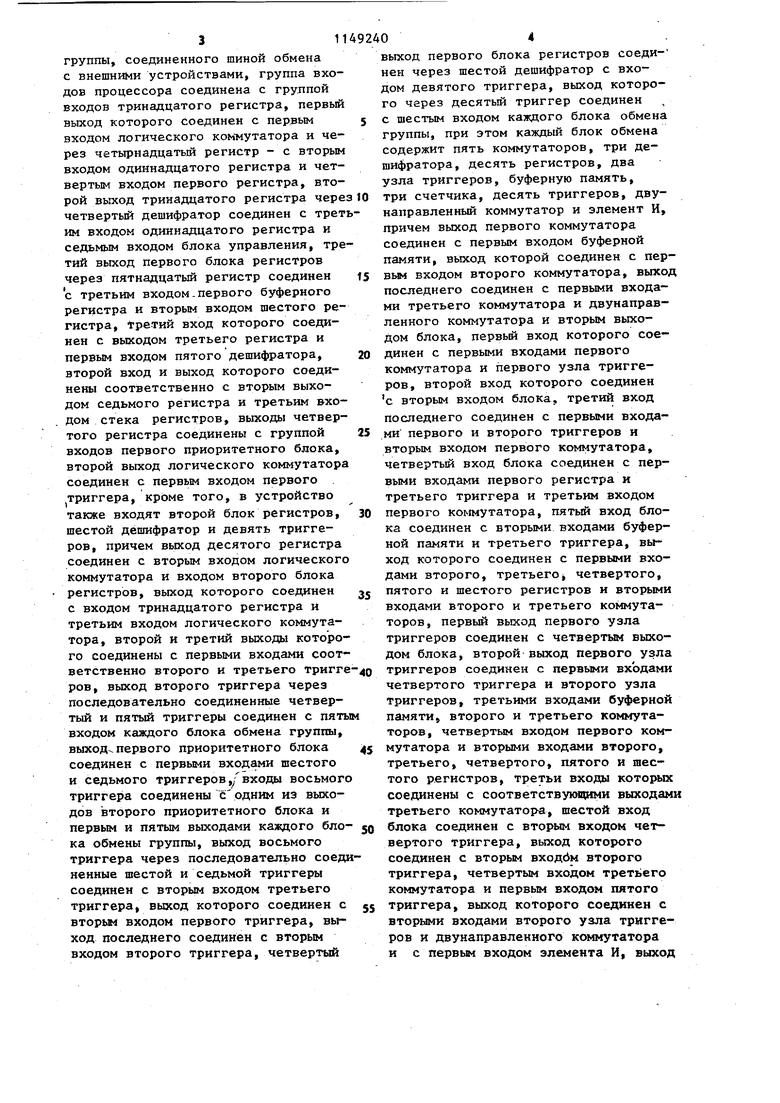

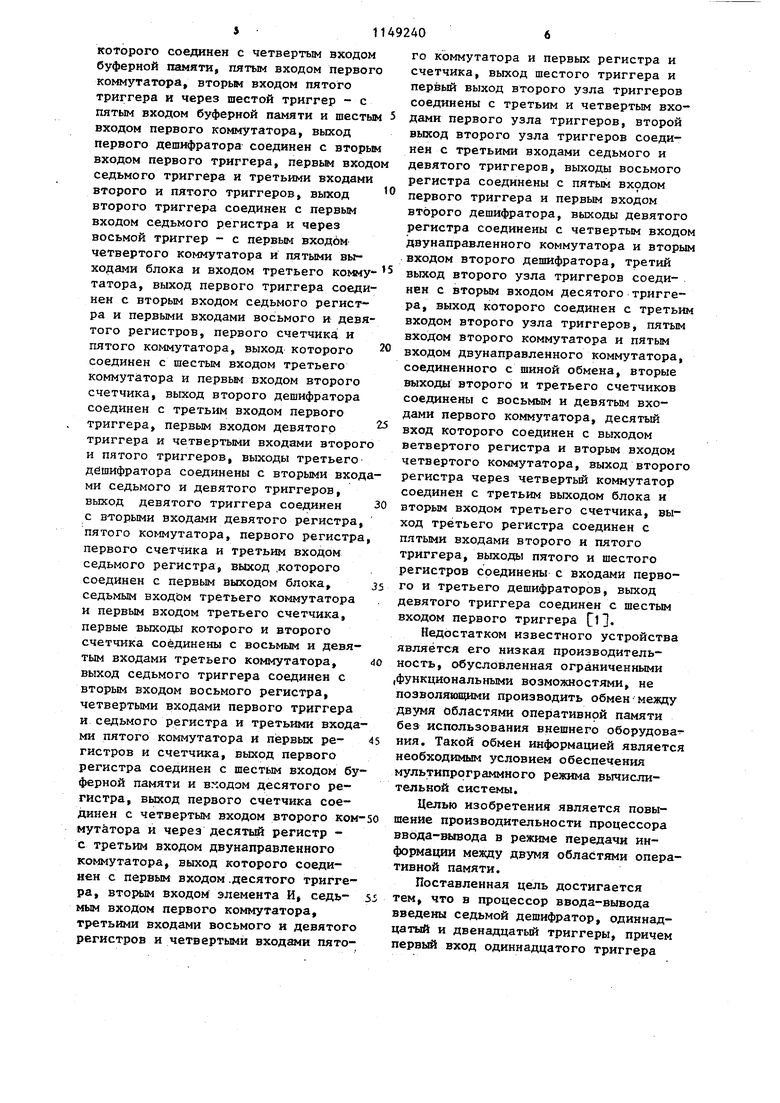

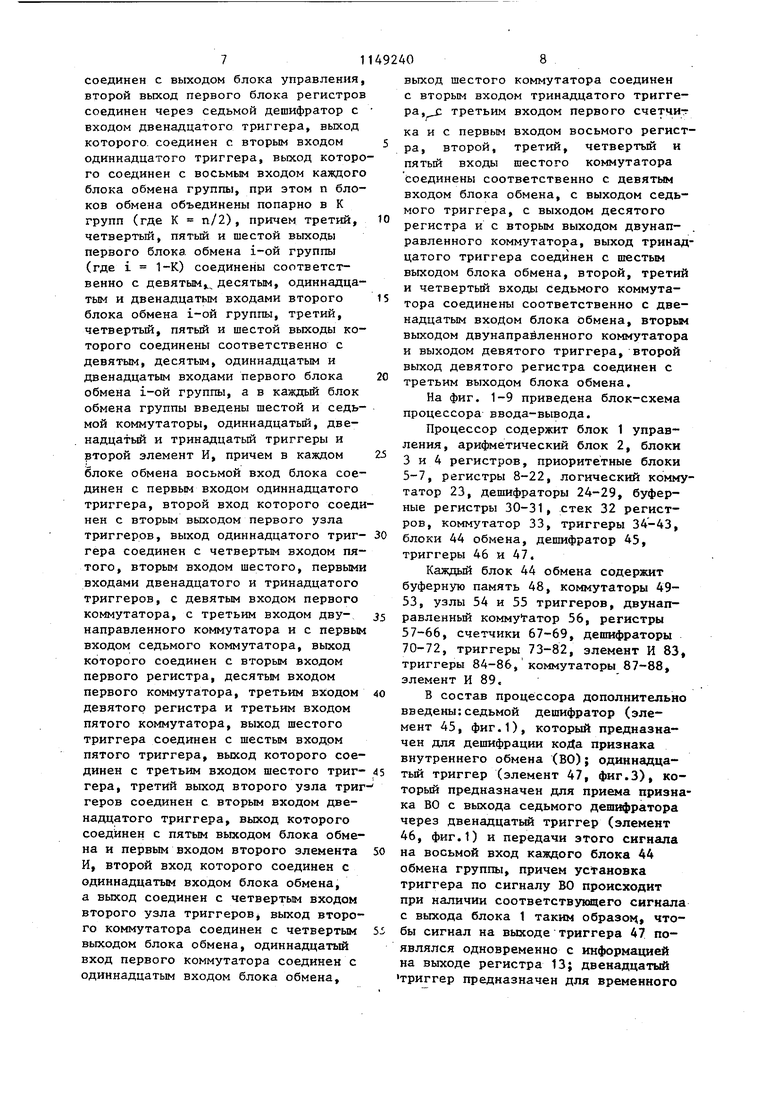

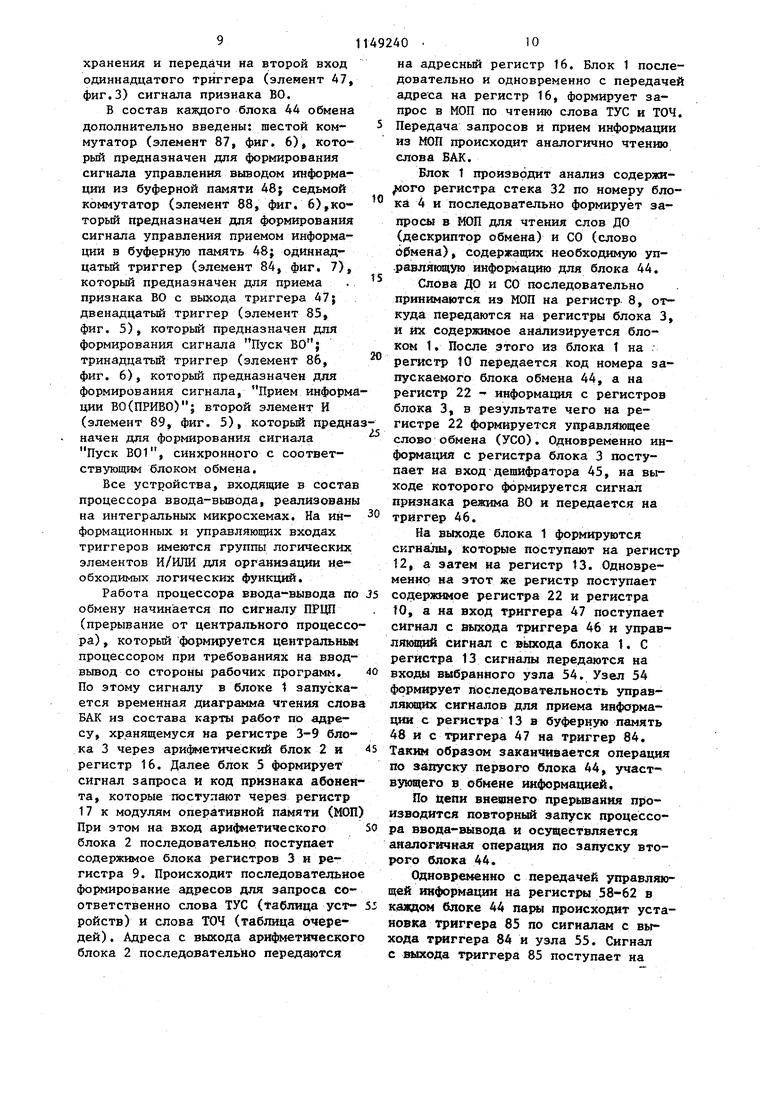

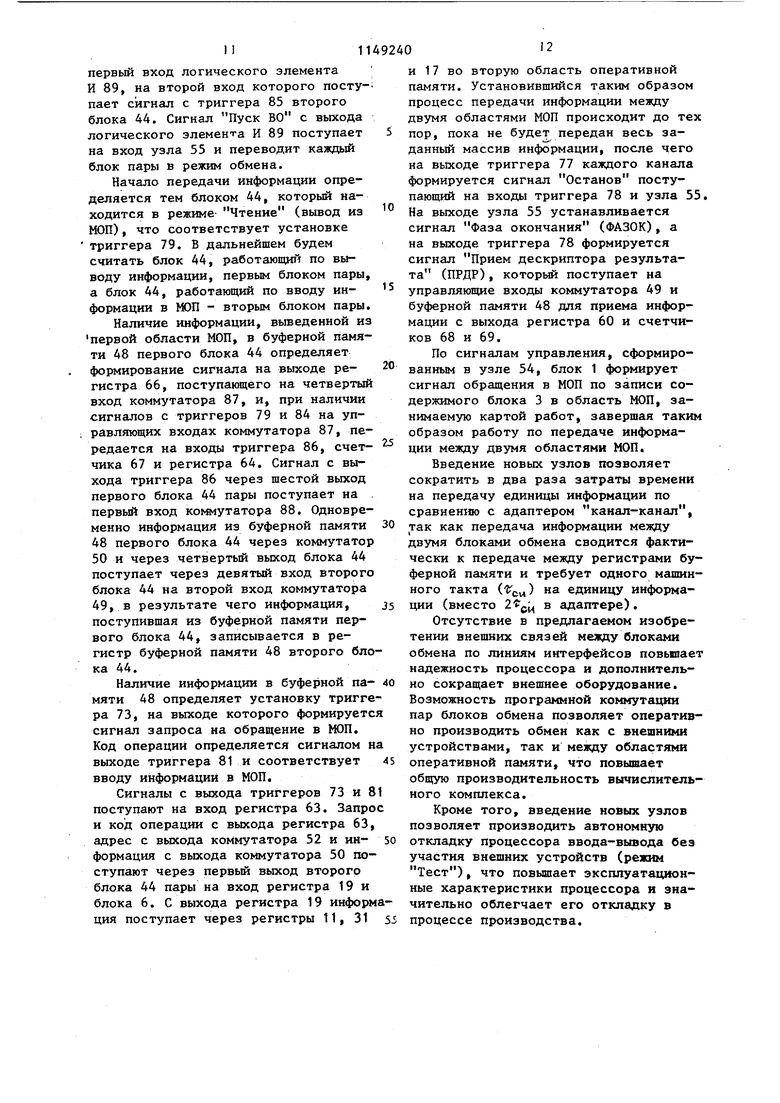

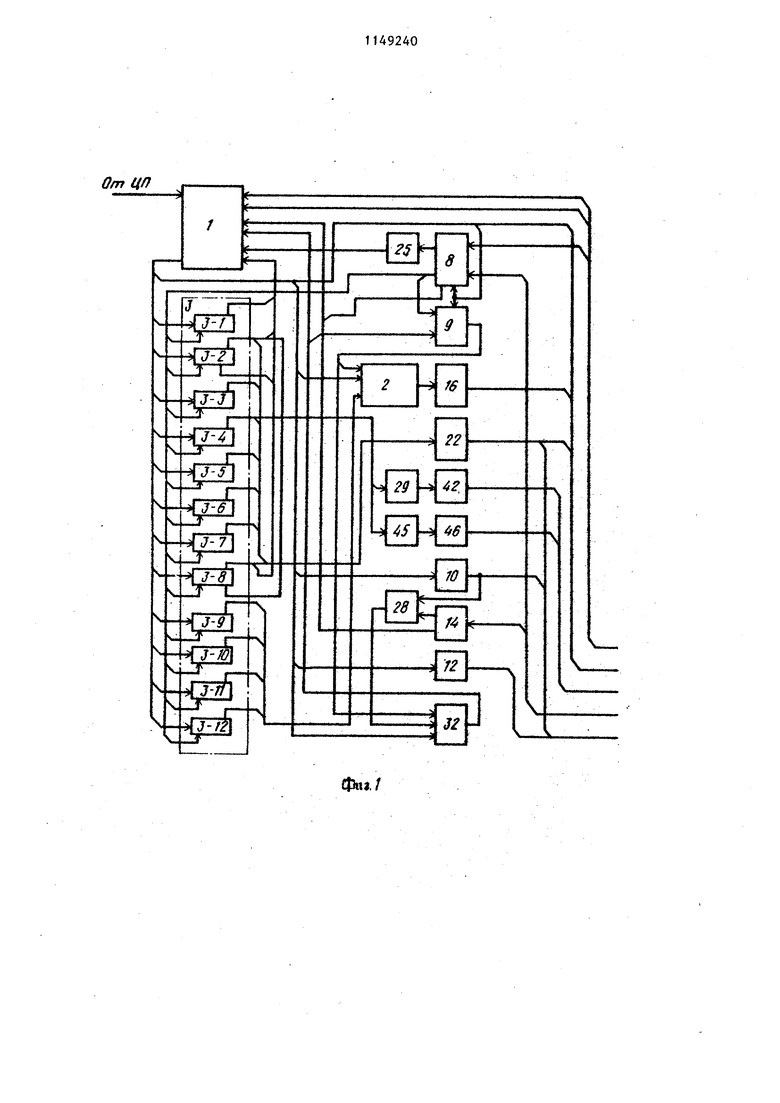

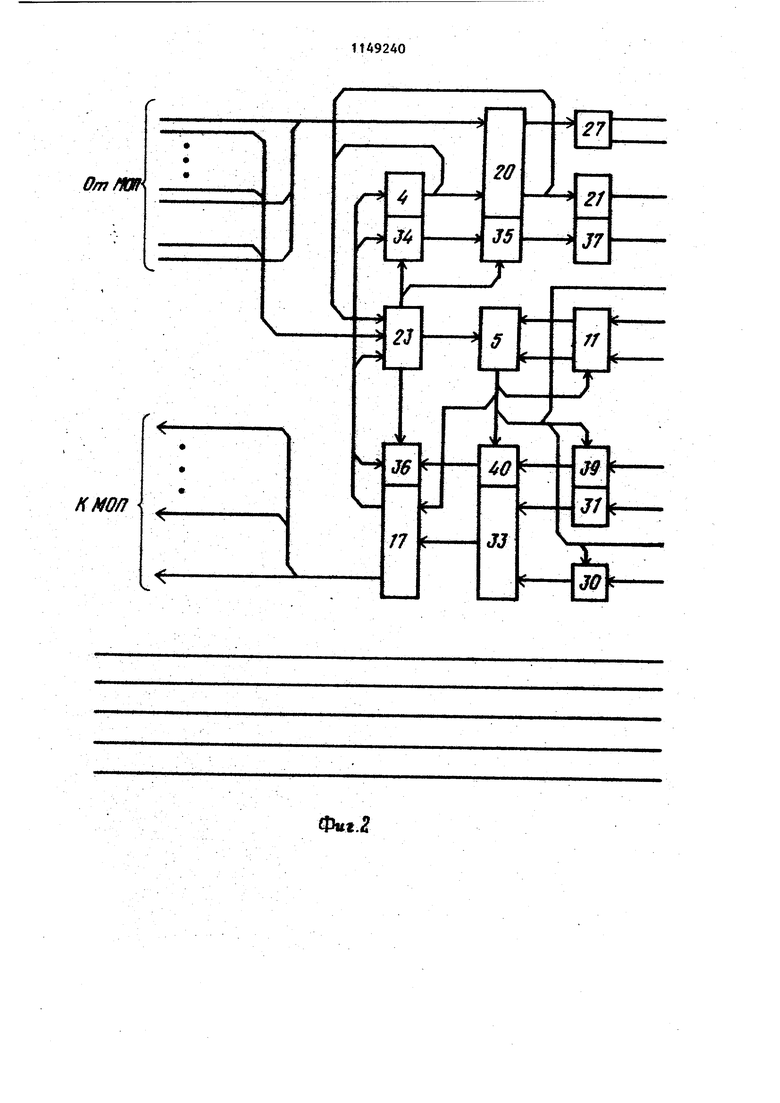

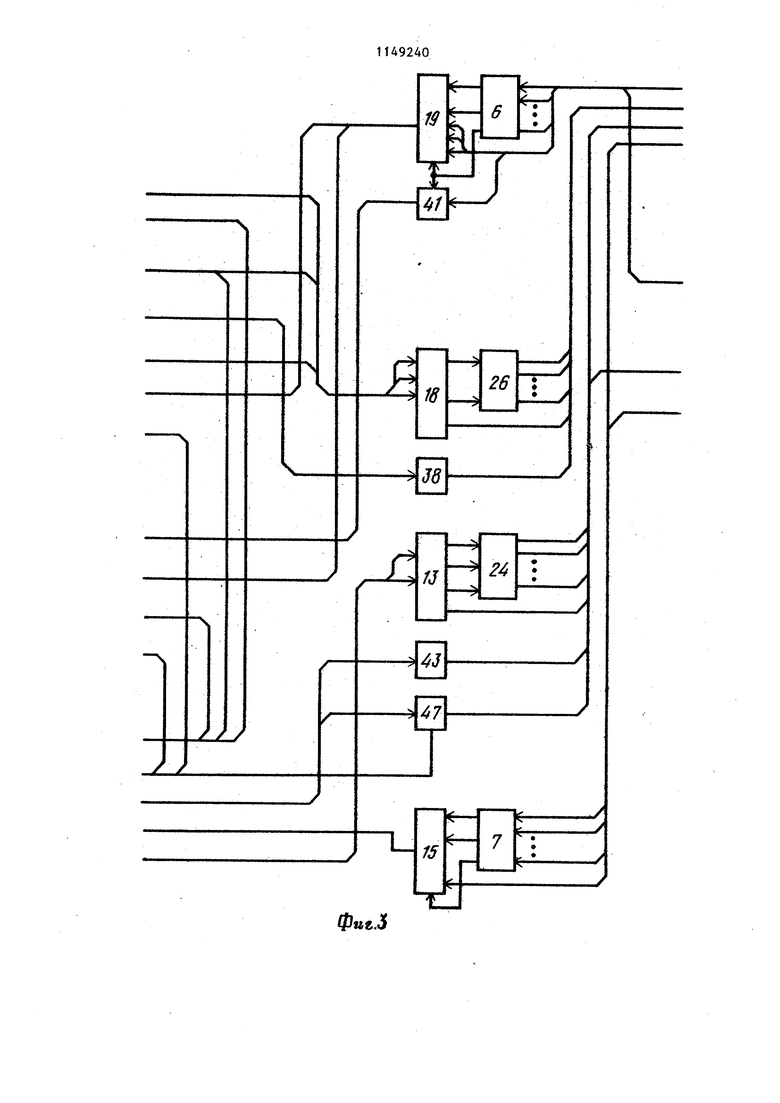

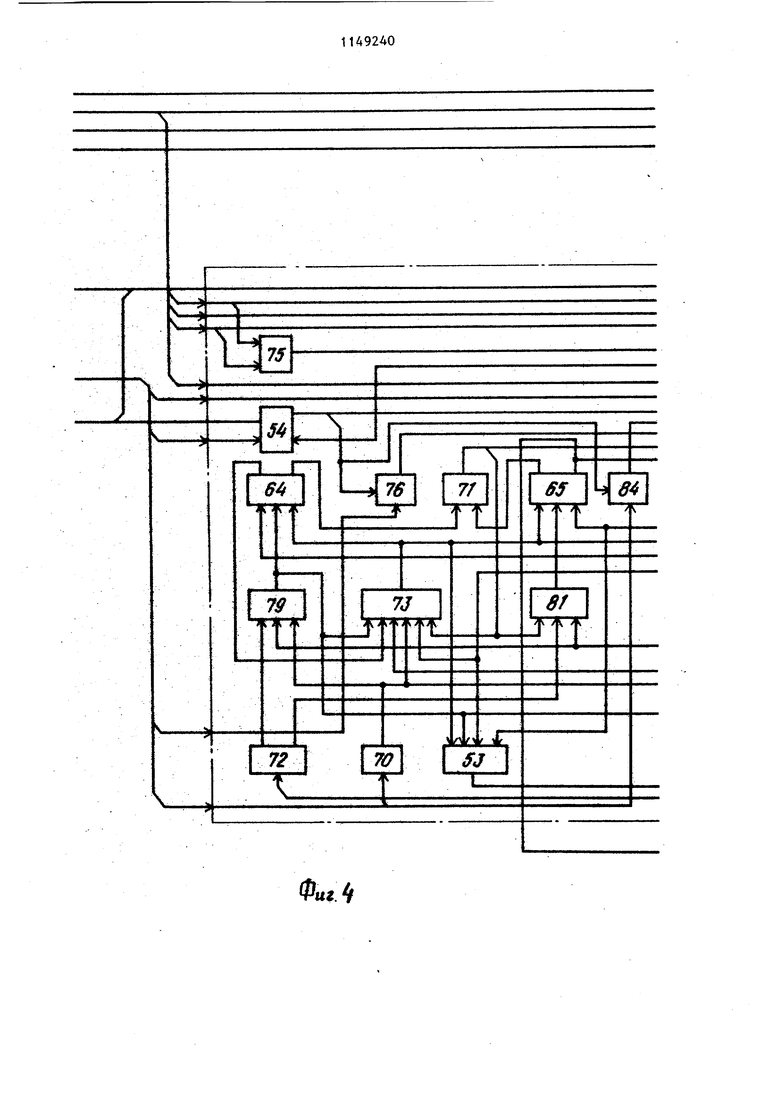

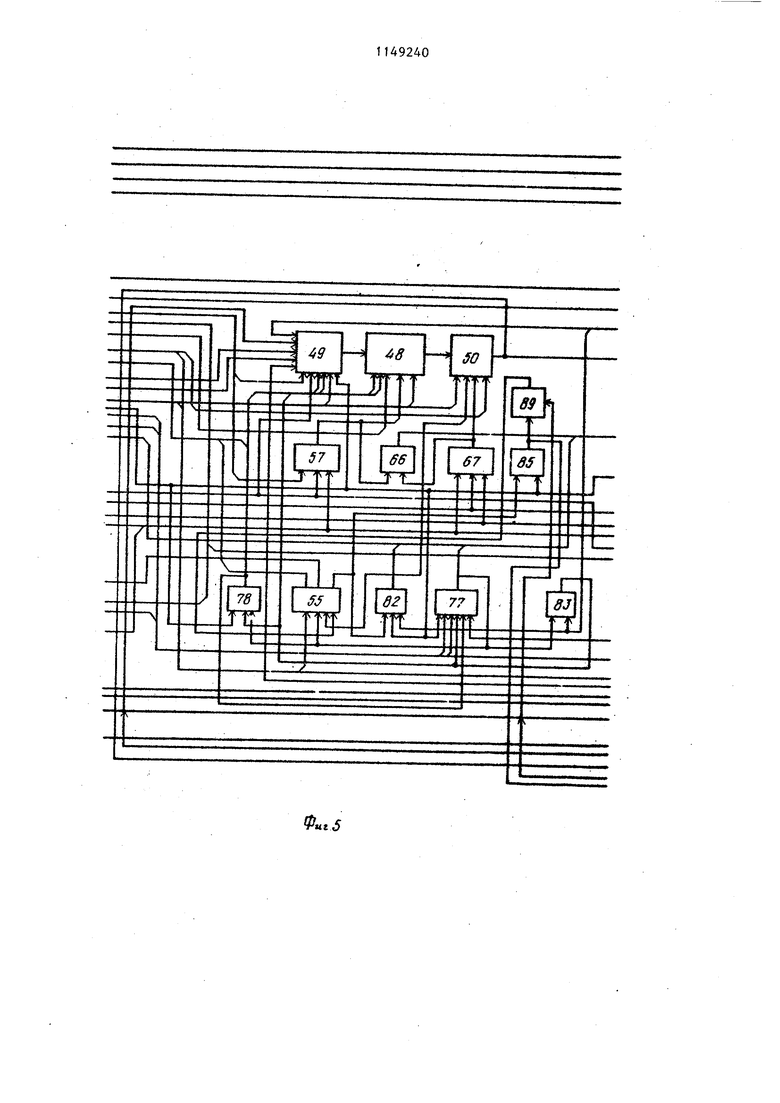

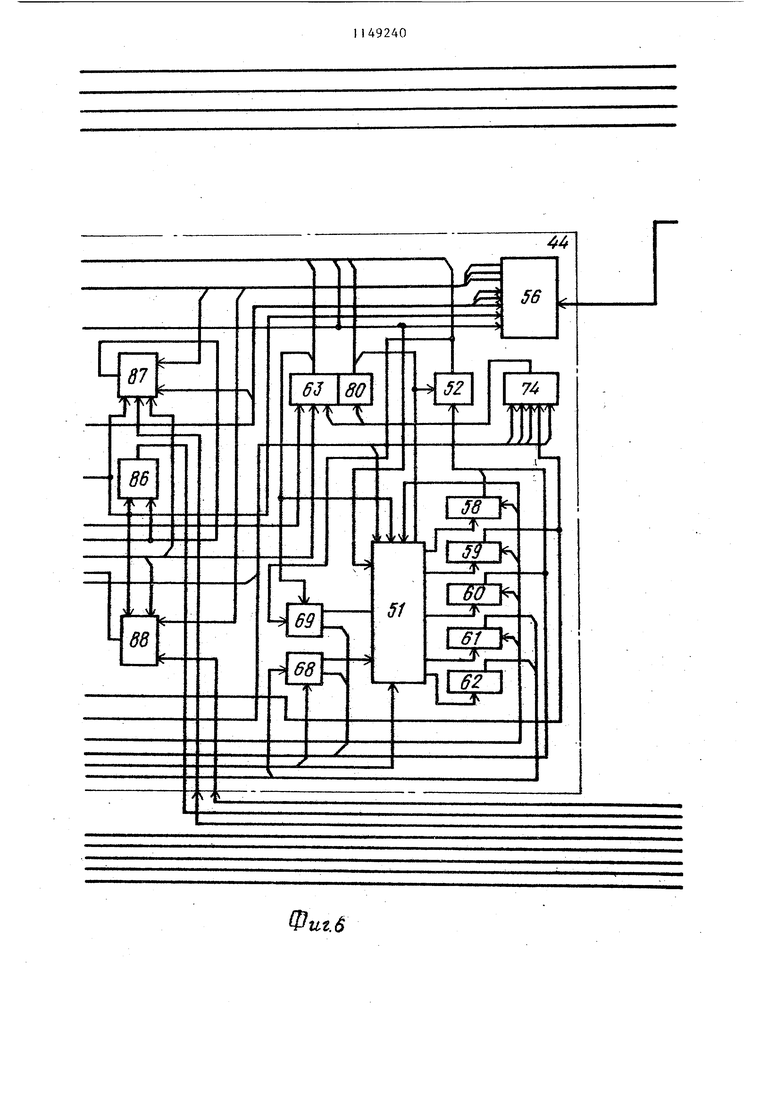

На фиг. 1-9 приведена блок-схема процессора ввода-вывода.

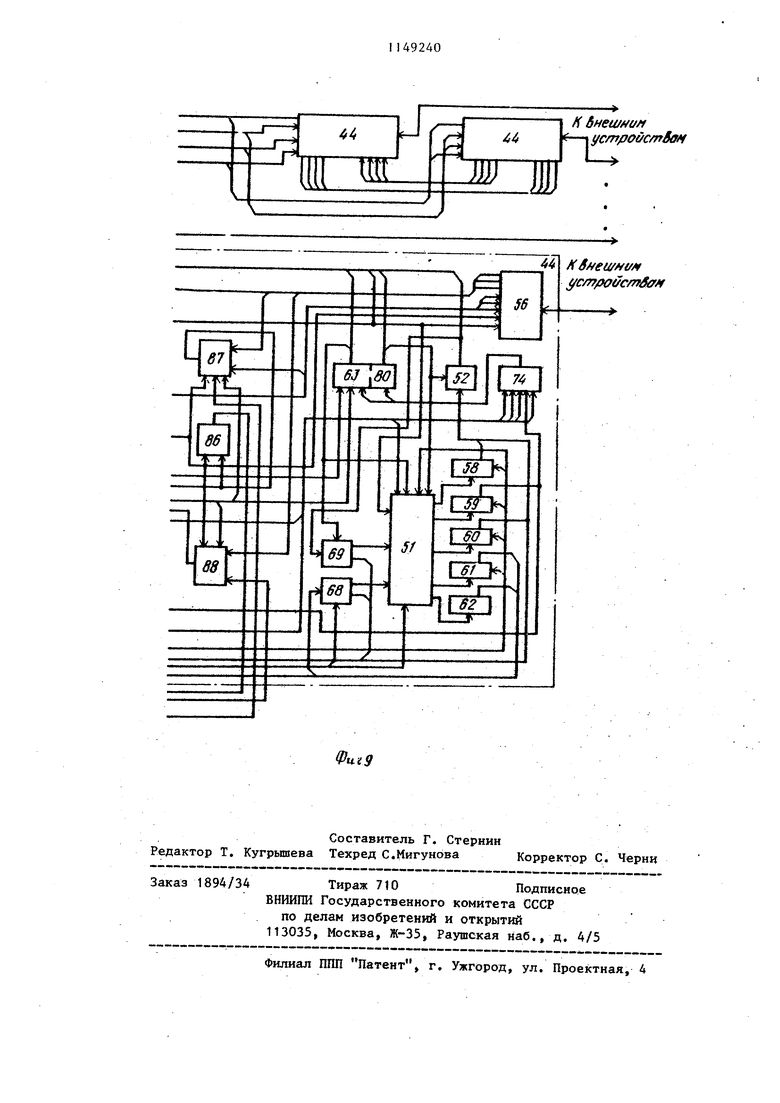

Процессор содержит блок 1 управления, арифметический блок 2, блоки 3 и 4 регистров, приоритетные блоки 5-7, регистры 8-22, логический коммутатор 23, дешифраторы 24-29, буферные регистры 30-31, стек 32 регистров, коммутатор 33, триггеры 34-43, блоки 44 обмена, дешифратор 45, триггеры 46 и 47,

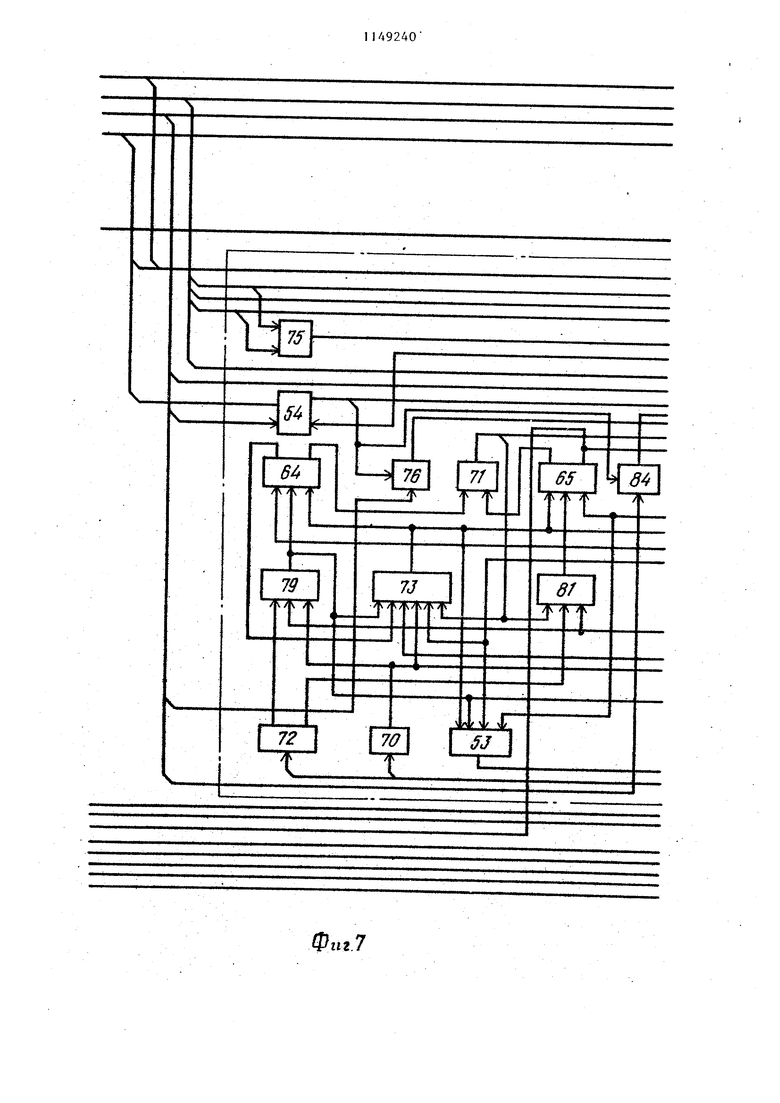

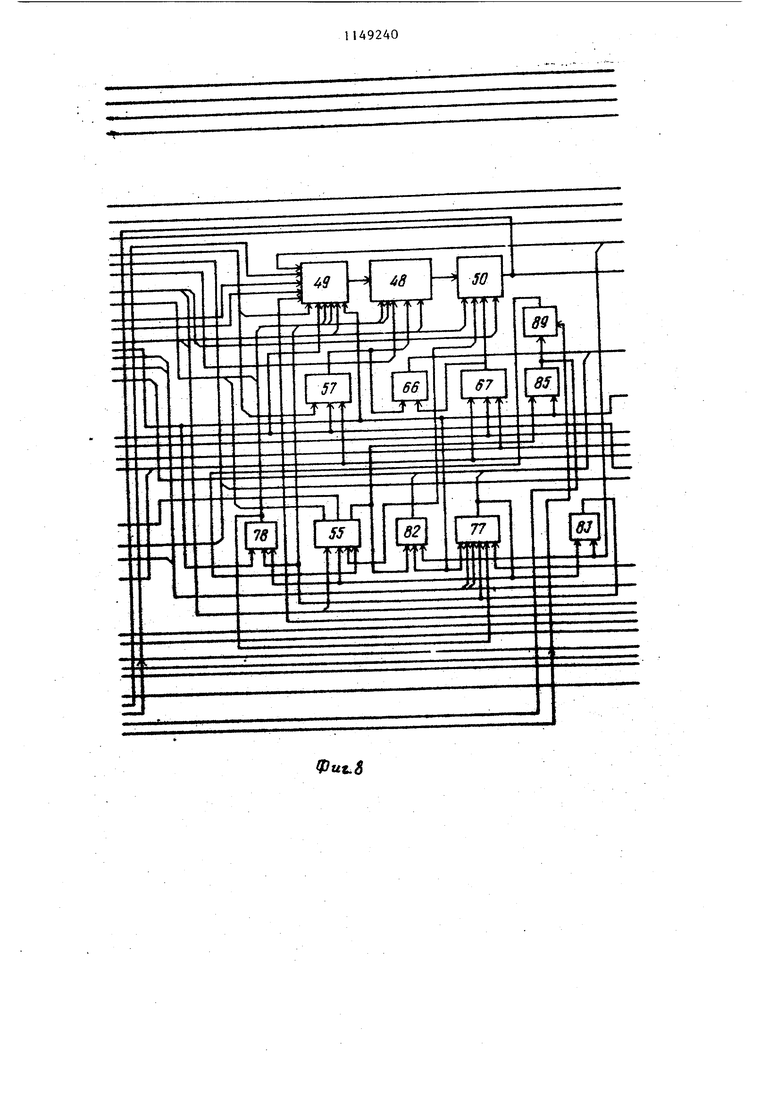

Каждый блок 44 обмена содержит буферную память 48, коммутаторы 4953, узлы 54 и 55 триггеров, двунаправленньй коммутатор 56, регистры 57-66, счетчики 67-69, дешифраторы 70-72, триггеры 73-82, элемент И 83, триггеры 84-86, коммутаторы 87-88, элемент И 89.

В состав процессора дополнительно введены:седьмой дешифратор (элемент 45, фиг.1), который предназначен для дешифрации коДа признака внутреннего обмена (ВО); одиниадцатьй триггер (элемент 47, фиг.З), который предназначен для приема признака ВО с выхода седьмого дешифратора через двенадцатый триггер (элемент 46, фиг.1) и передачи этого сигнала на восьмой вход каждого блока 44 обмена группы, причем установка триггера по сигналу ВО происходит при наличии соответствукщего сигнала с выхода блока 1 таким образом;, чтобы сигнал на выходе триггера 47 появлялся одновременно с информацией на выходе регистра 13; двенадцатый триггер предназначен для временного хранения и передачи на второй вход одиннадцатого триггера (элеиент 47, фиг.З) сигнала признака ВО. В состав каждого блока 44 обмена дополнительно введены: шестой коммутатор (элемент 87, фиг. 6), который предназначен для формирования сигнала управления выводом информации из буферной ПШ4ЯТИ 48f седьмой коммутатор (элемент 88, фиг, 6),который предназначен для формирования сигнала управления приемом информа ции в буферную память 48; одиннадцатый триггер (элемент 84, фиг, 7), который предназначен для приема признака ВО с выхода триггера 47} двенадцатый триггер (элемент 85, фиг. 5), который предназначен для формирования сигнала Пуск тринадцатьй триггер (элемент 86, фиг. 6), которьй предназначен для формирования сигнала, Прием информа ции ВО(ПРИВО); второй элемент И (элемент 89, фиг. 5), которьй предна начен для формирования сигнала Пуск В01, синхронного с соответствующим блоком обмена. Все устройства, входящие в состав процессора ввода-вывода, реализованы на интегральных микросхемах. На ийформационных и управляющих входах триггеров имеются группы логических элементов И/ИЛИ для организации необходимых логических функций. Работа процессора ввода-вывода по обмену начинается по сигналу ПРЦП (прерывание от центрального процессо ра) , который 4юрмируется центральшФ процессором при требованиях на вводвывод со стороны рабочих программ, По этому сигналу в блоке 1 запускается временная диаграмма чтения слов БАК из состава карты работ по адресу, хранящемуся на регистре 3-9 бло ка 3 через арис1а4етический блок 2 и регистр 16. Далее блок 5 формирует сигнал запроса и код признака абонен та, которые поступают через регистр 17 к модулям оперативной памяти (МОП При этом на вход арифметического блока 2 последовательно поступает содержимое блока регистров 3 и регистра 9. Происходит последовательно формирование адресов для запроса соответственно слова ТУС (таблица устройств) и слова ТОЧ (таблица очередей) . Адреса с выхода арифметическог блока 2 последовательйо передаются на адресный регистр 16. Блок 1 последовательно и одновременно с передачей адреса на регистр 16, формирует запрос в МОП по чтению слова ТУС и ТОЧ, Передача запросов и прием информации из ЬЮП происходит аналогично чтению слова ВАК. Блок 1 производит анализ содержи юго регистра стека 32 по номеру блока 4 и последовательно формирует запросы в МОП для чтения слов ДО (дескриптор обмена) и СО (слово 60мена), содержащих необходимую уп-равлЯющую информацию для блока 44, Слова ДО и СО последовательно принюхаются из МОП на регистр 8, откуда передаются на регистры блока 3, и ИХ содержимое анализируется блоком 1, После этого из блока 1 на , регистр 10 передается код номера запускаемого блока обмена 44, а на регистр 22 - информация с регистров блока 3, в результате чего на регистре 22 формируется управляющее слово обмена (УСО), Одновременно информация с регистра блока 3 поступает на вход дешифратора 45, на выходе которого формируется сигнал признака режима ВО и передается на триггер 46, На выходе блока 1 формируются сигналы, которые поступают на регистр 12, а затем на регистр 13, Одновременно на этот же регистр поступает содержимое регистра 22 и регистра to, а на вход триггера 47 поступает сигнал с выхода триггера 46 и управляющий сигнал с выхода блока 1, С регистра 13 сигналы передаются на входы выбранного узла 54, Узел 54 формирует последовательность управляк цих сигналов для приема информации с регистра 13 в буферную память 48 и с триггера 47 на триггер 84, Таким образом заканчивается операция по запуску первого блока 44, участвующего в обмене информацией. По цепи внешнего прерывания производится повторный запуск процессора ввода-вывода и осуществляется аналогичная операция по запуску второго блока 44, Одновременно с передачей управляющей информации на регистры 58-62 в каждом блоке 44 происходит установка триггера 85 по сигналам с выхода триггера 84 и узла 55, Сигнал с триггера 85 поступает на первый вход логического элемента И 89, на второй вход которого поступает сигнал с триггера 85 второго блока 44. Сигнал Пуск ВО с выхода логического элемента И 89 поступает на вход узла 55 и переводит каждый блок пары в режим обмена. Начало передачи информации определяется тем блоком 44, который находится в режиме Чтение (вывод из МОП), что соответствует установке триггера 79. В дальнейшем будем считать блок 44, работающий по выводу информации, первым блоком пары, а блок 44, работающий по вводу информации в МОП - вторым блоком пары. Наличие информации, вьгоеденной из первой области МОП, в буферной памяти 48 первого блока 44 определяет формирование сигнала на выходе регистра 66, поступающего на четвертый вход коммутатора 87, и, при наличии сигналов с триггеров 79 и 84 на уп: равляющих входах коммутатора 87, передается на входы триггера 86, счетчика 67 и регистра 64. Сигнал с выхода триггера 86 через шестой выход первого блока 44 пары поступает на первый вход коммутатора 88. Одновременно информация из буферной памяти 48 первого блока 44 через коммутатор 50 и через четвертый выход блока 44 поступает через девятый вход второго блока 44 на второй вход коммутатора 49, в результате чего информация, поступившая из буферной памяти первого блока 44, записывается в регистр буферной памяти 48 второго бло ка 44. Наличие информации в буферной памяти 48 определяет установку тригге ра 73, на выходе которого формируетс сигнал запроса на обращение в ШП. Код операций определяется сигналом н выходе триггера 81 и соответствует вводу информации в МОП. Сигналы с выхода триггеров 73 и 8 поступают на вход регистра 63. Запро и код операции с выхода регистра 63, адрес с выхода коммутатора 52 и информация с выхода коммутатора 50 поступают через первый выход второго блока 44 пары на вход регистра 19 и блока 6. С выхода регистра 19 информ ция поступает через регистры 11, 31 и 17 во вторую область оперативной памяти. Установившийся таким образом процесс передачи информации между двумя областями МОП происходит до тех пор, пока не будет передан весь заданньй массив информации, после чего на выходе триггера 77 каждого канала формируется сигнал Останов поступающий на входы триггера 78 и узла 55. На выходе узла 55 устанавливается сигнал Фаза окончания (ФАЗОК), а на выходе триггера 78 формируется сигнал Прием дескриптора результата (ПРДР), который поступает на управляющие входы коммутатора 49 и буферной памяти 48 для приема информации с выхода регистра 60 и счетчиков 68 и 69. По сигналам управления, сформированным в узле 54, блок 1 формирует сигнал обращения в МОП по записи содержимого блока 3 в область МОП, занимаемую картой работ, завершая таким образом работу по передаче информации между двумя областями МОП. Введение новых узлов позволяет сократить в два раза затраты времени на передачу единицы информации по сравнению с адаптером канал-канал, так как передача информации межДУ двумя блоками обмена сводится фактически к передаче между регистрами буферной памяти и требует одного машинного такта ( единицу информации (вместо в адаптере). Отсутствие в предлагаемом изобретении внешних связей между блоками обмена по линиям интерфейсов повыпает надежность процессора и дополнительно сокращает внешнее оборудование. Возможность программной коммутации пар блоков обмена позволяет оперативно производить обмен как с внешними устройствами, так и между областями оперативной памяти, что повышает общую производительность вычислительного комплекса. Кроме того, введение новых узлов позволяет производить автономную откладку процессора ввода-вывода без участия внешних устройств (режим Тест), что повышает эксплуатационные характеристики процессора и значительно облегчает его откладку в процессе производства. От ЦП

От fffff

KMOff

Фип

26

18

24

/J

Фиг.3

Фиг 4

у

Чу,

т

Ч

64

/ / V /

7

V/V /

LfJ t

Фг1г.7

8f

I / г ч7

V7 г;

t

1

7

Фиг.В

сж

Н 6HeiUf uff I ycfrfpoucmBifff

4

т

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Процессор ввода-вывода | 1980 |

|

SU934465A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-07—Публикация

1983-07-29—Подача