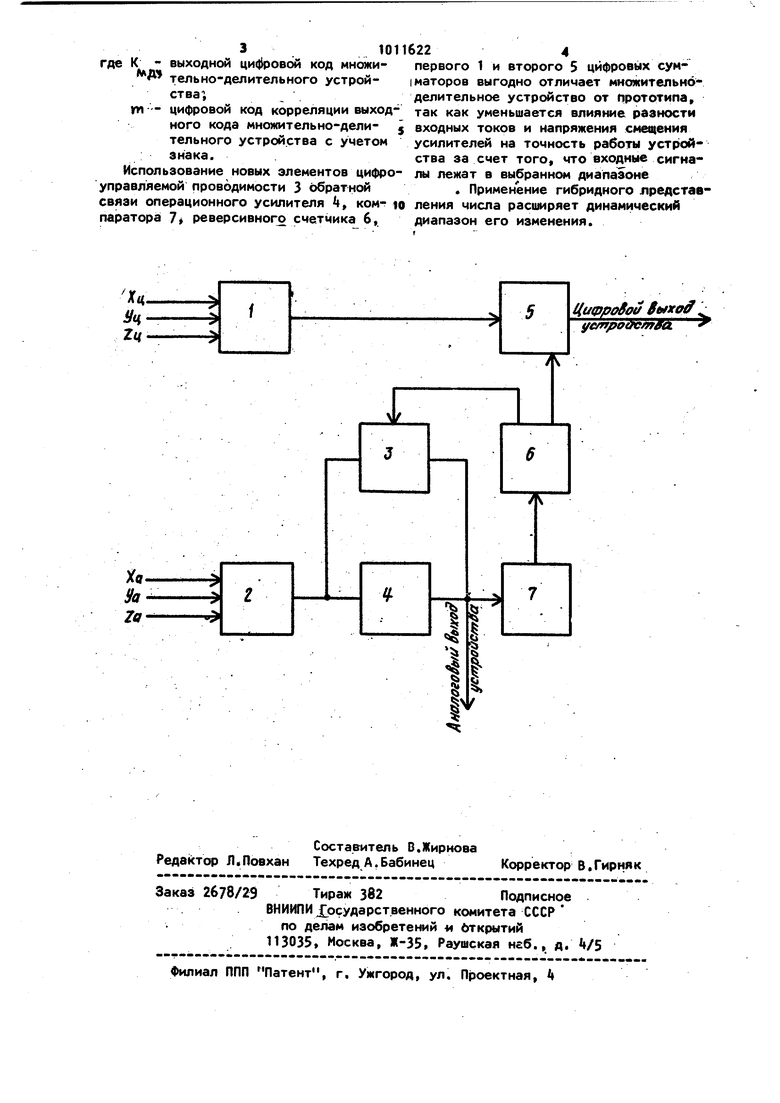

Изобретение относится к аналоговой и гибридной вычислительной технике. Известны устройства для перемножег ния - деления аналоговых величин, со держащие множительно-делительные блок и операционные усилители 1.. Эти устройства характеризуются недостаточновысокой точностью, Наиболее близким техническим решением к изобретению является множительно-делительное устройство, содержащее входной множительно-делительный блок с токовым выходом и операционный усилитель t 2. Известное устройство характеризует ся недостаточно высокой точностью и узким диапазоном изменения переменных Целью изобретения является повышение точности работы устройства и расширение динамического диапазона изменения переменных за счет представления их в гибридной цифро-аналоговой форме, : Поставленная цель достигается тем, что в множительно-делительное устройство, содержащее множительно-делитель ный блок с токовым выходом, входы которого являются аналоговыми входами усройства, а выход соединен со вхо дом операционного усилителя, выход ко торого является аналоговым выходом устройства, дополнительно введены циф роуправляемая проводимость, компара-; тор, реверсивный счетчик и два цифровых сумматора, причем входы первого из.цифровых сумматоров являются цифровыми входами устройства, а выход подключен к первому входу второго циф рового сумматора, выход которого является цифровым выходом устройства, а второй вход второго цифрового сумматора соединен с первым выходом реверсивного счетчика, подключенного вторым выходом к управляющему входу цифроуправляемой проводимости, подключен ной между выходом и входом операционного усилителя, выход компаратора соединен со входом реверсивного счетчика, а выход операционного усилй теля подключен к входу компаратора. На чертеже приведена структурная схема множительно-делительного устройства. Устройство содержит первый цифровой сумматор 1j множительно-дёлительный блок 2 с токовым выходом, цифроуправляемую проводимость 3, операционный усилитель t, второй цифровой сумматор 3, реверсивный счетчик б и компаратор 7. Входным величинам ставится в соответствие произведение .где XQ - аналоговая часть входной величины X, которая изменяется в пределах и - максимально допустимое напряжение для представления аналоговой .части, К - основание; Х, - цифровая часть входной величины X, Выходной ток входного множительноделительного блока 2 описывается; выражением -, .V. где ty - ток, пропорциональный входной величине X, 1„ - ток, пропорциональный входной величине , 1 - ток, пропорциональный входной величине Z, Сигнал с выхода операционного усилителя подается на вход компаратора 7. В случае, если выходное напряжение операционного усилителя не лежит в выбранном диапазоне ,уц}(; , компаратор вырабатывает сигнал, , под действием которого изменяется выходное состояние реверсивного сметчика 6, который, управляя цифроуправляемой проводимостью 3 в обратной связи операционного усилителя , возвращает выходной сигнал операционного усилителя в выбранный диапазон. Одновременно со второго выхода реверсивного счетчика 6 на первый вход второго цифрового сумматора 5 поступает код коррекции порядка выходного числа. На выходе первого цифрового сумматора 1 вырабатывается код в соответствии с математическим выражением Этот код поступает на второй вход второго цифрового сумматора 5 Коорый на выходе вырабатывает цифровой код в соответствии с выражением - Z -VVii,

310116224

где К. - выходной ци(|1ровс)й код множи- первого 1 и второго 5 цифровых сум тельно-делительного устрой- |маторов выгодно отличает множительноства;делительное устройство от прототипа

гп - цифровой код корреляции выход- так как уменьшается влияние разности ного кода множительно-дели- j входных токов и напряжения смещения тельного устройства с учетом усилителей на точность работы устройзнака.ства за счет того, что входные сигнаИспользование новых элементов цифро- лы лежат в выбранном диапазоне управляемой проводимости 3 обратной . Применение гибридного лредстав связи операционного усилителя k ком- to ления числа расимряет динамический паратора 7 реверсивного счетчика 6, диапазон его изменения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое множительное устройство | 1980 |

|

SU883930A1 |

| Множительно-делительное устройство | 1980 |

|

SU949662A1 |

| Цифроуправляемый резистор | 1987 |

|

SU1443006A1 |

| Дробно-рациональный цифроаналоговый преобразователь | 1980 |

|

SU896646A1 |

| Аналого-цифровое делительное устройство | 1979 |

|

SU886017A1 |

| Устройство автоматической смены масштабов для аналоговой вычислительной машины | 1983 |

|

SU1113809A1 |

| Датчик сил упругой деформации механизма и устройство для его настройки | 1985 |

|

SU1288511A1 |

| Интегратор | 1981 |

|

SU1081643A2 |

| Цифро-аналоговый множительно- ТРигОНОМЕТРичЕСКий пРЕОбРАзОВАТЕль | 1978 |

|

SU822223A1 |

| Аналого-цифровая вычислительная система | 1985 |

|

SU1320821A1 |

МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее множитёльно-делительный блок с токовым выходом, входы которого являются аналоговыми входакм устройства, а выход соединен со входом операционного усилителя,Шход которого является аналоговый выходом устройства, о т л и ч а ю щ е е с я TGMi 4TOi с целью повышения точностиработы устройства и расширения динамического диапазона изменения переменных за счет представления их в гибри : ной аналого-цифровой форме, е него введены цифроуправляемая проводикюсть, компаратор, реверсивный счетчик и два цифровых сумматора, причем входы пёр вого из цифровых сумматоров являются цифровыми .входами устройства., а выход подключён к первому входу второго «ифрового сумматора, выход которого является цифровым выходом ycTpoJicTBa, а второй вход второго цифрового сумйа тора соединен с первым выходом рев сивного счетчика, подключенного вто рым выходом к управляющему входу 1|(ф роуправляемой проводимости, подклпченной между выходом и входсм4 операционного усилителя, выход компаратера соединен со входом реверсивного счетчика, а выход операционного yqiлителя подключен к вход компа| атора. - -.- . - :.

Хц.

Ч2ц

Ха. Уа19

Цифровой ibixt,

ytyrrpoac/nga

LI

1

Ч

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Применение прецизионных аналоговых И.С | |||

| Н,, Радио и 1981, с, 92-10 | |||

| связь, 2 | |||

| Патент США Г , ai, 235г195,опублик | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1983-04-15—Публикация

1981-12-10—Подача