ческой смены масштабов суммирования и интегрирования, усилители 6 с управляемым коэффициентом усиления, блоки 7 переключения емкости, управляемые источники 9 опорного напряжения, шины ввода кодов и адресов порядков и мантисс, шины вывода номеров и адресов подобластей. Работа системы основана на ступенчатой ре- 1гулировке коэффициентов передачи

1

Изобретение относится к автоматике и вычислительной технике, в частности к аналого-цифровым вычислительным системам (АЦВС).

Цель изобретения - повышение точности решения векторно-матричного уравнения X АХ + В с большими значениями элементов матрицы А и вектора-столбца В и расширение диапазона изменения переменных.

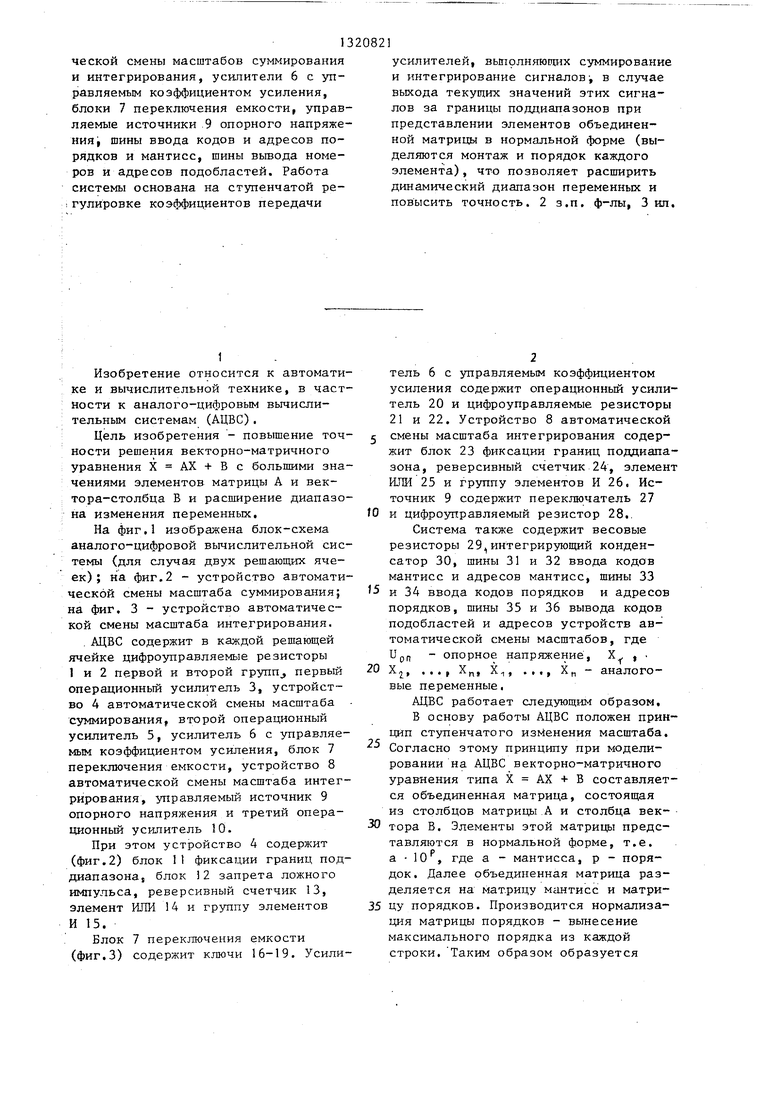

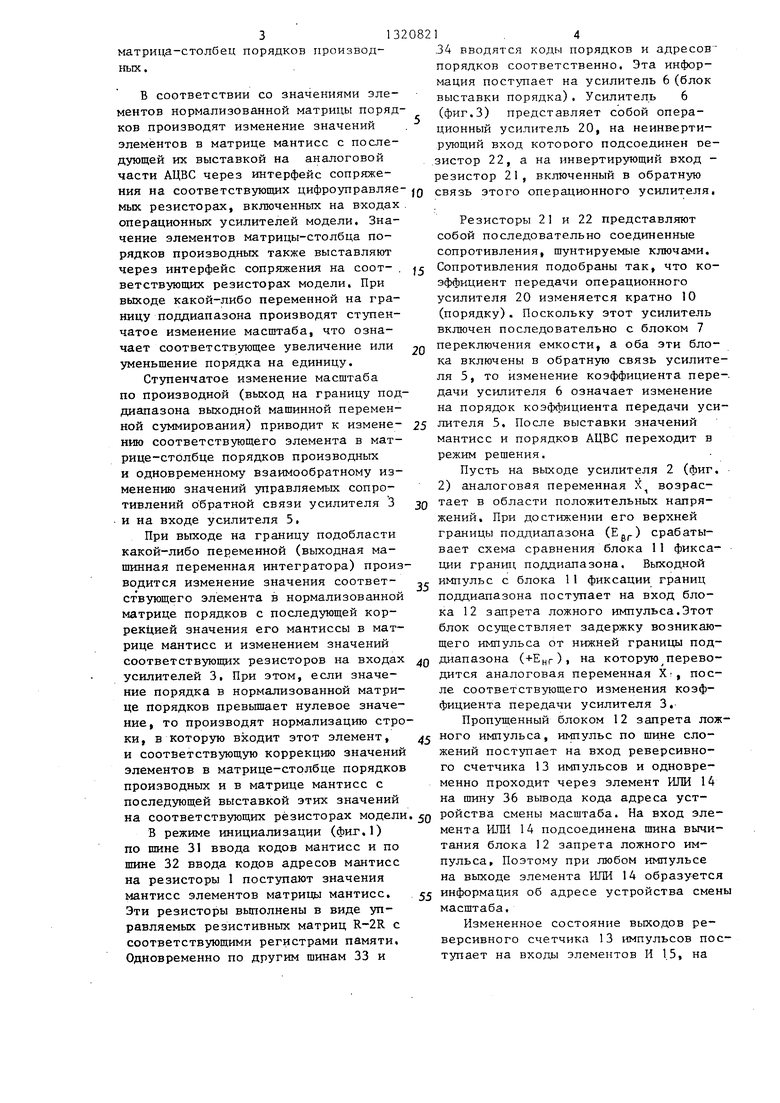

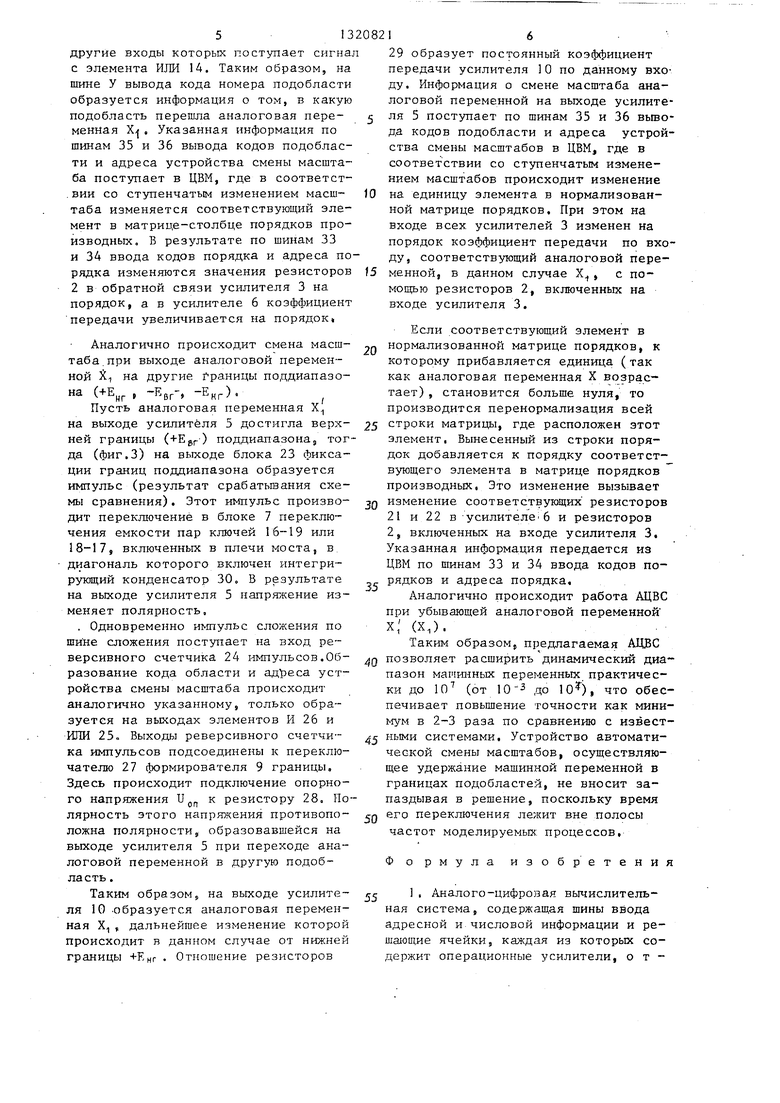

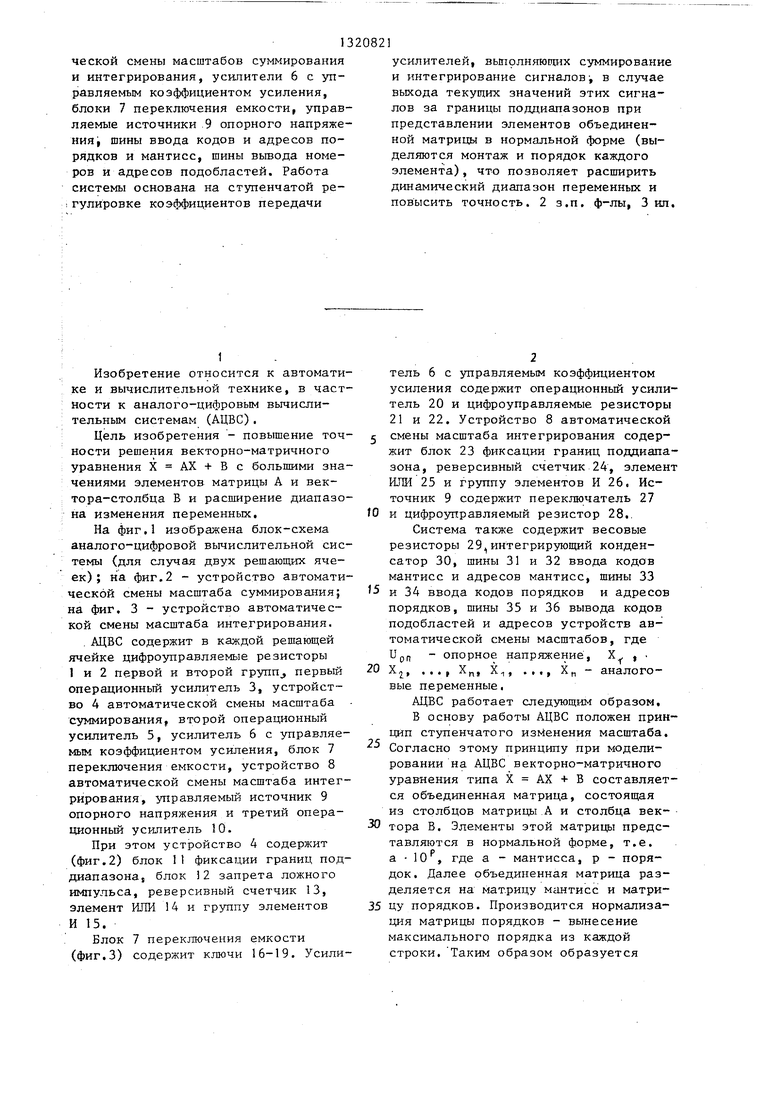

На фиг.1 изображена блок-схема аналого-цифровой вычислительной системы (для случая двух решающих ячеек) ; на фиг.2 - устройство автоматической смены масштаба суммирования; на фиг, 3 - устройство автоматической смены масштаба интегрирования. . АЦВС содержит в каждой решающей ячейке цифроуправляемые резисторы 1 и 2 первой и второй групп, первый операционный усилитель 3, устройство 4 автоматической смены масштаба суммирования, второй операционный усилитель 5, усилитель 6 с управляемым коэффициентом усиления, блок 7 переключения емкости, устройство 8 автоматической смены масштаба интегрирования, управляемый источник 9 опорного напряжения и третий операционный усилитель 10.

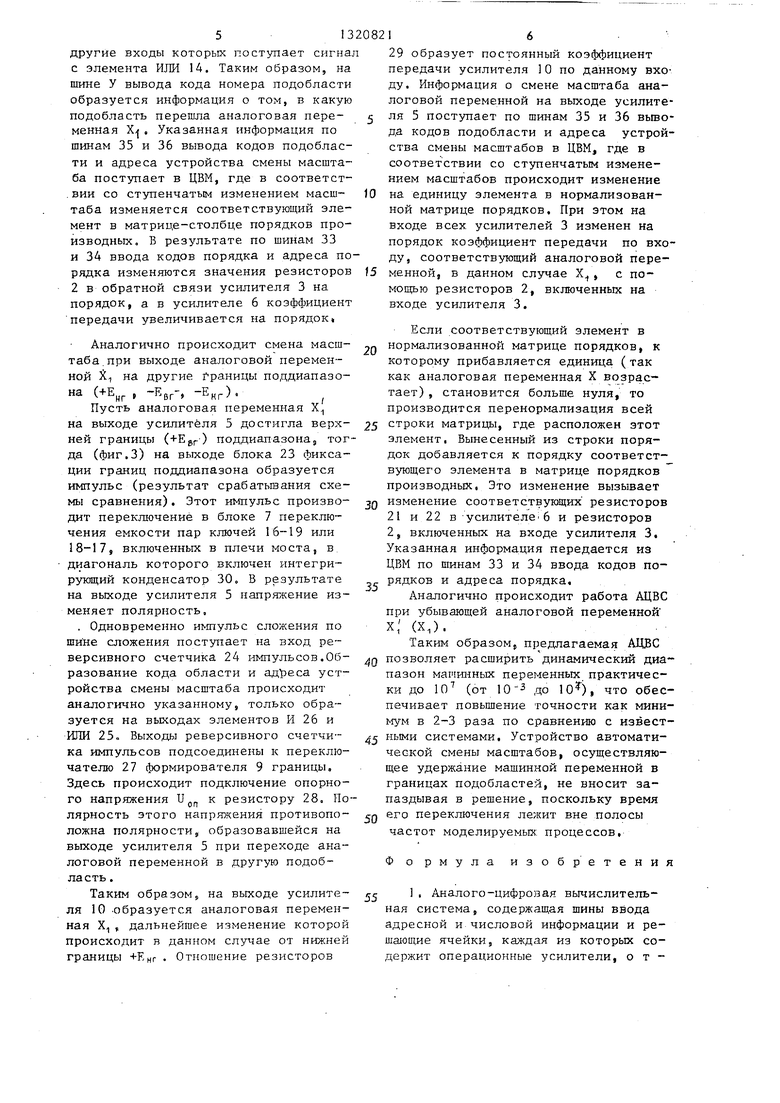

При этом устройство 4 содержит (фиг.2) блок 11 фиксации границ поддиапазона, блок 2 запрета ложного импульса, реверсивный счетчик 13, элемент ИЛИ 14 и группу элементов И 15.

Блок 7 переключения емкости (фиг.З) содержит ключи 16-19. Усилиусилителей, выполняющих суммирование и интегрирование сигналовj в случае выхода текущих значений этих сигналов за границы поддиапазонов при представлении элементов объединенной матрицы в нормальной форме (выделяются монтаж и порядок каждого элемента), что позволяет расширить динамический диапазон переменных и повысить точность. 2 з.п. ф-лы. Зил.

тель 6 с управляемым коэффициентом усиления содержит операционный усилитель 20 и цифроуправляемые резисторы 21 и 22. Устройство 8 автоматической

смены масштаба интегрирования содержит блок 23 фиксации границ поддиапазона, реверсивный счетчик 24, элемент ИЛИ 25 и группу элементов И 26. Источник 9 содержит переключатель 27

и цифроуправляемый резистор 28..

Система также содержит весовые резисторы 29,интегрирующий конденсатор 30, шины 31 и 32 ввода кодов мантисс и адресов мантисс, шины 33

и 34 ввода кодов порядков и адресов порядков, шины 35 и 36 вывода кодов подобластей и адресов устройств автоматической смены масштабов, где

и

рп опорное напряжение.

X

1-

Xj, ..., Х„, Х, ..., Х„ - аналоговые переменные,

АЦВС работает следующим образом. В основу работы АЦВС положен принцип ступенчатого изменения масштаба.

Согласно этому принципу при моделировании на АЦВС векторно-матричного уравнения типа X АХ + В составляется объединенная матрица, состоящая из столбцов матрицы А и столбца вектора В. Элементы этой матрицы представляются в нормальной форме, т.е. а Ю , где а - мантисса, р - порядок . Далее объединенная матрица разделяется на матрицу мантисс и матрицу порядков. Производится нормализация матрицы порядков - вынесение максимального порядка из каждой строки. Таким образом образуется

313

матрица-столбец порядков производных.

В соответствии со значениями элементов нормализованной матрицы порядков производят изменение значений элементов в матрице мантисс с последующей их выставкой на аналоговой части АЦВС через интерфейс сопряжения на соответствующих цифроуправляе мых резисторах, включенньтх на входах операционных усилителей модели. Значение элементов матрицы-столбца порядков производных также выставляют через интерфейс сопряжения на соот- . ветствующих резисторах модели. При выходе какой-либо переменной на границу поддиапазона производят ступенчатое изменение масштаба, что означает соответствующее увеличение или уменьшение порядка на единицу.

Ступенчатое изменение масштаба по производной (выход на границу поддиапазона выходной машинной переменной суммирования) приводит к измене- нию соответствующего элемента в матрице-столбце порядков производных и одновременному взаимообратному изменению значений управляемых сопротивлений обратной связи усилителя 3 и на входе усилителя 5.

При выходе на границу подобласти какой-либо переменной (выходная машинная переменная интегратора) производится изменение значения соответ- ствующего элемента в нормализованной матрице порядков с последующей коррекцией значения его мантиссы в матрице мантисс и изменением значений соответствующих резисторов на входах усилителей 3. При этом, если значение порядка в нормализованной матрице порядков превышает нулевое значение, то производят нормализацию строки, в которую входит этот элемент, и соответствующ5пю коррекцию значений элементов в матрице-столбце порядков производных и в матрице мантисс с последующей выставкой этих значений на соответствующих резисторах модели

В режиме инициализации (фиг,1) по шине 31 ввода кодов мантисс и по щине 32 ввода кодов адресов мантисс на резисторы 1 поступают значения мантисс элементов матрицы мантисс. Эти резисторы выполнены в виде управляемых резистивных матриц R-2R с соответствующими регистрами памяти. Одновременно по другим шинам 33 и

.34 вводятся коды порядков и адресов порядков соответственно. Эта информация поступает на усилитель 6(блок выставки порядка), Усилитель 6 (фиг.З) представляет собой операционный усилитель 20, на неинвертирующий вход которого подсоединен ое- зистор 22, а на инвертирующий вход - резистор 21, включенный в обратную связь этого операционного усилителя.

Резисторы 21 и 22 представляют собой последовательно соединенные сопротивления, шунтируемые ключами. Сопротивления подобраны так, что коэффициент передачи операционного усилителя 20 изменяется кратно 10 (порядку). Поскольку этот усилитель включен последовательно с блоком 7 переключения емкости, а оба эти блока включены в обратную связь усилителя 5, то изменение коэффициента пере дачи усилителя 6 означает изменение на порядок коэффициента передачи усилителя 5. После выставки значений мантисс и порядков АЦВС переходит в режим решения.

Пусть на выходе усилителя 2 (фиг. 2) аналоговая переменная Х возрастает в области положительных напряжений. При достижении его верхней границы поддиапазона (Е.,-) срабатывает схема сравнения блока 11 фиксации гранш; поддиапазона. Выходной импульс с блока 11 фиксации границ поддиапазона поступает на вход блока 12 запрета ложного импульса,Этот блок осуществляет задержку возникающего импульса от нижней границы поддиапазона (+Ецг)« на которую переводится аналоговая переменная Хг, после соответствующего изменения коэффициента передачи усилителя 3,Пропущенный блоком 12 запрета ложного импульса, импульс по шине сложений поступает на вход реверсивного счетчика 13 импульсов и одновременно проходит через элемент ИЛИ 14 на шину 36 вьгоода кода адреса устройства смены масштаба. На вход элемента ИЛИ 14 подсоединена шина вычитания блока 12 запрета ложного импульса. Поэтому при любом импульсе на выходе элемента ИЛИ 14 образуется информация об адресе устройства смен масштаба.

Измененное состояние выходов реверсивного счетчика 13 импульсов поступает на входы элементов И 15, на

5132

другие входы которых поступает сигнал с элемента ИЛИ 14. Таким образом, на шине У вывода кода номера подобласти образуется информация о том, в какую подобласть перешла аналоговая пере- манная Х. Указанная информация по шинам 35 и 36 вывода кодов подобласти и адреса устройства смены масштаба поступает в ЦВМ, где в соответст.ВИИ со ступенчатьм изменением масш- таба изменяется соответствующий элемент в матрице-столбце порядков производных « В результате по шинам 33 и 34 ввода кодов порядка и адреса порядка изменяются значения резисторов 2 в обратной связи усилителя 3 на порядок, а в усилителе 6 коэффициент

передачи увеличивается на порядок

Аналогично происходит смена масш

таба,при выходе аналоговой переменной 1 на другие драницы поддиапазона (+Е , -ЕВГ-, -ЕНГ)«

Пусть аналоговая переменная Х на выходе усилителя 5 достигла верх- ней границы (+Egr-) поддиапазона, тогда (фиг.З) на выходе блока 23 фиксации границ поддиапазона образуется импульс (результат срабатьшания схемы сравнения). Этот импульс произво- дит переключение в блоке 7 переключения емкости пар ключей 16-19 или 18-17, включенных в плечи моста, в. диагональ которого включен интегрирующий конденсатор 30. В результате на выходе усилителя 5 напряжение изменяет полярность,

. Одновременно импульс сложения по шине сложения поступает на вход реверсивного счетчика 24 импульсов.Об- разование кода области и адТреса устройства смены масштаба происходит аналогично указанному, только образуется на выходах элементов И 26 я ИЛИ 25п Выходы реверсивного счетчи- ка импульсов подсоединены к переключателю 27 формирователя 9 границы, Здесь происходит подключение опорного напряжения U к резистору 28. Полярность этого напряжения противопо- ложна полярности, образовавшейся на выходе усилителя 5 при переходе аналоговой переменной в другую подобласть .

Таким образом, на выходе усилите- ля 10 .образуется аналоговая переменная X,, дальнейшее изменение которой происходит в данном случае от нижней границы +ЕЦГ Отношение резисторов

5

0

5 д

Q д

16

29 образует постоянный коэффициент передачи усилителя 10 по данному входу. Информация о смене масштаба аналоговой переменной на выходе усилителя 5 поступает по шинам 35 и 36 вьшо- да кодов подобласти и адреса устройства смены масштабов в ЦВМ, где в соответствии со ступенчатым изменением масштабов происходит изменение на единицу элемента в нормализованной матрице порядков. При этом на входе всех усилителей 3 изменен на порядок коэффициент передачи по входу, соответствующий аналоговой переменной, в данном случае Х, с по- мош;ью резисторов 2, включенных на входе усилителя 3,

Если соответствующий элемент в нормализованной матрице порядков, к которому прибавляется единица (так как аналоговая переменная X возрастает) , становится больше нуля, то производится перенормализация всей строки матрицы, где расположен этот элемент. Вынесенный из строки порядок добавляется к порядку соответствующего элемента в матрице порядков производньк. Это изменение вызывает изменение соответствующих резисторов 21 и 22 в-усилителе 6 и резисторов 2, включенных на входе усилителя 3, Указанная информация передается из ЦВМ по шинам 33 и 34 ввода кодов порядков и адреса порядка.

Аналогично происходит работа АЦВС при убывающей аналоговой переменной

х; (X,).

Таким образом, предлагаемая АЦВС позволяет расширить динамический диапазон ма1чинных переменных практически до 10 (от до 10), что обеспечивает повьшение точности как минимум в 2-3 раза по сравнению с известными системами. Устройство автоматической смены масштабов, осуществляющее удержание машинной переменной в границах подобластей, не вносит запаздывая в решение, поскольку время его переключения лежит вне полосы частот моделируемых, процессов.

Формула изобретения

1. Аналого-цифровая вычислительная система, содержащая шины ввода адресной и числовой информации и решающие ячейки, каждая из которых содержит операционные усилители, о т 7132

личаюп1аяся тем, что, с целью повышения точности решения век- торно-матричного уравнения X АХ +В с большими значениями элементов матрицы А и вектора-столбца В и расши- рения диапазона изменения переменных, в каждую решающую ячейку введены первая и вторая группы из (п+1)-го циф- роуправляемых резисторов (где п - количество переменных), устройство автоматической смены масштаба суммирования, устройство автоматической сМены масштаба интегрирования усилитель с управляемым коэффициентом уси

20

25

30

ения, блок переключения емкости, 15 правляемый источник опорного напряжения и два. весовых резистора,прием каждый из п цифроуправляемых езисторов первой группы подключен ервьад выводом к соответствующему сигнальному входу решающей ячейки, а вторым выводом - к первому выводу соответствующего цифроуправляемого резистора второй группы, соединенного вторым выводом с входом первого операционного усиления и первым вьшо- дом (п+1)-го цифроуправляемого резистора второй группы, второй вывод которого подключен к выходу первого . операционного усиления, входу устройства автоматической смены масштаба суммирования и первому вьтоду (п+1)-го цифроуправляемого резистора первой группы, соединенного вторым вьщодом с входом второго операционного усиления и выходом блока переключения емкости, сигнальный вход которого подключен к выходу усиления с управляющим коэффициентом усиления,- соединенного сигнальным входом с выходом второго операционного усилителя, первым вьшодом первого весового резистора и сигнальным входом устройства автоматической смены масштаба интегрирования, подключенного 45 первым и вторым выходами к управляющим входам блока переключения емкости, а третьим., четвертым и пятым выходами - к входам управления знаком и стробирующему входу управляемого 50

источника опорного напряжения,, соединенного выходом с вторым выводом первого весового резистора, входом третьего операционного усилителя и первым выводом второго весового резистора, второй йывод которого подключен к выходу третьего операционного усилителя и сигнальному выходу

40

35

55

0

0

5

5

решающей ячейки, при этом управляющие и стробирующие входы Цифроуправляемых резисторов первых групп решающих ячеек соединены с шиной вво- :Да кодов мантиссы и шиной ввода адресов мантиссы соответственно,управ-- ляющие и стробирующие входы цифроуправляемых резисторов вторых групп и блоков выставки порядка решающих ячеек подключены к шине ввода кодов порядка и шине ввода адресов порядка соответственно, информационные выходы устройств автоматической смены масштаба суммирования и устройств автоматической смены масштаба интегрирования соединены с шиной вьшодако- дов номера подобласти, инициирующие выходы устройств автоматической смены масштаба суммирования и устройств автоматической смены масштаба интегрирования подключены к шине вывода адреса устройства автоматической смены масштаба, а сигнальные входы и сигнальные выходы решающих ячеек соединены между собой согласно топологии решаемой задачи.

2, Система по п.1, о т л и ч а ю- щ а я с я тем, что каждое устройство автоматической смены масштаба суммирования содержит блок фиксации границ поддиапазона, блок запуска ложного импульса, реверсивный счетчик, элемент ИЛИ и группу элементов И,сое- диненных выходами с информационными выходами устройства автоматической смены масштаба суммирования, первыми входами - с выходами разрядов реверсивного счетчика, а вторыми входами - с инициирующим выходом устройства автоматической смены масштаба суммирования и выходом элемента ИЛИ, подключенного первым входом к первому выходу блока запрета ложного импульса и с мирующему входу реверсивного счетчика, а вторым входом - к второму выходу блока запрета ложного импульса н вычитающему входу реверсивного счетчика, соединенного выходом обнуления с управляю- входом блока запрета ложного импульса, подключенного информационными входами к импульстшм выходам достижения миниму а и максимума блока фиксации границ поддиапазона, вход которого соединен с входом устройства автоматической смены масштаба суммирования.

3. Система по п,1,отличаю- щ а я с я тем, что каждое устройство автоматической смены масштаба интегрирования содержит блок фиксации границ поддиапазона, реверсивный счетчик, элемент ИЛИ и группу элементов И, соединенньк выходами с информационными выходами устройства автоматической смены масштаба интегрирования, первыми входами - с выходами разрядов реверсивного счетчика, а вторыми входами с инициирующим выходом устройства автоматической смены масштаба интегрирования и выходом элемента ИЛИ, подключенного первым входом к суммирующему входу реверсивного счетчика и импульсному выходу

20821

10

достижения максимума блока фиксации границ поддиапазона, соединенного входом с сигнальным входом устройства автоматической смены масштаба ин- г тегрирования, потенциальными выходами достижения максимума и минимума - с первым и вторым выходами устройства автоматической смены масштаба интегрирования, а импульсным выходом

JO достижения минимума - с вторьм входом элемента ИЛИ и вычитающим входом реверсивного счетчика, подключенного прямым и инверсным выходами знака и выходом обнуления - к третьему, четf5 вертому и пятому выходам устройства автоматической смены масштаба интегрирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая вычислительная система | 1986 |

|

SU1420605A1 |

| Устройство автоматической смены масштабов для аналоговой вычислительной машины | 1983 |

|

SU1113809A1 |

| Устройство для автоматической смены масштабов в аналоговой вычислительной машине | 1983 |

|

SU1080153A1 |

| Устройство для автоматической смены масштабов в аналоговой вычислительной машине | 1982 |

|

SU1080154A1 |

| Устройство для автоматической сменыМАСшТАбОВ B АНАлОгОВОй ВычиСлиТЕль-НОй МАшиНЕ | 1978 |

|

SU815729A1 |

| Устройство для изменения масштабов в аналоговых вычислительных машинах | 1983 |

|

SU1195361A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Интегратор | 1986 |

|

SU1401485A2 |

| Автоматический цифровой измеритель сопротивления | 1988 |

|

SU1624350A1 |

Изобретение относится к области автоматики и вычислительной техники. Цель изобретения - повьшение точности решения векторно-матричного уравнения X АХ + В с большими значения- ми элементов матрицы А и вектора - столбца В и расширение диапазона изменения переменных. Аналого-цифровая вычислительная система содержит циф- роуправляемые резисторы 1 и 2 первых и вторых групп, операционные усилители 3,5,10, устройства 4,8 автомати(Л щ 3132 W Jf JJJ ф1/«./

Л, 03 32

Фие.2

.Л/

LIlM

JJ

Фat.3

Редактор И.Касарда

Составитель С.Казинов Техред Н.Глущенко

Заказ 2660/52 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб. , д.4/5

,иввв-в.---«.ее -- - -

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор С.Шекмар

| Устройство для решения системОдНОРОдНыХ диффЕРЕНциАльНыХуРАВНЕНий | 1979 |

|

SU801005A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Силаев Е.В | |||

| и др | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Харьковский политехнический институт, Харьков, 1983 | |||

| Рукопись депонирована в УкрНИНТИ, № 640-УП-Д83 | |||

| Деп | |||

| Солесос | 1922 |

|

SU29A1 |

| iLtl | |||

Авторы

Даты

1987-06-30—Публикация

1985-04-02—Подача