tsd

N9

ОС

2.-Устройство по п. 1, о т л ичающееся тем, что блок управления длительностью синхросигналов содержит L элементов И, два элемента ИЛИ, два триггера, причем выход первого элемента ИЛИ является выходом блока, (L+l)-n вход которого соединен с первыми входами элементов и, с первым входом первого элемента ИЛИ, второй вход которого соединен с прямым выходом первого триггера, инверсный выход которого соединен с информационным входом второго триггера, прямой выход которого соединен с информационным входом первого триггера, синхровход которого соединен с инверсным выходом второго элемента ИЛИ, прямой выход которого соединен с синхровходом второго триггера , входы второго элемента ИЛИ соединены соответственно с выходами элементов И, вторые входы которых являются входами с (L+2)-ro по (2L+l)-й блока, ВХОДЫ с первого по L-й которого соединены соответственг но с третьими входами элементов И.

3. Устройство по п. 1, о т л ичающееся тем, что блок выработки синхросигналов содержит регист сдвига, многовходовой элемент и, причем i-и разряд (где f 1, 2, ... L) регистра сдвига содержит четыре элемента И, два элемента НЕ, два триггера, причем выходы первого и второго элементов И i-го разряда регистра сдвига соединены соответственно о единичным и нулевым входами первого триггера разряда регистра сдвига, выходы третьего и четвертого элементов И i-ro разряда регистра сдвига соединены соответственно с единичным и нулевым входами второго триггера i-ro разряда регистра сдвига, выход первого триггера

(i-t-l)-ro разряда регистра сдвига соединен с первым, входом третьего элемента И {1+1)-го разряда регистра сдвига и является )-м выходом блока, второй вход третьего элемента и i-ro разряда регистра сдвига соединен с выходом первого элемента НЕ i-ro разряда регистра сдвига, выход второго элемента НЕ i-ro разряда регистра сдвига соединен с первым входом четвертого элемента И i-ro разряда регистра сдвига, прямые выходы вторых триггеров разрядов с первого по (1-1)-й регистра сдвига соединены с первыми входами вторых элементов И соответствующих разрядов регистра сдвига и с первыми входами первых элементов И последующих разрядов регистра сдвига соответственно прямой выход первого триггера первого разряда регистра сдвига соединен с вторым входом третьего элемента И первого разряда регистра сдвига, с вторым входом четвертого элемента И L-ro разряда регистра сдвига и является первым выходом блока, инверсные выходы первых триггеров i-х разрядов регистра сдвига соединены соответственно с входами многовходового элемента И, выход которого соединен с первым входом первого элемента И первого разряда регистра сдвига,. прямой выход второго триггера L-ro разряда регистра сдвига соединен с первым входом второго элемета И L-ro разряда, регистра сдвига, тактовый вход блока соединен с вторыми входами первого и второго элементов И i-ro разряда регистра сдбига, с входами первого и второго элементов НЕ i-ro разряда регистра сдвига, управляющий вход блока соединен с., третьим входом первого элемента И первого разряда регистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации с контролем | 1983 |

|

SU1161933A1 |

| Устройство для синхронизации каналов | 1985 |

|

SU1262471A1 |

| Мультимикропрограммное устройство управления | 1983 |

|

SU1161942A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1164706A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Устройство для поиска перемежающихся неисправностей | 1986 |

|

SU1381511A1 |

| Устройство для сопряжения группы каналов ЭВМ с группой периферийных устройств | 1987 |

|

SU1520529A1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1221648A1 |

| Устройство для формирования входных воздействий в системе программного контроля | 1980 |

|

SU920729A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

1. УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ, содержащее задающий гейератор, n элементов задержки (где n - число каналов), n блоков выработки синхросигналов, причем выход задающего генератора соединен с входами элементов задержки, управляющие входы блоков выработки синхросигналов соединены с входом запуска устройства, выходы блоков выработки синхросигналов являются выходами устройства, о тличающееся тем, что с целью увеличения функциональных возможностей путем обеспечения переменного периода, в устройство введен дешифратор, n блоков управления длительностью синхросигналов, выходы которых соединены соответственно с-тактовыми входами блоков выработки синхросигналов, выходы дешифратора с первого по L-й (где L -.число импульсов в такте) соединены соответственно с входами с первого по L-ft блоков управления длительностью синхросигналов, (i + 1)-е входыкотоо « рых соединены соответственно с выходами элементов задержки, выходы блоков выработки синхросигналов соедине ны соответственно с входами с

1

Изобретение относится к вычислительной технике и предназначено- для микропрограммной ЭВМ, имеющей набор микрокоманд с различным циклом выполнения.

В ЭВМ с микропрограммным управлением команда реализуется путем выполнения последовательности микрокоманд. Время, необходимое для выполнения одной микрокоманды, называется машинным циклом. Машинный цикл состоит из определенной последовательности управляющих сигналов, для синхронизации которых используется серия синхроимпульсов (СИ), вырабатываемых устройством синхронизации. Известно устройство синхронизации , содержащее генератор эталонной частоты формирователь Зс1дающей се.рии СИ и распределители СИ по логическим блокам. Формирователь задающей серии вырабатывает серию СИ, являющуюся исходной для нескольких рабочих серий СИ. Длительность и период следования СИ в пределах рабочих серий одинаковы для всех серий и определяются задающей серией СИ Ц

Устройство непригодно для синхронизации быстродействующих вычислителных систем, в которых длительность СИ сравнима с. временем распростране.ния сигналов в пределах системы. поскольку в этом случае простое распределение СИ приводит к рассогласованию работы устройств системы из-за различных задержек в распределителях СИ. Устройство не дает возможности организовать динамическое изменение длительности цикла, что при наличии нескольких типов микрокоманд снижает быстродействие системы, поскольку жестко настроено на цикл самой длинной микрокоманды, Наиболее близким к предлагаемому является устройство синхронизации быстродействующей ЭВМ, которое содер жит генератор эталонной частоты, выход которого соединен с входом формирователя задающей серии СИ. Выходы формирователя Соединены с входами группы цепей задержки. Выходы цепей задержки, размноженные и настроенны с помощью линий задержек на различные длины связей, разводятся по логическим узлам ЭВМ С23. Однако данное устройство имеет ограниченные функциональные возможности, так как имеет Ьостоянный машинный цикл и все типы микрокоманд выполняются за время, равное времени выполнения самой длительной микр команды. При наличии нескольких тип микрокоманд, время выполнения которых различно (самая короткая требуе в 2 раза меньше времени, чем длинная) , использование одного машинного .цикла для всех микрокоманд приво дит к значительной потере быстродей ствия машины. . Цель изобретения - увеличение функциональных возможностей путем обеспечения переменного периода. Поставленная, цель достигается тем, что в устройство для синхрониЗсщии, содержащее задающий генерато п элементов задержки (где п - число каналов), п блоков выработки синхро сигналов, причем выход задающего генератора соединен с входами элементов задержки, управляющие входы блоков выработки синхросигналов соединены с входом запуска устройства выходы блоков выработки синхросигна лов являются выходами устройства, введен дешифратор, п блоков управле ния длительностью синхросигналов, выходы которых соединены соответственно с тактовыми входами блоков выработки синхросигналов,.выходы дешифратора с первого по L-й (где L число импульсов в такте) соединены соответственно с входами с первого по L-й блоков управления длительностью синхросигналов, (L+l)-e вход которых соединены соответственно с выходами элементов задержки, выходы блоков выработки синхросигналов соединены соответственно с входами с (L+2)-ro по (21+1)-й блоков управления длительностью синхросигнал вход дешифратора является входом кода микрокоманды устройства. Блок управления длительностью синхросигналов содержит L элементов И, два элемента ИЛИ, два триггера, причем выход первого элемента ИЛИ является выходом блока, (И-1)-й вход которого соединен с первыми входа1йи элементов И, с первым входом первого элемента ИЛИ, второй вход которого соединен с прямлм выходом первого триггера, инверсный выход которого соединен с информационным входом в:орого триггера, прямой выход которого соединен с информационным входом первого триггера, синхровход которого соединен с инверсным выходом второго элемента ИЛИ, прямой Выход которого соединен с синхровходом второго триггера, входы второго элемента ИЛИ соединены соответственно с выходами элементов И, вторые входы которых являются входами с (L+2)-ro по (21+1;-й блока, входы с первого по L-й которого соединены соответственно с третьими входами элементов И. Блок выработки синхросигналов содержит регистр сдвига, многовходовой элемент И, причем i-и раэряд (где i 1, 2, ..., L) регистра сдвига содержит четыре элемента И, два элемента НЕ, два триггера, причем выходы первого и второго элементов И 1-го разряда регистра сдвига соединены соответственно с единичным и нулевым входами первого триггера i-ro. : разряда регистра сдвига, выходы третьего и четвертого элементов И i-ro разряда регистра сдвига соединены соответственно с единичным и нулевым входами второго триггера . i-ro разряда регистра сдвига, выход первого триггера (i+l)-ro разряда регистра сдвига соединен с первым входом третьего элемента И (i+l)-ro разряда регистра сдвига и является (i+l)-M выходом блока, второй вход третьего элемента И I-го разряда регистра сдвига соединен с выходом первого элемента НЕ i-ro разряда регистра сдвига, выход второго элемента НЕ i-ro разряда регистра сдвига соединен с первым входом четвертого элемента И i-ro разряда регистра сдвига, прямые выходы вторых триггеров разрядов с первого по (L-l)-й регистра сдвига соединены с первыми входами вторых элементов И соответствующих разрядов регистра сдвига и с первыми входами первых элементов И последующих разрядов регистра сдвига соответственно, прямой выход первого триггера первого разряда регистра сдвига соединен с вторым входом третьего элемента И первого разряда регистра сдвига, с вторым входом четвертого элемента И L-ro разряда регистра сдвига и является первым

выходом блока, инверсные выходы первых триггеров i-x разрядов регист ра сдвига соединены соответственно .с входами многовходового элемента И, выход которого соединен с первым входом первого элемента И первого разряда регистра сдвига, прямой выход второго триггера L-ro разряда регистра сдвига соединен с первым входом второго элемента И L-ro разряда регистра сдвига, тактовый вход блока соединен с вторыми входами первого и второго элементов И i-rc разряда регистра сдвига, с входами: первого и второго элементов НЕ i-ro разряда регистра сдвига, управляющий вход блока соединен с третьим входом первого элемента И первого разряда регистра сдвига.

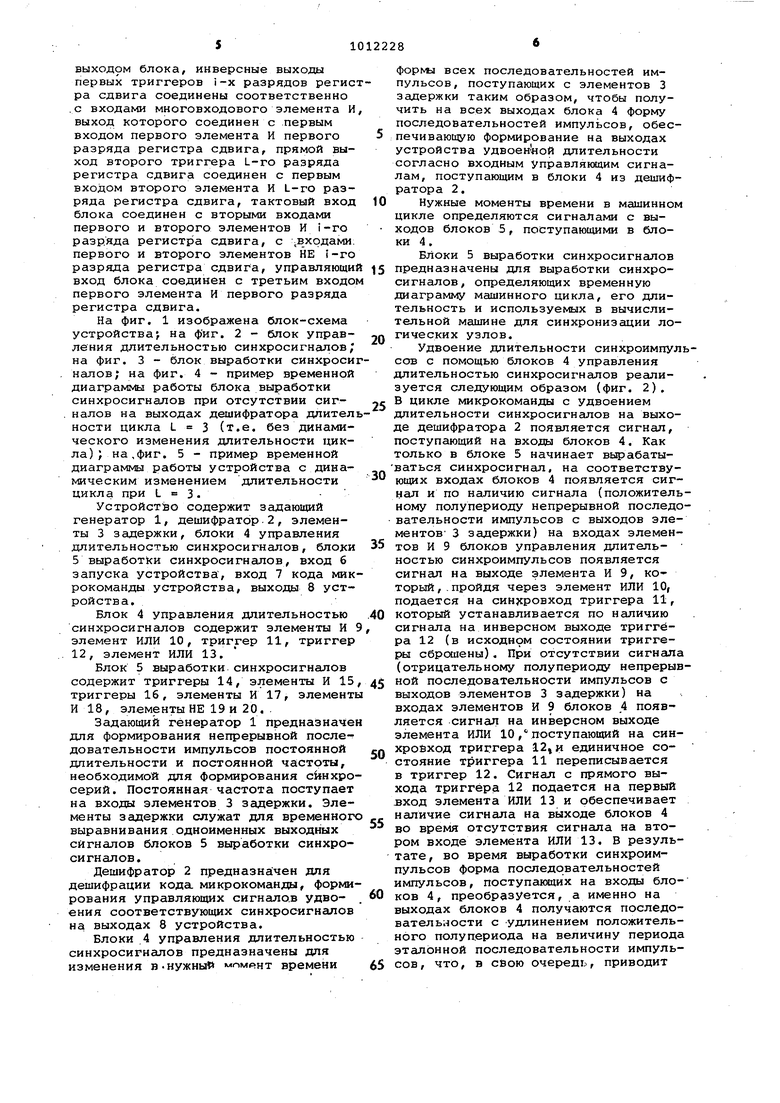

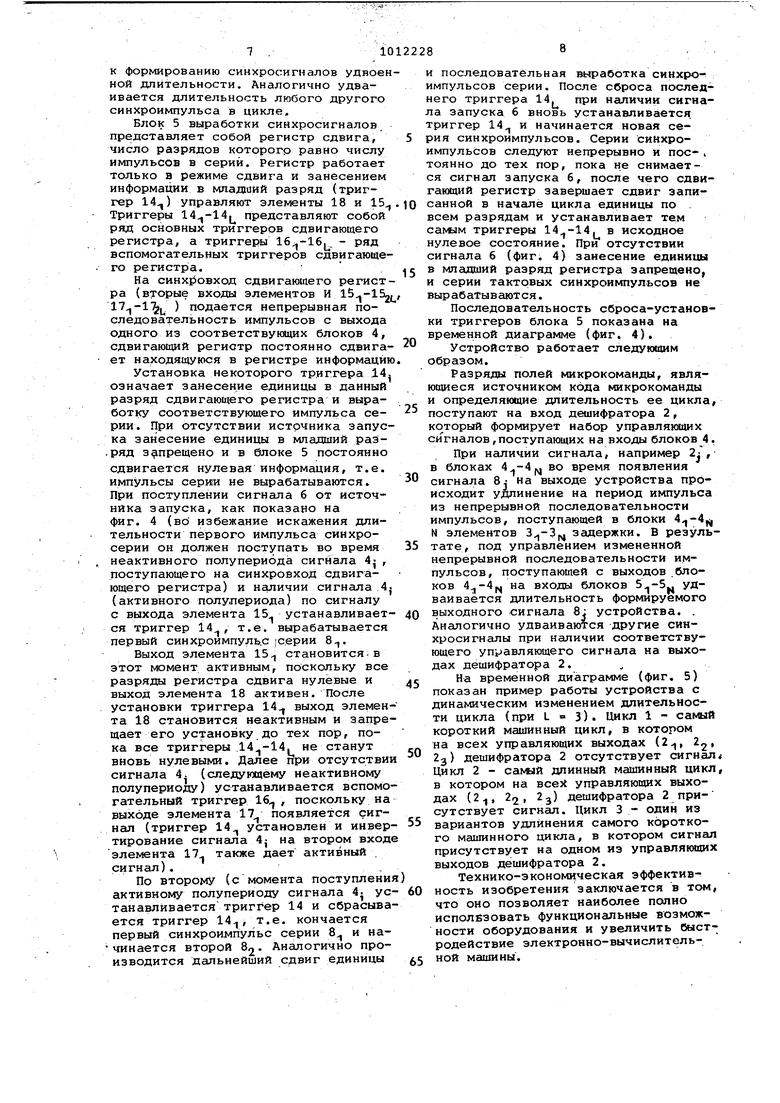

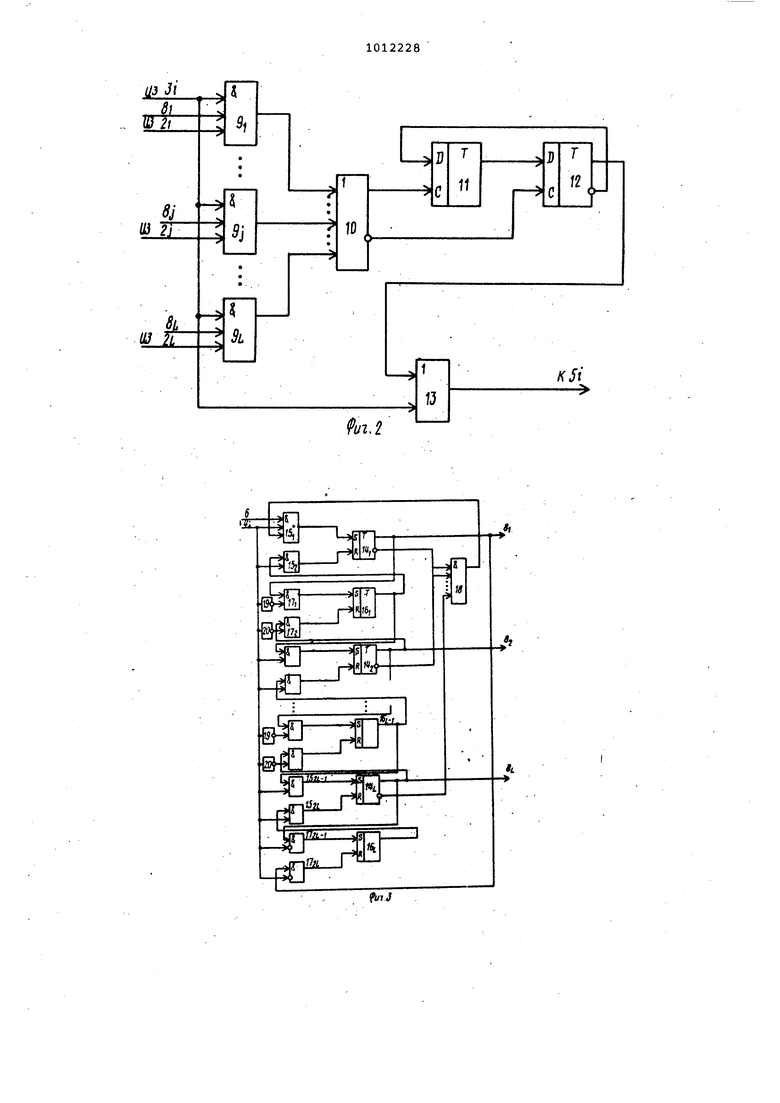

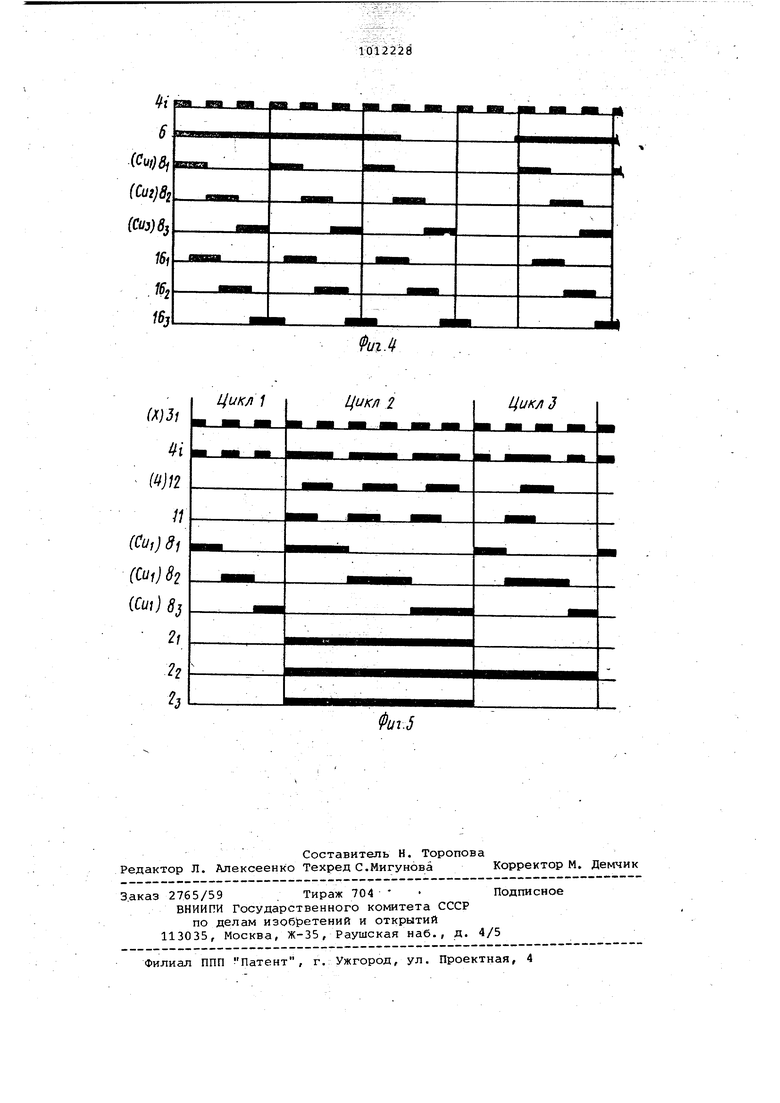

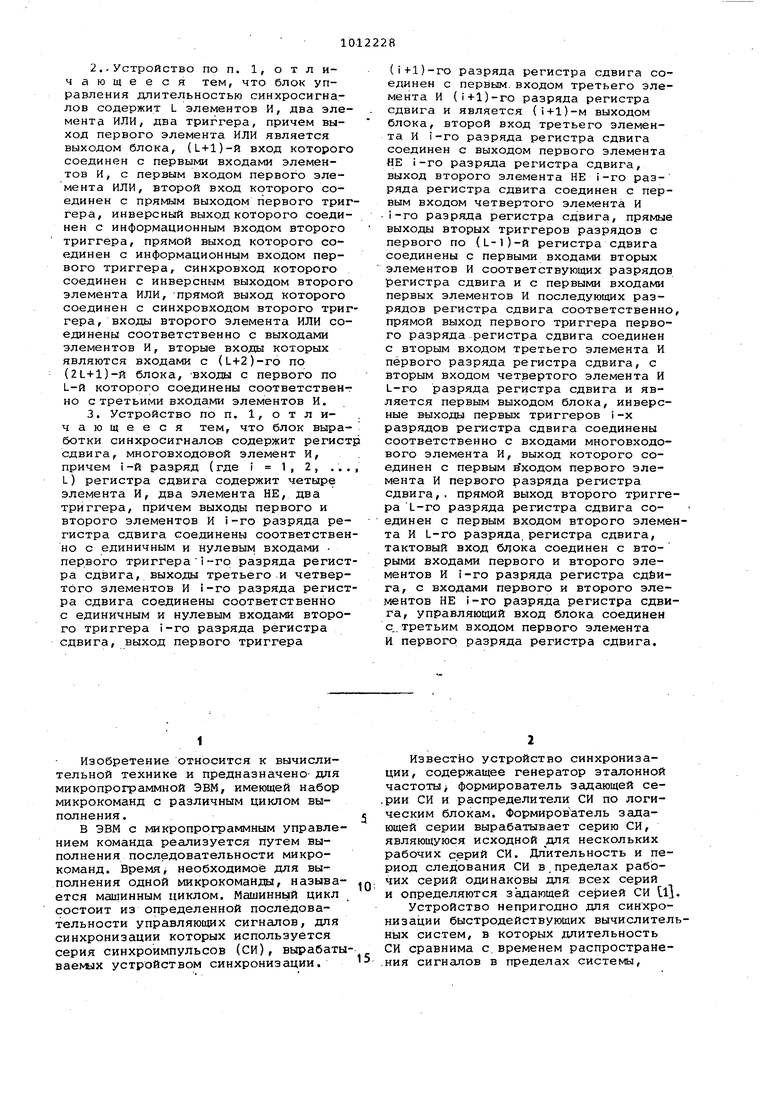

На фиг. 1 изображена блок-схема устройства; на фиг. 2 - блок управления длительностью синхросигналов; на фиг. 3 - блок выработки синхросигналов; на фиг. 4 - пример временной диаграм1«ы работы блока выработки синхросигналов при отсутствии сиг. налов на выходах дешифратора длительности цикла L 3 (т.е. без динамического изменения длительности цикла); на, фиг. 5 - пример временной диаграммы работы устройства с динамическим изменением длительности цикла при .

Устройство содержит задающий генератор 1, дешифратор 2, элементы 3 задержки, блоки 4 управления длительностью синхросигналов, блоки 5 выработки синхросигналов, вход 6 запуска устройства, вход 7 кода микрокоманды устройства, выходы 8 устройства.

Блок 4 управления длительностью синхросигналов содержит элементы И 9 элемент ИЛИ 10, триггер 11, триггер 12, элемент ИЛИ 13.

Блок 5 выработки синхросигналов содержит триггеры 14, элементы И 15, триггеры 16, элементы И 17, элементы И 18, элементы НЕ 19 и 20. ,

Задающий генератор 1 предназначен для формирования непрерывной после-т довательности импульсов постоянной длительности и постоянной частоты, необходимой для формирования сйнхросерий. Постоянная частота поступает на входы элементов 3 задержки. Элементы задержки служат для временного выравнивания одноименных выходных сигналов блоков 5 выработки синхросигналов.

Дешифратор 2 предназна:чен для дешифрации кода микрокоманды, формирования управляющих сигнало.в удво- . ения соответствующих синхросигналов на выходах 8 устройства.

Блоки 4 управления длительностью синхросигналов предназначены для изменения в-нужный МПМРНТ времени

формл всех последовательностей импульсов, поступающих с элементов 3 задержки таким образом, чтобы получить на всех выходах блока 4 форму последовательностей импульсов, обеспечивающую формирование на выходах устройства удвоен«ой длительности согласно входным управляющим сигналам, поступающим в блоки 4 из дешифратора 2.

Нужные моменты времени в машинном цикле определяются сигналами с выходов блоков 5, поступающими в блоки 4 .

Блоки 5 выработки синхросигналов предназначены для выработки синхросигналов, определяющих временную диаграмму машинного цикла, его длительность и используемых в вычислительной машине для синхронизации логических узлов.

Удвоение длительности синхроимпулсов с помощью блоков 4 управления длительностью синхросигналов реализуется следующим образом (фиг. 2). В цикле микрокоманды с удвоением длительности синхросигналов на выходе дешифратора 2 появляется сигнал, поступающий на входы блоков 4. Как только в блоке 5 начинает вьрабатываться синхросигнал, на соответствующих входах блоков 4 появляется сигнал и по наличию сигнала (положительному полупериоду непрерывной последовательности импульсов с выходов элементов 3 задержки) на входах элементов И 9 блоков управления длительностью синхроимпульсов появляется сигнал на выходе элемента И 9, который , . пройдя через элемент ИЛИ 10, подается на син;сровход триггера 11, который устанавливается по наличию сигнала на инверсном выходе триггера 12 (в исходном состоянии триггеры сброшены). При отсутствии сигнгша (отрицательному полупериоду непрерывной последовательности импульсов с выходов элементов 3 задержки) на входах элементов И 9 блоков 4 появляется сигнсШ на инверсном выходе элемента ИЛИ 10 ,поступаю1«ий на синхровход триггера единичное состояние триггера 11 переписывается в триггер 12. Сигнал с прямого выхода триггера 12 подается на первый вход элемента ИЛИ 13 и обеспечивает наличие сигнала на выходе блоков 4 во время отсутствия сигнала на втором входе элемента ИЛИ 13. В результате, во время выработки синхроимпульсов форма последовательностей импульсов, поступающих на входы блоков 4, преобразуется, а именно на выходах блоков 4 получаются последовательности с удлинением положительного полупериода на величину периода эталонной последовательности импульсов, что, в свою очередь, приводит

к формированию синхросигналов удвоенной длительности. Аналогично удваивается длительность любого другого синхроимпульса в цикле.

Блок 5 выработки синхросигналов представляет собой регистр сдвига, число разрядов которого равно числу импульсов в серий. Регистр работает только в режиме сдвига и занесением информации в младший разряд (триггер 14) управляют элементы 18 и 15 Триггеры представляют собой ряд основных триггеров сдвигающего регистра, а триггеры 16;,-16. - ряд вспомогательных триггеров сдвигающего регистра.

На синх15овход сдвигающего регистра (вторые входы элементов И , ) подается непрерывная последовательность импульсов с выхода одного из соответствующих блоков 4, сдвигающий регистр постоянно сдвигает находящуюся в регистре информацию

Установка некоторого триггера 14, означает занесение единицы в данный разряд сдвигающего регистра и выработку соответствующего импульса серии. При отсутствии источника запуска занесение единицы в младший раэ.ряд запрещено и в блоке 5 постоянно сдвигается нулевая информация, т.е. импульсы серии не вырабатываются. При поступлении сигнала 6 от источника запуска, как показано на фиг. 4 (во избежание искажения длительности первого импульса синхросерии он должен поступать во время неактивного полупериода сигнала 4 , поступающего на синхровход сдвигающего регистра) и наличии сигнала 4. (активного полулериода) по сигналу с выхода элемента 15 устанавливается триггер 14, т.е. вырабатывается первый синхроимпуль.с {серии 8.

Выход элемента 15 становится.в этот момент активным, поскольку все разряды регистра сдвига нулевые и выход элемента 18 активен. После установки триггера 14 выход элемента 18 становится неактивным и запрещает его установку до тех пор, пока все триггеры . не станут вновь нулевыми. Далее при отсутствии сигнала 4- (следуищему неактивному полупериоду) устанавливается вспомогательный триггер 16, поскольку на выходе элемента 17 появляется сигнал (триггер 14 установлен и инвертирование сигнала 4j на втором входе элемента 17 также дает активный сигнал)..

По второму (с момента поступления активному полупериоду сигнала 4. устанавлйваетсятриггер 14 и сбрасывается триггер 14, т.е. кончается первый синхроимпульс серии 8 и начинается второй 82- Аналогично производится дальнейший сдвиг единицы

и последовательная выработка синхроимпульсов серии. После сброса последнего триггера 14 при наличии сигнала запуска 6 вновь устанавливается триггер 14 и начинается новая серия синхроимпульсов. Серии синхроимпульсов следуют непрерывно и пос- , тоянно до тех пор, пока не снимается сигнал запуска 6, после чего сдвигающий регистр завершает сдвиг записанной в начале цикла единицы по всем разрядам и устанавливает тем caivfcJM триггеры . в исходное нулевое состояние. При отсутствии сигнала 6 (фиг. 4) занесение единицы в младший разряд регистра запрещено, и серии тактовых синхроимпульсов не вырабатываются.

Последовательность сброса-установки триггеров блока 5 показана на временной диаграмме (фиг. 4).

Устройство работает следующим образом.

Разряды полей микрокоманды, являющиеся источником кода микрокоманды и определяющие длительность ее цикла поступают на вход дешифратора 2, который формирует набор управлякяцих сигналов,поступакмдих на входы блоков 4. При наличии сигнала, например 2j , в блоках во время появления сигнала Bj на выходе устройства происходит удлинение на период импульса из непрерывной последовательности импульсов, поступающей в блоки 4,-4 М элементов задержки. В результате, под управлением измененной непрерывной последовательности импульсов, поступающей с выходов блоков 4,,-4р на входы блоков удваивается длительность формируемого выходного сигнала 8 устройства. . Аналогично удваиваются другие синхросигналы при наличии соответствующего управляющего сигнала на выходах дешифратора 2. ,

На временной диаграмме (фиг, 5) показан пример работы устройства с динамическим изменением длительности цикла (при L 3). Цикл 1 - самый короткий машинный цикл, в котором на всех управляющих выходах (2,, 2, Zg) дешифратора 2 отсутствует сигнал Цикл 2 - самый длинный машинный цикл в котором на всея управляющих выходах (2, 22, 2) дешифратора 2 присутствует сигнал. Цикл 3 - один из вариантов удлинения самого короткого машинного цикла, в котором сигнал присутствует на одном из управляющих выходов дешифратора 2.

Технико-экономическая эффективность изобретения заключается в том что оно позволяет наиболее полно исполвзовать функциональные возможности оборудования и увеличить быстродействие электронно-вычислительной машины.

J Цикл 1 Цикл 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ТЕЛЕФОННОЕ РЕЛЕ | 1923 |

|

SU1020A1 |

| м., Статистика, 1975, с | |||

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Серопян С | |||

| С | |||

| Построение системы синхронизации быстродействунйцей ЭВМ | |||

| - Вопросы радиоэлектроники , серия ЭВТ, 1979, вып | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Автомат для изготовления роликов для игольчатых подшипников | 1955 |

|

SU105110A1 |

Авторы

Даты

1983-04-15—Публикация

1981-09-15—Подача