коммутатора соединен с выходом поля операции памяти микропрограмм, выход поля управления константой которой соединен с первыми входами элементов И группы блока формирования константы и с первым входом второго дешифратора, третий выход которого соединен с первыми входами элементов ИЛИ группы блока формирования -константы, вторые входы которых соединены соответственно с вькодами эле ментов И группы блока управления константой, вторые входы которых соединены с выходами поля константы памяти микропрограмм и с вторым входом второго дешифратора, выходы элементов ИЛИ группы блока формирования константы соединены с входами Кода маски операционного блока, .вход младшего разряда адреса строки памяти микропрограмм соединен с выходом второго элемента ИЛИ блока формирования адреса условного перехода, первый и второй входы которого соединены соответственно с выходом второго триггера и с выходом младшего разряда адреса строки блока микро-

9021

программного управления, вход загрузки адреса микрокоманды которого соединен с первым выходом первого дешифратора, первая группа выходов которого соединена с входами установки-сброса второго регистра, выходы которого соединены соответственно с первыми входами п-элементов И группы блока формирования адреса-условного перехода, первый вход (п+1)-го элемента И группы блока формирования адреса условного перехода соединен с выходом переноса операционного блока, вторая группа выходов первого дешифратора соединена с вторыми входами (п + 1) элементов И группы блока формирования адреса условного перехода, выходы которых соединены с входами первого элемента ИЛИ блока формирования адреса условного перехода, выход которого соединен с информационным входом первого триггера, выход которого соединен с информационным . входом второго триггера, выход поля начальной установки памяти микропрограмм соединен с входом первого дешифратора ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1984 |

|

SU1164721A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1262516A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Микропроцессор | 1982 |

|

SU1035610A1 |

| Микропрограммный процессор | 1982 |

|

SU1037264A1 |

| Микропроцессор | 1984 |

|

SU1257657A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Микропрограммное устройство управления с контролем переходов | 1980 |

|

SU966694A1 |

МИКРОПРОЦЕССОР, содержащий операционный блок, блок микропрограммного управления, память микропрограмм и генератор тактовых импульсов, причем выход генератора тактовых импульсов соединен с входами синхронизации операционного блока и блока микропрограммного управления, выход признаков которого соединен с входом переноса операционного блока, информационный и адресный выходы которого являются соответственно информационным и адресным выходами микропроцессора, вход внешних данных операционного блока соединен с входом кода команды блока микропрограммного управления и является входом внешних данных микропроцессора, выход переноса операционного блока соединен с входом признаков блока микропрограммного управления, выходы разрядов адреса колонки-микрокоманды и старших разрядов адреса строки микрокоманды которого соединены соответственно с входами разрядов адре са колонки и старших разрядов адреса строки памяти микропрограмм, .выходы поля управления переходом, поля управления занесением .и хранением флажков и поля управления выдачей флажков которой.соединены соответственно с входами управления.переходами, управления занесением и хранением флажков и управления выдачей флажков блока микропрограммного .управления, выход поля управления внешним обьектом памяти микрокоманд является управляющим выходом микропроцессора, отличающийся § тем, что, с целью сокращения оборудования, он содержит два регистра, (Л коммутатор, два дешифратора,блок формирования константы, содержащий груп пы элементов И и элементов ИЛИ, &лок формирования адреса условного перехода, содержащий группу элементов И, два элемента ИЛИ, элемент, НЕ и два триггера, причем информационный вход первого регистра соединен с входом внешних данных микропроцессора, вхо ды синхронизации первого, второго э регистров и первого триггера соеди N9 нены с выходом генератора тактовых импульсов и с входом элемента НЕ, выход которого соединен с входом синхронизации второго триггера, выход первого регистра соединен с первым информационным входом коммутатора, выход которого соединен с входом кода операции операционного ка, управляющий вход коммутатора соединен с первым выходом второго дешифратора, второй выход которого соединен с входом чтения-записи первого регистра, второй информационный вход

Изобретение относится к области вычислительной техники и может быть использовано для управления работой различных периферийных устройств электронных цифровых вычисли тельных машин.

Известно устройство, содержащее арифметико-логический блок, блок микропрограммного управления, синхронизирующий контроллер tl3Недостатком этого устройства является большая потребляемая мощность и высокая стоимость, поэтому его использование для управления простыми низкоскоростными и среднескоростными периферийными устройствами неэффективно.

Известно устройство, содержащее арифметико-логический блок, блок управления, генератор синхросигналов 2.

Недостатками этого устройства является высокая стоимость электропитния, поскольку необходимы три номинала электропитания, и низкое быстродействие, что не позволяет эффективно использовать его для управления среднескоростными устройствами (например, дисплеем).

Наиболее близким по технической . сущности к предлагаемому является микропроцессор, содержащий операционный блок, блок микропрограммного управления, память микропрограмм и генератор тактовых импульсов, причем выход генератора тактовых импульсов соединен с входами сикрохронизации операционного блока и блока микропрограммного управления, выход признаков которого соединен с входом переноса операционного блока, информационный и адресный выходы которого являются соответственно информационным и адресным выходами микропроцессора, вход внешних данных операционного блока соединен с входом кода

31

команды блока микропрограммного управления и является входом внешних данных микропроцессора, выход переноса операционного блока соединен с входом признаков блока микропрограммного управления, выходы разрядов адреса колонки микрокоманды и старших разрядов адреса строки памяти микропрограмм, выходы поля управления переходом, поля управления занесением и хранением флажков и поля управления выдачей флажков которой соединены соответственно с входами управления переходами, управления занесением и хранением флажков и управления выдачей флажков блока микропрограммного управления, выход поля управления внешним объектом памяти микрокоманд является управляющим выходом микропроцессора Сз.

Недостатком этого устройства является следующее. Используемые функции управления адресом блока микропрограммного управления дают возможность перехода (условного и безусловного) к довольно ограниченному множеству адресов микрокоманд, причем внутри этого множества условные переходы имеют нерегулярную структуру, изменяя различные разряды адреса следующей микрокоманды (в зависимости от выполняемой функции управления адресом), Данные ограничения препятствуют эффективному заполнению памяти микропрограмм, приводят к ее недоиспользованию, поскольку размещение микропрограмм с полным использованием всех ячеек памяти микропрограмм часто является неразрешимой задачей для разветвленных микропрограмм. Кроме того, отсутствует возможность использования поля константы операционного блока в микрокоманде для управления другими функциями микропроцессора, что приводит к существенному увеличению разрядности микрокоманды. А также отсутствует возможность оперативной модификации кода микроопераций операционного блока, что ограничивает возможности параметризации микропрограмм (использования одной и той же микропрограммы для реализации различных функций), а следовательно, объем микропрограмм управления периферийным устройством может не уложиться в заданные разрядностью адреса микрокоманды ограничения.

90214

Цель изобретения - сокращение оборудования путем снижения объема памяти микропрограмм.

Поставленная цель достигается тем, что в микропроцессор, содержащий операционный блок, блок микропрограммного управления, память микропрограмм и генератор тактовых импульсов, причем выход генератора тактовых импульсов соединен с входами синхронизации операционного блока и блока микропрограммного управления, выход признаков которого соединен с входом переноса операцион- ного блока, информационный и адресный выходы которого являются соответственно информационным и адресным выходами микропроцессора, вход внешних данных операционного блока соединен с входом кода команды блока микропрограммного управления и является входом внешних данных микропроцессора выход переноса операционного блока соединен с входом признаков блока микропрограммного управления, выходы разрядов адреса колонки микрокоманды и старших разрядов адреса строки микрокоманды которого соединены соответственно с входами разрядов адреса колонки и старших разрядов адреса строки памяти микропрограмм, выходы поля управления переходом, поля управления занесением и хранением флажков и поля управления вьщачей флажков которой соединены соответственно с входами управления переходами, управления заТ1есением и хранением флажков и управления выдачей флажков блока микропрограммного управления, выход поля управления внешним объектом памяти микрокоманд является управляющим выходом микропроцессора, введены два регистра, коммутатор, два дешифратора, блок формирования константы, содержащий группы элементов И и элементов ИЛИ, блок формирования адреса условного /перехода, содержащий группу элементов И, два элемента ИЛИ, элемент НЕ

0 и два триггера, причем информационный вход первого регистра соединен с входЬм внешних данных микропроцессора, входы синхронизации первого, второго регистров и первого

5 триггера соединены с выходом генератора тактовых импульсов и с входом элемента НЕ, выход которого соединен .с входом синхронизации второ51го триггера, выход первого регистра соединен с первым информационным входом коммутатора, выход которого соединен с входом кода операции. операционного блока, управляющий вход коммутатора соединен с первым выходом второго дешифратора, вто рой выход которого соединен с входом чтения-записи первого регистра, второй информационный вход коммутатора соединен с выходом поля операции памяти микропрограмм, выход поля управления константой которой соединен с первыми входами элементов И группы блока формирования константы с первым входом второго дешифратора, третий выход которого соединен с первыми входами элементов ИЛИ груп-пы блока формирования константы, вто рые входы которых соединены соответственно с выходами элементов И группы блока управления константой. I вторые входы которых соединены с вых дами поля константы памяти микропрограмм и с вторым входом второго дешифратора, выходы элементов ИЛИгруп пы блока Нормированияконстанты соединены с входами кода маски операцио ного блока, вход младшего разряда ад реса строки памяти микропрограмм соединен с выходом второго элемента ИЛИ блока формирования адреса условного перехода, первьм и второй входы которого соединены соответственно с выходом второго триггера и с выходом младшего разряда адреса;строки блока микропрограммного управления, вход загрузки адреса микрокоманды ко торого соединен с первым выходом первого дешифратора, первая группа выходов которого соединена с входами установки-сброса второго регистра, выходы которого соединены соответственно с первыми входами h-элементов И группы блока формирования адре-45 са условного перехода, первый вход ( п+1)-го элемента И группы блока формирования адреса условного перехода соединен с выходом переноса операционного блока, вторая группа выходов первого дешифратора соединена с вторыми входами (n-f1) элементов И группы блока формирования адреса условного перехода, выходы которых соединены с входами перво

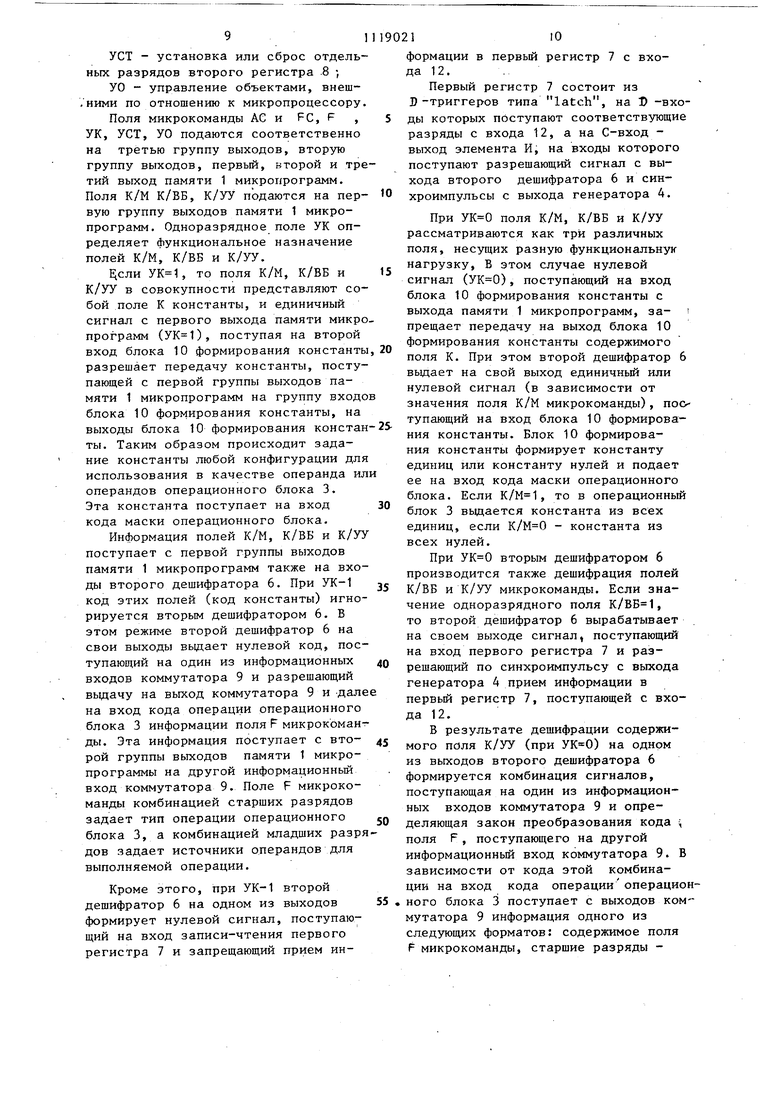

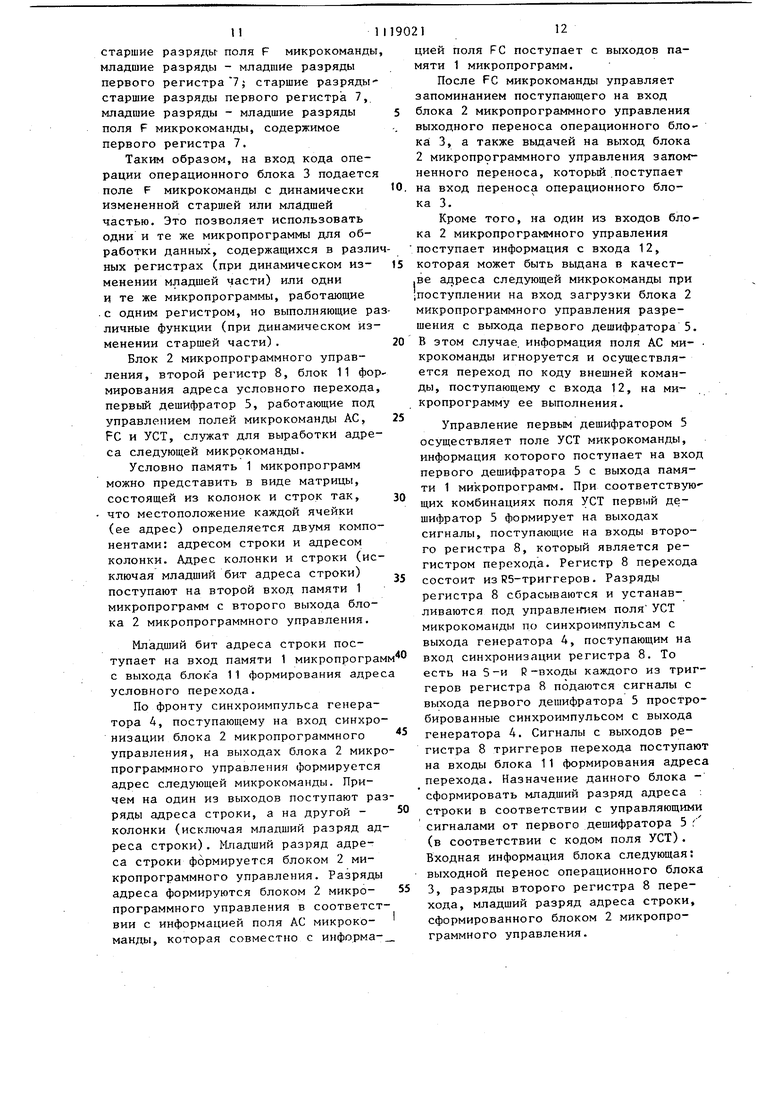

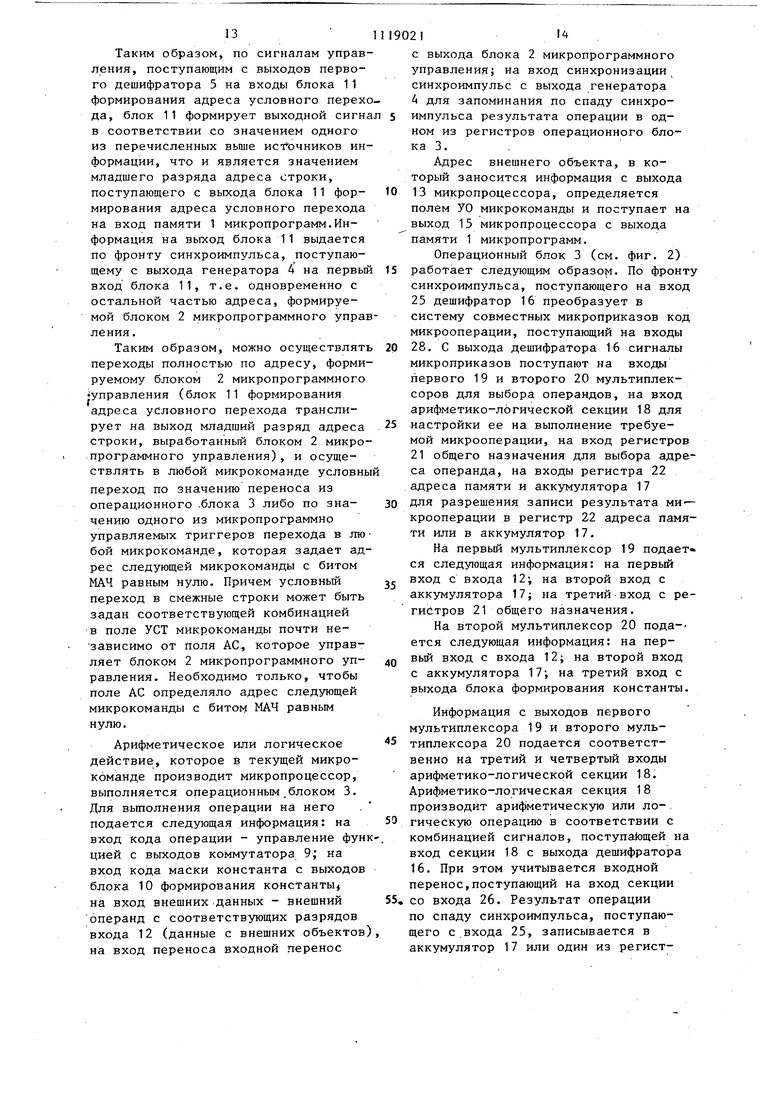

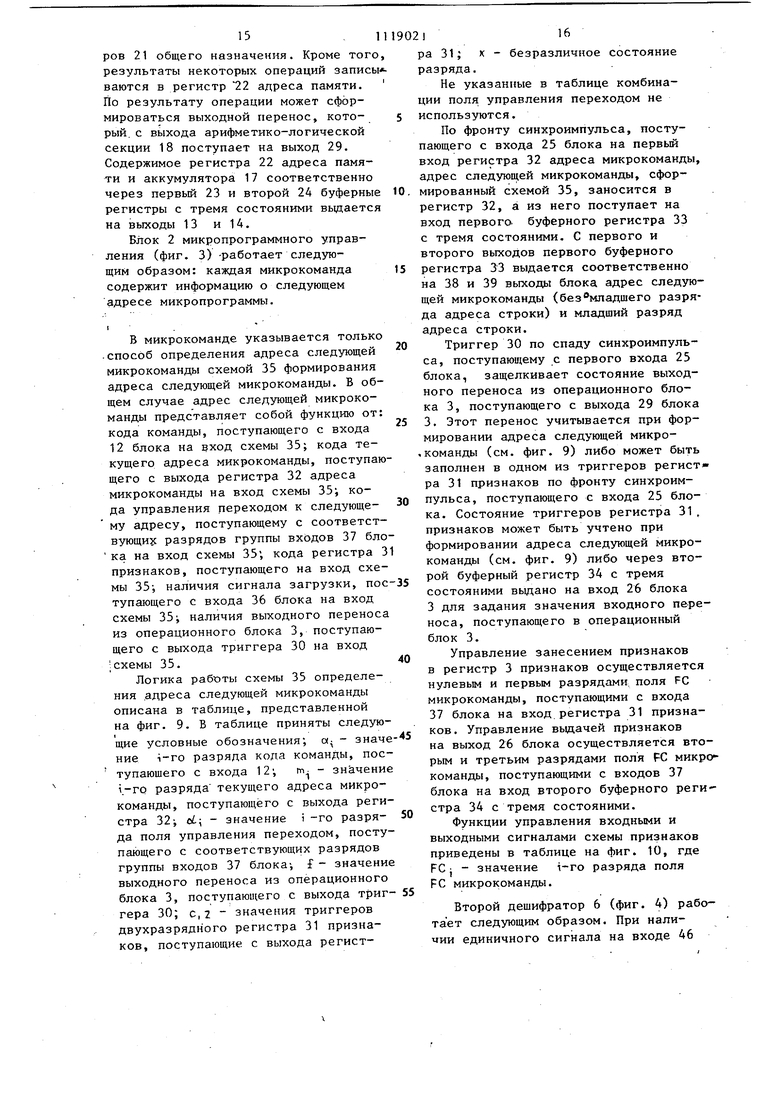

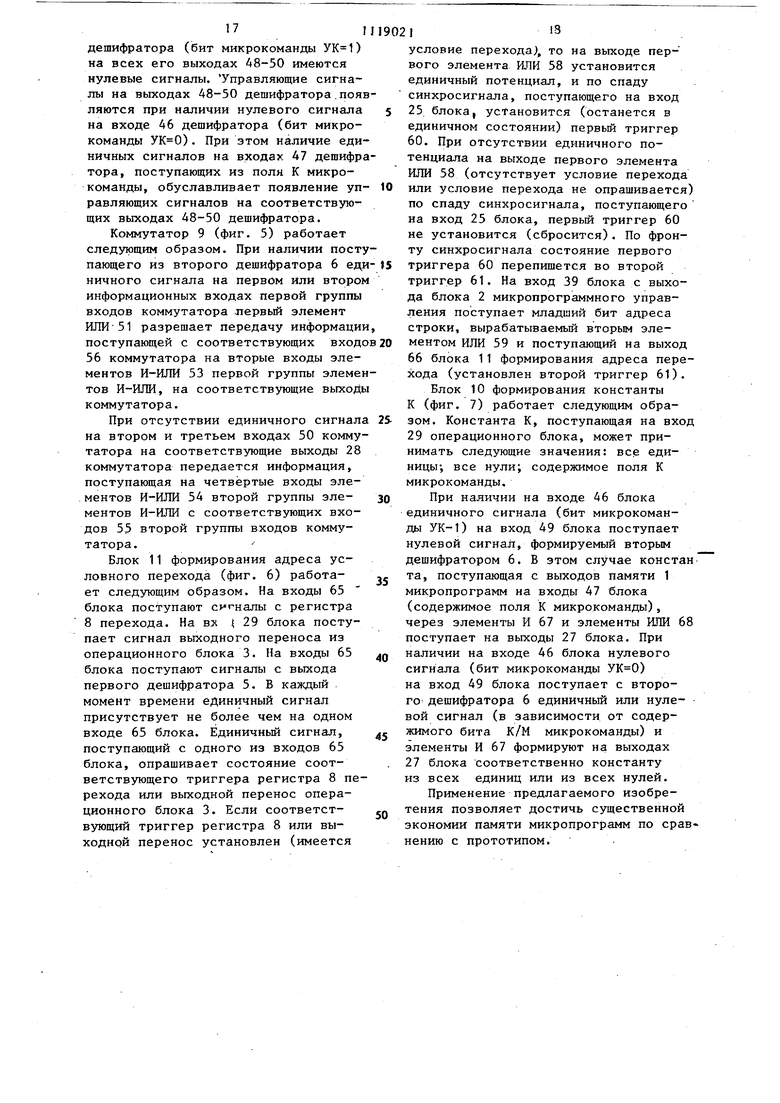

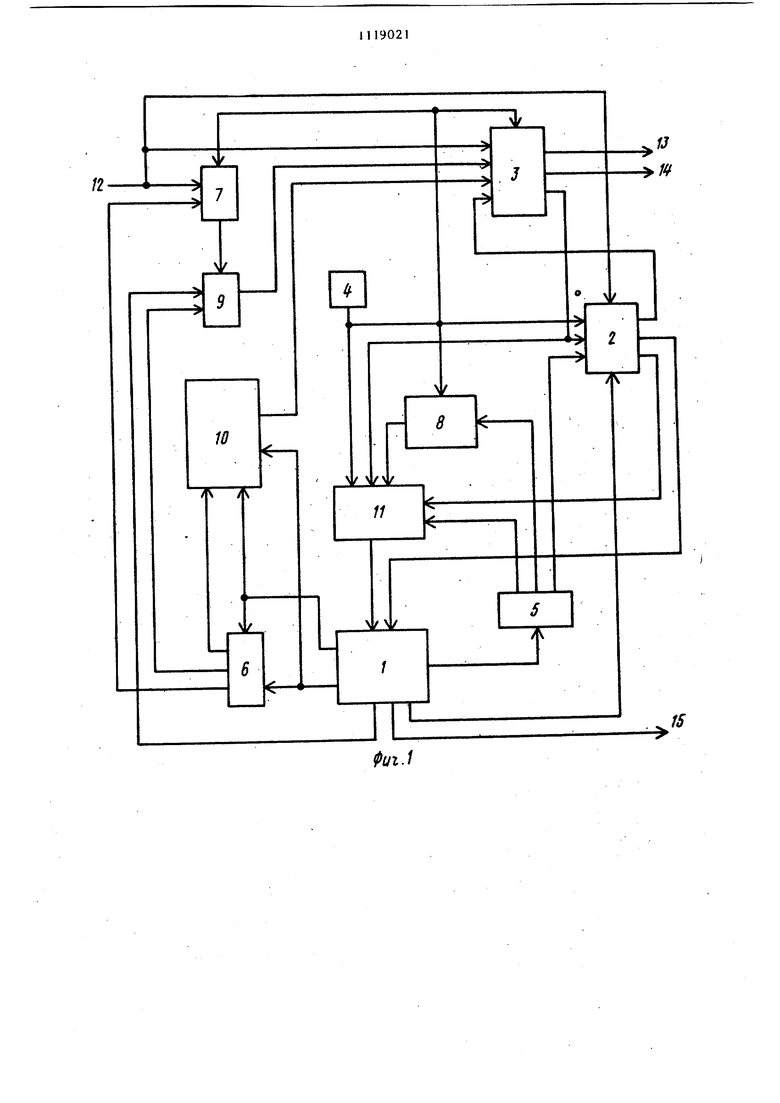

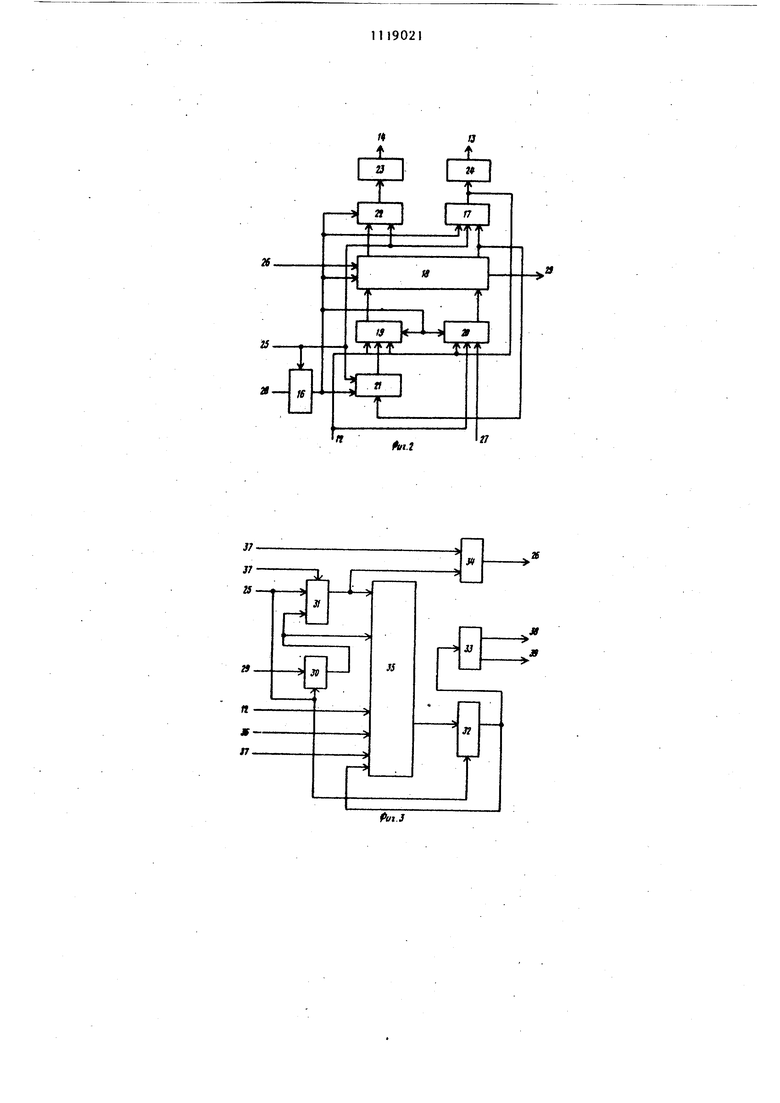

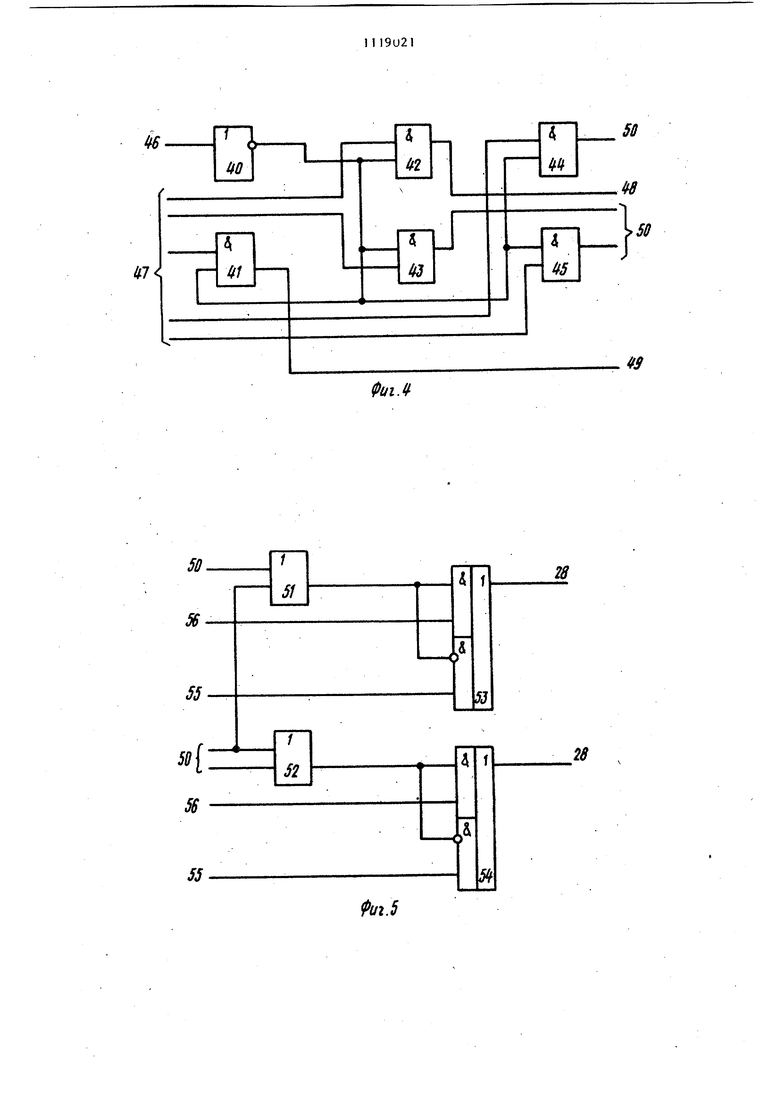

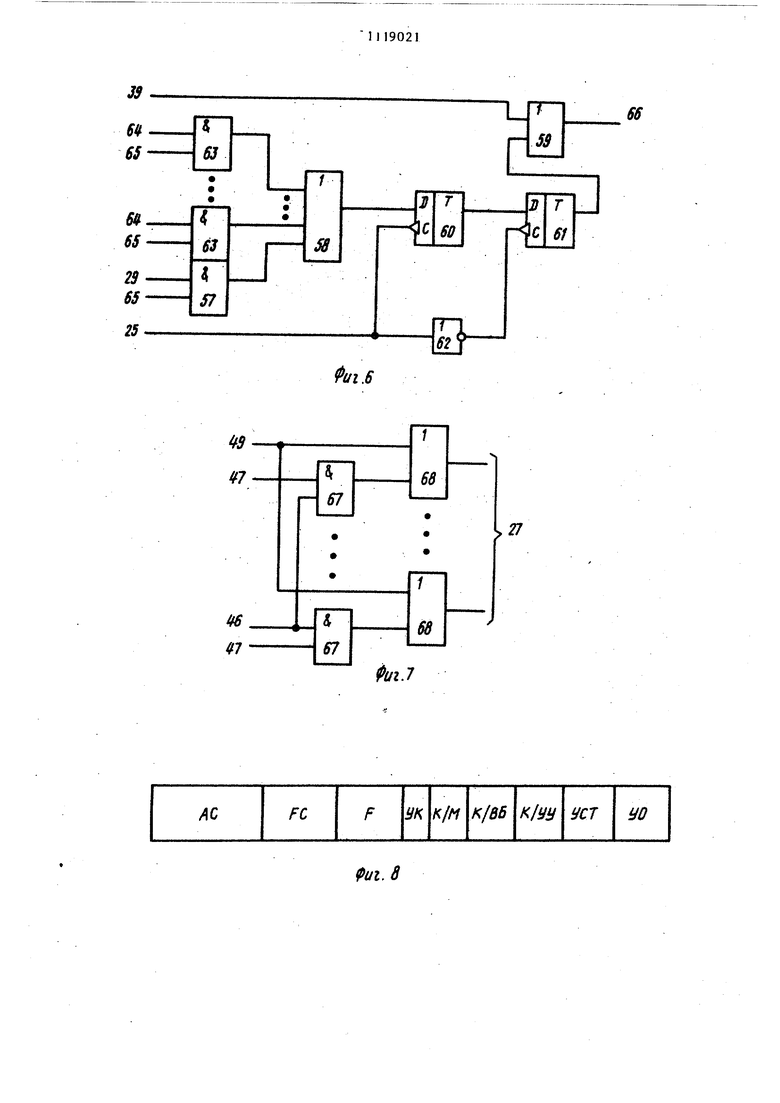

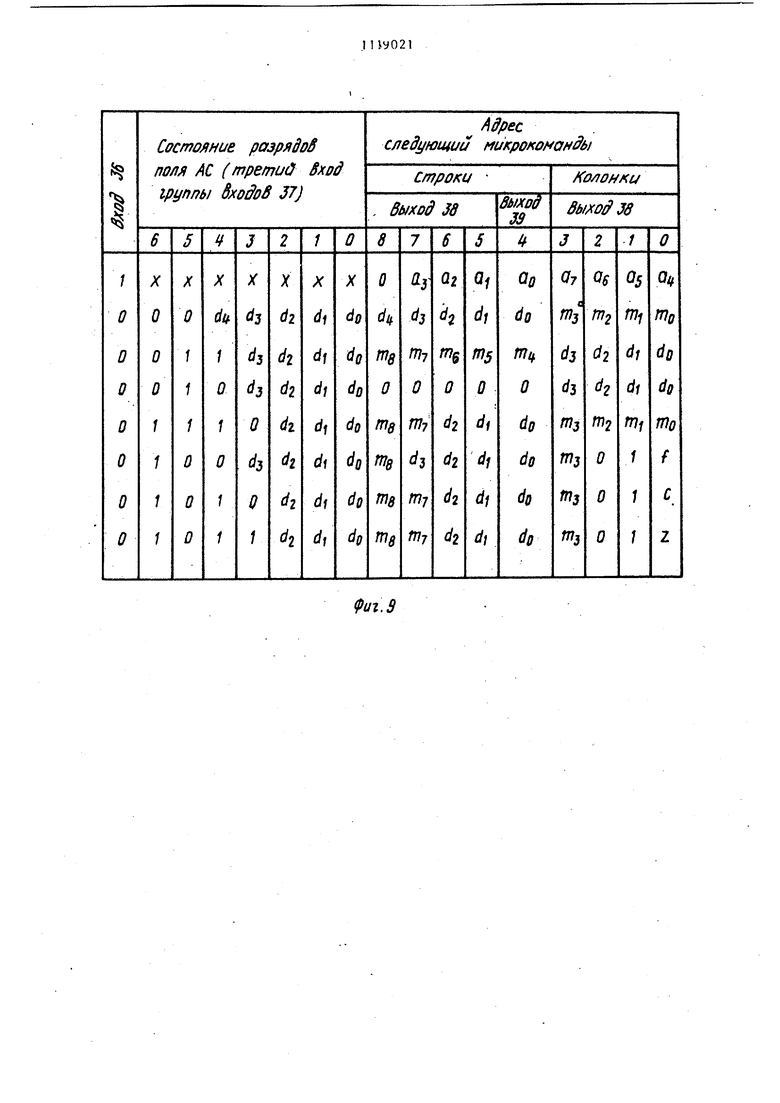

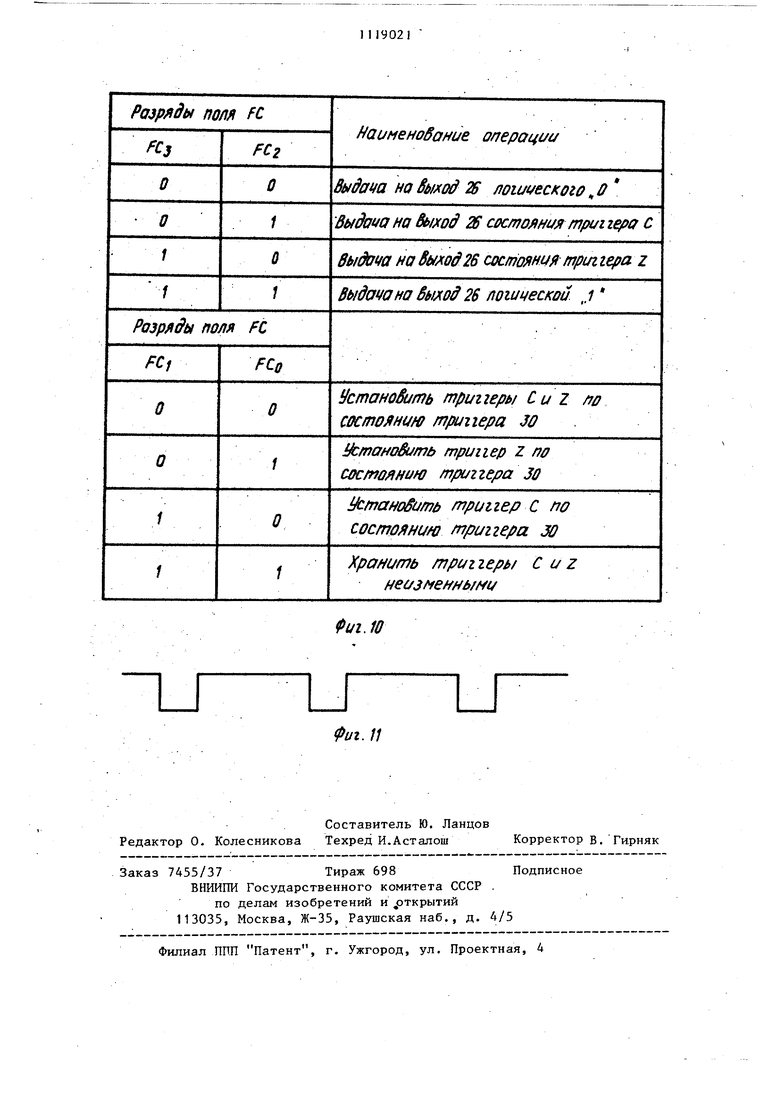

го элемента ИЛИ блока формирования адреса условного перехода, выход «оторого соединен с информационстры с тремя состояниями, соответственно входы синхронизации и переноса 25 и 26, соответственно входы кода 1 ным входом первого триггера, выход которого соединен с информационным входом второго триггера, выход поля начальной установки памяти микропрограмм соединен с входом первого дешифратора. На фиг. 1 изображен функциональная схема микропроцессора; на фиг. 2 - функциональная схема операционного блока-, на фиг. 3 - функциональная схема блока микропрограммного управленияi на фиг. 4 - функциональная схема второго дешифратора-, на фиг. 5 - функциональная схема коммутатора; на фиг. 6 - функциональ нал схема блока формирования адреса условного перехода; на фиг. 7 функциональная схема блока формирования константы; на фиг. 8 - формат микрокоманды; на фиг. 9 - таблица логики работы схемы определения адреса следующей микрокоманды блока микропрограммного управления; на фиг. 10 - таблица функции управления входными и выходными сигналами схемы признаков блока микропрограммного управления-, на фиг. -11 - временная диаграмма синхросерии, вырабатываемой генератором синхроимпульсов. Микропроцессор (фиг. 1) содержит память 1 микропрограмм, блок 2 микропрограммного управления, операционный блок 3, ге.нератор 4 тактовых импульсов, первый дешифратор 5, второй дешифратор 6, первьй регистр 7, второй регистр 8, коммутатор 9, блок 10 формирования константы, блок 11 формирования адреса условного перехода, вход внешних данных ,12, соответственно информационный, адресный и управляющий выходы микропроцессора 13 - 15. Операционный блок 3 (фиг. 2) пред назначен для выполнения арифметических и логических операций и хранения промежуточны с результатов. Он реализован путем соединения нескольких секционных БИС К589И 02, каждая из которых содержит дешифратор 16, аккумулятор 17, арифметико-логическую секцию 18, первый 19 и второй 20 мультиплексоры, регистры 21 общего назначения, регистр 22 адреса памяти. первый 23 и второй 24 буферные реги/маски и кода операции операционного блока 27 и 28, выход переноса 29. Блок 2 микропрограммного управления (фиг. 3) предназначен для формирования адреса следующей микрокома ды..Он реализован на БИС К589 ИК01 и содержит триттер 30, регистр 31 признаков, регистр 32 адреса микрокоманд, первый 33 и второй 34 буферные регистры с тремя состояниями, схему 35 формирования адреса следующей микрокоманды, вход 36 загрузки, вход 37 синхронизации, выхо ды 38, 39 соответственно разрядов адреса строки и разрядов адреса ко лонки. Второй дешифратор 6 содержит элемент НЕ 40, первый 41, второй 42 третий 43, четвертый 44, пятый 45 элементы И, входы 46 и 47, выходы 48 - 49, группу выходов 50, Коммутатор 9 (фиг. 5) содержит первый 51 и второй 52 элементы ИЛИ, первую 53 и вторую 54 группы элемен тов И-ИПИ информационные входы 55,5 Блок 11 формирования адреса условного перехода (фиг. 6) и второ регистр 8 предназначены для формирования разрядов адреса памяти микр программ. Блок 11 формирования адр .са условного перехода содержит элемент И 57, первый 58 и второй 59 эл менты ИЛИ, первый 60 и второй 61 триггеры, элемент НЕ 62, группу эле ментов И 63, входы 64, 65, выход 66 Блик 10 формирования константы (фиг. 7) предназначен для формирова ния константы, поступающей на вход кода маски операционного блока 3. О содержит группу элементов И 67 и ИЛИ 68. . Первьй дешифратор 5 предназначен для управления блоком 2 микропрогра много управления, вторым регистром и блоком 11 «Ьормирования адреса условного перехода. Второй дешифратор 6 предназначен для управления блоком 10 формирования константы, коммутатором 9 и пер вым регистром 7. Генератор 4 предназначен для выработки синхроимпульсов, синхронизирующих работу устройства. Микропроцессор работает следующи образом. В общем случае управление периферийным устройством можно свести к управлению состоянием регистров и 18 памятью периферийного устройства. Состояние выбранных внешних обьектов (регистра или ячейки памяти) периферийного устройства поступает в микропроцессор по входу 12. При этом адрес выбранного регистра периферийного устройства подается на выход 15 микропроцессора. Если выбранным объектом окажется память, то адрес ячейки памяти должен быть подан на выход 14 микропроцессора. Обработав входную информацию в соответствии с заданным алгоритмом управления периферийным устройством, микропроцессор выдает на выход 13 измененное состояние выбранного объекта. Режим работы с объектом (считывание или запись) также задается с помощью выхода 15. Для реализации всех алгоритмов работы микропроцессора используется микропрограммный принцип управления. Микропрограммы хранятся в памяти 1 микропрограмм. По фронту очередного синхроимпульса генератора 4 на первый и второй входы памяти 1 микропрограмм поступает адрес очередной микрокоманды, который вырабатывается блоком 11 формирования адреса усЛОБНОГО перехода и блоком 2 микропро граммного управления. По данному адресу из памяти 1 микропрограмм считывается очередная микрокоманда, которая управляет работой микропроцессора в течение очередного, цикла синхросерии генератора 4. Формат микрокоманды представлен на фиг. 8. Обозначения полей микрокоманды расшифровываются следующим образом: УК - управление константой, подаваемой на первую группу входов операционного блока 3; К/М - разряд константы, подаваемой на первую группу входов блока 3, или маска (единица или ноль), по значению которой блок 10 формирует :константу, подаваемую на первую группу входов блока 3; К/ВБ - разряд константы, подаваемой на первую группу входов блока 3, или выборка информации поступающей с входа 12 устройства; К/УУ - часть разрядов константы, подаваемой на первую группу блока 3, или управление установкой кода, поступающего на вторую группу входов;

УСТ - установка или сброс отдельных разрядов второго регистра 8 ;

УО - управление объектами, внеш.ними по отношению к микропроцессору.

Поля микрокоманды АС и FC, F , УК, УСТ, УО подаются соответственно на третью группу выходов, вторую группу выходов, первый, второй и третий выход памяти 1 микро1фогрс1мм. Поля К/М К/ВБ, К/УУ подаются на первую группу выходов памяти 1 микропрограмм. Одноразрядное поле УК определяет функциональное назначение полей К/М, К/ВБ и К/УУ.

Е;СЛИ , то поля К/М, К/ВБ и К/УУ в совокупности представляют собой поле К константы, и единичный сигнал с первого выхода памяти микропрограмм (), поступая на второй вход блока 10 формирования константы разрешает передачу константы, поступающей с первой группы выходов памяти 1 микропрограмм на группу входо блока 10 формирования константы, на выходы блока 10 формирования KOHCTaH ты. Таким образом происходит задание константы любой конфигурации для использования в качестве операнда ил операндов операционного блока 3. Эта константа поступает на вход кода маски операционного блока.

Информация полей К/М, К/ВБ и К/УУ поступает с первой группы выходов памяти 1 микропрограмм также на входы второго дешифратора 6. При УК-1 код этих полей (код константы) игнорируется вторым дешифратором 6. В этом режиме второй дешифратор 6 на свои выходы выдает нулевой код, поступающий на один из информационных входов коммутатора 9 и разрешающий вьщачу на выход коммутатора 9 и -дале на вход кода операции операционного блока 3 информации поля F микрокоманды. Эта информация поступает с второй группы выходов памяти 1 микропрограммы на другой информационный вход коммутатора 9. Поле F микрокоманды комбинацией старших разрядов задает тип операции операционного блока 3, а комбинацией младших разрядов задает источники операндов для выполняемой операции.

Кроме этого, при УК-1 второй дешифратор 6 на одном из выходов формирует нулевой сигнал, поступающий на вход записи-чтения первого регистра 7 и запрещающий прием информации в первый регистр 7 с входа 12.

Первый регистр 7 состоит из Л-триггеров типа latch, на D -входы которых поступают соответствующи разряды с входа 12, а на С-вход выход элемента И, на входы которого поступают разрешающий сигнал с выхода второго дешифратора 6 и синхроимпульсы с выхода генератора 4.

При поля К/М, К/ВБ и К/УУ рассматриваются как три различных поля, несущих разную функциональнук нагрузку, В этом случае нулевой сигнал (), поступающий на вход блока 10 формирования константы с выхода памяти 1 микропрограмм, запрещает передачу на выход блока 10 формирования константы содержимого поля К. При этом второй дешифратор вьщает на свой выход единичный или нулевой сигнал (в зависимости от значения поля К/М микрокоманды), поотупающий на вход блока 10 формирования константы. Блок 10 формирования константы формирует константу единиц или константу нулей и подает ее на вход кода маски операционного блока. Если , то в операционный блок 3 выдается константа из всех единиц, если - константа из всех нулей.

При вторым дешифратором 6 производится также дешифрация полей К/ВБ и К/УУ микрокоманды. Если значение одноразрядного поля , то второй дешифратор 6 вырабатывает на своем выходе сигнал, поступающий на вход первого регистра 7 и разрешающий по синхроимпульсу с выхода генератора 4 прием информации в первый регистр 7, поступающей с входа 12.

В результате дешифрации содержимого поля К/УУ (при ) на одном из выходов второго дешифратора 6 формируется комбинация сигналов, поступающая на один из информационных входов коммутатора 9 и определяющая закон преобразования кода поля F, поступающего на другой информационньш вход коммутатора 9. В зависимости от кода этой комбинации на вход кода операции операционого блока 3 поступает с выходов коммутатора 9 информация одного из следующих форматов: содержимое поля F микрокоманды, старшие разряды Пстаршие разряды- поля F микрокоманды младшие разряды - младшие разряды первого регистра7J старшие разряды старшие разряды первого регистра 7,. младшие разряды - младшие разряды поля F микрокоманды, содержимое первого регистра 7. Таким образом, на вход кода операции операционного блока 3 подается поле F микрокоманды с динамически измененной старшей или млйдшей частью. Это позволяет использовать одни и те же микропрограммы для обработки данных, содержащихся в разли ных регистрах (при динамическом изменении младшей части) или одни И те же микропрограммы, работающие .с одним регистром, но выполняющие р личные функции (при динамическом изменении старшей части). Блок 2 микропрограммного управления, второй регистр 8, блок 11 фо мирования адреса условного перехода первый дешифратор 5, работающие под управлением полей микрокоманды АС, FC и УСТ, служат для выработки адре са следующей микрокоманды. Условно память 1 микропрограмм можно представить в виде матрицы, состоящей из колонок и строк так, что местоположение каждой ячейки (ее адрес) определяется двумя компо нентами: адресом строки и адресом колонки. Адрес колонки и строки (ис ключая младший бит адреса строки) поступают на второй вход памяти 1 микропрограмм с второго выхода блока 2 микропрограммного управления. Младший бит адреса строки поступает на вход памяти 1 микропрогра с выхода блока 11 формирования адре условного перехода. По фронту синхроимпульса генератора 4, поступающему на вход синхро низации блока 2 микропрограммного управления, на выходах блока 2 микр программного управления формируется адрес следующей микрокоманды. Причем на один из выходов поступают ра ряды адреса строки, а на другой колонки (исключая младший разряд ад реса строки). Мпадший разряд адреса строки формируется блоком 2 микропрограммного управления. Разряды адреса формируются блоком 2 микропрограммного управления в соответст вии с информацией поля АС микрокоманды, которая совместно с информа1цией поля FC поступает с выходов памяти 1 микропрограмм. После FC микрокоманды управляет запоминанием поступающего на вход блока 2 микропрограммного управления выходного переноса операционного блока 3, а также выдачей на выход блока 2 микропрограммного управления запомненного переноса, которьй .поступает на вход переноса операционного блока 3. Кроме того, на один из входов бло ка 2 микропрограммного управления поступает информация с входа 12, которая может быть выдана в качестве адреса следующей микрокоманды при поступлении на вход загрузки блока 2 микропрограммного управления разрешения с выхода первого дешифратора 5. В зтом случае, информация поля АС ми- . крокоманды игноруется и осуществляется переход по коду внешней команды, поступающему с входа 12, на микропрограмму ее выполнения. Управление первым дешифратором 5 осуществляет поле УСТ микрокоманды, информация которого поступает на вход первого дешифратора 5 с выхода памяти 1 микропрограмм. При соответствую-щих комбинациях поля УСТ первый дешифратор 5 формирует на выходах сигналы, поступающие на входы второго регистра 8, который является регистром перехода. Регистр 8 перехода состоит из КЗ-триггеров. Разряды регистра 8 сбрасываются и устанавливаются под управлением поля УСТ микрокоманды по синхроимпульсам с выхода генератора 4, поступающим на вход синхронизации регистра 8. То есть на 5-и R-входы каждого из триггеров регистра В подаются сигналы с выхода первого дешифратора 5 простробированные синхроимпульсом с выхода генератора 4. Сигналы с выходов регистра 8 триггеров перехода поступают на входы блока 11 формирования адреса перехода. Назначение данного блока сформировать младший разряд адреса : строки в соответствии с управляющими сигналами от первого дешифратора 5 f (в соответствии с кодом поля УСТ). Входная информация блока следующая: выходной перенос операционного блока 3, разряды второго регистра 8 перехода, младший разряд адреса строки, сформированного блоком 2 микропрограммного управления. Таким образом, по сигналам управ ления, поступающим с выходов первого дешифратора 5 на входы блока 11 формирования адреса условного перех да, блок 11 формирует выходной сигн в соответствии со значением одного из перечисленных вьшге источников ин формации, что и является значением младшего разряда адреса строки, поступающего с выхода блока 11 формирования адреса условного перехода на вход памяти 1 микропрограмм.Информация на выход блока 11 выдается по фронту синхроимпульса, поступающему с выхода генератора 4 на первьй вход блока 11, т.е. одновременно с остальной частью адреса, формируемой блоком 2 микропрограммного упра ления. Таким образом, можно осуществлят переходы полностью по адресу, форми руемому блоком 2 микропрограммного управления (блок 11 формирования адреса условного перехода транслирует на выход младший разряд адреса строки, выработанный блоком 2 микро программного управления), и осуществлять в любой микрокоманде условн переход по значению переноса из операционного .блока 3 либо по значению одного из микропрограммно управляемых триггеров перехода в лю бой микрокоманде, которая задает ад рес следующей микрокоманды с битом МАЧ равным нулю. Причем условный переход в смежные строки может быть задан соответствующей комбинацией в поле УСТ микрокоманды почти независимо от поля АС, которое управляет блоком 2 микропрограммного управления. Необходимо только, чтобы поле АС определяло адрес следующей микрокоманды с битом МАЧ равным нулю. Арифметическое или логическое действие, которое в текущей микрокоманде производит микропроцессор, выполняется операционным блоком 3, Для вьтолнения операции на него подается следующая информация: на вход кода операции - управление фун цией с выходов коммутатора 9; на вход кода маски константа с выходов блока 10 формирования константы на вход внешних данных - внешний операнд с соответствующих разрядов входа 12 (данные с внешних объектов на вход переноса входной перенос С выхода блока 2 микропрограммного управления; на вход синхронизации синхроимпульс с выхода генератора 4 для запоминания по спаду синхроимпульса результата операции в одном из регистров операционного блока 3, , Адрес внешнего объекта, в который заносится информация с выхода 13 микропроцессора, определяется полем УО микрокоманды и поступает на выход 15 микропроцессора с выхода памяти 1 микропрограмм. Операционный блок 3 (см, фиг. 2) работает следующим образо. По фронту синхроимпульса, поступающего на вход 25 дешифратор 16 преобразует в систему совместных микроприказов код микрооперации, поступающий на входы 28, С выхода дешифратора 16 сигналы микроприказов поступают на входы первого 19 и второго 20 мультиплексоров для выбора операндов, на вход арифметико-логической секции 18 для настройки ее на выполнение требуемой микрооперации, на вход регистров 21 общего назначения для выбора адреса операнда, на входы регистра 22 адреса памяти и аккумулятора 17 для разрешения записи результата микрооперации в регистр 22 адреса памяти или в аккумулятор 17, На первый мультиплексор 19 подает ся следующая информация: на первый вход с входа 12; на второй вход с аккумулятора 17; на третий вход с регистров 21 общего назначения. На второй мультиплексор 20 пода-ется следующая информация: на первый вход с входа 12; на второй вход с аккумулятора 17; на третий вход с выхода блока формирования константы. Информация с выходов первого мультиплексора 19 и второго мультиплексора 20 подается соответственно на третий и четвертый входы арифметико-логической секции 18. Арифметико-логическая секция 18 производит арифметическую или логическую операцию в соответствии с комбинацией сигналов, поступа(ощей на вход секции 18 с выхода дешифратора 16. При этом учитывается входной перенос,поступающий на вход секции со входа 26, Результат операции по спаду синхроимпульса, поступающего с,входа 25, записывается в аккумулятор 17 или один из регист15, ров 21 общего назначения. Кроме того результаты некоторых операций записы ваются в регистр 22 адреса памяти. По результату операции может сформироваться выходной перенос, который, с выхода арифметико-логической секции 18 поступает на выход 29. Содержимое регистра 22 адреса памяти и аккумулятора 17 соответственно через первый 23 и второй 2А буферные регистры с тремя состояними вьщается на выходы 13 и 14. Блок 2 микропрограммного управления (фиг. 3) -работает следующим образом: каждая микрокоманда содержит информацию о следующем адресе микропрограммы. . В микрокоманде указывается только .способ определения адреса следующей микрокоманды схемой 35 формирования адреса следующей микрокоманды. В общем случае адрес следующей микрокоманды представляет собой функцию от кода команды, поступающего с входа 12 блока на вход схемы 35; кода текущего адреса микрокоманды, поступаю щего с выхода регистра 32 адреса микрокоманды на вход схемы 35i кода управления переходом к следующему адресу, поступающему с соответст вующие разрядов группы входов 37 бл ка на вход схемы 35; кода регистра признаков, поступающего на вход схе мы 35-, наличия сигнала загрузки, по тупающего с входа 36 блока на вход схемы 35V наличия выходного перенос из операционного блока 3, поступающего с выхода триггера 30 на вход .схемы 35. Логика рабхэты схемы 35 определения адреса следующей микрокоманды описана в таблице, представленной на фиг. 9. В таблице приняты следую щие условные обозначения; сх - знач ние i-ro разряда кода команды, пос тупающего с входа 12; зн&чени i.-ro разряда текущего адреса микрокоманды, поступающего с выхода реги стра 32-, oL - значение i -го разряда поля управления переходом, посту пающего с соответствующих разрядов группы входов 37 блока-, f - значени выходного переноса из операционного блока 3, поступающего с выхода триг гера 30; 0,2 - значения триггеров двухразрядного регистра 31 признаков, поступающие с выхода регист116ра 31; X - безразличное состояние разряда. Не указанные в таблице комбинации поля управления переходом не используются. По фронту синхроимпульса, поступающего с входа 25 блока на первый вход регистра 32 адреса микрокоманды, адрес следующей микрокоманды, сформированный схемой 35, заносится в регистр 32, а из него поступает на вход первого- буферного регистра 33 с тремя состояними. С первого и второго выходов первого буферного регистра 33 выдается соответственно на 38 и 39 выходы блока адрес следующей микрокоманды (без младшего разряда адреса строки) и младший разряд адреса строки. Триггер 30 по спаду синхроимпульса, поступающему с первого входа 25 блока, защелкивает состояние выходного переноса из операционного блока 3, поступающего с выхода 29 блока 3. Этот перенос учитывается при формировании адреса следующей микрокоманды (см. фиг. 9) либо может быть заполнен в одном из триггеров регист ра 31 признаков по фронту синхроимпульса. Поступающего с входа 25 блока. Состояние триггеров регистра 31, признаков может быть учтено при формировании адреса следующей микрокоманды (см. фиг. 9) либо через второй буферный регистр 34 с тремя состояними выдано на вход 26 блока 3 для задания значения входного пе-реноса, поступающего в операционный блок 3. Управление занесением признаков в регистр 3 признаков осуществляется нулевым и первым разрядами, поля FC микрокоманды, поступающими с входа 37 блока на вход регистра 31 признаков. Управление вьдачей признаков на выход 26 блока осуществляется вторым и третьим разрядами поля FC микро команды, поступающими с входов 37 блока на вход второго буферного регистра 34 с тремя состояними. Функции управления входными и выходными сигналами схемы признаков приведены в таблице на фиг. 10, где FC j - значение i-ro разряда поля FC микрокоманды. Второй дещифратор 6 (фиг. 4) работает следующим образом. При наличии единичного сигнала на входе 46 дешифратора (бит микрокоманды ) на всех его выходах 8-50 имеются нулевые сигналы. Управляющие сигналы на выходах 48-50 дешифратора.поя ляются при наличии нулевого сигнала на входе 46 дешифратора (бит микрокоманды ). При этом наличие еди ничных сигналов на входах 47 дешифр тора, поступающих из поля К микрокоманды, обуславливает появление уп равляющих сигналов на соответствующих выходах 48-50 дешифратора. Коммутатор 9 (фиг. 5) работает следующим образом. При наличии пост пающего из второго дешифратора 6 ед яичного сигнала на первом или второ информационных входах первой группы входов коммутатора лервый элемент ИЛИ-51 разрешает передачу информаци поступающей с соответствующих вход 56 коммутатора на вторые входы элементов И-ИЛИ 53 первой группы элеме тов И-ИЛИ, на соответствующие выход коммутатора. При отсутствии единичного сигнал на втором и третьем входах 50 комму татора на соответствующие выходы 28 коммутатора передается информация, поступающая на четвёртые входы элементов И-ИЛИ 54 второй группы элементов И-ИЛИ с соответствующих входов 55 второй группы входов коммутатора. Блок 11 формирования адреса условного перехода (фиг. 6) работает следующим образом. На входы 65 блока поступают сигналы с регистра 8 перехода. На вх i. 29 блока поступает сигнал выходного переноса из операционного блока 3. На входы 65 блока поступают сигналы с выхода первого дешифратора 5. В каждый момент времени единичный сигнал присутствует не более чем на одном входе 65 блока. Единичный сигнал, поступающий с одного из входов 65 блока, опрашивает состояние соответствующего триггера регистра 8 перехода или выходной перенос операционного блока 3. Если соответствующий триггер регистра 8 или выходной перенос установлен (имеется условие перехода), то на выходе первого элемента ИЛИ 58 установится единичный потенциал, и по спаду синхросигнала, поступающего на вход 25 блока, установится (останется в единичном состоянии) первый триггер 60. При отсутствии единичного потенциала на выходе первого элемента ИЛИ 58 (отсутствует условие перехода или условие перехода не опрашивается) по спаду синхросигнала, поступающего на вход 25 блока, первый триггер 60 не установится (сбросится). По фронту синхросигнала состояние первого триггера 60 перепишется во второй триггер 61. На вход 39 блока с выхода блока 2 микропрограммного управления поступает младший бит адреса строки, вырабатываемый вторым элементом ИЛИ 59 и поступающий на выход 66 блока 11 формирования адреса перехода (установлен второй триггер 61). Блок 10 формирования константы К (фиг. 7) работает следующим образом. Константа К, поступающая на вход 29 операционного блока, может принимать следующие значения: все единицы; все нули; содержимое поля К микрокоманды. При наличии на входе 46 блока единичного сигнала (бит микрокоманды УК-1) на вход 49 блока поступает нулевой сигнал, формируемый вторым дешифратором 6. В этом случае констан та, поступающая с выходов памяти 1 микропрограмм на входы 47 блока (содержимое поля К микрокоманды), через элементы И 67 и элементы ИЛИ 68 поступает на выходы 27 блока. При наличии на входе 46 блока нулевого сигнала (бит микрокоманды ) на вход 49 блока поступает с второго дешифратора 6 единичный или нулевой сигнал (в зависимости от содержимого бита К/М микрокоманды) и элементы И 67 формируют на выходах 27 блока соответственно константу из всех единиц или из всех нулей. Применение предлагаемого изобретения позволяет достичь существенной экономии памяти микропрограмм по сравнению с прототипом.

а.

А .

j;J7

яп -

г

п -

ЯГ5 ГЖЖ1 П I

я/|.г

af

j

J7

FC

AC

К/УУ

К/вб

IM

УО

УСТ

Фиг. 8

фиг. 9

ui. W

фиг. 11

Авторы

Даты

1984-10-15—Публикация

1982-11-26—Подача