чтения которого соединен с вторым выходом управляемого блока синхронизации, третий выход которогосоединен с входами записи регистра контрольного кода и регистра индикации, третий информационный вход схемы сравнения соединен с выходом кода имени комплекса ветвлений регистра микрокоманд, с первым входом первого блока свертки по юдулю два и с управляющим входом управляемого блока синхронизации, четвертый выход которого соединен с входом чтения блока памяти микрокоманд, с входом синхронизации триггера первого блока контроля и с входом синхронизации триггера третьего блока контроля, пятый выход управляемого блока синхронизации соединен с входом синхронизации регистра микрокоманд, выход кода микрооперации и первый выход контрольного разряда которого соединены с входами второго блока свертки по модулю два и с информационными входами выходного регистра, выход которого является управляющим выходом устройства, шестой выход управляемого блока синхронизации . соединен с первым входом элемента И третьего блока контроля, седьмой выход управляемого блока синхронизации соединен с входом синхронизации выходного регистра,выход кода маски регистра микрокоманд соединен с вторым входом первого блока свертки по модулю два, третий вход которого соединен с вторым выходом контрольного разряда регистра -микрокоманд, вход сброса которого соединен с входом сброса управляемого блока синхронизации и является входом начальной установки устройства, вход запуска устройства подключен к входу пуска управляемого блока синхронизации, группа выходов регистра индикации соединена с первыми входами элементов И группы первого блока контроля и элементов ИЛИ первой группы первого блока контроля, выходы первого и второго блоков свертки по модулю два соединены соответственно с первым и вторьм входами первого элемента ИЛИ второго блока контроля, выход которого соединен с вторым входом элемента И второго блока контроля, выход которого соединен с первым входом второго элемента ИЛИ второго блока контроля, второй вход которого соединен с входом элемента задержки первого блка контроля и с выходом триггера первого блока контроля, вход устаноки в О которого соединен с выходом элемента задержки первого блока контроля, выход триггера третьего блока контроля соединен с входом элемента задержки третьего блока контроля и с третьим входом второго элемента ИЛИ второго блока контроля выход которого является выходом индикации неисправности устройства, выход несравнения схемы сравнения соединен с информационным входом триггера третьего блока контроля, вход установки в О которого соединен с выходом элемента задержки третьего блока контроля, второй вход первого элемента ИЛИ первой группы первого блока контроля, второй вход первого элемента И группы первого блока контроля и первый вход первого элемента ИЛИ второй группы первого блока контроля подключены к шине нулевого потенциала, второй вход i-ro (i .2,.3,... ,n) элемента ИЛИ первой группы первого блока контроля и второй вход i-ro элемента.И группы первого блока контроля подключены к выходу (i-l)-ro элемента ИЛИ первой группы первого блока контроля, выход первого элемента И группы первого блока контроля соединен с вторым входом первого элемента ИЛИ второй группы первого блока контроля, первый вход i-ro элемента ИЛИ второй;- группы первого блока контроля соединен с выходом (i-1)-ro элемента ИЛИ второй группы первого блока контроля, выход i-ro элемента И группы первого блока контроля соединен со вторым входом 1-го элемента .ИЛИ -второй группы первого блока контроля, выходы п-го элемента ИЛИ первой группы первого блока контроля и п-го элемента ИЛИ второй группы первого блока.контроля соединены соответственно с первым и BTOpbw входами элемента И первого блока контроля , выход которого соединен с информационным входом триггера первого блока крнтроля.

2. Устройство по п.1,.о т л ичающееся тем, что управляемый блок синхронизации содержит i дешифратор, шифратор, распределитель импульсов, счетчик, два Ж-триггера, генератор тактовых им пульсов, четыре элемента ИЛИ, три элемента И, четыре элемента задержки и шесть формирователей импульсов, причем первые входы первого и второго элементов ИЛИ и вход установки в О счетчика подключены к входу начальной установки блока, выход первого элемента ИЛИ соединен с К входом первого Ж-триггера выход которого соединен с первым входом первого элемента И, второй вход которого соединен свыходом генератора тактовых импульсов и с входом распределителя импульсов, первый и второй выходы которого соединены с первыми входами соответственно второго и третьего элементов И, вторые входы которых соединены с выходом второго Ж-триггера, I- и К-входы которого соединены соответственно с -выходами третьего и второго элементов ИЛИ, выход первого элемента И соединен со счетным входом счетчика, информационный вход которого соединен с выходом шифратора, вход которого соединен с выходом дешифратора, входы которого являются управляющими входами

блока, выход второго элемента И соединен с входами первого формирователя импульсов и, первого и второго элементов задержки, выход третьего элемента И соединен с входами второго формирователя импульсов и третьего и четвертого элементов задержки, выходы первого, второго и четвертого элементов задержки соединены соответственно с входами третьего, четвертого, пятого и шестого формирователей импульсов, выходы первого, второго, третьего, четвертого, пятого и шестого формирователей импульсов являются соответственно первым, вторым, третьим, четвертым, пятым и шестьтм выходами блока, выход переполнения счетчика соединен с вторым входом первого элемента ИЛИ и с первым входом третьего элемента ИЛИ, второй вход которого является входом пуска

блока, информационные -входы счетчика соединены с входами четвертого элемента ИЛИ, выход которого является седьмым выходом блока, выход шестого формирователя импульсов соединен с входом первого JK-триггера и с вторым входом второго элемента ИЛИ, выход пятого формирователя импульсов соединен с входом синхронизации счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1043650A2 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Параллельное микропрограммное устройство управления | 1983 |

|

SU1109750A1 |

| Микропрограммное устройство управления и отладки микропрограмм процессора | 1984 |

|

SU1168937A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

1. МИКРОПРОГРАММНОЕ УСТ.РОЙСТВО УПРАВЛЕНИЯ, содержащее - блок памяти микрокоманд, регистр микрокоманд, блок ассоциативной памяти признаков ветвления, регистр маски, регистр признаков ветвления, регистр индикации, причем первый информационный вход регистра маски является входом маски устройства, второй информационный вход регистра маски соединен с выходом кода маски регистра микрокоманд, информационный вход которого соединен с выходом блока памяти микрокоманд, группа адресных входов которого соединена с группой выходов регистра индикации, информационный вход которого соединен с первым выходом блока ассоциативной памяти признаков ветвления, информационный вход которого соединен с выходом регистра признаков ветвления, первый и второй информационные входы которого соединены соответственно с выходом регистра маски и с выходом кода имени комплекса ветвлений регистра микрокоманд, отличающееся тем, что, с целью повьшения достоверности функционирования устройства, оно содержит регистр -контрольного кода, схему сравнения, первый блок контроля, содержащий две группы по п элементов ИЛИ (где п - разрядность регис-тра индикации), группу элементов И, элемент задержки, элемент И и триггер, второй блок контроля, содержащий два элемента PfflH и элемент И, два блока свертки по (Л модулю два, выходной регистр, блок регистрации условий, управляемый блок синхронизации и третий блок контроля, содержащий триггер, элемент задержки и схему сравнения, причем первый информационный вход блока регистрации условий соединен с оь выходом кода маски регистра микро4 команд, второй информационный вход . блока регистрации условий соединен о с входом условий устройства, перОд вый выход управляемого блока синхронизации соединен с входом записи регистра признаков ветвления и управляющим входом блока регистрации условий, выход которого соединен с первым информационным входом схемы сравнения, второй информационный вход которой соединен с выходом регистра контрольного кода, информационный вход которого соединен с вторым выходом блока ассоциативной .памяти признаков ветвления, вход

Изобретение относится к цифровой вычислительной технике и автоматике и быть использовано в микропрограммных устройствах управления вычислительных машин.

Цель изобретения - повышение . достоверности функционирования.

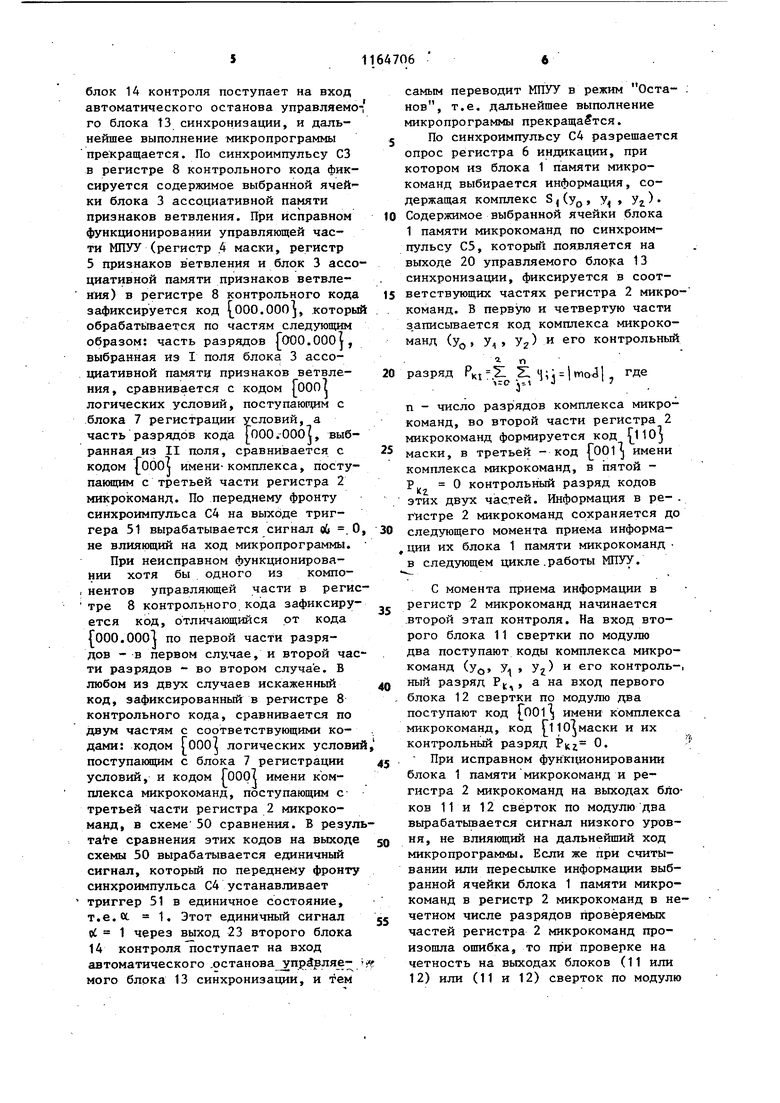

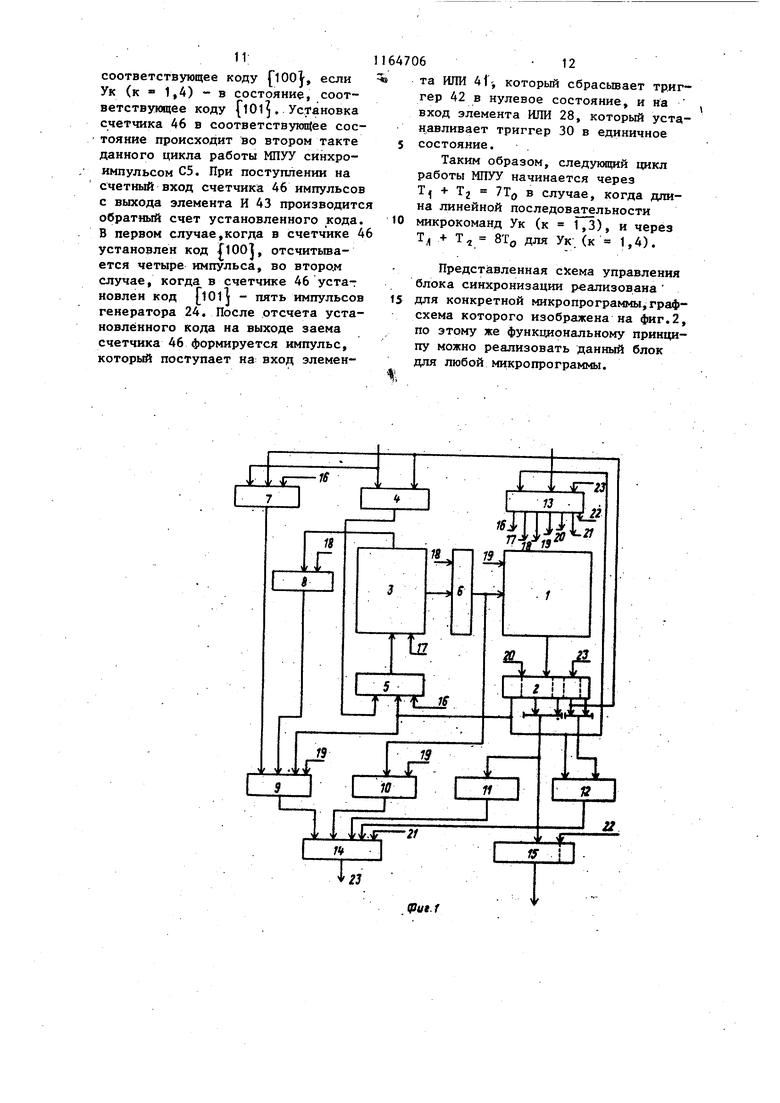

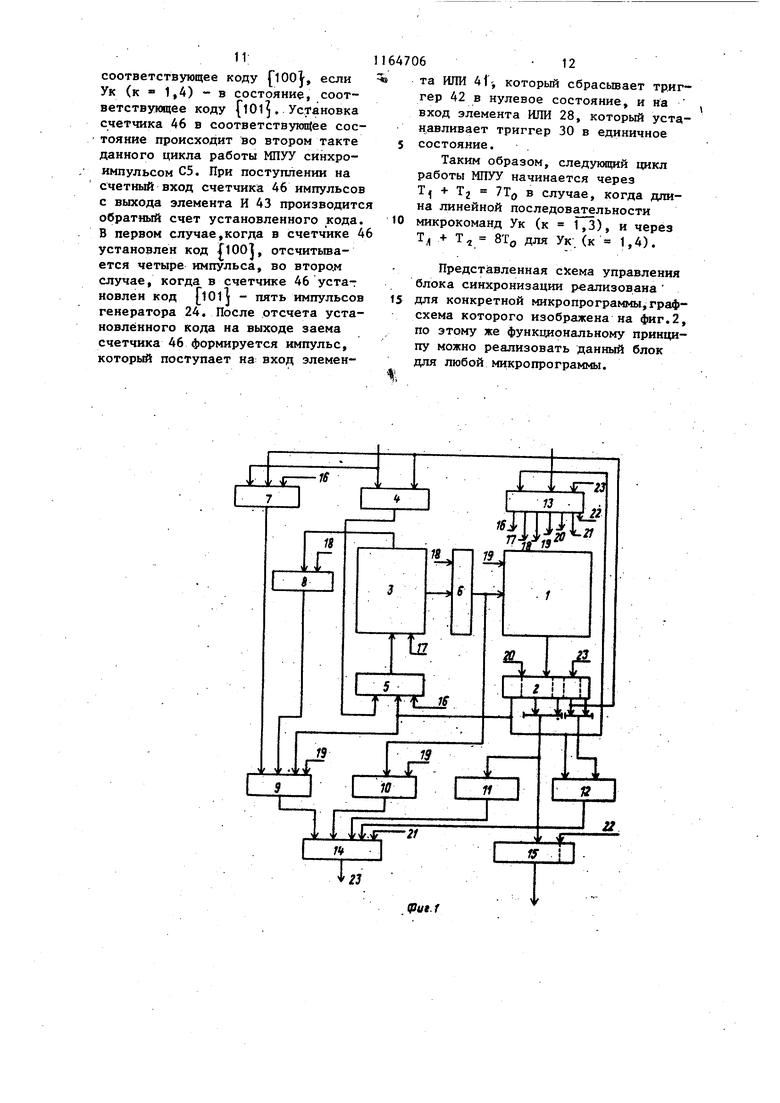

На приведена структурная схема предлагаемого устройства фиг.2 - граф-схема корректной микропрограммы на фиг;3 - таблица содержимого блока памяти микрокоманд на фиг.4 - таблица содержимого блока ассоциативной памяти признаков ветвления;- на фиг.5 - функциональная схема управляемого блока синхронизации; на фиг.6 - то.же, блока регистрации условий; на

фиг.7 - то же, третьего блока контроля; на фиг. 8 - то же, первого блока контроля; на фиг.9 - то же, второго блока контроля; на фиг.10 диаграмма следования синхроимпульсов управляемого блока синхронизации.

Микропрограммное устройство управления (фиг.1) содержит блок 1

памяти микрокоманд, регистр 2

микрокоманд, блок 3 ассоциативной памяти признаков ветвления, регистр 4 маски, регистр 5 признаков ветвления, регистр 6 индикации, блок 7

регистрации условий, регистр 8 контрольного кода, третий блок 9

контроля, первый блок 1о контроля, второй блок 11 свертки по модулю

. 3Г)

ва, первый блок 12 свертки по одулю два, управляемьп блок 13 синхронизации, второй блок 14 конроля, выходной регистр 15, выхоы 16-22 управляемого блока синронизации и выход 23 второго блоа контроля.

Каждая ячейка блока 1 памяти икрокоманд состоит из пяти полей: в первом поле хранятся коды 1 икрооманд/ во втором - коды маски; в третьем - код имени комплекса икрокоманд; в четвертом поле четвертый разряд, который дополняет сумму единиц соответствующих ячеек первого поля до нечетностиJ в пятом поле - контрольньгй разряд, который дополняет сумму единиц соответствуюш их ячеек второго и третьего полей до нечетности.

Управляющий блок синхронизации содержит (фиг,5) генератор 24 тактовых импульсов, распределитель 25 импульсов, второй 26 и третий 27 элементы И, третий 28 и второй 29 элементы ИЛИ, второй IK триггер 30, первый 31, третий 32, четвертый 33, второй 34, пятый 35, шестой 36 формирователи импульсов, первый 37, второй 38, третий 39 и четвертый 40 элементы задержки, первый элемент ИЛИ 41, первый IK триггер 42, первый элемент И 43, дешифратор 44, шифратор 45,, счетчик 46 и четвертый элемент ИЛИ 47.

Блок регистрации условий (фиг.6) содержит группу элементов И 48, группу D-триггеров 49.

Третий блок контроля (фиг.7) содержит схему сравнения 50, триггер 51 и элемент задержки 52.

Первый блок контроля (фиг.8) содержит первую группу элементов ИЛИ 53, вторую группу элементов ИЛИ 54, группу элементов И 55, элемент И 56, элемент задержки 57 и триггер 58.

Второй блок контроля (фиг.9) содержит первый элемент ИЛИ 59,второй элемент ИЛИ 60 и элемент И 61.

Работу микропрограммного устройства управления МПУУ рассмотрим на примере выполнения микропрограммы, из ражен ной на фиг. 2, где yi (i 0,17) - управляющая часть микрокоманды, а SJ (J 0,7) - имя комплекса микрокоманд, коды которой выбираются за одно обращение к блоку .памяти микрокоманд и обрабаты64

ваются последовательно в порядке, диктуемом микропрограммой. Размещение микропрограмм. в блоке памяти микрокоманд и в блоке ассодиативной памяти микрокоманд и в блоке ассоциативной памяти признаков изображено на фиг.З и фиг.4 соответственно. Каждая ячейка блока ассоциативной памяти признаков (фиг.З)

состоит из двух полей: поле I предназначено для хранения значений логических условий Р, Р„, Р, поле II - для хранения кода имени комплекса микрокоманд.

Разряды второй и третьей частей регистра 2 микрокоманд находятся в начальный момент времени в состоянии О. В начальный момент времени запускается блок 13, чем под-

готавливается микропрограммное

устройство управления (МПУУ) к работе. По первому синхроимпульсу С1, который появляется на выходе 16 управляемого блока 13 синхронизации, все разряды регистра 5 признаков ветвления, блока 7 регистрации условий перебрасьшаются в состояние О. По синхроимпульсу С2, который появляется на выходе 17 управляемого блока 13 синхронизации, производится сравнение содержимого регистра 5 признаков ветвления и содержимого блока 3 ассоциативной признаков ветвления и вырабатывается единичный сигнал совпадения с содержимым первой ячейки блока 3.ассоциативной памяти призлаков ветвления. По синхроимпульсу СЗ-, который появляется на выходе 18 .

управляемого блока 13 синхронизации, единичный сигнал совпадения устанавливает в единичное состояние триггер регистра 6 индикации, соответствующий первой ячейке памяти 1 микрокоманд.

С установкой кода состояния МПУУ в регистре 6 индикации начинается первый этап контроля посредством первого блока 10 контроля. На входы X,-Х первого блока 10 контроля

поступает код flOOOOnnZ, установленный в регистре 6 индикации. При появлении лишней единицы в регистре 6 индикации на выходе первого блока 10 контроля по переднему фронту

синхроимпульса С4, который появляется на вьпсоде 19 управляемого блока 13 синхронизации, формируется сигнал , который через второй блок 14 контроля поступает на вход автоматического останова управляемо го блока 13 синхронизации, и дальнейшее выполнение микропрограммы прекращается. По синхроимпульсу СЗ в регистре 8 контрольного кода фиксируется содержимое выбранной ячейки блока 3 ассоциативной памяти признаков ветвления. При исправном функционировании управляющей части МПУУ (регистр 4 маски, регистр 5 признаков ветвления и блок 3 ассо циативной памяти признаков ветвле кия) в регистре 8 контрольного кода зафиксируется код 000.000J, которы обрабатьгеается по частям следующим образом: часть разрядов fCTOO.OOOV, выбранная из I поля блока 3 ассоциативной памяти признаков ветвления, сравнивается с кодом ГООО логических условий, поступаюрщм с .блока 7 регистрации условий, а часть разрядов кода ООО.-ООО, выбранная из II поля, сравнивается с кодом fOOOs имени-комплекса, поступающим с третьей части регистра 2 микрокоманд. По переднему фронту синхроимпульса С4 на выходе триггера 51 вырабатывается сигнал oG .0 не влияющий на ход микропрограммы. При неисправном функционировании хотя бы одного из компо, нентов управляющей части в регис тре 8 контрольного кода зафиксируется код, отличающийся от кода f000.000 по первой части разрядов - в первом случае, и второй час ти разрядов - во втором случае. В любом из двух случаев искаженный код, зафиксированный в регистре 8 контрольного кода, сравнивается по двум частям с соответствующими кодами: кодом ООО логических услови поступакяцим с блока 7 регистрации Г Т условий, и кодом |000( имени комплекса микрокоманд, поступающим с третьей части регистра 2 микрокоманд, в схеме50 сравнения. В резул таге сравнения этих кодов на выходе схемы 50 вырабатывается единичный сигнал, который по переднему фронту синхроимпульса С4 устанавливает триггер 51 в единичное состояние, т.е. ос 1. Этот единичный сигнал сС 1 через выход 23 второго блока 14 контроля поступает на вход автоматического .останова управляемого блока 13 синхронизации, и тем самым переводит МПУУ в режим Оста- . нов, т.е. дальнейшее выполнение микропрограммы прекращается. По синхроимпульсу С4 разрешается опрос регистра 6 индикации, при котором из блока 1 памяти микрокоманд выбирается информация, содержащая комплекс S (YQ У Уг ) Содержимое выбранной ячейки блока 1 памяти микрокоманд по синхроимпульсу С5, которьп появляется на выходе 20 управляемого блока 13 синхронизации, фиксируется в соответствующих частях регистра 2 микрокоманд. В первую и четвертую части з.аписывается код комплекса микрокоманд (у, у, у) и его контрольный разряд PKI .11 Z1 Ч; j 1 тоЛ где п - число разрядов комплекса микрокоманд, во второй части регистра 2 микрокоманд формируется код l10 маски, в третьей - код {001 имени комплекса микрокоманд, в пятой Р. 0 контрольный разряд кодов этих двух частей. Информация в ре- . г истре 2 микрокоманд сохраняется до следующего момента приема информации их блока 1 памяти микрокоманд в следующем цикле.работы МПУУ. С момента приема информации в регистр 2 микрокоманд начинается .второй этап контроля. На вход второго блока 11 свертки по модулю два поступают коды комплекса микрокоманд (уд, у. , у,) и его контроль-, ный разряд Pj,, а на вход первого блока 12 свертки по модулю два поступают код о01 имени комплекса микрокоманд, код | 110 маски и их контрольный разряд О При исправном функционировании блока 1 памяти микрокоманд и регистра 2 микрокоманд на выходах блоков 11 и 12 сверток по модулю два вырабатывается сигнал низкого уровня, не влияющий на дальнейший ход микропрограммы. Если же при считывании или пересылке информации выбранной ячейки блока 1 памяти микрокоманд в регистр 2 микрокоманд в нечетном числе разрядов проверяемых частей регистра 2 микрокоманд произошла ошибка, то при проверке на четность на выходах блоков (11 или 12) или (11 и 12) сверток по модулю 7 два вьфабатьшается единичный сигнал оигибки. Единичные сигналы ошибок с выходов блоков(11 О 12) или (11 и 12) св ерток по модулю два поступают на входы элемента 59 ИЛИ второго блока 14 контроля и по синхроимпульсу Сб, который появляется ТТа выходе 21 управляемого блока 13 синхронизации, ошибочный единичный сигнал проходит на-вых;од 23 второго блока 14 контроля, который в свою очередь поступает на вход автоматическогоостанова управляемо го блока 13 синхронизации, что пере водит МПУУ в режим Останов, т.е. прекращается дальнейшее выполнение микропрограмм. При неисправном функционировании МПУУ средствами ко троля вырабатывается сигнал ошибки который через выход 23 второго блок 14 контроля переводит управляемый блок 13 синхронизации в состояние Останов, и тем самым блокируется пересылка комплекса (у, у , Уг) микрокоманд с его контрольным разрядом, С момента приема кода значений логических условий на вход регистра 4 маски и выработкой синхроимпульса С1 начинается новый цикл работы МПУУ. Пусть значения логических условий, влияющих на траекторию выполнения микропрограммы,в данный момент имеют значения Р( PJ 0, значение РЗ безразлично. На соответствующих вторых входах регистра 4 маски и блока 7 регистра ции условий находится код {lЮj ма ки, зафиксированной во второй части регистра 2 микрокоманд предыдущим циклом работы МШТ. В этом случае по синхроимпульсу С1 в блоке 7 регистрации условий и в первой части регистра 5 признаков ветвления фиксируется комбинация кода ЮО логических условий, а во второй ча ти регистра 5 признаков ветвления код {001j имени комплекса микрокоманд, который поступает с третье части регистра 2 микрокоманд. По синхроимпульсу С2 производится сра нение содержимого регистра 5 признаков ветвления с содержимым блока 3 ассоциативной памяти признаков ветвления, в результате чего вьфабатывается единичный сигнал совпадения в третьей ячейке блока ассоциативной памяти признаков 68 ветвления. По синхроимпульсу СЗ в регистре 6 индикации фиксируется код 001.ОООО состояния МПУУ, а в регистре 8 контрольного ко.да код ЮО.OOl содержимого третьей ячейки блока ассоциативной памяти призна1сов. С этого момента начинается первый этап контроля данного цикла работы МПУУ. На соответствующие входы XQ-X первого блока 10 контроля поступает код О01.0000 состояния МПУУ. Если в регистре 6 индикации отображено более одного состояния МПУУ,то на выходе первого блока 10 контроля вырабатьшается сигнал ошибки / 1, который через соответствующий вход элемента 60 ИОД и его выход 23 переводит МПУУ в режим Останов, в противном случае р О, который не влияет на дальнейший ход микропрот-раммы. Комбинация кода р00 .логических условий зафиксирована в триггерах 48 следующим образом: a1 1, а2 О, аЗ. О, - выходные сигналы триггеров 48 поступают на соответствующие входы схемы 50 сравнения. На первые входы схемы 50 сравнения поступает код Г001 имени комплекса микрокоманд с третьей части регистра 2 микрокоманд.. На вторые . входы схемы 50 сравнения поступает код П00.ООН, зафиксированный в регистре 8 контрольного кода. В случае неисправной работы управляющей части (регистра 4 маски, регистра 5 признаков ветвления и блока 3 ассоциативной памяти приз- на.ков ветвления МПУУ) по синхроимпульсу С4 в триггере 51 вьфабатывается сигнал ошибки и 1. Этот сигнал через соответствующий вход элемента 60 ШШ и его выход 23 переводит МПУУ в режим Останов путем блокировки выработки синхро- импу тьсов управляемого блока 13 синхронизации. В случае исправной работы р О, что не влияет на дальнейший ход микропрограммы, по синхроимпульсу С4 разрешается опрос регистра 6 индикации, при котором из блока 1 памяти микрокоманд выбирается информация, содержащая следующий комплекс микрокоманд (у УЗ, Уд) который выполняется после комплекса (ур, у, у) при значениях логических условий Р 1, Р О,значение Р безразлично. Дальнейшая работаи контроль проходит аналогично предыдущему циклу работы и контроля МПУУ. Таким образом, на первом этапе .контроля при помопщ блока 7 регист рации условий, регистра -8 контроль ного кода, схемы 50 сравнения, первого 10 и третьего 24 блоков контроля выявляются все ошибки управляющей части (регистр 4 маски, регистр 5 признаков ветвления и блок 3 ассоциативной памяти призна ков ветвления) и контролируется од нозначность состояния МПУУ. Управляющая часть контролируется путем сравнения содержимого выбранной ячейки из блока 1 ассоциативной памяти признаков ветвления с его входными атрибутами: кодом логичес ких условий, который фиксируется блоке 7 регистрации условий, и кодом имени Sj комплекса микрокоманд, зафиксированным в третьей части регистра 2 микрокоманд. Однозначность состояния МПУУ отсгбражается в регистре 6 индикации, проверяется при помощи первого бло ка 10 контроля. На втором этапе контроля при помощи первого и втор го блоков 12 и 11 свертки по модул два выявляются ошибки хранения и пересылки в информационной части МПУУ (блок 1 памяти микрокоманд и регистр 2 микрокоманд), Управляемый блок 13 синхрониза.-ции работает следующим образом. В начешьный момент времени по второму входу управляемого блока 13 синхронизации сигналом Пуск чере элемент 28 ИЛИ устанавливают в сое тоялие 1 триггер 30, единичный в ход которого соединен с первыми . входами элементов 26 и 27 И, вторы входы которых соединены соответственно с первым и вторым выходами распределителя импульсов .25 (РИ), вход которого соединен с выходом генератора 24. Распределитель импульсов 25 образует две последовательности импульсов. Период Т и длительность импульсов, вырабатываемых генератором 24, выб ираются в зависимости от элементной базы МПУУ и параметров объекта управления. По первому импульсу с генератора 24 с момента пуска МПУУ единичный импульс с выхода элемента 2 И поступает на входы формирователя . (Ф1) импульсов и элементов 37 и 31 задержки.Выходы элементов 37 и 38 38 задержки соединены с входами формирователей 32 и 33 (Ф2-ФЗ) синхроимпульсов соответственно. По второму импульсу с генератора 24 единичный импульс с выхода 27 И поступает на входы формирователя 34 (Ф4) и элементов 39 и 40 задержки. Выходы элементов 39 и 40 задержки, соединены .с входами формирователей 35 и 36 (Ф5-Ф6) импульсов. Выходы формирователей 31-36 (Ф1-Ф6) синхроимпульсов являются выходами 16-21 управляемого блока 13 синхронизации. Таким образом, по первому импульсу генератора 24 вырабатывается последовательность синхроимпульсов С1-СЗ, по второму - последовательность синхроимпульсов С4-С6. Синхро-. импульсы С1-С6 вьфабатьгоаются за такт Т 4 2Тд, временная диаграмма следования которых представлена на фиг.10. Выход 21 формирователя 36 синхроимпульсов соединен с объединенными входами элемента 29 ИЛИ и триггера 42, С выработкой синхроим- пульсов С6 перебрасывается в нулевое состояние триггер 30 и устанавливается в единичное состояние триггер 42, выход которого--соединен с первым входом элемента И 43, второй вход которого соединен с выходом генератора 24, в результате прекращается вьфаботка синхроимпульсов С1-С6 и запускается вторая часть блока. . На входы дешифратора 44 поступает код имени комплекса Sj микрокоманд yi от третьей части регистра 2 микрокоманд, который необходимо выполнить в данном цикле работы МПУУ. На выходе дешифратора 44 возбуясдается только один выход, соответствуюпщй коду имени комплекса микрокоманд. Сигнал с выхода дешифратора 44 поступает на вход шифратора 45, на выходе которого в зависимости от линейной длины последовательности микроком нд вьфабатываются сигналы для установки счетчика 46 в состояние, соответствующее коду {ЮО или 101. Если линейная последовательность микрокоманд УК (к 1,3), где к - число микрокоманд последовательности микрокоманд, то счетчик 46 устанавливается в состояние.

11

соответствующее коду , если УК (к 1,4) - в состояние, соответствующее коду {l015. Установка счетчика 46 в соответствуюп{ее состояние происходит во втором такте данного цикла работы МПУУ синхроимпульсом С5. При поступлении на счетный вход счетчика 46 импульсов с выхода элемента И 43 производится обратный счет установленного кода. В первом случае,когда в счетчике 46 установлен код XlOOJ, отсчитьшается четыре импульса, во втором случае, когда в счетчике 46 установлен код l01 - пять импульсов генератора 24. После отсчета установленного кода на выходе заема счетчика 46 формируется импульс, который поступает на вход элемен64706-12

та ИЛИ 41j который сбрасьшает триггер 42 в нулевое состояние, и на вход элемента ИЛИ 28, который устанавливает триггер 30 в единичное 5 состояние.

Таким образом, следукнций цикл работы МПУУ начинается через

7Т

Т, + Т(J в случае, когда длина линейной последовательности

10 микрокоманд УК (к 1,3), и через

Т 8То для УК. (к 1,4).

Представленная схема управления блока синхронизации реализована 15 для конкретной микропрограммы,графсхема которого изображена на фиг.2, по этому же функциональному принципу можно реализовать данный блок для любой микропрограммы.

фиг. 2

с ffoffett J

Ж

Ж

Фил.З

0;

h

УГ

Sj

Sj

S7 .Sf

.S7

Фие.

fpuz.5

Вход втотй

Y «У 62 у ffjY аг ai I Y I У 1 Y I Т I Y I Т

f19(Citj

02

Вход третий (1$)

фиг.В

«L

Фиг,7

(pa г. 8

То

tu

п

(Риъ.9

| Микропрограммное устройство управления | 1974 |

|

SU537346A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельств.о СССР | |||

| Микропрограммное устройство управления | 1981 |

|

SU951307A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1977 |

|

SU723572A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| .. | |||

Авторы

Даты

1985-06-30—Публикация

1983-05-26—Подача