Изобретение относится к вычислительной технике, а именно к синхронизируемым вычислительным системам.

Цель изобретения - расширение функциональных возможностей за счет .обеспечения переменного периода синхросигналов в нечетные и четные такты работы устройства для каждого канала.

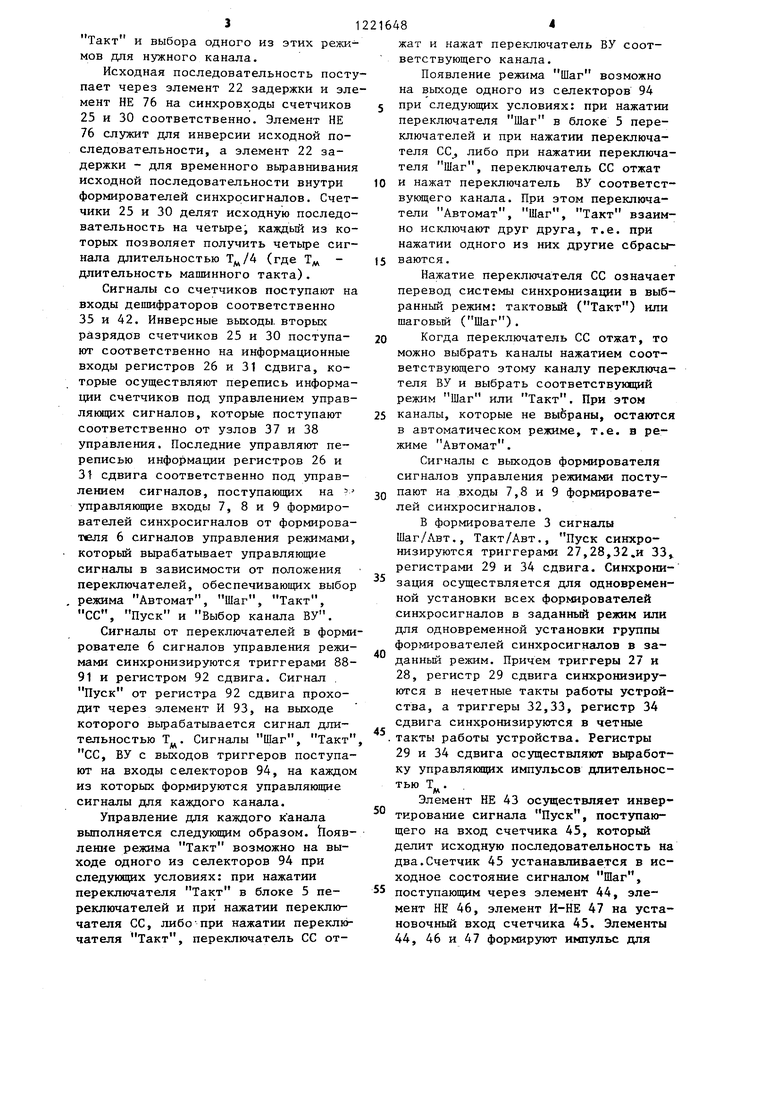

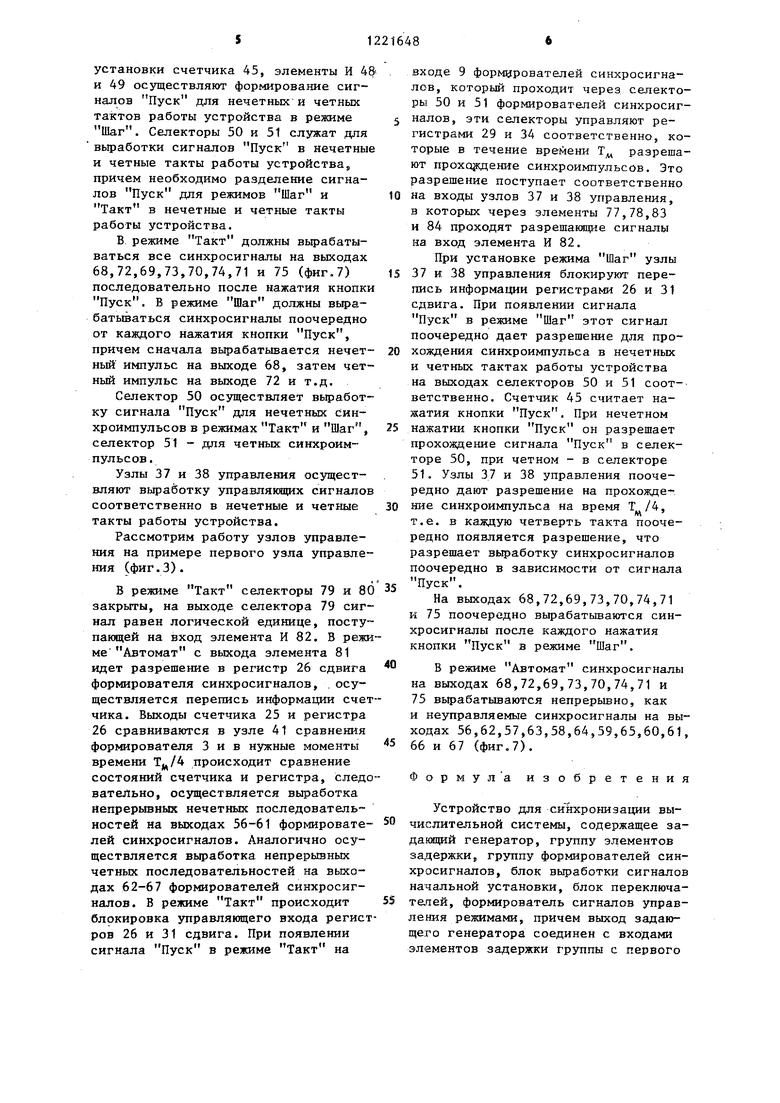

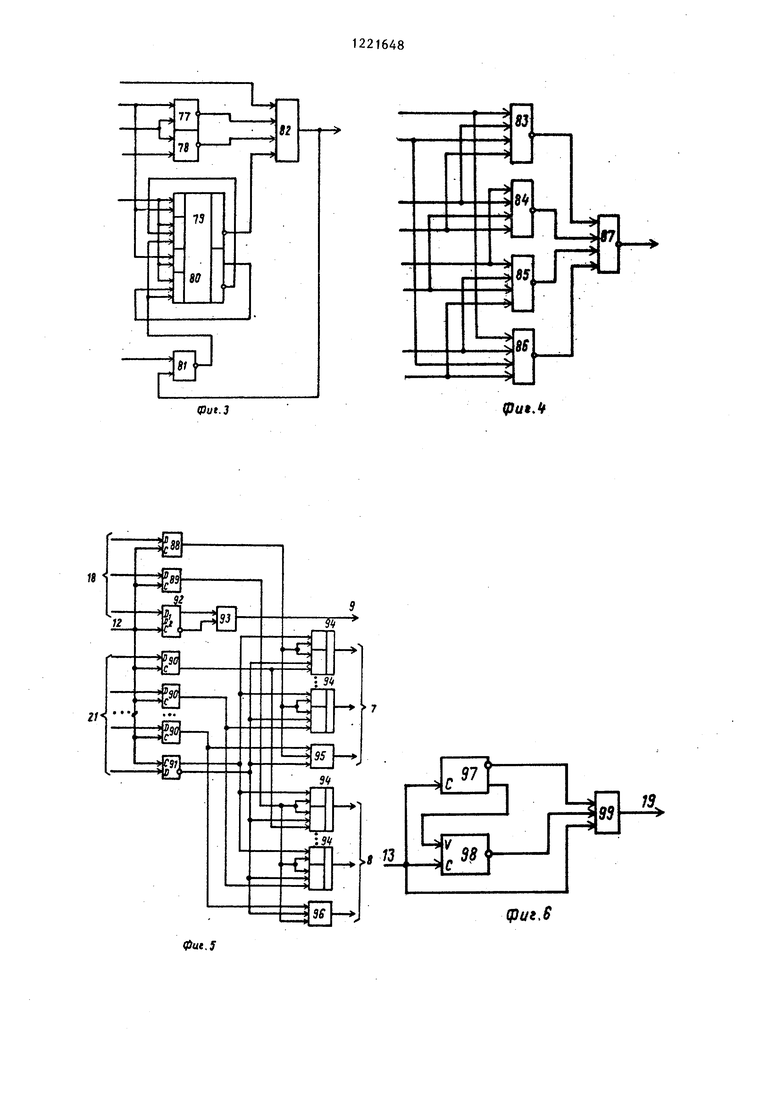

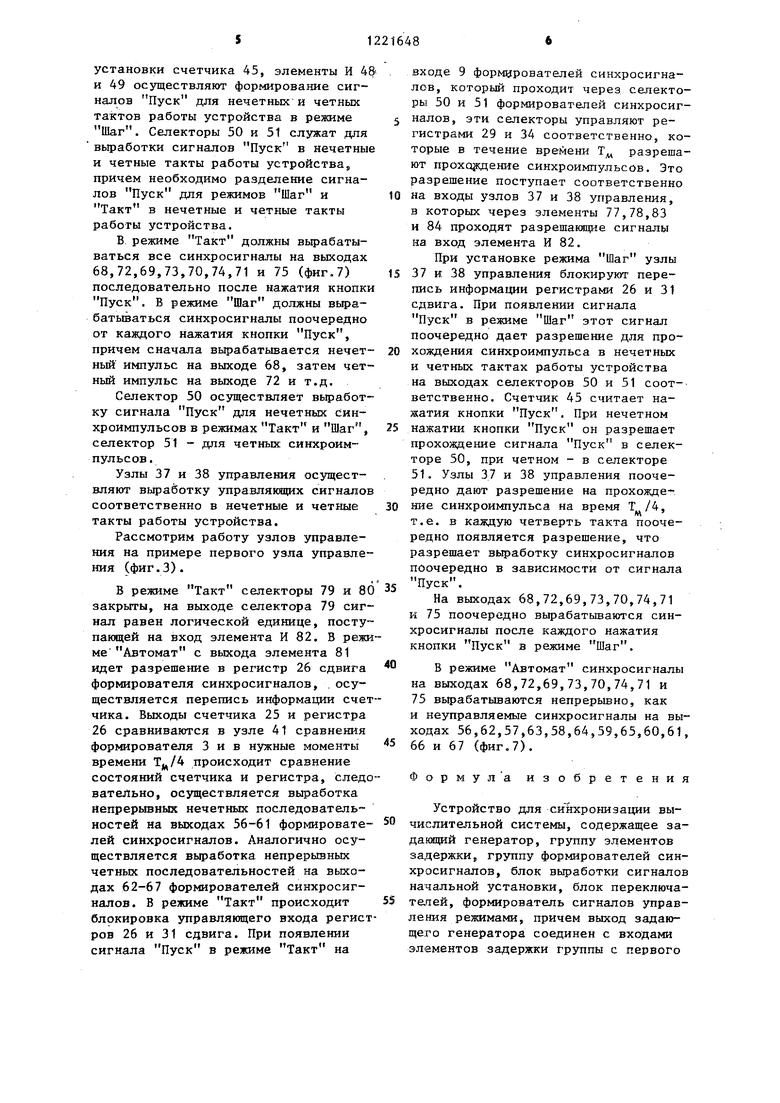

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - схема формирователя синхросигналов; на фиг. 3 - схема узла управления; на фиг. 4 - схема узла сравнения; на фиг. 5 - схема формирователя сигна- лов управления режимами; на фиг,6 - схема, блока выработки сигналов начальной установки; на фиг. 7 - временная диаграмма синхросигналов, вырабатываемая формирователем син- хросигналов.

Устройство содержит задающий генератор 1, группу элементов 2 задержки, группу формирователей 3 синхросигналов, блок 4 выработки сигналов начальной установки, блок 5 переключателей, формирователь 6 сигналов управления редимами,управляющие входы 7,8 и 9 форьшрователей синхросигналов, синхровходы to формирователей синхросигналов,установочные входы 1 формирователей синхросигналов, син- хровход 12 формирователя сигналов управления режимами, вход 13 блока выработки сигналов начальной установки, группы 14,15,16 и 17 выходов формирователей синхросигналов, первую группу 18 информационных входов формирователя сигналов управления режимами, группу 19 выходов блока выработки сигналов начальной установки, выход 20 задающего генератора, вторую группу 21 информационных входов формирователя сигналов управления режимами.

Формирователь 3 синхросигналов содержит элемент 22 задержки, элемент И-НЕ 23, элемент И-НЕ 24, сч ет- .чик 25, регистр 26 сдвига, триггеры 27 и 28, регистр 29 сдвига, счетчик 30, регистр 31 сдвига,триггеры 32 и 33, регистр 34 сдвига, дешифратор 35, селектор 36, узел 37 управления, узел 38 управления, селектор 39, узлы 40 и 41 сравнения, дешифратор 42, элемент НЕ 43, элемент 44 задержки, счетчик 45, элемент НЕ 46, элемент И-НЕ 47, эле

0 5 0

5 0

5

5

0

мект И 48, элемент И 49, селектор 50, селектор.51, группы элементов И 52-55, выходы 56-61 элементов И 52, выходы 62-67 элементов И 53, выходы 68-71 элементов И 54, выходы 72-75 элементов И 55, элемент НЕ 76.

Узлы 37 и 38 управления содержат элементы И-НЕ 77 и 78, селекторы 79 и 80, элемент И-НЕ 81 и элемент И 82.

Узлы 40 и 41 сравнения, содержат элементы И-НЕ 83-87.

Формирователь 6 сигналов управления режимами содержит первьй триггер 88, второй триггер 89, триггеры с третьего по (и+2)-й 90, (м+3)-й триггер 91, регистр 92 сдвига, элемент И 93, селекторы 94, элементы И 95 и 96.

Блок 4 выработки сигналов начальной установки содержит счетчики 97 я 98 и элемент И 99.

Устройство работает следующим образом.

Задающий генератор 1 вырабатывает исходнзпо последовательность, по- сту1такмцую через элементы 2 задержки, слузкащие для выравнивания синхросигналов, на входы 10 формирователей 3 сишфосигналов.

Исходная последовательность синхросигналов поступает также на вход 13 блока 4 выработки сигналов начальной установгсн, счетчики 97 и 98 которого делят исходную последовательность соответственно на два и четыре, элемент И 99 блока выработки сигналов начальной установки вырабатывает сигнал начальной установки.

Сигналы начальной установки поступают через элементы 2 задержки, слу- жащн;е также для вьфавнивания сигналов начальной установки, на вход 11 формирователей синхросигналов.

Сигналы начальной установки в формирователях синхросигналов через элементы И-НЕ 23 и 24 поступают на входы начальной установки соответственно счетчиков 30 и 25 синхросигналов. Выравнивание этих сигналов осуществляется для обеспечения одновременной установки в исходное состояние счетчиков 25 и 30 всех формирователей 3 синхросигналов.

В начале работы устройства в блоке 5 переключателей последние устанавливаются в состояние, необходимое 5гля задания режима Автомат, Шаг,

3

Такт и выбора одного из этих режимов для нужного канала.

Исходная последовательность поступает через элемент 22 задержки и элемент НЕ 76 на синхровходы счетчиков 25 и 30 соответственно. Элемент НЕ 76 служит для инверсии исходной последовательности, а элемент 22 задержки - для временного выравнивания исходной последовательности внутри формирователей синхросигналов. Счетчики 25 и 30 делят исходную последовательность на четыре; каждьш из которых позволяет получить четыре сигнала длительностью (где Т - длительность машинного такта) .

Сигналы со счетчиков поступают на входы дешифраторов соответственно 35 и 42. Инверсные выходы, вторых разрядов счетчиков 25 и 30 поступают соответственно на информационные входы регистров 26 и 31 сдвига, которые осуществляют перепись информации счетчиков под управлением управляющих сигналов, которые поступают соответственно от узлов 37 и 38 управления. Последние управляют переписью информации регистров 26 и 3t сдвига соответственно под управлением сигналов, поступающих на управляющие входы 7, 8 и 9 формирователей синхросигналов от формирователя 6 сигналов управления режимами, который вырабатывает управляющие сигналы в зависимости от положения переключателей, обеспечивающих выбор режима Автомат, Шаг, Такт, СС, Пуск и Выбор канала ВУ.

Сигналы от переключателей в форми рователе 6 сигналов управления режимами синхронизируются триггерами 88- 91 и регистром 92 сдвига. Сигнал , Пуск от регистра 92 сдвига проходит через элемент И 93, на выходе которого вырабатывается сигнал длительностью Т . Сигналы Шаг, Такт СС, ВУ с выходов триггеров поступают на входы селекторов 94, на каждом из которых формируются управляющие сигналы для каждого канала.

Управление для каждого к анала выполняется следуклцим образом. Появление режима Такт возможно на выходе одного из селекторов 94 при следующих условиях: при нажатии переключателя Такт в блоке 5 переключателей и при нажатии переклю чателя СС, либо при нажатии переключателя Такт, переключатель СС от21648

жат и нажат переключатель ВУ соответствующего канала.

Появление режима Шаг возможно на выходе одного из селекторов 94

5 при следующих условиях: при нажатии переключателя Шаг в блоке 5 переключателей и при нажатии переключателя СС, либо при нажатии переключателя Шаг, переключатель СС отжат

10 и нажат переключатель ВУ соответствующего канала. При этом переключатели Автомат, Шаг, Такт взаимно исключают друг друга, т.е. при нажатии одного из них другие сбрасы(5 ваются.

Нажатие переключателя СС означает перевод системы синхронизации в выбранный режим: тактовый (Такт) или шаговьм (Шаг).

20 Когда переключатель СС отжат, то можно выбрать каналы нажатием соответствующего этому каналу переключателя ВУ и выбрать соответствующий режим Шаг или Такт. При этом

25 каналы, которые не выёраны, остаются в автоматическом режиме, т.е. в режиме Автомат.

Сигналы с выходов формирователя сигналов управления режимами посту3Q пают на входы 7,8 и 9 формирователей синхросигналов.

В формирователе 3 сигналы Шаг/Авт., Такт/Авт., Пуск синхронизируются триггерами 27,28,32,и 33 регистрами 29 и 34 сдвига. Синхрони- зация осуществляется для одновременной установки всех формирователей синхросигналов в заданный режим или для одновременной установки группы формирователей синхросигналов в заданный режим. Причем триггеры 27 и 28, регистр 29 сдвига синхронизируются в нечетные такты работы устройства, а триггеры 32,33, регистр 34 сдвига синхронизируются в четные . такты работы устройства. Регистры 29 и 34 сдвига осуществляют выработку управлякицих импульсов длительное- тью Т.

Элемент НЕ 43 осуществляет инвер тирование сигнала Пуск, поступающего на вход счетчика 45, который делит исходную последовательность на два.Счетчик 45 устанавливается в исходное состояние сигналом Шаг,

55 поступающим через элемент 44, элемент НЕ 46, элемент И-НЕ 47 на установочный вход счетчика 45. Элементы 44, 46 и 47 формируют импульс для

35

40

45

установки счетчика 45, элементы И 4& и 49 осуществляют формирование сигналов Пуск для нечетных и четных тактов работы устройства в режиме Шаг. Селекторы 50 и 51 служат для вьфаботки сигналов Пуск в нечетные и четные такты работы устройства причем необходимо разделение сигналов Пуск для режимов Шаг и Такт в нечетные и четные такты работы устройства.

В режиме Такт должны вырабатываться все синхросигналы на выходах 68,72,69,73,70,74,71 и 75 (фиг.7) последовательно после нажатия кнопки Пуск. В режиме Шаг должны вырабатываться синхросигналы поочередно от каждого нажатия кнопки Пуск, причем сначала вырабатывается нечетный импульс на выходе 68, затем четный импульс на выходе 72 и т.д.

Селектор 50 осуществляет вьфабот- ку сигнала Пуск для нечетных Синхроимпульсов в режимах Такт и Шаг, селектор 51 - для четных синхроимпульсов .

Узлы 37 и 38 управления осуществляют выработку управляющих сигналов соответственно в нечетные и четные такты работы устройства.

Рассмотрим работу узлов управления на примере первого узла управления (фиг.З).

В режиме Такт селекторы 79 и 80 закрыты, на выходе селектора 79 сигнал равен логической единице, поступающей на вход элемента И 82. В режиме Автомат с выхода элемента 81 идет разрешение в регистр 26 сдвига формирователя синхросигналов, осуществляется перепись информации счетчика. Выходы счетчика 25 и регистра 26 сравниваются в узле 41 сравнения формирователя 3 и в нужные моменты времени Тд,/4 происходит сравнение состояний счетчика и регистра, следовательно, осуществляется выработка непрерывных нечетных последователь- ностей на выходах 56-61 формирователей синхросигналов. Аналогично осуществляется выработка непрерывных четных последовательностей на выходах 62-67 формирователей синхросигналов. В режиме Такт происходит блокировка управляющего входа регистров 26 и 31 сдвига. При появлении сигнала Пуск в режиме Такт на

входе 9 формурователей синхросигналов, который проходит через селекто- рьз 50 и 51 формирователей синхросиг- налов, эти селекторы управляют регистрами 29 и 34 соответственно, которые в течение времени Т разрешают прохо щенне синхроимпульсов. Это разрешение поступает соответственно

на входы узлов 37 и 38 управления, в которых через элементы 77,78,83 и 84 проходят разрешанщие сигналы на вход элемента И 82.

При установке режима Шаг узлы

37 и 38 управления блокируют перепись информации регистрами 26 и 31 сдвига. При появлении сигнала Пуск в режиме Шаг этот сигнал поочередно дает разрешение для прохождения синхроимпульса в нечетных и четных тактах работы устройства на выходах селекторов 50 и 51 соответственно. Счетчик 45 считает нажатия кнопки Пуск. При нечетном

нажатии кнопки Пуск он разрешает прохождение сигнала Пуск в селекторе 50, при четном - в селекторе 51. Узлы 37 и 38 управления поочередно дают разрешение на прохожде

ние синхроимпульса на время Т /4, т.е. в каждую четверть такта поочередно появляется разрешение, что разрешает выработку синхросигналов поочередно в зависимости от сигнала

ПУСК.

На выходах 68,72,69,73,70,74,71 к 75 поочередно вырабатьшаются синхросигналы после каждого нажатия кнопки Пуск в режиме Шаг.

в режиме Автомат синхросигналы на выходах 68,72,69,73,70,74,71 и 75 вырабатываются непрерьшно, как и неуправляемые синхросигналы на выходах 56,62,57,63,58,64,59,65,60,61,

66 и 67 (фиг. 7).

Формула изобретения

Устройство для сиТгхронизации вы- числительной системы, содержащее за- даншщй генератор, группу элементов задержки, группу формирователей синхросигналов, блок выработки сигналов начальной установки, блок переключа- теней, формирователь сигналов управления режимами, причем выход задающего генератора соединен с входами элементов задержки группы с первого

по ti -и (где и - число каналов вычислительной системы) и с входом блока выработки сигналов начальной установки, выход которого соединен с входами элементов задержки Труппы с (г1 + 1)-го по (2|1 + 1)-й, выходы элементов задержки с первого по h -и соединены с синхровходами соответствующих формирователей синхросигналов, установочные входы которых соединены соответственно с выходами элементов задержки группы с.(п+1)-го по 2п-й, первая группа выходов блока переключателей соединена с первой группой информационных входов формирователя сигналов управления режимами, синхровход которого соединен с выходом (2п+1)-го элемента задержки группы, выходы первой группы выходов формирователя сигналов управления режимами соединены с первыми управляющими входами формирователей синхросигналов, формирователь сигналов управления режимами содержит два триггера, регистр сдвига и первый элемент И, причем информационные входы первого триггера, второго триггера и регистра сдвига являются соответственно первым, вторым, третьим входами первой группы информационных входов блока, синхровход которого соединен с синхровходами регистра сдвига,второго триггера и первого триггера, прямой выход .первого разряда регистра сдвига соединен с первым входом первого элемента И, второй вход которого соединен с инверсным выходом второго разряда регистра сдвига, выход первого элемента И является выходом формирователя сигналов управления режимами, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения переменного периода синхросигналов в нечетные и четные такты работы устройства для каждого канала, вторая группа выходов блока переключателей соединена соответственно с второй группой информационных входов формирователя сигналов управления режимами, выходы второй группы которого соединены соответственно с вторыми управляющими входами формирователей синхросигналов с первого по ti-й, третьи управляющие входы которых соединены с соответствующими выходами третьей группы формирователя сигналов управления режимами, в ко- 5 торый введены триггеры с третьего по (И+3)-й, 2п-2 селекторов, второй и третий элементы И, причем входы второй группы с первого по (п+1)-й информационных входов формирователя 0 сигналов управления режимами соединены с информационными входами триггеров соответственно с третьего по (ь+3)-й, синхровходы которых объединены и соединены с синхровходом пер5 вого триггера, выход которого соединен с первыми входами первой и второй групп нечетных селекторов и с первым входом второго элемента И, вторые входы первой группы нечетных

0 селекторов объединены и подключены к первым входам первой группы четных селекторов и к прямому выходу (h+3)-ro триггера, инверсньй выход которого соединен с вторыми входами

5 второй группы нечетных селекторов, с первыми входами второй группы чет-, ных селекторов, с вторым входом второго элемента И и с первым, входом третьего элемента И, выход второго

0 триггера соединен с вторыми входами первой и второй групп четных селекторов и с вторым входом четвертого элемента И, выходы триггеров с третьего по (|п + 1)-й соединены с третьи5 ми входами второй группы нечетных селекторов соответственно с первого по (2м-1)-й, с третьи№1 входами второй группы четных селекторов соответственно с второго по (2п-2)-й,

0 выход (п+2)-го триггера соединен с третьим входом второго элемента И и с третьим входом третьего элемента И, выходы нечетных селекторов являются выходами соответственно с

5 первого по (п-1)-й первой группы .выходов блока, выходы четных селекторов с второго по (2и-2)-й являются выходами соответственно с первого по (-1)-й второй группы формирова0 теля сигналов управления режимами, выход второго элемента И является П-м выходом первой группы формирователя сигналов управления режимами, выход третьего элемента И является

5 h-M выходом второй группы формирователя сигналов управления режимами.

М

7«,/5, rif, (f}i/s.f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации вычислительной системы | 1983 |

|

SU1129597A1 |

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU974364A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1367015A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для синхронизации цифровой системы | 1981 |

|

SU981980A1 |

| СИГНАТУРНЫЙ АНАЛИЗАТОР | 1991 |

|

RU2017209C1 |

| Генератор испытательных кодов | 1985 |

|

SU1322275A1 |

| Устройство для синхронизации вычислительной системы | 1982 |

|

SU1068921A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

Изобретение относится к области вычислительной техники, а именно к синхронизируемым вычислительным системам. Целью изобретения является расширение функциональных возможностей за счет обеспечения переменного периода синхросигналов в нечетные и четные такты работы устройства для каждого канала. Устройство содержит задающий генератор, группу элементов задержки, группу формирователей син- хросигналов, блок выработки сигналов начальной установки, блок переключателей, формирователь сигналов управления режимами. 7 ил. (Л с to 1C 4) 00

-С

77

78

fl

83

75

80

Vr

KJ

(Put.J

fa

8Й

8S

1ри9Л

«

21

bo

-c

С

.;5

-Г-

(Риг.6

Гн12

Tn

LJ

Редактор М.Петрова

Составитель И.Сафронова Техред В. Кадар

Коррект Подписн

1613/54 Тираж 671

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д,4/5

Филиал ППП Патент, г.Ужгород, ул.Проектная,4

фи&. 7

Корректор Л, Пат аи Подписное

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU922709A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для синхронизации вычислительной системы | 1983 |

|

SU1129597A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-03-30—Публикация

1984-12-26—Подача