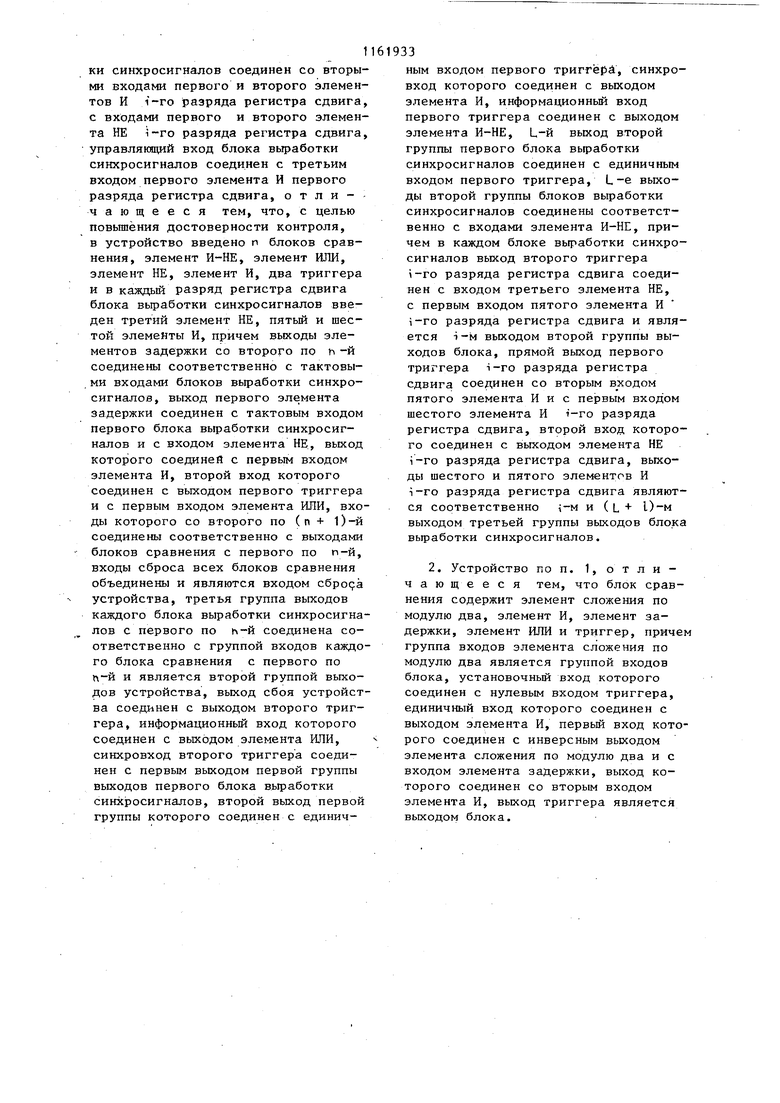

ки синхросигналов соединен со вторы ми входами первого и второго элемен тов И 1-го разряда регистра сдвига с входами первого и второго элемен та НЕ -го разряда регистра сдвига управляющий вход блока вьфаботки синхросигналов соединен с третьим входом первого элемента И первого разряда регистра сдвига, о т л и чающееся тем, что, с целью повышения достоверности контроля, в устройство введено п блоков сравнения, элемент И-НЕ, элемент ИЛИ, элемент НЕ, элемент И, два триггера и в каждый разряд регистра сдвига блока выработки синхросигналов введен третий элемент НЕ, пятьм и шестой элементы И, причем выходы элементов задержки со второго по п -и соединены соответственно с тактовыми входами блоков вьфаботки синхросигналов, выход первого элемента задержки соединен с тактовым входом первого блока выработки синхросигналов и с входом элемента НЕ, выход которого соединей с первым входом элемента И, второй вход которого соединен с выходом первого триггера И с первым входом элемента ИЛИ, вхо ды которого со второго по (п + 1)-й соединены соответственно с выходами блоков сравнения с первого по п-й, входы сброса всех блоков сравнения объединены и являются входом сброса устройства, третья группа выходов каждого блока выработки синхросигна лов с первого по h-й соединена соответственно с группой входов каждо го блока сравнения с первого по п-й и является второй группой выходов устройства, выход сбоя устройст ва соединен с выходом второго триггера, информационньй вход которого соединен с вькодом элемента ИЛИ, синхровход второго триггера соединен с первым выходом первой группы выходов первого блока выработки синхросигналов, второй выход первой группы которого соединен с единич3ным входом первого триггер, синхровход которого соединен с выходом элемента И, информационный вход первого триггера соединен с выходом элемента И-НЕ, L-й вькод второй группы первого блока вьфаботки синхросигналов соединен с единичным входом первого триггера, L-е выходы второй группы блоков вьфаботки синхросигналов соединены соответственно с входами элемента И-НЕ, причем в каждом блоке выработки синхросигналов выход второго триггера i-го разряда регистра сдвига соединен с входом третьего элемента НЕ, с первым входом пятого элемента И i-ro разряда регистра сдвига и является i-м вькодом второй группы выходов блока, прямой выход первого триггера i-ro разряда регистра сдвига соединен со вторым в ходом пятого элемента И и с первым входом шестого элемента И i-ro разряда регистра сдвига, второй вход которого соединен с выходом элемента НЕ i-ro разряда регистра сдвига, выходы шестого и пятого элементов И i-го разряда регистра сдвига являются соответственно {-м и (L+ О-м выходом третьей группы выходов блока выработки синхросигналов. 2. Устройство по п. 1, отличающееся тем, что блок сравнения содержит элемент сложения по модулю два, элемент И, элемент задержки, элемент ИЛИ и триггер, причем группа входов элемента сложения по модулю два является группой входов блока, установочный вход которого соединен с нулевым входом триггера, единичный вход которого соединен с выходом элемента И, первый вход которого соединен с инверсным выходом элемента сложения по модулю два и с входом элемента задержки, выход которого соединен со вторым входом элемента И, выход триггера является выходом блока. 1 Изобретение относится к вьпислительной технике.и предназначено для использования в устройствах обработ ки данных, имеющих микропрограммный принцип управления. Известно устройство для синхрони зации вычислительной системы, содер жащее генератор тактовых импульсов, управляющие и управляемые распределители импульсов, триггер управления, две группы элементов И, группу элементов ИЛИ, блоки управления, первые группы входов которых соединены с выходами соответствукяцих управляющих распределителей импульсов а вторые - с управляющими входами устройства, причем выходы всех распределителей являются выходами устройства, единичный вход триггера со динен с первым выходом управляющего распределителя, второй выход которо го соединен с нулевым входом тригге ра, первые входы элементов И обеих групп соединены с первым выходом генератора тактовых- импульсов и с первым входом управляющего распределителя, вторые входы элементов И первой группы соединены с прямым выходом триггера управления, инверс ный выход которого соединен со вторыми входами элементов И второй гру пы, третьи входы элементов И второй группы соединены с выходами соответ ствукяцих блоков управления, выход каждого элемента ИЛИ группы соединен с первым входом соответствующего управляемого распределителя импульсов, первьй и второй входы каждо го элемента ИЛИ группы соединены соответственно с выходами элементов И первой и второй групп, второй выход генератора тактовых импульсов соединен со вторыми входами всех распределителей импульсов 1 1. В этом устройстве длительность и период следования синхросигналов в рабочих сериях намного превьшают время их распространения в пределах машины. При такой системе синхронизации не требуется учитывать задержку распространения сигналов управления синхронизации и синхросигналов в линиях связи, а.также разброс параметров линий связи. Контроль синхронизации в этом случае ограничивается только проверкой выработки синхросигналов всеми блока32ми выработки синхросигналов в цикле выполняемой микрокоманды. В ЭВМ, построенных на быстродействующих элементах, машинный цикл уменьшается, а количество микроопераций внутри цикла увеличивается. Поэтому возникает необходимость в использовании синхросигналов малой длительности, такой, которая сравнима со временем их распространения в блоках машины. Соответственно требуется для различных блоков машины выравнивание длительности распространения управляющих сигналов синхронизации с помощью элементов задержки. Контроль синхронизации должен обеспечивать не только проверку наличия всех синхросигналов,в цикле, но также и . проверку синхронной работы всех бло- ков машины, что не позволяет известное устройство. Наиболее близким к предложенному является устройство для синхронизации, содержащее задающий генератор, 11 элементов задержки (где и- число каналов), п блоков вьфаботки синхросигналов, дешифратор, h блоков управления длительностью синхросигналов, причем выход задающего генератора соединен, с входами элементов задержки, управляющие входы блоков выработки синхросигналов соединены с входом запуска устройства, выходы блоков выработки синхросигналов являются выходами устройства, выходы блоков управления длительностью синхросигналов соединены соответственно с тактовыми входами блоков выработки синхросигналов, выходы дешифратора с первого по L-Й (где L, - число импульсов в такте) соединены соответственно с входами с первого по блоков управления длительностью синхросигналов, ( t,)6 входы которых соединены соответственно с выходами элементов задержки, выходы блоков выработки синхросигналов соединены соответственно с входами с (U+ 2)-го по (2и+1)-й блоков управления длительностью синхросигналов, вхсд дешифратора является входом кода микрокоманды устройства С ЗНедостатком данного устройства является трудность обнаружения раесинхронизации в работе отдельного блока выработки синхросигналов, которая может проявиться в сбое любого логического блока машины. Это затруд няет приск и локализацию неисправности и уменьшает надежность машины в целом. Целью изобретения является повышение достоверности контроля. Поставленная цель достигается тем, что в устройство для синхронизации с контролем, содержащее задаю щий генератор,п элементов задержки (где п - число каналов), h блоков выработки синхросигналов, причем ка дьй блок выработки синхросигналов содержит регистр сдвига, многовходо вой элемент И, причем i-й разряд (где 1 1, 2, ...,L ) регистра сдв га содержит четыре элемента И, два элемента НЕ, два триггера, причем выход зaдaюIцeгq генератора соединен с входами элементов задержки, вход запуска устройства соединен с управ ляющими входами блоков выработки синхросигналов, первая группа выход которых является первой группой выходов устройства, причем в каждом блоке выработки снхросигналов выходы первого и второго элементов И -го разряда регистра сдвига соединены соответственно с единичным и нулевым входами первого триггера i-го разряда регистра сдвига, выходы третьего и четвертого элементов И i-ro разряда регистра сдвига соединены соответственно с единичным и нулевым входами второго триггера i-ro разряда регистра сдвига выход первого триггера ( i+ 1)-го разряда регистра сдвига соединен с первым входом третьего элемента И ( i + + t)-ro .разряда регистра сдвига и является ( i + 1)-м выходом первой группы выходов блока выработки синхросигналов, второй вход третьего элемента И i-ro разряда регистра сдвига соединен с выходом первого элемент,а НЕ i-ro разряда регистра сдвига, выход второго элемента НЕ i-ro разряда регистра сдвига соединен с Первым входом четвертого элемента И i-ro разряда регистра сдви га, прямые выходы вторых триггеров разрядов с первого по (L 1)-й регистра сдвига соединены с первыми входами вторых элементов И соответствующих разрядов регистра сдвига и с первыми входами первых элементов И последующих разрядов регистра сдвига соответственно, прямой выход первого триггера первого разряда регистра сдвига соединен со вторым входом третьего элемента И первого разряда регистра сдвига, со вторым входом четвертого элемента И L-ro разряда регистра сдвига и является первым выходом первой группы выходов блока, выработки синхросигналов, инверсные выходы первых триггеров i-x разрядов регистра сдвига соединены соответственно с входами многовходового элемента И, выход которого соединен с первым входом первого элемента И первого разряда регистра сдвига, прямой выход второго триггера разряда регистра сдвига соединен с первым входом второго элемента И разряда регистра сдвига, тактовый вход блока выработки синхросигналов соединен со вторыми входами первого и второго элементов И i-ro разряда регистра сдвига, с входами первого и второго элементов НЕ i-ro разряда регистра сдвига, управляющий вход блока выработки синхросигналов соединен с третьим входом первого элемента И первого разряда регистра сдвига, введено п блоков сравнения, элемент И-НЕ, элемент ИЛИ, элемент НЕ, элемент И, два Триггера и в каждый разряд регистра сдвига блока выработки синхросигналов введен третий элемент НЕ, пятый и шестой элементы И, причем выходы элементов задержки со второго по h-й соединены соответственно с тактовыми входами блоков выработки синхросигналов, выход первого элемента задер/кки соединен с тактовым входом первого блока выработки синхросигналов и с входом элемента НЕ, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом первого триггера и с первым входом элемента ИЛИ, входы которого со второго по (п+ 1)-й соединены соответственно с выходами блоков сравнения с первого по п-й, входы сброса всех блоков сравнения объединены и являются входом сброса устройства, третья группа выходов каждого блока выработки синхросигналов с первого по h-й соединена соответственно с группой входов каждого блока сравнения с первого по п-й и является второй группой выходов устройства, выход сбоя устройства соединен с выходом второго триГ5гера, информационный вход которого соединен с выходом элемента ИЛИ, синхровход второго триггера соедине с первым выходом первой rpynnti выхо дов первого блока выработки синхросигналов, второй выход первой групР пы которого соединен с единичным входом первого триггера, синхровход которого соединен с выходом элемента И, информационный вход первого триггера соединен с выходом элемента И-НЕ, L-й выход второй группы первого блока выработки синхросигна лов соедине,н с единичным входом первого триггера, L-e выходы второй группы блоков выработки синхросигналов соединены соответственно с входами элемента И-НЕ, причем в каждом блоке выработки синхросигналов выход второго триггера i-ro разряда регистра сдвига соединен с .входом третьего элемента НЕ, с первым входом пятого элемента И л-го разряда регистра сдвига и является i-м выходом второй группы выходов блока, прямой выход первого триггер i-го разряда регистра сдвига соединен со вторым входом пятого элемента И и с первым входом шестого элемента И 1-го разряда регистра сдви га, второй вход которого соединен с выходом элемента НЕ i-ro разряда регистра сдвига, выходы шестого и пятого элементов И ) -го разряда регистра сдвига являются соо1ветст.венно i-M и ( L + l)-M выходом третьей группы выходов блока вырабо ки синхросигналов. Кроме того, блок сравнения содер жит элемент сложения по модулю два, элемент И, элемент задержки, элемен ИЛИ и триггер, причем группа входов элемента сложения по модулю два является группой .входов блока, устано вочный вход которого соединен с нул вым входом триггера, единичный вход которого соединен с выходом элемента И, первый вход которого соединен с инверсным выходом элемента сложения по модулю два и с входом элемен та задержки, вьгхрд которого соедине со вторым входом элемента И, выход триггера является выходом блока. Устройство вырабатывает две серии импульсов: первую серию синхросигналов, каждьй из которых длительное тью равен периоду следования эталон336 . ной последовательности импульсов с выхода задающего генератора и с периодом следования, равным машинному циклу (эти импульсы вьфабатьгоаются на выходах первой и второй групп блоков выработки синхросигналов)J вторую серию синхросигналов, каждый из которых равен длительностью полупериоду следования эталонной последовательности импульсов, а период следования равен машинному циклу (.эти импульсы вырабатьтаются на выходах третьей группы блоков выработки синхросигналов). На фиг. 1 изображена блок-схема устройства для контроля синхронизации для микропрограммной ЭВМ; на фиг. 2 - блок вьфаботки синхросигналов; на фиг. 3 - блок сравнения) на фиг.4 - временная диаграмма следования первой серии синхросигналов и контроль их выработки блоками выработки синхросигналов; на фиг. 5 временная диаграмма следования первой и второй серии синхросигналов и контроль выработки импульсов второй серии синхросигналов. Устройство содержит задающий генератор 1, элементы 2 задержки-, блоки 3 выработки синхросигналов, блоки А сравнения, элемент И-НЕ 5, элемент ИЛИ 6, триггеры 7 и 8, элемент НЕ 9, элемент И 10, вход 11 запуска устройства, вход 12 сброса устройства, выход 13 сбоя устройства, в блоке 3 выработки синхросигналов: управляющий вход 14.блока, тактовый вход 15 элока, первую группу выходов 16 блока, вторую группу вьЕХодов 17 блока, третью группу вькодов 18 блока. Каждый разряд регистра сдвига блока выработки синхросигналов содержит элементы И 19 и 20, триггер 21, элементы НЕ 22 и 23, элементы И 24 и 25, триггер 26, многовходовой элемент И 27, элемент НЕ 28, элементы И 29 и 30; в блоке 3 вьфаботки си гхросигналов - выходы 31-33 первой группы, выходы 34-36 второй группы, выходы 37-42 ;ретьей группы. Каждый блок сравнения содержит элемент 43 сложения по модулю два, элемент 44 задержки, элемент И 45, триггер 46. Устройство работает следующим образом. Задающий генератор 1 вьфабатывает эталонные синхросигналы постоянной длительности и частоты. Эталоннал последовательность поступает на входы элементоы 2 задержки, служащие для выравнивания во времени синхросигналов между блоками 3 выработки синхросигналов. Блоки 3 выработки синхросигналов предназначены для выработки серии синхросигналов, которые служат для синхронизации работы логических узлов Блоки 4 сравнения предназначены для контроля выработки всех синхросигналов из второй серии, а также контроля их временных параметров. Блок выработки синхросигналов работает следующим образом. На тактовый вход 15 сдвигающего регистра подается непрерьшная последовательность импульсов с выхода одного из злементов задержки, согласно которой сдвигающий регистр постоянно сдвигает находящуюся в регистре информацию. Установка одно го из триггеров 21 или 26 означает занесение единицы в данный разряд сдвигающе1о регистра и выработку соответствующего импульса первой серии синхросигналов. Одновременно с выработкой импульсов первой серии с помощью элементов И 29 и 30 вырабатываются импульсы второй серии синхросигналов путем конъюнкции соответствующих выходов блока выработки синхросигналов. При отсутствии сигнала по управляющему входу 14 занесение единицы в младший разряд запрещено и в блоке 3 постоянно сдвигается нулевая информация, т.е. импульсы серии не вырабатываются. При поступлении управляющего си нала цо входу 14, чтобы не было искажения длительности первого импульса синхросерии, сигнал 14 долж поступать во время неактивного пер ода сигнала 15, поступающего на та товый вход сдвигающего регистра и наличии активного полупериода по сигналу с выхода элемента И 19, ус гганавливаетс триггер 21, т.е. вырабатьгаается первый синхроимпульс серии. Выход триггера 21 активен п тому, что все разряды регистра сдв га нулевые и выхОд элемента И 27 а тивен. После установки триггера 21 выход элемента И 27 становится не тивным и запрещает установку тригг ра 21 до тех пор, пока все триггер , не станут вновь нулевыми. Далее, по следующему неактивному по лупериоду сигнала устанавливается триггер 26, поскольку становится активным выход элемента 27 (триггер 21 установлен и инвертирование сигнала на втором входе элемента 24 тоже дает активный сигнал). По второму (с момента поступления) активному полупериоду сигнала 15 устанавливается триггер 21 и сбрасывается триггер 21, т.е. кончается первый синхросигнал первой серии. Аналогично производится дальнейший сдвиг единицы и последовательная выработка синхросигналов. После сброса предпоследнего из триггеров 2Ц21 при наличии управляющего сигнала 14 вновь устанавливается триггер 21 и начинается новая серия синхросигналов. Серии синхросигналов следуют непрерывно и постоянно до тех пор, пока не снимается сигнал по входу 14, после чего сдвигающий регистр завершает сдвиг записанной в начале цикла единицы по всем разрядам и устанавливает тем самым триггеры . и в исходное нулевое состояние. При отсутствии сигнала по входу 14 (фиг. 2) занесение единицы в младший разряд регистра запрещено и серии тактовых синхроимпульсов не вырабатьшаются. Одновременно с выработкой синхросигналов первой серии путем конъюнкции соответствую цих импульсов этой серии на входах элементов И 29 и 30 вырабатываются импульсы второй серии. Последовательность синхросигналов, вьфабатываемых блоком 3, показана на временных диаграммах (фиг. 4 и 5). Группа входов элемента 4J сложения по модулю два(фиг.3) являются импульсами второй серии блока выработки синхросигналов. Блок 4 сравнения предназначен для контроля выработки импульсов второй серии синхросигналов соответствующим блоком вьфаботки синхросигналов. Блок сравнения работает следующим образом. Соответствующий блок выработки синхросигналов вырабатьшает первую и вторую серии синхросигналов (фиг. 5). Синхросигналы второй серии собираются на элементе 43 по модулю два. В каждый момент ,9 времени должен присутствовать только один синхросигнал из второй серии Если какой-либо из синхросигнала от сутствует или имеется перекрытие, превышакщее величину задержки на элементе 44, элемент И 45 вырабатывает импульс, который устанавливает триггер 46 (перед началом работы, т.е. до момента начала выработки та товьпс сигналов), сигналом по входу 12 сброса триггер 46 будет сброшен. На фиг. 5 приведена временная ди аграмма следования всех серий синхро сигналов и срабатывание схем контроля в случае.невыработки синхросигнала 39 во втором и третьем машинных циклах. I Контроль осуществляется следующим образом. Задающий генератор 1 постоянно и непрерывно вырабатывает эталонную последовательность импульсов, которая поступает на входы элементов 2 задержки, с помощью которых выравнивается время поступления последовательности импульсов на входы блоков 3 выработки синхросигналов где при поступлении сигнала по входу 11 запуска на управляющие входы 14 блоков 3 последние начинают вырабатывать первую и вторую серии синхроимпульсов. Вторые серии сй.нхросигналов каждого блока 3 выработки синхросигналов собираются на входы соответствующих блоков 4 сравнения, которые предварительно сигналом по входу 12 сброса приведены в исходное состояние. Выходы блоков 4 сравнения собраны на группу входов элемента ИЛИ 6 для того, чтобы зафиксировать ошибку синхросигналов второй серии триггером 7. Одновременно я последних импульсов 36 первой серии синхро сигналов каждого блока 3 выработки синхросигналов собираются на входы элемента И-НЕ 5. Если импульсы вырабатываются правильно (т.е. их параметры одинаковы и блоки выработки работают синхронно), в момент записи по информационному входу триггера 8 (вькодной сигнал с элемента И-НЕ 5 триггер 8 должен сброситься в ноль. Предварительно триггер 8 по синхросигналу с выхода первого блока 3 3310 устанавливается в единицу. Если триггер не сбрасывается в момент поступления сигнала с выхода элемента И 10 (отрицательный полупериод выравненной эталонной последовательности импульсов) в конце 1щкла, когда на выходе элемента И-НЕ 5 отсутствует сигнал, то триггер В останется установленным в единицу и в следующем цикле по сигналу 31 с выхода первого блока 3 выработки синхросигналов единица переписьгоается в триггер 7. На выходе 13 сбоя устройства появляется сигнал ошибки. Стробирование триггеров 7 и 8 подобрано так, чтобы момент установки триггера 8 в единицу не совпадал с моментом перезаписи в триггер 7. Технико-экономическая эффективность от использования предлагаемого устройства заключается в том, что оно обеспечивает наиболее полный и достоверный контроль схем с достаточно точной локализации места неисправности, что улучшает показатели надежности ЭВМ. Отсутствие в цепях контроля подстроечных элементов (линий задержек) также повьшшет надежность схем контроля и уменьшает трудоемкость наладочного процесса. Ошибки синхронизации могут вызвать сбой в любом блоке машины и делают невозможным продолжение вычислений. Ранняя и точная локализация ошибок уменьшает время поиска неисправности и последующее восстановление нормальной работы машины. Устройство позволяет быстро и с достаточной степенью приближения к месту и времени сбоя обнаружить ошибку в схемах синхронизации машины. Таким образом, удается значительно уменьшить время восстановления устройства после отказа, которое является одним из главных показателей надежности машины. Изобретение устраняет линии задержки и необходимость их корректировки при наладке каждого образца машины, что повышает достоверность и снижает трудоемкость наладки устройства.

(сип 11

(Си 2} Уг

(СиЗ) зг

35

(Cu5} J3

(Си б) 36

т

jBsm

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации | 1981 |

|

SU1012228A1 |

| Устройство для синхронизации вычислительной системы | 1983 |

|

SU1129597A1 |

| Устройство для синхронизации каналов | 1985 |

|

SU1262471A1 |

| Устройство для сопряжения памяти с процессором | 1983 |

|

SU1142838A1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1221648A1 |

| Устройство для синхронизации вычислительной системы | 1982 |

|

SU1068921A1 |

| Автокоррелятор | 1989 |

|

SU1617447A1 |

| Генератор случайного поля | 1989 |

|

SU1636996A1 |

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU974364A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1594551A1 |

1. УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ С КОНТРОЛЕМ, содержащее задаю-; щий генератор, п элементов задержки ( где h - число каналов), п блоков вьфаботки синхросигналов, причем каждьй блок выработки синхросигналов содержит регистр сдвига, многовходовой элемент И, причем -й разряд (где 1 1, 2, ..., I.) регистра сдвига содержит четыре элемента И, два элемента НЕ, два триггера, причем выход задающего генератора соединен с входами элементов задержки, вход запуска устройства соединен с управляющими входами блоков выработки синхросигналов, первая группа выходов которых является первой группой выходов устройства, причем в каждом блоке выработки синхросигналов выходы первого и второго элементов И i-ro разряда регистра сдвига соединены соответственно с единичнг 1 и нулевым входами первого триггера 1-го разряда регистра сдвига, выходы третьего и четвертого элементов И i-ro разряда регистра сдвига соединены соответственно с единичным и нулевым входами второго триггера -разряда регистра сдвига, выход первого триггера ( i + 1)-го разряда регистра сдвига соединен с первым входом третьего элемента И ( i + + 1)-го разряда регистра сдвига и является ( i + 1)-м выходом первой группы выходов блока выработки синхросигналов, второй вход третьего элемента И i-ro разряда регистра сдвига соединен с выходом первого элемента НЕ 1-го разряда регистра сдвига, выход второго элемента НЕ i-ro разряда регистра сдвига соединен с первым входом четвертого элемента И 1-го разряда регистра сдвига, прямою выходы вторых триггеров 9 разрядов с первого по ( L.- 1)-й ре(Л гистра сдвига соединены с первыми входа.-ш вторых элементов И соответствуклцих разрядов регистра сдвига и с первыми входами первых элементов Q И последующих разрядов регистра сдвига соответственно, прямой выход первого триггера первого разряда регистра сдвига соединен со втор1ым Од входом третьего элемента И первого разряда регистра сдвига, со вторым ;о входом четвертого элемента И .L, -го со разряда регистра сдвига и является 00 первым выходом первой группы выходов блока выработки синхросигналов, инверсные выходы первых триггеров i-x разрядов регистра сдвига соединены соответственное с входами многовходового элемента F, выход которого соединен с первым входом первого элемента И первого разряда регистра сдвига, прямой выход второго триггера Ц-го разряда регистра сдвига соединен с первым входом второго элемента И L-го разряда регистра сдвига, тактовый вход блока выработ

JOL

2т (2 in

цин/11

/Zf

(СиП J/ (Си 2} jif(СиЗ) JZ

(Си Ч) 35 iCuSj Jj iCu6} 36

(TU1)37

(ru2)38

iruj)39

(TU4)IfO

(Тия)ff,

(ru6)чг.

ja.

JffiL

Фиг Ц Цинг

иинл 3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для синхронизации вычислительной системы | 1976 |

|

SU717774A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для синхронизации | 1981 |

|

SU1012228A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-15—Публикация

1983-04-21—Подача