та И и два триггера, причем установочный вход первого триггера -соединен с выходом первого элемента И, синхроп ниэирукэдий вход - с первьм входом втораго элемента И и первым входом блока, информационный вход - с первым выходом компаратора, а выход с вторым выходом блока, установочный вход второго триггера соединен с выходом второго элемента И синхронизирующий вход - с первым входом первого элемента И и вторым входом блока выход - спервым выходом блока, а информационный вход - с вторым выходом компаратора, третий и четвертый выходы которого соединены соответственно с вторыми входами первого и второго элементов И, а группа входов с группой входов блока,

3. Устройство ПОП.1, отличающееся тем, что блок связи с магистралью содержит блок памяти, два регистра адреса, два регистра данных, два элемента И, элемент ИЛИ, дйа триггера, два элемента задержки, элемент НЕ, компаратор адреса и генератор импульсов, причем выход генератора импульсов соединен с синхрог низирующим входом первого триггера и через элемент НЕ с синхронизирующим входом второго триггера, выход которого соединен с синхронизирующими входами первых регистров адреса и данных и элемента И, входом первого элемента задержки и с установочным входом первого триггера, выход которого соединен с синхронизирующимивходами вторых регистров адреса и дан ных и элемента И, входом второго элемента задержки и с установочньзм входом второго триггера, группа входов блока памяти соединена с группами выходов первого и второго регистров адреса и с группой адресных выходов блока, группа входов-выходов с первыми входами-выходами первого и второго регистров данных, а вход с выходом элемента ИЛИ,.первый и второй входы которого соединены соответств1енно с выходами первого и второго элементов И, группа входов первого регистра адреса, выход первого элемента задержкиj группа входов первого элемента И, второй вход-выход первого регистра данных и информационный вход второго триггера соединены соответственно с первой группой адресных входов первым выходом, группой управлякицих входов и первыми группой информационных входов,-выходов и входом блока, па входов второго регистра.адреса,выход второго элемента задержки,инфррма ционный вход второго элемента И, второй вход-выход второго регистра данных соединены соответственно Е вторалми группой адресных входов, выходом, входом и группой информационных входов-выходов блока, инфор лационный вход первого, триггера соеринен через компаратор адреса с второй группой адресных входов блока, управляющие входы первого и второго регистров данных подключены соответственно к группе управляквдих входов и второму входу блока.

4. Устройство ПОП.1, отличающееся тем, что блок связи с линиями содержит линейный дешифратор и группу линейных согласовате лей, причем вход линейного дешифратора соединен с входом блока, а rpyftna выходов - с управляющими входами линейных согласователей группы, первые и вторые входы-выходы которых являются соответственно первой и второй группами входов-выходов блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными | 1984 |

|

SU1239724A2 |

| Устройство для обмена данными | 1988 |

|

SU1599863A1 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| Устройство для обмена данными | 1989 |

|

SU1700562A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

1

, Изобретение относится к вычислительной- технике и может быть использовано в вычислительных системс15с для сопряжения ЭВМ с каналами связи.

Известны- устройства для обмена информацией, содержащие дешифратор режима, регистр адресов, блик коммутации, блок связи,с каналом, блок формирования обменных сигналов, блок приема, блок управления, буферный регистр и блок выдачи информации

Недостатком этих устройств являются ограниченные функциональные возможности.. ;

Наиболее близким к предлагаемому является устройство для обмена информацией, содержащее генератор тактовых импульсов, управлякяций дешифратор ввода-вывода, блок памяти, линейный блок ввода-вывода и блок микропрограммного управления, группа адресных выходов которого через шину адреса соединена с группами входов

управляющего дешифратора, дешифратора ввода-вывода и адресными группами входов блока памяти и линейного блока вбода-вывода, группа информационных входов-выходов через шину данных с первой группой информационных входов-выходов линейного блока вводавывода и группой информационных входов-выходов блока памяти, группа управляющих выходов - через шину управления с группами управляющих входов блока памяти и линейного блока ввода-вывода, тактовый вход - с выходом генератора тактовых импульсо а синхронизирующий вход - с первым выходом управляющего дешифратора, второй и третий выходы которого соединены соответственно с синхронизиру щими входами блока памяти и дешифратора ввода-вывода, первый выход которого соединен с входом линейного блока ввода-вывода С2. Недостатком этого устройства является ограниченная область применения, вследствие чего оно не может быть использовано в иерархических системах передачи данных, так как может организовывать связи с внешними устройствами только через линей ные устройства ввода-вывода с одинаковой приоритетностью связи для каждого канала и не может по этой причи не обеспечить обмен с высокой скоростью с системой высшего уровня. Цель изобретения - расширение области применения устройства, Поставленная цель достигается тем что в устройство, содержащее генера тор- тактовых импульсов, управляющий дешифратор , .дешифратор /ввода-вывода блок памяти, линейныйблок вводавывода и блок микропрограммного уп.равления, группа адресных выходов которого через шину адреса соединен с группами входом дешифратора ввода вывода и управляющего дешифратора и адресньоми группами входов блока памяти и-линейного блока ввода-вывода,, группа информационных входоввыходов - через шину данных с перво группой информационных входов-выходов линейного блока ввода-вывода и группой информационных входов-выходов блока памяти, группа управляю щих выходов - через шину управления с группами управляющих входов блока памяти и линейного блока ввода-выво да, тактовый вход - с выходом генер тора тактовых импульсов, а синхронизирующий вход - с первым выходом управляющего дешифратора, второй и третий выходы которого соединены соответственно с синхронизукяцими; входами блока памяти и дешифратора ввода-вывода, первый выход которого соединен с входом линейного блокаввода-вывода, введены блок прерыван блок связи с магистралью, блок регистров и блок связи с линиями, при чем первая группа входов-выхо дов блока связи с линиями Соединена с второй группой входов-выходов линей ного блока ввода-вывода, вторая руппа входов-выходов - с группой инейных входов-выходов устройства, вход - с выхэдом блока регистров, ход которого соединен с вторым выодом дешифратора ввода-вывода, група информационных входов-выходов группа управляющих входов соединены соответственно через шину данных и шину управления с группами инфорационных входов-выходов и управляюих выходов блока микропрограммного управления и с первыми информационных входов-выходов и группрй управляющих входов блока связи с магистралью, первая группа адресных входов которого соединена через адресную шину с группой гщресных выходов блока микропрограммного управления, группа а;с1Ресных выходовс группой входов блока прер авания, первые вход и выход - соответственно с четвертым выходом р вторым входом управляющего дешифратора-, первьй вход блока прерываний через шину управления, а первый в1лход непосредственно соединены соответственно с группой управляющих выходов и управляющим входом блока микропрограммного управления, вторые вход и выход блока прерывания и вторые вход, выход, группа адресных входов и группа информационных входов-выходов блока связи с магистралью соединены с соответствукяцими группами магистральных входов-выходов устройства. Блок прерываний содержит компара тор, два элемента И и два триггера, причем установочный вход первого триггера соединен с выходом первого элемента И, синхронизирующий вход с первым входом второго элемента И и первым входом блока, информационный вход - с первым выходом компаратора, а выход - с вторым выходом блока, установочный вход второго триггера соединен с.выходом второго элемента И, синхронизирующий вход с первым входом первого элемента И, и вторым входом блока выход - с первым выходом блока, а информационный вход - с вторым выходом компаратора , третий и четвертый выходы которого соединены соответственно с вторыми входами первого и второго элементов И, а группа входов - с группой . входов блока. БЛОК связи с магистралью содержит блок памяти, два Е егистра адреса, два регистра данных, два элемента И, элемент ИЛИ, два триггера, два элемента задержки, элемент НЕ, компаратор адреса и генератор импульсов, причем выход генератора мпуль,сов соединен с синхронизирующим первого триггера и через элеме(«& НЕ с синхронизирующим входом аторогО триггера, выход которого соединен с синхронизирующими входами первых

регистров адреса и данных и элемент И, входом первого элемента задержки и с установочным входом первого триггера, выход которого соединен с синхронизирующими входами вторых регистров адреса и данных и элемента И, входом второго элемента задержки и с установочным входом второго триггера, группа входов памяти соединена с группами выходов первого и второго регистров адреса и с группой адресных выходов блока, группа входов-выходов - с первыми входамивыходами первого и второго регистров данных, а вход - с выходом элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и второго элементов И, группа входов первого регистра адреса, выход первого элемента згщержки, группа входов первого элементаИ, второй вход-выход первого регистра данных и информационный вход второго триггера соединены соответственно с первой группо адресных входов, первым выходом, группой управляющих входов и первыми группой информационных входов-выходов и входом блока, группа входов второго регистра адреса, выход второго элемента задержки, информационный вход второго элемента И, второй вход-выход второго регистра данных соединены соответственно с вторыми группой адресных входов, выходом, входом и группой .информационных входов-выходов блока, информационный вход первого триггера соединен через компаратор адреса с второй группой адресных входов блока, управляющие входы первого и второго регистров данных подключены соответственно к группе управляющих входов и второму входу блока.

Блок связи с линиями содержит линеный дешифратор и группу линейных согласователей, причем вход линейного дешифратора соединен с входом блока, а группа выходов - с управляющими входами линейных сргласователей группы, первые и вторые входы-выходы которых являются соответственно первой и второй группами входов-выходов блока.

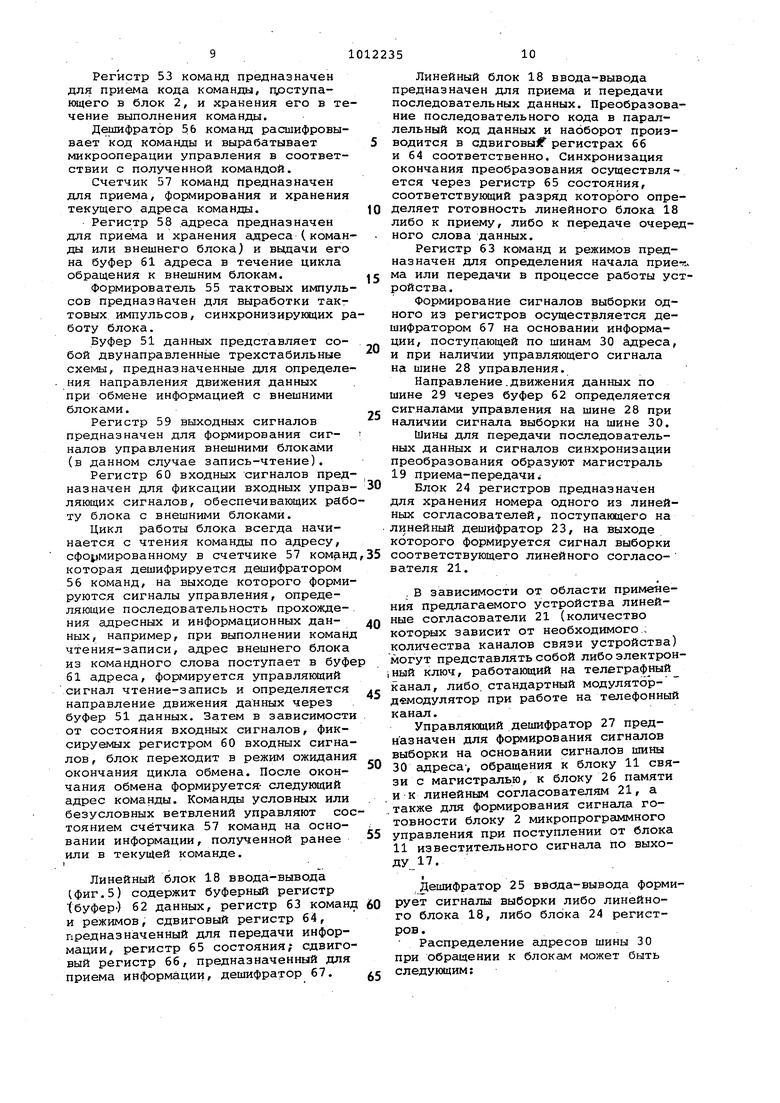

На фиг.1 представлена блок-схема устройства; на фиг. 2-5 - функциональгные схемы блока связи с магистралью, блока прерываний, блока микропрограммного управления и линейного блока ввода-вывода.

Устройство содержит (фиг.1) генератор 1 тактовых импульсов, блок 2 микропрограммного управления, имеющий тактовый 3 л синхронизирующий 4 входы, блок 5 прерываний с вторым входом б, группой входов 7, первыми входом 8 и выходом 9 и вторым выходом 10, блок. 11 связи .с магистралью, второй вход 12, группы адресных входов 13, информаииОннЕЛХ входов-выходов

14 и выход 15 которого предназначены для связи с внешней магистралью, а первые вход 16 и выход 17 являются входом выборки и выходом синхронизации, линейный блок 18 ввода-вывода, второй вход-выход которого соединен последовательно с магистралью 19 блока 20 связи с линиями для последовательного ввода-вывода на линейные согласователи 21, вторые входы-выходы 22 которых являются линейными входами-выходами устройства, линейный дешифратор 23, блок 24 регистров, дешифратор 25 ввода-вывода, бло 26 памяти, управляющий дешифратор 27. На фиг.1 указаны также шины управления 28, данных 29 и гщреса 30.

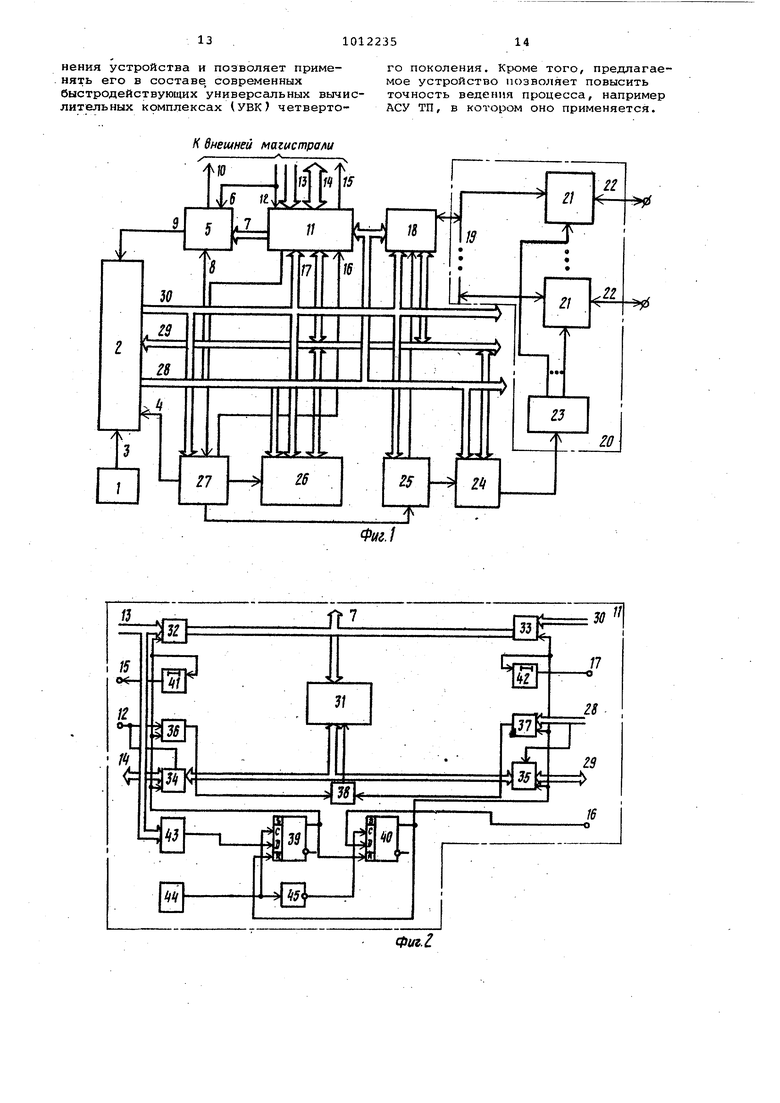

Блок 11 связи с магистралью -(фиг. содержит блок 31 памяти, второй и первый регистры 32 и 33 адреса, второй и первый регистры 34 и 35 данных второй и первый элементы И 36 и 37, элемент ИЛИ 38, триггеры 39 и 40, второй.и первый элементы 41 и 42, задержки, компаратор 43 адреса, генератор 44 импульсов и элемент НЕ 45.

Блок 11 связи с магистралью представляет собой оперативно-запоминающее устройство, предназначенное для хранения и накопления массивов приемпередачи и для информационной связи с системой верхнего уровня через внешнюю-магистраль, и имеет каналы обращения как со стороны внешней магистрали, так и со стороны внутренней магистрали. Его регистры 32, 33, 34 и 35 могут быть выполнены, например, на базе трехстабильных регистров (буферов).

Распределение во времени циклов обращения к блоку 11 осуществляется триггерами 39 и 40, единичное состояние которых определяет прохождение сигналов адреса, данных и управления на вход блока 31 . Триггеры 39 и 40 соединены таким образом, что их одновременное единичное состояние исключается. Если состоя-. ние триггера 39 соответствует единичному, то сигнал с выхода этого . триггера, поступая на установочный вход триггера 40, удерживает его в нулевом состоянии .и наоборот. Распределение во времени включения триггеров осуществляется взаимоин

.версными сигналами, поступающими с генератора 44 с использованием элемента НЕ 45 на их входы синхронизации. Сигналы, указываю1цие на начало цикла обращения, поступают на информационные входы триггеров. Сигнал обращения со стороны внешней магистргши формируется на выходе компаратора 43 в зависимости от состояния входов 13, соединенных с шиной адреса. Наличие компаратора 43 определяется различной адресной емкостью шины адреса и блока 31 памяти. Возможная емкость блока 31 памяти является частью всего массива системы верхнего у 5овня. Например, для органзации адресации к возможному массиву памяти системы верхнего уровня, равной 64 килослова-, необходима шестнадцатиразрядная.шина адреса (входы 13),а isMKOCTb блока 31 памяти составляет 1 килослово, для адресации к которой Необходимо всего лишь десятиразрядная шина адреса. Оставши еся шесть разрядов адреса являются как бы номером части всего возможного массива и сравниваются с заране заданным номером в компараторе 43 адреса. При совпадении заданного номера с номером, соответствуювдим состоянию шины адреса, на выходе компаратора 43 формируется сигнал выборки. Если состояние триггера 40 соответствует нулевому состоянию, то .триггер 39 по фронту синхросигнала устанавливается в единичное состояние. Сигнал с выхода этого триггера, поступая на входы регистра 34 данных элемента И 36, регистра 32 адреса и элемента 41 задержки, разрешает прохождение сигналов адреса, управления и данных на входы блока 31 памяти и формирование известительного сигнала внешней магистрали. Сигнал по входу 12 с шины управления внешней магистрали определяет направление движения данных через регистр 34 (записи или чтение).

Если состояние триггера 40 соответствует единичному,состоянию, то установка триггера 39 задерживается до установки триггера 40 в нулевое состояние, задерживая тем самьм известительный сигнал на выходе 15 для внешней магистрали ii прохождение сигналов адреса, управления и данных. .

Признаком обращения к блоку 11 со стороны внутренней магистрали является сигнал выборки на входе 16. Работа блока 11 в последующем цикле аналогична, за исключением того, что в данном цикле участвуют регистры 33 и 35, элемент 42 задержки и элемент 37.

Выход блока 11 предназначен для сигнализации об адресе выбираемой . ячейки из блока 31 памяти.

Блок 5 прерываний (фиг.З) содержит компаратор 46, два элемента И 47, и 48, и два триггера 49 и 50.

Блок 5 прерываний преднааначен для формирования сигналов прерывания в сторону внешней магистрали через выход 10, а в сторону блока 2 микропрограммного управления - через выхо 9, и осуществляет синхронизацию начала и окончания процесса приемапередачи устройства при работе с вне.ней 1чагистралью, Формирование сигналов прерывания осуществляется по коду адреса обра1дения к блоку ll и в зависимости от режима обргицения (чтение запись). Из всего массива памяти блока 11 выделены два адреса (две ячейки) X и Y которые выполняют функции ячейки состояния (Yj и ячейки команды (X) . Формирование сигналов, соответствуквдих обращению к одной из ячеек, осуществляется компаратором 46 методом сравнения кода текущего адре са обращения с заранее определенньми кодами. Коды текущего адреса обращен ния поступают на входы 7 с выход блока 11.

Если производится обращение к ячейке X, то на выходах компаратора 46, соединенных с элементом И 48 и триггером 50, формируется сигнал, и в зависимости от наличия сигнала на входах 6 или В триггер 50 устанавливается либо в единичное,состояние, либо в нулевое. Следовательно, если производится обращение к ячейке со стороны внешней магистрали, триггер 50 устанавливается в единичное состояние (формируется сигнал прерывания в сторону блока 2 микропрограммного управления), если производится обращение к ячейке X со стороны внутренней магистрали, триггер 50 устанавливается в нулевое состояние (сбрасывается сигнал прерывания в сторону блока 2).,

При обращении к ячейке Y управление триггером 49 (сигналы прерывания в сторону внетиней магистрали) осуществляется аналогично, только с использованием элемента И 47.

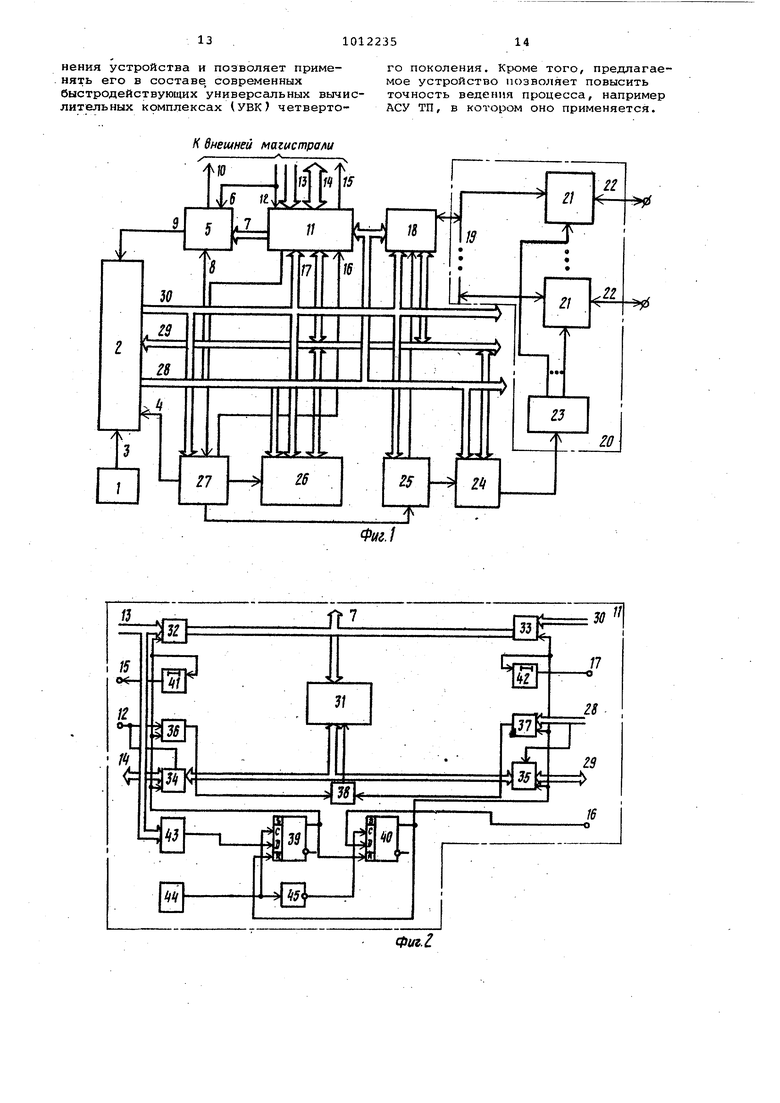

Блок 2 микропрограммного управления (фиг.4) содержит буферный регист (буфер) 51 данных. ари4 1етическологический узел (АЛУ) 52, регистр 53 команд, блок 54 регистров общего назначения, фор1- ирователь 55 тактовы импульсов, дешифратор 56 команд, счечик 57 команд, регистр 58 гщреса, регистр 59 выходных сигналов, регистр 60 входных сигналов, буферный регист (буфер) 61 адреса.

Блок 2 предназначен для реализаци программы, хранящейся в блоке 26 памти, в результате выполнения которой производится координация работы блоков устройства. Блок 2 выполняет определенный список к-оманд, включающий в себя команды чтения-записи, логической и арифметической обработки данных, условных и безусловных ветвлений.

АЛУ 52 обеспечивает обработку двоично-кодированных данных. ,

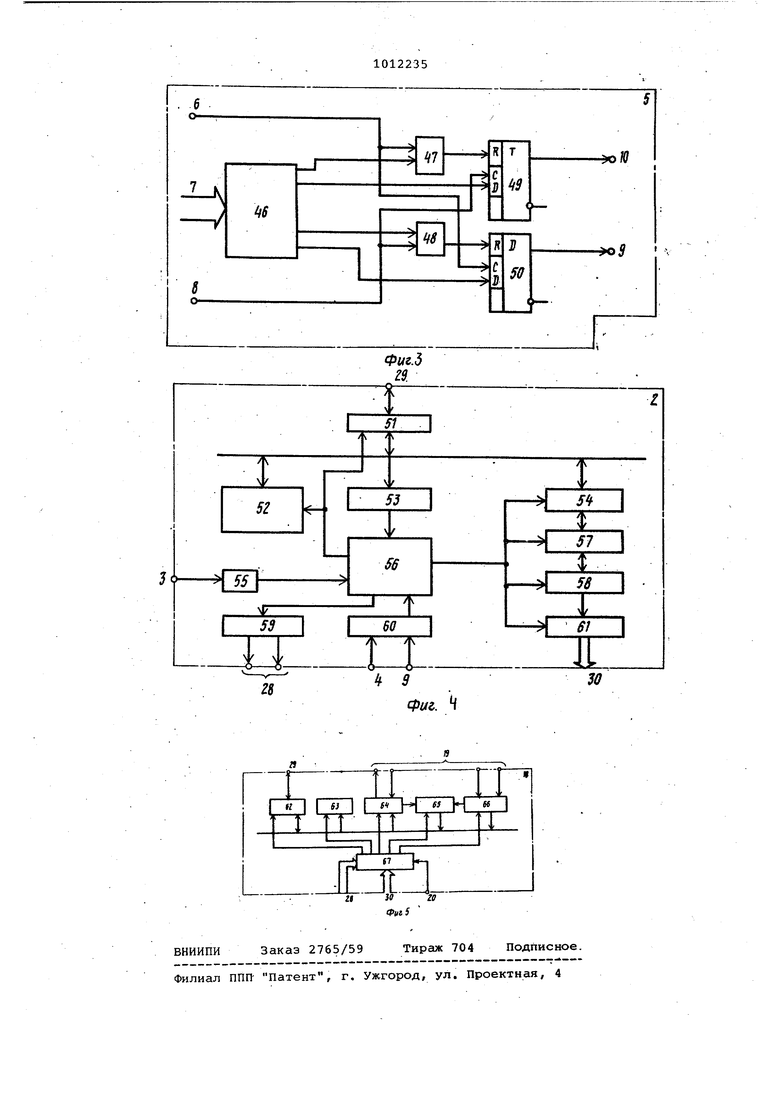

Блок 54 регистров общего «аэначе ния предназначен для хранения It вьщачи данных, участвукщих в процессе обработки и выполнения заданной команды. Регистр 53 команд предназначен для приема кода команды, поступающего в блок 2, и хранения его в те чение выполнения команды. Дешифратор 56 команд расшифровывает код команды и вырабатывает микрооперации управления в соответствии с полученной командой. Счетчик 57 команд Предназначен для приема, формирования и хранения текущего адреса команды. Регистр 58 адреса предназначен для приема и хранения адреса (коман ды или внешнего блока) и выдачи его на буфер 61 адреса в течение цикла обращения к внешним блокам. Формирователь 55 тактовых импуль сов предназначен для выработки тактовых импульсов, синхронизирукщих р боту блока. Буфер 51 данных представляет собой двунаправленные трехстабильные схемы, предназначенные для определе ния направления движения данных при обмене информацией с внешними блоками. Регистр 59 выходных сигналов предназначен для формирования сигналов управления внешними блоками (в данном случае запись-чтение). Регистр 60 входных сигналов пред назначен для фиксации входных управ ляющих сигналов, обеспечивающих раб ту блока с внешними блоками. Цикл работы блока всегда начинается с чтения команды по адресу, сформированному в счетчике 57 коман которая дешифрируется дешифратором 56 команд, на выходе которого форми руются сигналы управления, определяющие последовательность прохождения адресных и информационных данных, например, при выполнении коман чтения-записи, адрес внешнего блока из командного слова поступает в буф 61 адреса, формируется управляющий сигнал чтение-запись и определяется направление движения данных через буфер 51 данных. Затем в зависимост от состояния входных сигналов, фиксируемых регистром 60 входных сигна лов , блок переходит в режим ожидани окончания цикла обмена. После окончания обмена формируется- следующий адрес команды. Команды условных или безусловных ветвлений управляют со тоянием счётчика 57 команд на основании информации, полученной ранее или в текущей команде. Линейный блок 18 ввода-вывода (фиг.5) содержит буферный регистр |буфер) 62 данных, регистр 63 коман и режимов, сдвиговый регистр 64, предназначенный для передачи информагщи, регистр 65 состояния; сдвиго вый регистр 66, предназначенный для приема информации, дешифратор 67. Линейный блок 18 ввода-вывода предназначен для приема и передачи последовательных данных. Преобразование последовательного кода в параллельный код данных и наоборот производится в сдвиговый регистрах 66 и 64 соответственно. Синхронизация окончания преобразования осуществля-ется через регистр 65 состояния, соответствующий разряд которого определяет готовность линейного блока 18 либо к приему, либо к передаче очередного слова данных. Регистр 63 команд и режимов предназначен для определения начала прие-г.. ма или передачи в процессе работы устройства. Формирование сигналов выборки одного из регистров осуществляется дешифратором 67 на основании информации, поступающей по шинам 30 адреса, и при наличии управляющего сигнала на шине 28 управления. Направление.движения данных по шине 29 через буфер 62 определяется сигналами управления на шине 28 при наличии сигнала выборки на шине 30. Шины для передачи последовательных данных и сигналов синхронизации преобразования образуют магистраль 19 приема-передачиi Блок 24 регистров предназначен для хранения номера одного из линейных согласователей, поступакщего на линейный дешифратор 23, на выходе которого формируется сигнал выборки соответствующего линейного согласователя 21. В зависимости от области применения предлагаемого устройства линейные согласователи 21 (количество которых зависит от необходимого.; количества каналов связи устройства) могут представлять собой либо электронный ключ, работающий на телеграфный канал, либо, стандартный модулятордемодулятор при работе на телефонный канал. Управляющий дешифратор 27 предназначен для формирования сигналов выборки на основании сигналов шины 30 адреса-, обращения к блоку 11 связи с магистралью, к блоку 26 памяти и к линейным согласоватедям 21, а также для формирования сигнала готовности блоку 2 микропрограммного управления при поступлении от блока 11 известительного сигнала по выходу 17. Дешифратор 25 ввода-вывода формирует сигналы выборки либо линейного блока 18, либо блока 24 регистров. Распределение адресов шины 30 при обращении к блокам может быть следующим:

14

13

12

11 10 Подробное распределение разрядов адресных сигналов шины 30 позволяет равномерно распределить нагрузку цепей этой шины. Устройство работает следующим образом. в исходном состоянии блок 2 находится в ожидании сигнала прерывания с выхода 9.. (Ожидание сигнала прерыва ния соответствует ожиданию устройством команды (запись в ячейку X блока 11) со сторонывнешней магистрали для организации цикла приемапередачи. Поэтому прежде чем выдать команду устройству со стороны внешней, магистрали, необходи1у1О в блоке 31 памяти подготовить нужную информа цию. Если необходимо передать массив информации, то формируется соответствующий массив в заранее определенной области и в фиксированной ячейке записывается номер канала связи. Блок 5 прерываний формирует сигнал прерлвания, и блок 2 начинает выполнять программу, хранящуюся в блоке 26 памяти. Алгоритм организации прие ма-передачи (вид протокола, форматы посылок, способ контроля и т.д.) может быть различным и определяется программой, хранящейся в блоке 26 па мяти . Для примера приводим алгоритм приема-передачи при работе в полудуплексном синхронном режиме, учитывая, что на другом конце канала связи -СТОИТ внешнее, устройство, работаю щее по аналогичному протоколу. Блок 2, восприняв сигнсЩ-прерывания с;бл ка 5, производит чтение с фиксированной ячейки блока 31 памяти, соде жащей номер канала связи, записывает его в блок 24 регистров, выбрав тем самым соответствующий линейный согласователь 21. Затем читает ячей ку X (сбрасывая тем самым сигнал прерывания ) , анализирует полученну команду и в случае передачи записывает в регистр 63 команды и режим линейного блока 18 ввода-вывода ко манду, настраивающую его на передачу, и начинает передавать хранящийс

9876543210

адреса ячеек блока 31 памяти и ячеек блока 26 памяти/ номер регистра в линейном блоке 18 и в блоке 24 регистров ,

О - обращение либо к линейному блоку 18 ввода-вывода, 1 - обращение .к блоку 24 регист1 ов,.

00 - обращение к блоку, 26памяти, 10 -обращение к блоку 11 связи смагистралью/ 11 - обращение к линейньлм согласователям 21. в памяти массив данных. Перед выдачей в передатчик каждого слова данных читается регистр 65 сос- ояния линейного блока 18 и анализируется его готовность для передачи. В момент передачи в блоке 2 к каждому слову может быть прифоЕ 1ирована служебная информация для осуществления контроля данных в соответствии с выбранным методом контроля (например, приформировывается разряд четности или фЬрмируется циклический код остатка и т.п.). После передачи всего массива блок 2 перестраивает линейный блок 18 ца прием и, читая состояние регистра 65 состояния, организует ожидание с внешнего устройства посылки данных, подтверждающей прием внешним устройством переданного массива. Блок 2 при получении признака готовности приемника линейного блока 18 считывает данные, переданные внешним устройством, Зсшисывает в ячейку X блока 31 Пс1мяти слово, сигнализирующее систему верхнего уровня о завершении цикла приема-передачи, в котором формируются приз накидостоверности обмена. После этого блок 2 снова переходит в режим ожидания сигнала прерывания Iполучение очередной команды с.внешней магистрали). Таким образом, предлагаемое устройство позволяет реализовать двусторонний обмен данными по нескольким каналам СВЯ5И с использованием только одного линейного устройства вводавывода с различными протоколами, матами и методами контроля, определяемыми только лишь программой, хранящейся в программной памяти, и позволяет организовать ,. связь с системой верхнего уровня через вниинюю . магистраль,, организуквдей быстрый, наивысший по приоритету к ост льным каналам синхронизируемый по управлению, так и информационно . дополнительный канал связи. Это значительно расширяет область применения устройства и позволяет применять его в составе современных быстродействующих универсальных вычислительных комплексах (УВК) четверто/С внешней магистраAU 111 го поколения. Кроме того, предлагаемое устройство позволяет повысить точность ведения процесса, например АСУ ТП, в котором оно применяется. Фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 756400, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| 1971 |

|

SU415693A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1983-04-15—Публикация

1981-12-17—Подача