(54) УСТРОЙСТВО МИКРОПРОЦЕССОРНОГО УПРАВЛЕНИЯ И ОБРАБОТКИ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Устройство для сопряжения микропроцессора с системной шиной | 1990 |

|

SU1837299A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Каркас для размещения вдвижных блоков памяти | 1979 |

|

SU911751A1 |

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

| Система обмена данными в вычислительной сети | 1991 |

|

SU1807493A1 |

| Устройство для сопряжения магистрали приборного интерфейса с магистралью микро-ЭВМ | 1986 |

|

SU1368885A1 |

| Устройство для сопряжения магистрали эвм с магистралью внешних устройств | 1984 |

|

SU1229765A1 |

Устройство относится к вычислительной технике, а именно, к средствам микропроцессорного управления.

Известно микропроцессорное устройство, состоящее из микропроцессора, элемента памяти и элемента вводавывода. Такое устройство позволяет программным путем выполнять различные функции управления и обработки информации 1.

Недостатком данного устройства является непосредственное подключение к микропроцессору элементов памяти и ввода-вывода, что вызывает значительные трудности при расширении объема подключаемого оборудования и организации прерываний.

Наиболее близким к предлагаемому является микропроцессорное устройство, содержащее микропроцессор,контроллер интерфейса (системный контроллер с адресными буферами и генератором) , моцуль приоритетного прерывания , элементы памяти, элементы ввода-вывода, интерфейсную магистраль (шина адреса, шина данных, шина управления) 2.

Недостатком известного устройства является недостаточное эффективное использование интерфейсной магистрали, при подключении к ней нескольких активных устройств, что в свою очередь значительно снижает производительность микропроцессорных систем, а также ограничивает возможности их использования.

Цель изобретения - повышение производительности и расширение диапазона использования.

10

Поставленная цель достигается тем, что в устройство микропроцессорного управления и обработки информации/ содержащее микропроцессор, контроллер интерфейса, блок приори15тетного прерывания, блок памяти и блок ввода-вывода, причем вход-выход микропроцессора соединен с первым входом-выходом контроллера интерфейса, второй вход-выход которого

20 через интерфейсную магистраль соединен с вхсяами-выходами блока памяти, блока приоритетного прерывания, и первым входом-выходом блока вводавывода, первый вход микропроцессора

25 соединен с выходом блока приоритетного 1ферывания, введены блок приоритетного распределения интерфейсной магистрали, блок управления асинхронным и триггер запро30са, причем вход-выход блока приоритетного распределения интерфейсной магистрали через интерфейсную магистраль подклюден к входам-выходам блока приоритетного прерывания,вход блока управления асинхронным обменом, блока ввода-вывода подключены через шину разрешения к выходу блока приоритетного распределения интерфейсной магиртрали, вход-выход блока управления асинхронным обменом подключен к входу-выходу контроллера интерфейса, а первый выход блока управления асинхронным обменом - к второму входу микропроцессора, единичный и нулевой вХоды триггера запроса подключены к выходу контроллера интерфейса и второму выходу блока управления асинхронным обменом соответственно, выходы триггера запроса и второй входвыход блока ввода-вывода через шину запроса подключены к входу блока приоритетного распределения интерфейсной магистрали.

Кроме того, блок управления асинронным обменом содержит три триггера, формирователь импульсов, элемент задержки, элемент И и генератор тактовых сигналов, причем вход формирователя, импульсов является, входом блока, выход формирователя импульсов подключен к единичному входу первого триггера, единичный выход которого через элемент задержки подключен к. синхронизирующему входу второго триггера, единичный выход которого соединен с первым входом элемента И, выход которого соединен с информационным входом третьего триггера, единичный выход которого соединен с нулевым входом второго триггера, нулевой выход третьего триггера - с синхронизирующим входом первого триггера, синхронизирующий вход третьего триггера с выходом генератора тактовых сигналов и является первым выходом блока, выходы первого и второго триггеров и второй вход элемента И являются входом - выходом блока, выход третьего триггера является вторым выходом блока.

Причем, блок приоритетного распрделения интерфейсной магистрали содержит регистр, два дешифратора, формирователь импульсов, узел приоритетного сравнения и элемент задер51 и, причем информационный вход узла приоритетного сравнения соединен с выходом регистра, стробирующий вход узла приоритетного сравнения соединен с выходом элемента задержки, информационный и синхронизирующий выход узла приоритетного сравнения соединен с соответствуюЩ1МИ входами первого дешифратора, группа выходов которого является выходом блока, синхронизирующий вход регистра соединен с выходом второго дешифратора, исполнительный вход которого «ерез формирователь импульсов соединен с входом элемента задержки, информационный вход регистра, адресный и исполнительный входь1 второго дешифратора и вход элемента задержки являются входом-выходом блока, группа входов запроса

0 узла приоритетного сравнения является входом блока.

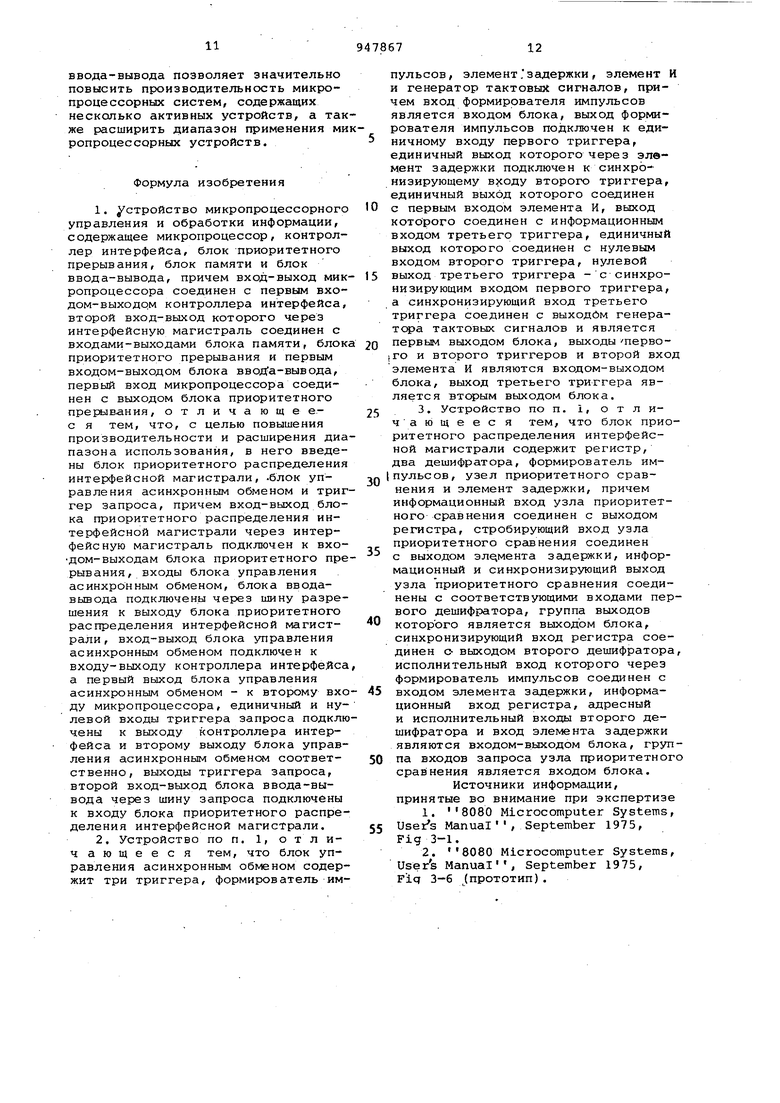

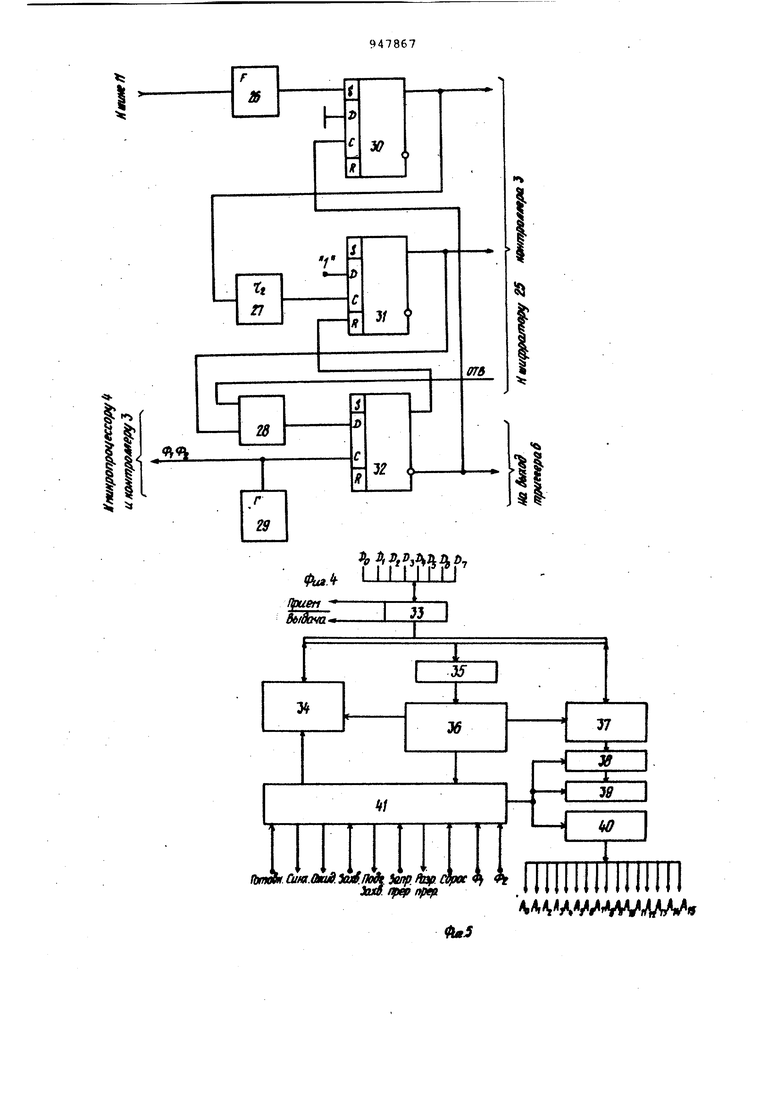

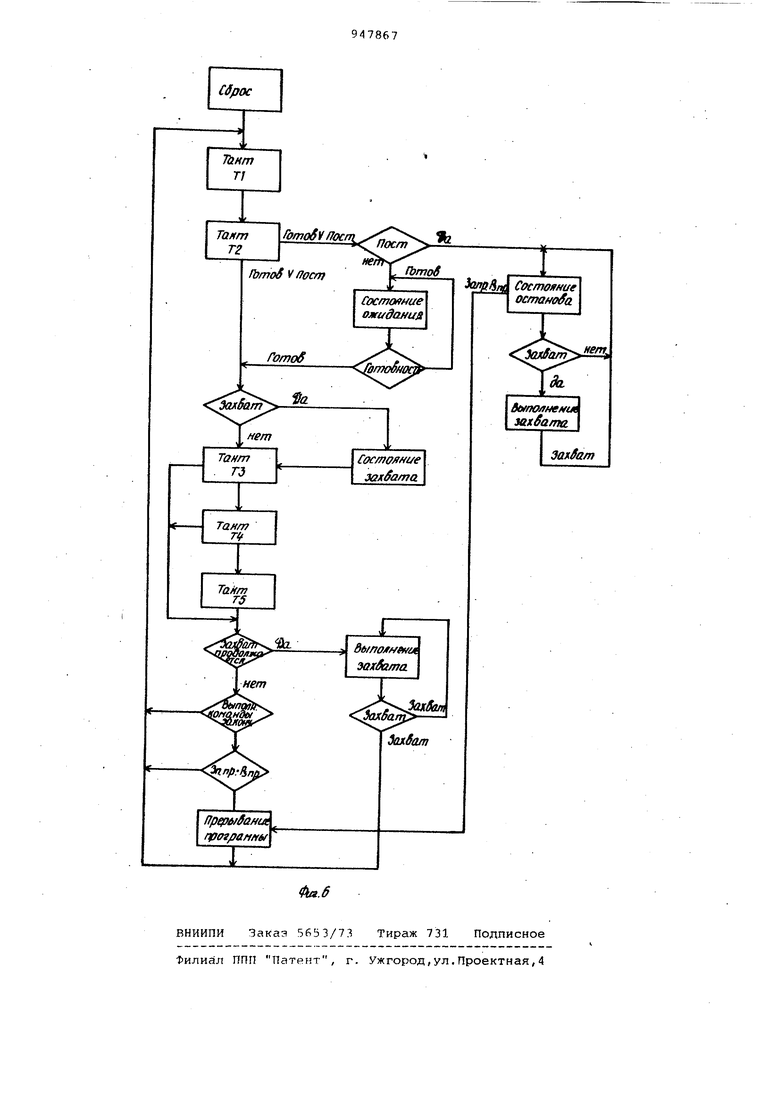

На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 - блок-схема блока приоритетного распределения интерфейсной магистрали; на фиг.З - блок-схема контроллера интерфейса; на фиг.4 блок-схема блока управления асинхронным обменом; на фиг.5 - блок-схема микропроцессора; на фиг. 6 . алгоритм работы микропроцессора.

Устройство содержит блок 1 приоритетного распределения интерфейсной магистрали, блок 2 приоритетного

с прерывания, контроллер 3 интерфейса, микропроцессор 4, блок 5 управления асинхронным обменом, триггер 6 запроса, блок 7 памяти, блок 8 ввода-вывода, интерфейсная магистраль 9, шина 10 запроса, шина 11 разрешения 11.

Блок 1 приоритетного распределения интерфейсной магистрали содержит формирователь 12 импульсов, регистр 13, дешифратор 14, узел 15 приоритетного сравнения, элемент -16 задержки, дешифратор 17.

Контроллер 3 интерфейса содержит элемент И 18, первый и второй групповые клапаны 19 и 20, первый и второй регистры 21 и 22; триггер 23, элемент 24 задержки, шифратор 25. Блок 5 управления асинхронным обменом содержит формирователь 26 импульсов., элемент 27 задержки,

5 элемент И 28, генератор 29 тактовых сигналов и триггеры 30-32.

Микропроцессор 4 содержит буфер данных 33, арифметикологический блок 34 (АЛУ), регистр 35 команд,

Q дешифратор 36 инструкций, регистры 37 общего назначения, счетчик 38 команд, регистр 3 адреса, буфер 40 регистра адреса, блок 41 синхронизации и управления. В устройстве приг менен микропроцессор серии К580ИК80, КО.348.393 ТУ.

Предлагаемое устройство обеспечивает функционирование в следующих режимах: организации программного обмена; организации прерывания микропроцессора; организации активного доступа к интерфейсной магистрали.

Режим организации программного 5 обмена. Работа устройства в этом режиме осуществляется под воздействием микропроцессора 4, который выполняет операции записи информации в блоки памяти и ввода-вывода, а также.операции чтения информации из блоков памяти и ввода-вывода. В начале каждого машинного цикл обращения к блоку памяти или блоку ввода-вывода в такте Т1 микропроце сор 4 устанавливают на адресньох ши нах код адреса, а на шинах данных код состояния микропроцессора.Конт роллер 3 в соответствии с кодом состояния осуществляет формировани интерфейсного исполнительного сигнала, а также вырабатывает сигналнеготовности, который подается на вход ГОТОВ: микропроцессора. В такте Т2 микропроцессор выдает на шины данньох информа11,ионные сигналы (или подключает шины данных для приема информации). К этому момент микропроцессор 4 совместно с контроллером 3 заканчивают формировани всех сигналов, необходимых для обмена информацией, однако подключение их к интерфейсной магистрали непроизводится до тех пор, пока на это не будет получено разрешени от блока 1, Для этого контроллер 3 через время Т после выдачи микропроцессору сигнала неготовности взводит триггер 6 в единичное сос тояние. При этом с выхода триггера на одну из линий шины 10 подается сигнал запроса доступа к интерфейс ной магистрали, Блок 1 фиксирует данный запрос и в случае, если по по интерфейсной магистрали не прои водится цикл обмена другим активным устройством и нет запроса более вы соким приоритетом, выдает по соответствующей линии шины 11 сигнал разрешения. По этому сигналу блок 5 начинает вырабатывать последовательность сиг налоб управления, поступающих на контроллер 3, которые обеспечивают подключение к интерфейсной магистра ли сигналов микропроцессора, В случае выполнения микропроцессором операции записи к интерфейсно магистрали подключаются сигналы адресные АДР, информационные ИНФ и с некоторой задержкой Г. исполнительн сигнал записи ЗАП, Адресуемый блок памяти или блок ввода-вывода, приня сигнал записи ЗАП, осуществляет при выданной микропроцессором информаци и отвечает сигналом ответа ОТВ, При выполнении микропроцессором операций чтения в интерфейсную магистраль вьщаются адресные сигналы АДР и исполнительный сигнал чтения ЧТН, а информационные входы контрол лера 3 подготавливаются для приема информации. По сигналу чтение ЧТН . адресуемый блок выдает в интерфейсную магистраль информационные сигналы и сопровождает их сигналом ответа ОТВ. Приняв сигнал ответа ОТВ, контроллер 3 устанавливает на шине ГОТОВ микропроцессора сигнал готовности, а в случае выполнения операций чтения производит также занесение информационного сообщения в буферный регистр (расположенный в контроллере 3). Блок 5 управления асинхрон«ым обменом по сигналу ответ.ОТВ организует отключение сигналов микропроцессора от интерфейсной магистрали. Сначала отключается исполнительный сигнал ЗАП и ЧТН..На это адресуемый элемент отвечает сбросом сигнала ответ ОТВ (а при операциях чтения и сбросом информационных сигналов ИНФ), После сброса сигнала ответ ОТВ блок 5 отключает адресные сигналы (при операциях записи и информационные), а также устанавливает триггер 6 в нулевое состояние, что вызывает сброс сигнала запроса интерфейсной магистрали. При этом блок 1 сбрасывает сигнал разрешения, соответствующий данному сигналу запроса. В этот момент сигналы микропроцессора полностью отключены от интерфейсной магистрали и ее используют другими активными устройствами,подключенными к ней. Микропроцессор анализирует сигнал готовности в конце такта Т2. Если к этому моменту времени уже произведен цикл обмена (следовательно на входе ГОТОВ микропроцессора установлен сигнал готовности), то микропроцессор переходит в такт ТЗ и осуществляет выполнение внутренних операций, В случае, когда к концу такта Т2 еще не произведен цикл обмена, то на входе ГОТОВ присутствует сигнал неготовности и микропроцессор входит в режим ожидания TW. Это происходит, например, при работе с медленно действующим блоком ввода-выв ода. Микропроцессор входит в режим ожидания и в том случае, при запросе устройством интерфейсной магистрали по ней производится цикл обмена внешним активн1лм устройством. Блок 1 при этом не выдает сигнала разрешения на доступ микропроцессора к интерфейсной магистрали до тех пор, пока внешнее активное устройство не закончит цикл обмена, и следовательно, после получения сигнала разрешения устройство не успеет произвести свой цикл обмена до окончания такта Т2 микропроцессора, Таким образом, ожидание устройством разрешения доступа к интерфейсной магистрали осуществляется аналогично тому, как и ожидание при работе с медленно действующими внешними устройствами. Количестйо тактов ожидания TW микропроцессора не ограничивается. Микропроцессор в конце каждого так TW производит анализ сигнала готов ности и при его наличии переходит в такт ТЗ. В такте ТЗ микропроцессор при выполнении операции чтения осуществ ляет прием информации, предваритель но занесенной в буферный регистр контроллера 3. Режим организации прерывания мик ропроцессора. Внешнее устройство, требующее прерывания текущей программы, устанавливает наодной из линий ЗПР интерфейсной магистрали 9 сигнал запроса прерывания. Количество линий ЗПР соответствует количеству уровне прерывания микропроцессора. Обычно количество уровней прерывания для микропроцессоров равно 8. Каждому уровню прерывания присвоен соответствукщий приоритет. Блок 2 анализирует наличие на линиях сигналов запроса прерывания. Если в данный момент микропроцессор не обслуживает прерывание с более высоким приоритетом, чем текущий запрос прерывания, то блок 2 формирует код вектора.прерывания, соответствующий данному запросу и выдае микропроцессору сигнал прерывания ПРЕР. Микропроцессор после выполнения очередной команды воспринимает этот сигнал ПРЕР (если вход прерыва ния не заблокирован микропроцессором) и во время обращения за следую щей командой в коде состояний устйнавливает сигнал подтверждения запр са прерывания. КонтроллеЬ 3 в соответствии с ко дом состояния микропроцессора формирует исполнительный сигнал разрешения прер-ывания РПР. Далее, производится запрос доступа к интерфейсной магистрали (взводится триггер 6 и при получении с блока 1 сигнала разрешения блок 5 организует по интерфейсной магистрали цикл обмена, аналогичный тому, который имеет мес то при выполнении микропроцессором операций чтения в режиме программно го обмена. Однако в этом случае адресные сигналы не имеют смысла, а блок 2 непосредственно воспринимает исполнительный сигнал, по кото рому выдает в интерфейсную магистраль код вектора прерывания и сигна ответа ОТВ. По сигналу ответ ОТВ контроллер 3 производит прием кода вектора прерывания, а блок 5 органи зует отключение сигналов микропроцессора от интерфейсной магистрали и выдает микропроцессору сигнал готовности (аналогично описанному в режиме программного обмена). Б такте ТЗ микропроцессор производит прием вектора прерывания и организует переход на выполнение соответствующей программы обслуживания данного прерывания. Вектор прерывания воспринимается микропроцессором как команда перехода. При одновременном поступлении с нескольких внешних устройств запросов на прерывание, блок 2 формирует код вектора прерывания, соответствующий запросу, имеющему наивысший приоритет. Режим организации активного доступа к интерфейсной магистрали. Организация доступа к интерфейсной магистрали является единой для всех активных устройств, подключенных к ней (в том числе и для микропроцессора предлагаемого устройства). Каждое активное устройство использует одну линию шины 10 запроса и соответственно одну линию шины 11 разрешения. Когда активному устройству нужно произвести цикл обмена по интерфейсной магистрали, оно формирует сигнал запроса, который по шине 10 подается на блок 1. Если в данный момент интерфейсная магистраль свободна (другое активное устройство не производит по ней цикл обмена), то блок 1 выдает по соответствующей предлагаемому устройству линии шины 11 сигнал разрешения. В случае, когда активное устройство требует доступа к интерфейсной магистрали, а она занята, блок 1 выдает сигнал разрешения предлагаемому устройству только после того, как магистраль освободится. В каждый конкретный момент времени блок 1 разрешает доступ к интерфейсной магистрали только одному активному устройству. Получив сигнал разрешения, активное устройство осуществляет цикл обмена (аналогично описанному выше), отключается от интерфейсной магистрали и сбрасывает свой сигнал запроса. Блок свою очередь, сбрасывает сигнал разрешения, соответствующий данному запросу. После этого интерфейсная магистраль свободна и блок 1 разрешает доступ к интерфейсной магистрали другому активному устройству. Таким образом, циклы обмена по интерфейсной магистрали следуют один за другим. При одновременном поступлении запросов от нескольких активных устройств блок 1 выдает -сигнал разрешения на пользование интерфейсной магистралью устройству, имеющему наивысший приоритет. Остальные запросы удовлетворяются в порядке понижения приоритетности. Приоритет устройств, подключенных к I интерфейсной магистрали, определяется номером линии шины 10, а следовательно, и шины 11, которую использует предлагаемое устройство для запроса интерфейсной магистрали Устройства, подключенные к линиям с более высоким номером, обладают и более высоким приоритетом. Номера линий шин 10 и 11 определяют уровень запроса доступа к интерфейсной магистрали. Блок 1 обеспечивает возможность программно-изменяемой блокировки уровней запроса Это осуществляется путем засылки активным устройством, например микр процессором устройства, соответствующего кода в блок 1. Активные уст ройства, имеющие уровень запроса меньший, чем абсолютное значение кода блокировки, засланного в блок не имеют доступа к интерфейсной магистрали . Команды микропроцессора выполниются по машинным циклам (М). В зави симости от типа команд их выполнение осуществляется за один, два, три, четыре или пять типичных машин ных циклов. В каждом манинном цикле осуществляется обращение к ЗУ или УУВ, каждый машинный цикл выполняет ся по машинным тактам (Т). Машинный цикл длится три, четыре или пять машинных тактов. Число тактов в цик ле определяется.кодом выполняемой команды. Длительность каждого такта равна периоду тактовой частоты и определяется как интервал времени между двумя соседними импульсами фа зы Ф1. При частоте импульсов фазы 2 МГу-длительность каждого такта 500 Микропроцессор находится в трех состояниях: Ожидание, Захват Останов. Длительность этих состояний определяется внешними управляющими сигналами. Эти состояния синхронизированы машинными тактами. Алгоритм работы микропроцессора (фиг.6) доказывает последовательнос перехода от такта к такту в машинно цикле и влияние внешних сигналов Готовность, Захват и Запрос прерывания на выполнение машинного цикла. При подаче на микропроцессор сиг нала Сброс машинный цикл начинается с такта Т1. В этом такте н адресные шины выдается адрес ячейки ЗУ, а на шины данных выводится информация состояния. Из такта Т1 микропроцессор всегда переходит в такт Т2. В этом такте производится анализ входных сигналов Готовность, Захват и сигнала состояния Подтверждение останова (Пост), формируемого при выполнении команды HUT. Если на входе Готовность напряжение логического нуля вьрабатывается сигнал состояния Пост, то микропроцессор переходит в состояние ожидания (TO) или в состояние Останов (TOCT) соответственно. В состоянии Ожидание микропроцессор .находится до тех пор, пока на вход Готовность не подается напряжение логической едини цы. Если на входе Готовность напряжение логической единицы, то микропроцессор переходит в такт ТЗ. В такте ТЗ происходит прием информации на регистр команд или регистры общего назначения из внешних устройств по каналу данных. В этом такте происходит анализ сигнала Захват. Если на входе Захват напряжение логической единицы, то после окончания такта ТЗ микропроцессор переходит в режим Захват. После выполнения такта ТЗ цикл заканчивается и микропроцессор переходит, в такт Т4. После выполнения такта Т4 цикл также заканчивается и микропроцессор переходит в такт Т5. После выполнения такта Т5 цикл заканчивается. Эти переходы, т.е. число тактов в циклед зависят от кода выполняемой команды. В течение тактов Т4 и Т5 выполняются внутренние операции микропроцессора. В это время не происхсдит обращение к ЗУ, УВВ и не требуется подачи внешних управляющих сигналов. В конце машинного цикла происходит анализ сигнала Захват. Если на вход Захват подается напряжение логической единицы, то продолжается выполнение режима Захват-. В противном случае происходит анализ окончания выполнения команды. Если команда не закончена, то микропроцессор начинает выполнять следующий машинный цикл с такта Т1. После выполнения последнего цикла команды анализируется сигнал на входе рос прерывания (Зп пр) . Напряжение логической единицы, поданное на вход Запрос прерывания , установит внутренний триггер запроса прерывания в единичное состояние, если на выходе Разрешение прерывания ( ) напряжение логической единицы. При этом микропроцессор начинает выполнять действия по прерыванию программы. Если на входе Запрос прерывания напряжение логического нуля, то микропроцессор начинает выполнять первый цикл йовой команды с такта Т1. Таким образом, такая организация обмена по интерфейсной магистрали микропроцессора предлагаемого уст.ройства блоком памяти и блоком

ввода-вывода позволяет значительно повысить производительность микропроцессорных систем, содержащих несколько активных устройств, а также расширить диапазон применения мик ропроцессорных устройств.

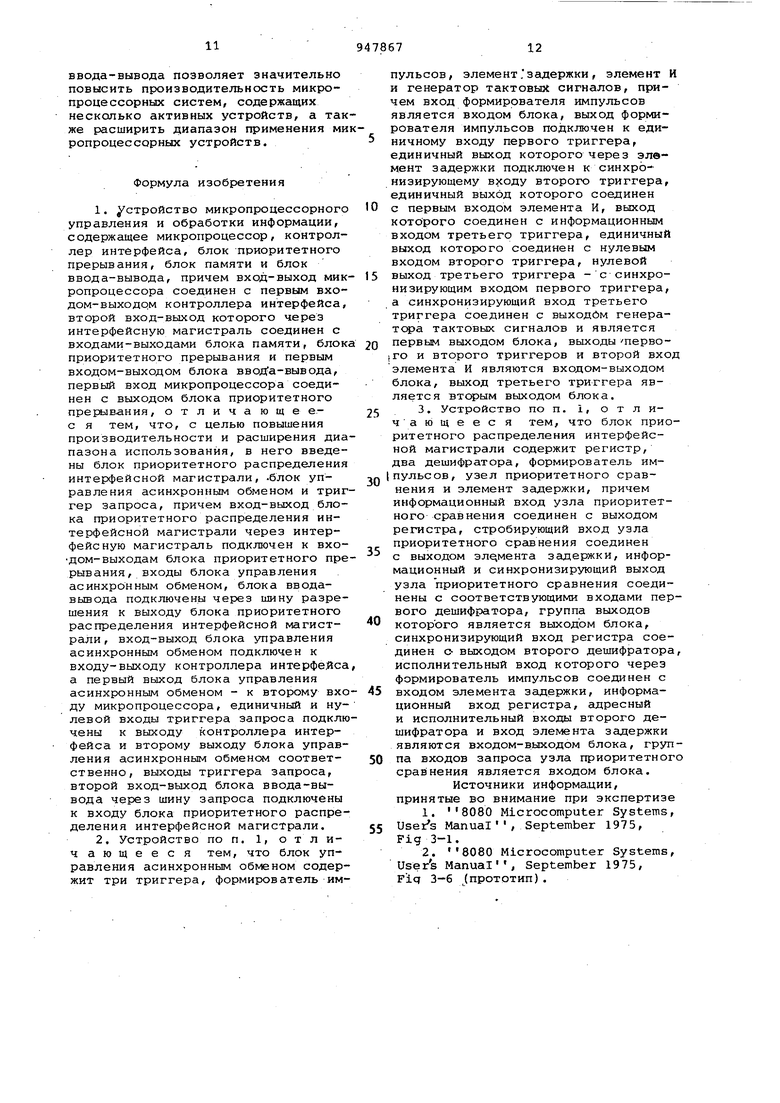

Формула изобретения

единичный выход которого через элемент задержки подключен к синхронизирующему входу второго триггера, единичный выход которого соединен

0 с первым входом элемента И, выход которого соединен с информационным входом третьего триггера, единичный выход которого соединен с нулевым входом второго триггера, нулевой

5 выход третьего триггера - с синхронизирующим входом первого триггера, а синхронизирующий вход третьего триггера соединен с выходим генератс а тактовых сигналов и является

первым выходом блока, выходыперво|ГО и второго триггеров и второй вход элемента И являются входом-выходом блока, выход третьего триггера является вторым выходом блока.

5 3, Устройство по п. i, о т л ичающеес я тем, что блок приоритетного распределения интерфейсной магистрали содержит регистр, два дешифратора, формирователь имр пульсов, узел приоритетного сравнения и элемент задержки, причем информационный вход узла приоритетного сравнения соединен с выходом регистра, стробирующий вход узла приоритетного сравнения соединен с выходом элемента задержки, информационный и синхронизирующий выход узла приоритетного сравнения соединены с соответствующими входами первого дешифратора, группа выходов

О которого является выходом блока,

синхронизирующий вход регистра соединен с- выходом второго дешифратора, исполнительный вход которого через формирователь импульсов соединен с

5 входом элемента защержки, информационный вход регистра, адресный и исполнительный входы второго дешифратора и вход элемента задержки являются входом-выходом блока, группа входов запроса узла приоритетного сравнения является входом блока.

Источники информации, принятые во внимание при экспертизе

Fig 3-1.

НвимеЮ

(f

19

Af.

Zi

МР

инФ

УГН.ЗАП.

25

Hffodtflffo S

fr.t

/f ueffpyff

ff модулю S

y

5

Ч:

/

tt

rj

I:

f

w

n

r 29

фu,l I I I 1.1 M I

D С Я

УГб

ч

« .ll

j{,4j,z)

I I I II r г I

A,AWMVAW.

Авторы

Даты

1982-07-30—Публикация

1979-08-09—Подача