Изобретение относитдя к вычислительной технике, может быть использовано в вычислительных системах для сопряжения ЭВМ с каналами связи и является усовершенствованием извест- HOFO устройства по авт. св. № 1012235 , Цель изобретения - расширение класса решаемых задач для уменьшения времени, -затрачиваемого ЭВМ на проведение обмена с устройствами нижнего уровня.:

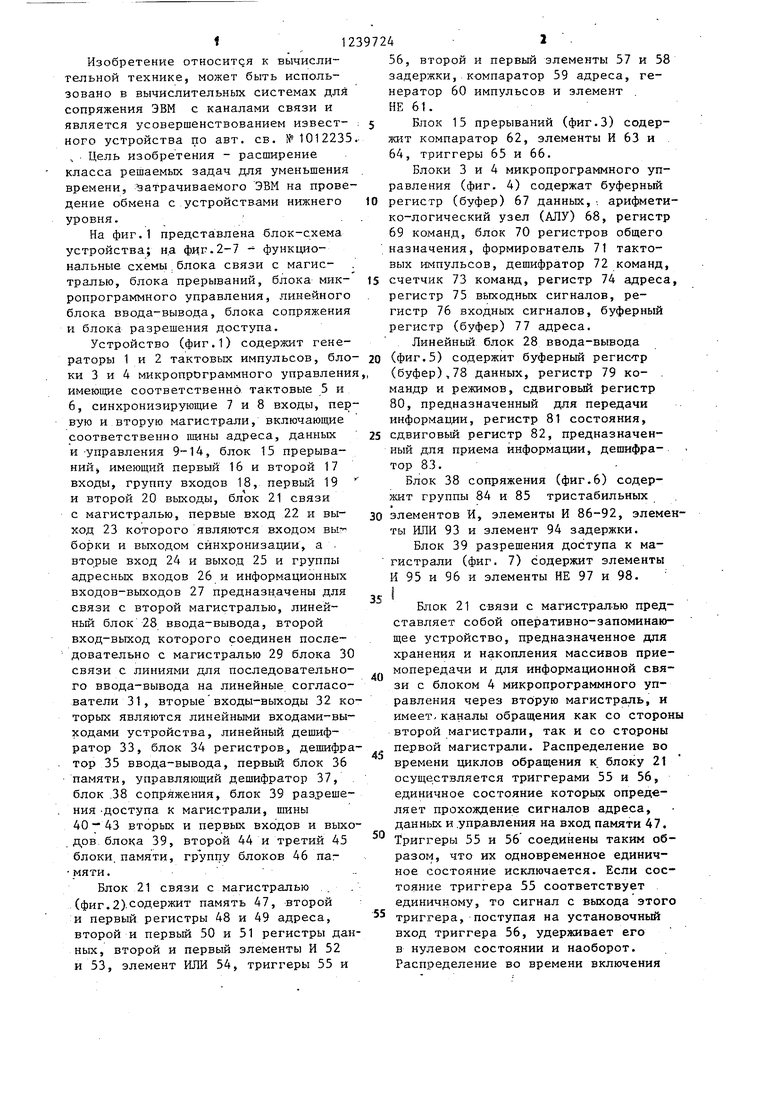

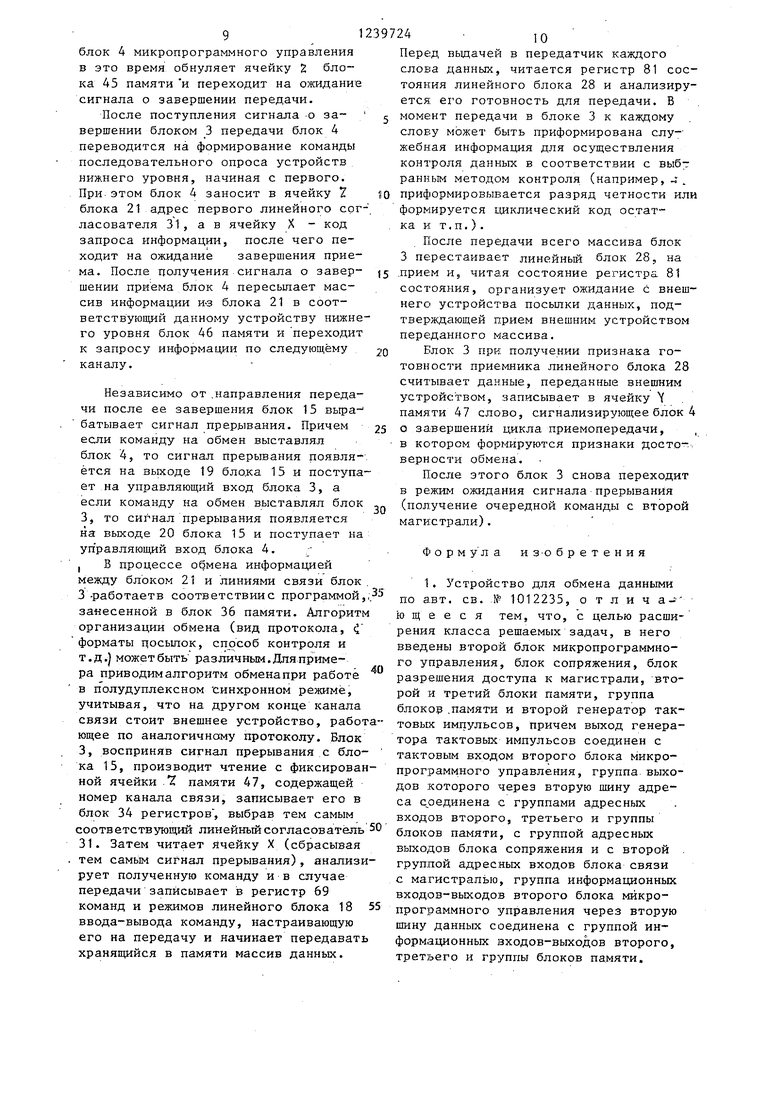

На фиг.1 представлена блок-схема устройства; на фиг.2-7 - функциональные схемы,блока связи с магистралью, блока прерываний, блока микропрограммного управления, линейного блока ввода-вывода, блока сопряжения и блока разрешения доступа.

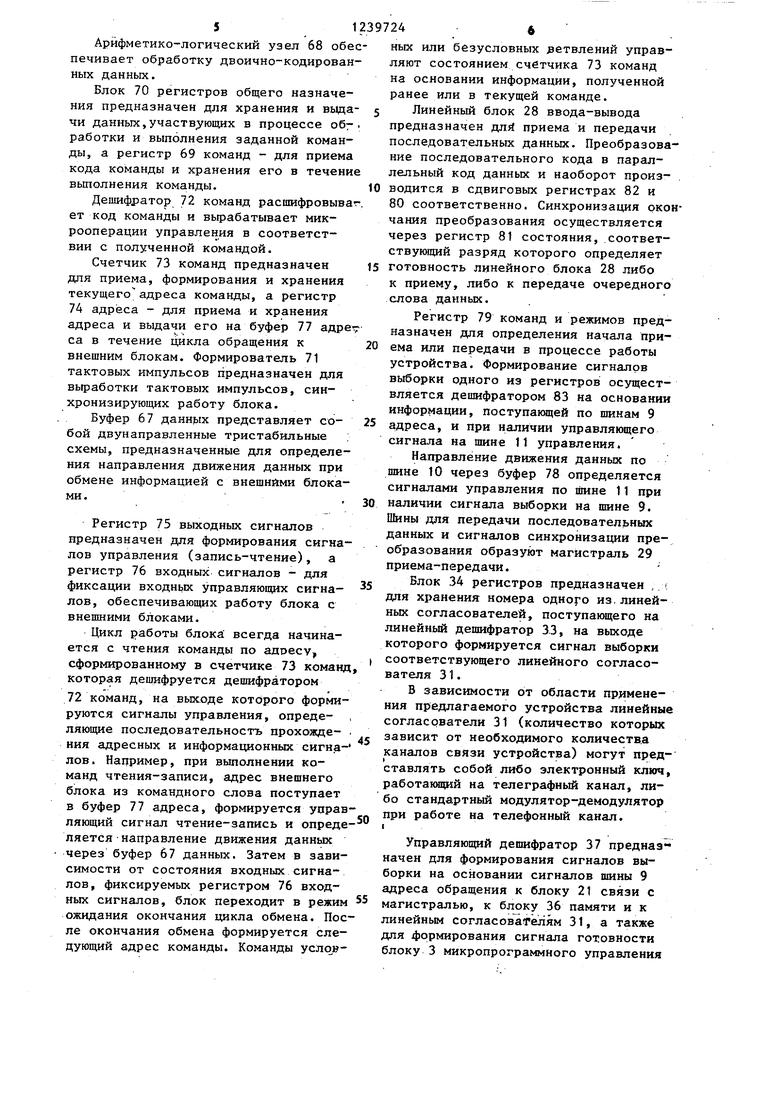

Устройство (фиг.1) содержит генераторы 1 и 2 тактовых импульсов, блоки 3 и 4 микропрограммного управлени имеющие соответственно тактовые 5 и 6, синхронизирующие 7 и 8 входы, первую и вторую магистрали, включающие соответственно пщны адреса, данных и -управления 9-14, блок 15 прерываний, имеющий первый 16 и второй 17 входы, группу входов 18, первьй 19 и второй 20 выходы, блок 21 связи с магистралью, первые вход 22 и выход 23 которого являются входом вып борки и выходом синхронизации, а . вторые вход 24 и выход 25 и группы адресных входов 26 и информационных входов-выходов 27 предназначены для связи с второй магистралью, линейный блок 28 ввода-вывода, второй вход-выход которого соединен последовательно с магистралью 29 блока 30 связи с линиями для последовательного ввода-вывода на линейные согласо- ватели 31, вторые входы-выходы 32 которых являются линейными входами-выходами устройства, линейный дешифратор 33, блок 34 регистров, дешифратор 35 ввода-вывода, первый блок 36 -памяти, управляющий дешифратор 37, блок .38 сопряжения, блок 39 разрешения -доступа к магистрали, шины 40 - 43 вторых и первых входов и выхо д,ов блока 39, второй 44 и третий 45 блоки, памяти, группу блоков 46 па- мяти.

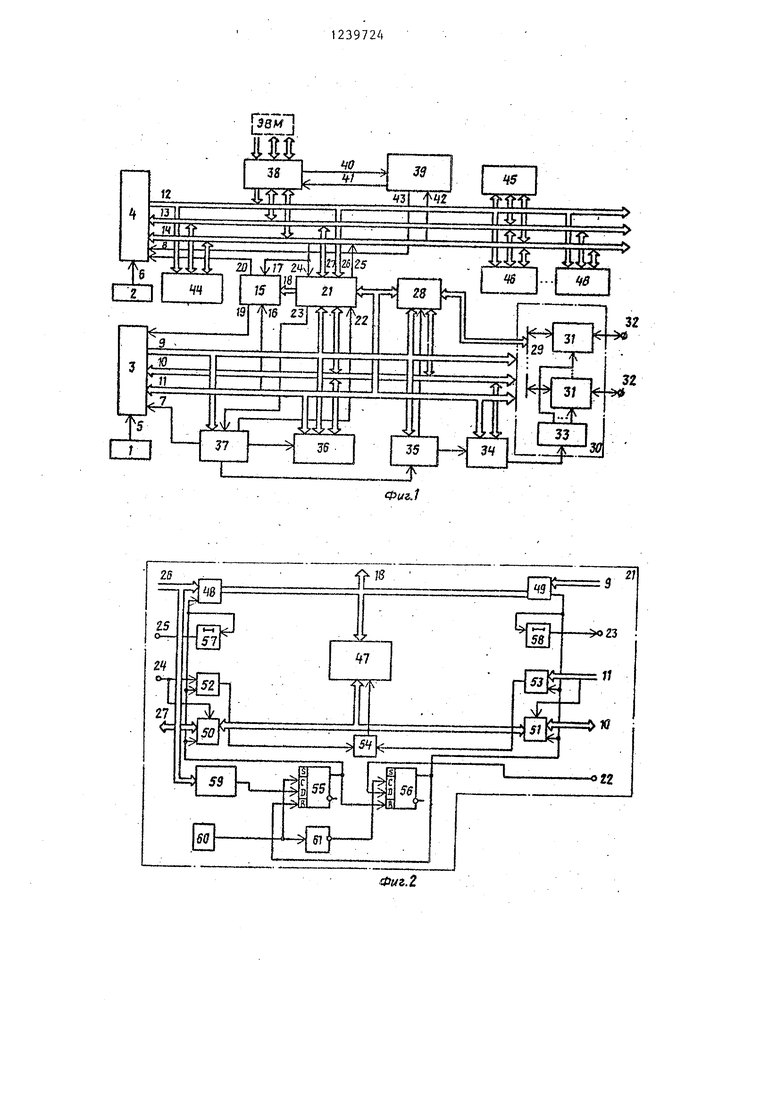

Блок 21 связи с магистралью , . (фиг.2).содержит память 47, второй и первьй регистры 48 и 49 адреса, второй и первый 50 и 51 регистры данных, второй и первый элементы И 52 и 53, элемент ИЛИ 54, триггеры 55 и

5

0

5

0

5

0

5

0

5

56, второй и первый элементы 57 и 58 задержки, компаратор 59 адреса, генератор 60 импульсов и элемент НЕ 61.

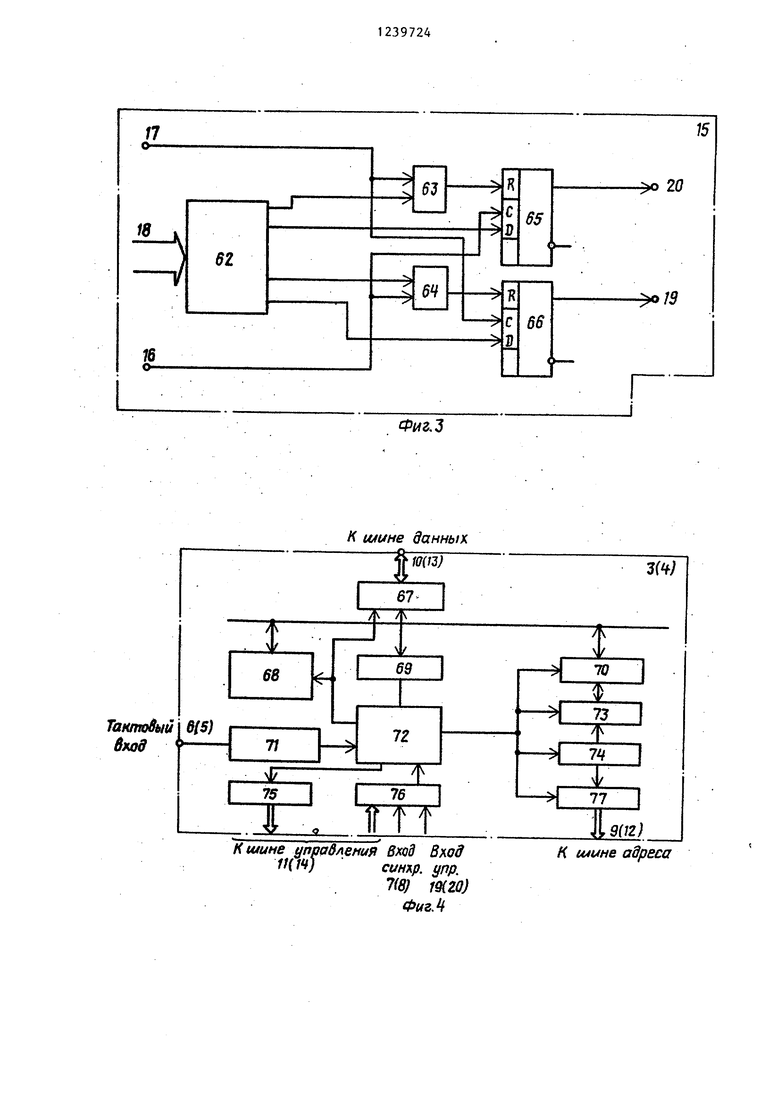

Блок 15 прерываний (фиг.З) содержит компаратор 62, элементы И 63 и 64, триггеры 65 и 66.

Блоки 3 и 4 микропрограммного управления (фиг. 4) содержат буферньш регистр (буфер) 67 данных, -. арифметико-логический узел (АЛУ) 68, регистр 69 команд, блок 70 регистров общего назначения, формирователь 71 тактовых импульсов, дешифратор 72 команд, счетчик 73 команд, регистр 74 адреса, регистр 75 выходных сигналов, регистр 76 входных сигналов, буферный регистр (буфер) 77 адреса.

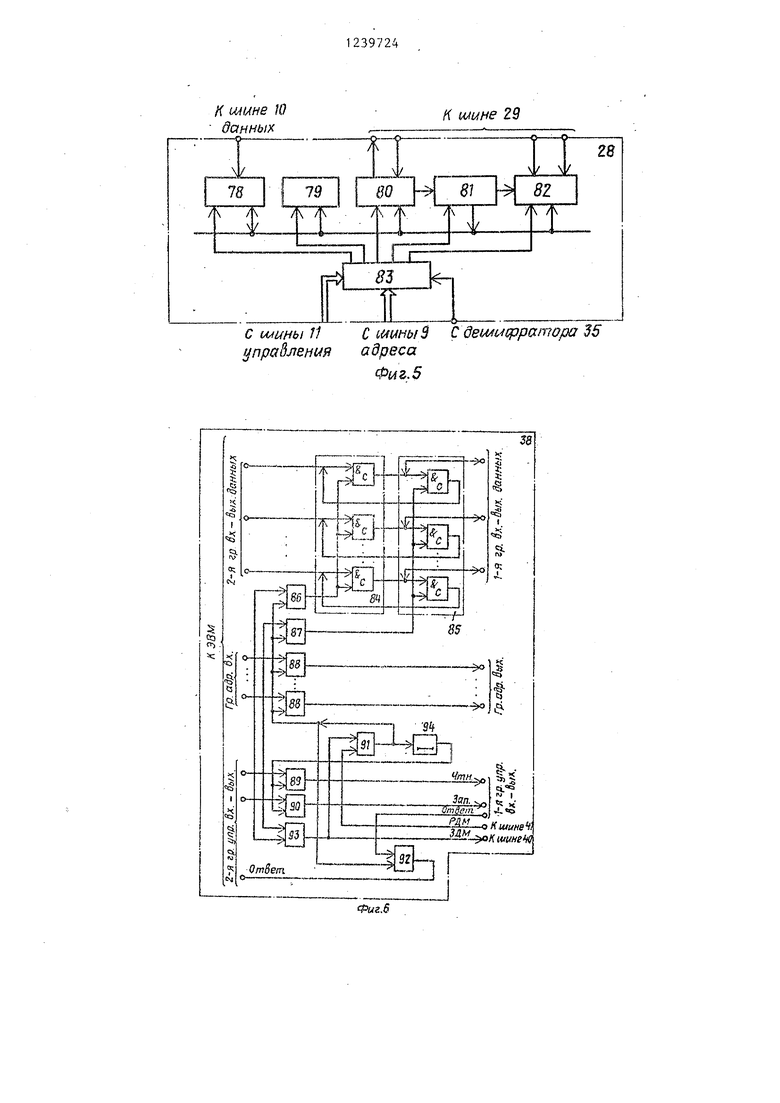

Линейньй блок 28 ввода-вывода (фиг.5) содержит буферньй регистр (буфер),78 данных, регистр 79 ко- . мандр и режимов, сдвиговый регистр 80, предназначенный для передачи информаиди, регистр 81 состояния, сдвиговьй регистр 82, предназначенный для приема информации, дешифратор 83.

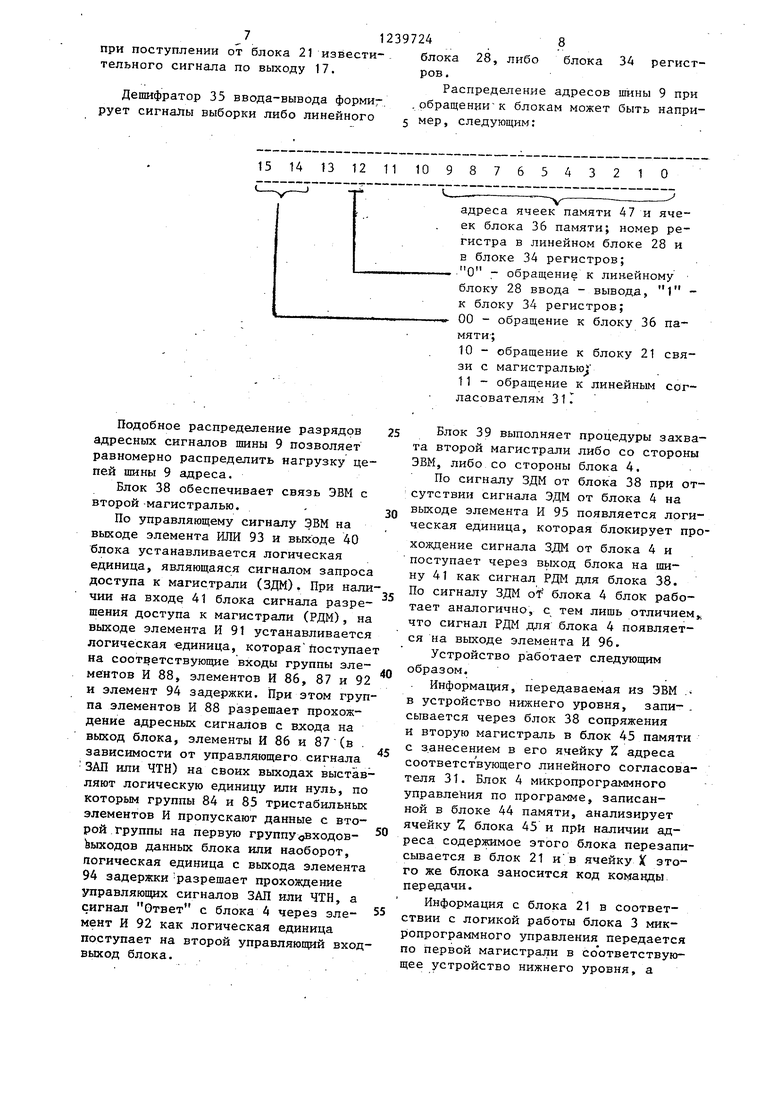

Блок 38 сопряжения (фиг.6) содержит группы 84 и 85 тристабильных элементов И, элементы И 86-92, элементы ИЛИ 93 и элемент 94 задержки.

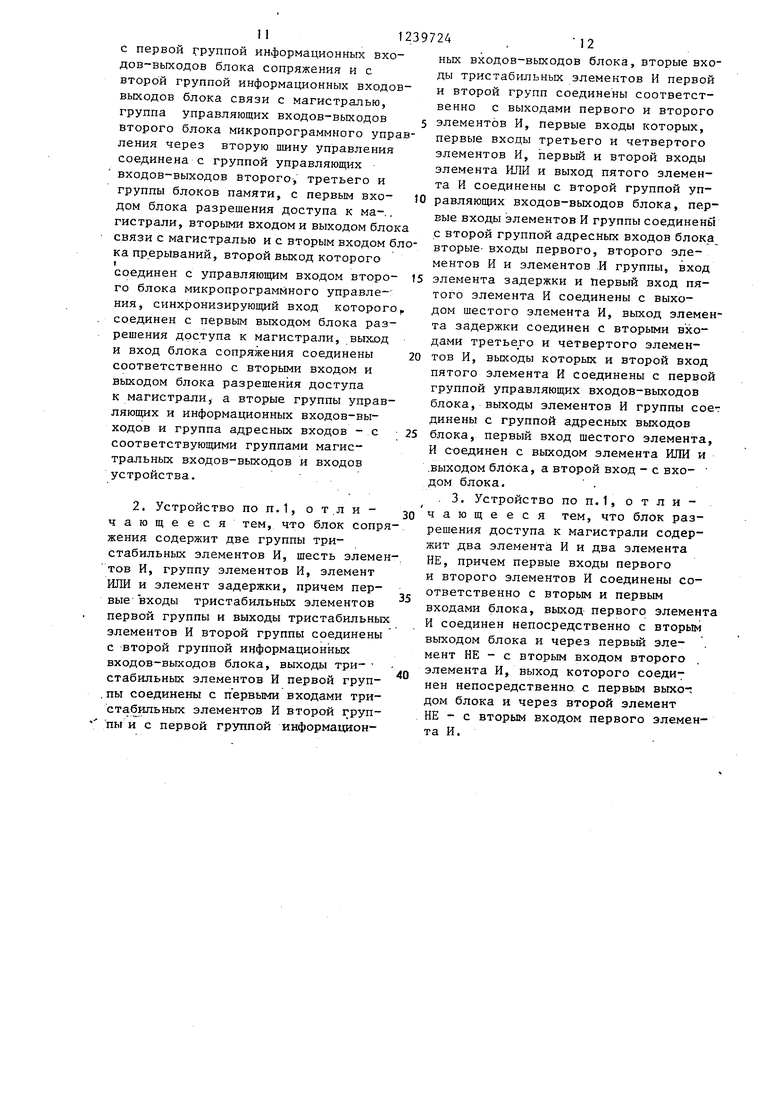

Блок 39 разрешения доступа к магистрали (фиг, 7) содержит элементы И 95 и 96 и элементы НЕ 97 и 98.

I

Блок 21 свя1зи с магистрал-ью представляет собой оперативно-запоминающее устройство, предназначенное для хранения и накопления массивов прие- мопередачи и для информационной связи с блоком 4 микропрограммного управления через вторую магистраль, и имеет- каналы обращения как со стороны второй магистрали, так и со стороны первой магистрали. Распределение во времени циклов обращения к блоку 21 осуществляется триггерами 55 и 56, единичное состояние которых определяет прохождение сигналов адреса, данных и .управления на вход памяти 47. Триггеры 55 и 56 соединены таким образом, что их одновременное единичное состояние исключается. Если состояние триггера 55 соответствует единичному, то сигнал с выхода этого триггера, поступая на установочный вход триггера 56, удерживает его в нулевом состоянии и наоборот. Распределение во времени включения

триггеров осуществляется взаимоинверсными сигналами, поступающими с генератора 60, с использованием элемента НЕ 61, на их входы синхронизации. Сигналы, указывающие на начало цикла обращения, поступают на информационные входы триггеров. Сигнал обращени со стороны второй магистрали формируется на выходе компаратора 59 в зависимости от состояния входов 26, соединенных с шиной адреса. Наличие компаратора 59 определяется различной адресной емкостью шины адреса и памяти 47, Например, для организации адресации к блокам 45 и 46 памяти необходима шестнадцатиразрядная шина адреса (входы 26), а емкость памяти 147 составляет 1 килослово, для адре сации к которой необходима всего лишь десятиразрядная шина адреса. 0с таватеся шесть разрядов адреса являютс как бы номером части всего возможно- по массива и,они сравниваются с заранее заданным номером в компараторе 59 адреса. При совпадении заданного номера с номером, соответствующим состоянию шины адреса, на выходе компаратора 59 формируется сигнал выборки. Если состояние триггера 56 срот ветствует нулевому состоянию, то триггер 55 по фронту синхросигнала устанавливается в единичное состоя- ние. Сигнал с выхода этого триггера, поступая на входы регистра 50 данных

элемента- И 52, регистра .48 аддеса и элемента задержки 57, разрешает прохождение сигналов адреса, управления данных на входы памяти 47 и..формирование сигнала Ответ блоку 4. Сигнал по входу 24 с шины 14 управления второй магистрали определяет направление движения данных через регистр 50 (за пись или чтение) .

Если состояние триггера 56 соот-.- ветствует единичному состоянию, то установка триггера 55 задерживается до установки триггера 56 в нулевое состояние, задерживая -тем самым ответ на выходе 25 для блока 4 и прохождение сигналов адреса, управления и данных. - - ,

Признаком обращения к блоку 21 со стороны перв ой магистрали является сигнал выборки на входе 22. Работа . блока 21 в последующем цикле аналогична за исключением того, что в дан ном цикле участвуют регистры 49 и 51, элемент 58 задержки и элемент И 33.

10

20

25

я, - я

- 55

2397244

Выход 18 блока 21 предназначен для сигнализации об адресе выбираемой ячейки из памяти 47.

Блок 15 прерываний предназначен для формирования сигналов прерывания в сторону блока 4 через выход 20, а в сторону блЬка 3 - через выход 19. Формирование сигналов прерывания осуществляется по коду адреса обращения к блоку 21 и в зависимости от режима обращения (чтение, запись).

Из всего NfaccHBa памяти 47 блока 21 выделены три адреса (три ячейки) ,Х, Y и Z, которые выполняют функ(5 ции состояния (Y), команды (у) и адг реса линейного согласования (z). Формирование сигналов, соответствующих обраЕ1;ению к одной из ячеек, осуществляется компаратором 62 методом сравнения кода текущего адреса обращения с заранее определенными кодами.,Коды текущего адреса обращения поступают на входы 18 с выхода блока 21.

Если производится обращение к ячейке X , то на выходах компаратора 62, соединенных с элементом И 64 и триггером 50, формируется сигнал, и в зависимости от наличия сигнала на входах 17 или 16 триггер 66 устанавливается либо в единичное состояние, либо в нулевое. Следовательно, если производится обращение к ячейке . X со стороны второй магистрали, то триггер 66 устанавливается в единич ное состояние (формируется сигнал прерывания в сторону блока 3 шкро- программного управления), если производится обращение к ячейке X со стороны первой магистрали, то триггер

66 устанавливается в нулевое состояние (сбрасывается сигнал прерывания в сторону блока 3) .

При обращении к ячейке Y управление триггером 65 (сигналы прерыва45 ния в сторону второй магистрали) осуществляется аналогично, только с

использованием элемента И 63. I

Блоки 3 и 4 предназначены для реализации программ, хранящихся соответственно в блоках 36 и 44 памяти, в результате выполнения которых производится координация работы бло ков устройства. Блоки 3 и 4 выполняют определенный список команд, включающий команды чтения-записи, . логической и арифметической обработки данных, условных и безусловных ветвлений.

30

50

Арифметико-логический узел 68 обесечивает обработку двоично-кодированых данных.

Блок 70 регистров общего назначения предназначен для хранения и вьща- и данных,участвующих в процессе обг аботки и выполнения заданной команы, а регистр 69 команд - для приема ода команды и хранения его в течение выполнения команды.

Дешифратор 72 команд расшифровывав, ет код команды и вьфабатывает микооперации управления в соответстии с полученной командой.

Счетчик 73 команд предназначен ля приема, формирования и хранения текущего адреса команды, а регистр 74 адреса - для приема и хранения адреса и выдачи его на буфер 77 адрет са в течение цикла обращения к внешним блокам. Формирователь 71 тактовых импульсов предназначен для выработки тактовых импульсов, синхронизирующих работу блока.

Буфер 67 данных представляет собой двунаправленные тристабильные схемы, предназначенные для определения направления движения данных при обмене информацией с внешними блоками.

Регистр 75 выходных сигналов предназначен для формирования сигналов управления (запись-чтение), а регистр 76 входных сигналов - для фиксации входньгх управляющих сигналов, обеспечивающих работу блока с внешними блоками.

Цикл работы блока: всегда начинается с чтения команды по адресу, сформированному в счетчике 73 команд, которая дешифруется дешифратором

72 команд, на выходе которого формируются сигналы управления, определяющие последовательность прохожде- . ния адресных и информационных сигна- лов. Например, при выполнении команд чтения-записи, адрес внешнего блока из командного слова поступает в буфер 77 адреса, формируется управляющий сигнал чтение-запись и опреде ляется направление движения данных через буфер 67 данных. Затем в зависимости от состояния входных сигналов, фиксируемых регистром 76 входных сигналов, блок переходит в режим ожидания окончания цикла обмена. После окончания обмена формируется следующий адрес команды. Команды услов-5

10

15

20

25

30

35

45

50

55

ных или безусловных ветвлений управляют состоянием счетчика 73 команд на основании информации, полученной ранее или в текущей команде.

Линейный блок 28 ввода-вывода предназначен дл51 приема и передачи последовательных данных. Преобразование последовательного кода в параллельный код данных и наоборот произ- . водится в сдвиговых регистрах 82 и 80 соответственно. Синхронизация окончания преобразования осуществляется через регистр 81 состояния, .соответ- ствую1ций разряд которого определяет готовность линейного блока 28 либо к приему, либо к передаче очередного слова данных.

Регистр 79 команд и режимов предназначен для определения начала приема или передачи в процессе работы устройства. Формирование сигналов выборки одного из регистров осуществляется дешифратором 83 на основании информации, поступакщей по шинам 9 адреса, и при наличии управляющего сигнала на шине 11 управления.

Направление движения данных по шине 10 через буфер 78 определяется сигналами управления по шине 11 при наличии сигнала выборки на шине 9. Шны для передачи последовательных данных и сигналов синхронизации преобразования образуют магистраль 29 приема-передачи.

Блок 34 регистров предназначен ,, . для хранения номера одного из. линейных согласователей, поступающего на линейный дешифратор 33, на выходе которого формируется сигнал выборки соответствующего линейного согласо- вателя 31.

В зависимости от области применения предлагаемого устройства линейные согласрватели 31 (количество которых зависит от необходимого количества каналов связи устройства) могут представлять собой либо электронный ключ, работаюпщй на телеграфный канал, либо стандартный модулятор-демодулятор

при работе на телефонный канал. I

Управляюпр1й дешифратор 37 преднаэ начен для формирования сигналов выборки на основании сигналов шины 9 адреса обращения к блоку 21 связи с магистралью, к блоку 36 памяти и к линейным согласователям 31, а также для формирования сигнала готовности блоку 3 микропрограммного управления

при поступлении от блока 21 извести- тельного сигнала по выходу 17.

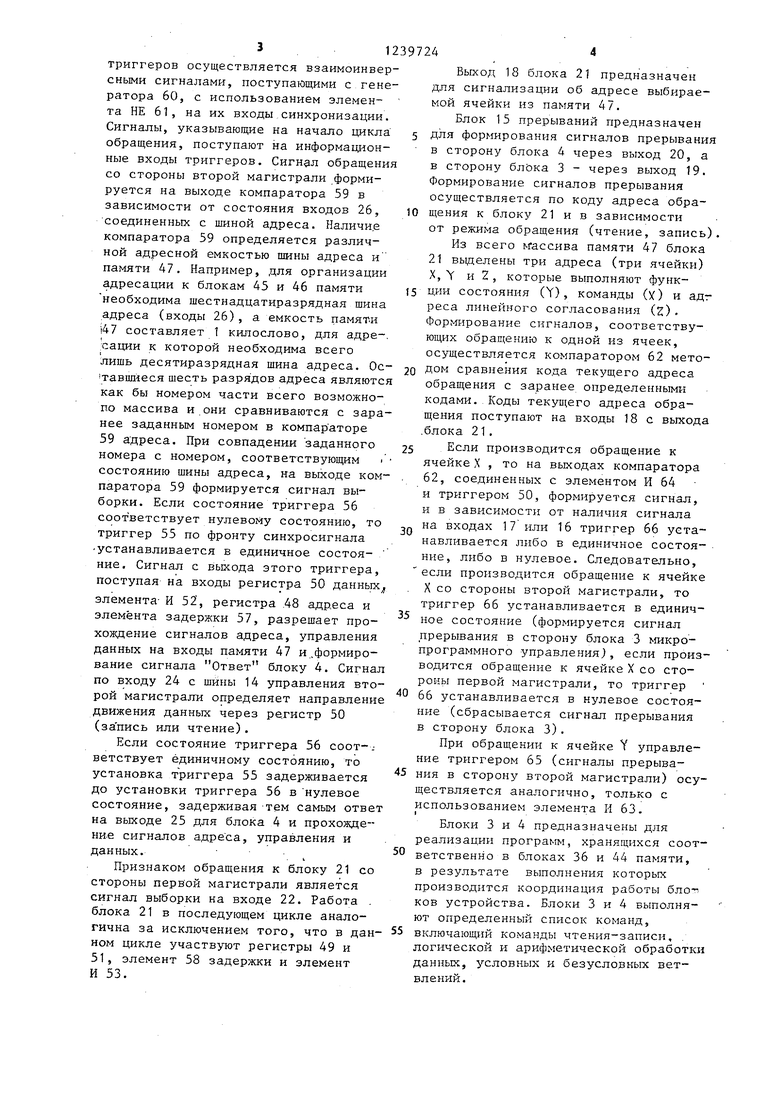

Дешифратор 35 ввода-вывода формиг рует сигналы выборки либо линейного

15 14 13 12 11 10 9

Подобное распределение разрядов адресных сигналов шины 9 позволяет равномерно распределить нагрузку цепей шины 9 адреса.

Блок 38 обеспечивает связь ЭВМ с второй магистралью.

По управляющему сигналу ЭВМ на выходе элемента ИЛИ 93 и выходе 40 блока устанавливается логическая единица, являющаяся сигналом запроса доступа к магистрали (ЗДМ), При наличии на входе 41 блока сигнала разрешения доступа к магистрали (РДМ), на выходе элемента И 91 устанавливается логическая единица, которая поступае на соответствующие входы группы элементов И 88, элементов И 86, 87 и 92 и элемент 94 задержки. При этом группа элементов И 88 разрешает прохождение адресных сигналов с входа на выход блока, элементы И 86 и 87(в зависимости от управляющего сигнала ЗАП или ЧТН) на своих выходах выставляют логическую единицу или нуль, по которым группы 84 и 85 тристабильных элементов И пропускают данные с второй группы на первую группу«входов- выходов данных блока или наоборот, погическая единица с выхода элемента 94 задержки -разрешает прохождение управляющих сигналов ЗАП или ЧТН, а сигнал Ответ с блока 4 через эле- мент И 92 как логическая единица поступает на второй управляющий вход выход блока.

блока 28, либо блока ров,

Распределение адресов .обращении к блокам может 5 мер, следующим;

76543210

- V - адреса ячеек памяти 47 и ячеек блока 36 памяти; номер регистра в линейном блоке 28 и в блоке 34 регистров; О - обращение к линейному блоку 28 ввода - вывода, 1 - к блоку 34 регистров; 00 - обращение к блоку 36 памяти-;

10- обращение к блоку 21 связи с магистралью

11- обращение к линейным сог- ласователям 31Г

Блок 39 выполняет процедуры захвата второй магистрали либо со стороны ЭВМ, либо со стороны блока 4.

По сигналу ЗДМ от блока 38 при от- :сутствии сигнала ЭДМ от блока 4 на выходе элемента И 95 появляется логическая единица, которая блокирует прохождение сигнала ЗДМ от блока 4 и поступает через выход блока на шину 41 как сигнал РДМ для блока 38. По сигналу ЗДМ о блока 4 блок работает аналогично, с тем лишь отличием„ что сигнал РДМ для блока 4 появляется на выходе элемента И 96.

Устройство работает следующим образом.

Информация, передаваемая из ЭВМ в устройство нижнего уровня, запи- . сывается через блок 38 сопряжения и вторую магистраль в блок 45 памяти с з.анесением в его ячейку Z адреса соответствующего линейного согласова- теля 31. Блок 4 микропрограммного управления по программе, записанной в блоке 44 памяти, анализирует ячейку Z блока 45 и при наличии адреса содержимое этого блока перезаписывается в блок 21 и в ячейку К этого же блока заносится код команды передачи.

Информация с блока 21 в соответствии с логикой работы блока 3 микропрограммного управления передается по Первой магистрали в со ответствую- щее устройство нижнего уровня, а

блок 4 микропрограммного управления в это время обнуляет ячейку 2 блока 45 памяти и переходит на ожидание сигнала о завершении передачи.

После поступления сигнала О за- вершении блоком 3 передачи блок 4 переводится на формирование команды последовательного опроса устройств, нижнего уровня, начиная с первого. При этом блок 4 заносит в ячейку 7 блока 21 адрес первого линейного сргласователя 31, а в ячейку X - код запроса информации, после чего пе- ходит на ожидание завершения приема. После получения сигнала о завершении приема блок 4 пересылает массив информации и-з блока 21 в соответствующий данному устройству нижнего уровня блок 46 памяти и переходит к запросу информации по следующему каналу.

Независимо от .направления передачи после ее завершения блок 15 выра- батывает сигнал прерывания. Причем если команду на обмен выставлял блок 4, то сигнал прерывания появляется на выходе 19 бло.ка 15 и поступает на управляющий вход блока 3, а если команду на обмен выставлял блок 3, то сигнал прерывания появляется на выходе 20 блока 15 и поступает на уп равляющий вход блока 4. ;- , В процессе обмена информацией между блоком 21 и линиями связи блок 3 -работаетв соответствии с программой, занесенной в блок 36 памяти. Алгоритм организации обмена (вид протокола, форматы досыпок, способ контроля и т.д. может быть раз личным. Для примера приводим алгоритм обменапри работе в полудуплексном синхронном режиме, учитывая, что на другом конце канала связи стоит внешнее устройство, работющее по аналогичному протоколу. Блок 3, восприняв сигнал прерывания с бло- ка 15, производит чтение с фиксированной ячейки -t памяти 47, содержащей номер канала связи, записывает его в блок 34 регистров, выбрав тем самым соответствующий линейныйсогласоватёль 31. Затем читает Ячейку X (сбрасывая тем самым сигнал прерывания), анализирует полученную команду и в случае передачи записывает в регистр 69 команд и режимов линейного блока 18 ввода-вывода команду, настраивающую его на передачу и начинает передавать хранящийся в памяти массив данных.

JO

15

0

5

05

0

0

Перед вьщачей в передатчик каждого слова данных, читается регистр 81 состояния линейного блока 28 и анализируется его готовность для передачи. В момент передачи в блоке 3 к каждому слову может быть приформирована служебная информация для осуществления контроля данных в соответствии с выбранным методом контроля (например, « . приформировывается разряд четности или формируется циклический код остатка и т. п. ).

После передачи всего массива блок 3 перестаивает линейный блок 28, на .прием и, читая состояние регистра 81 состояния, организует ожидание с внешнего устройства посылки данных, подтверждающей прием внешним устройством переданного массива.

Блок 3 при получении признака готовности приемника линейного блока 28 считывает данные, переданные внешним устройством, записывает в ячейку V памяти 47 слово, сигнализирующее блок 4 о завершений цикла приемопередачи, в котором формируются признаки досто- верности обмена.

После этого блок 3 снова переходит в режим ожида.ния сигнала прерывания (получение очередной команды с второй магистрали).

Формула из-обретения

1. 5 стройство для обмена данными по а.вт, св. .№ 1012235, о т л и ч а-- ю щ е е с я тем, что, с целью расширения класса решаемых задач, в него введены второй блок микропрограммного управления, блок сопряжения, блок разрешения доступа к магистрали, второй и третий блоки памяти, группа блокор .памяти и второй генератор так- товьк импульсов, причем выход генератора тактовых импульсов соединен с тактовым входом второго блока микропрограммного управления, группа выходов которого через вторую щину адреса с.,оединена с группами адресных входов второго, третьего и группы блоков памяти, с группой адресных выходов блока сопряжения и с второй . группой адресных входов блока связи с магистралью, группа информационных входов-выходов второго блока микропрограммного управления через вторую шину данных соединена с группой информационных входов-выходов второго, третьего и группы блоков памяти.

с первой группой иж ормационных входов-выходов блока сопряжения и с второй группой информационных входов- выходов блока связи с магистралью, группа управляющих входов-выходов второго блока микропрограммного управления через вторую шину управления соединена с группой управляющих входов-выходов второго, третьего и группы блоков памяти, с первым входом блока разрешения доступа к ма-., гистрали, вторыми входом и выходом блока связи с магистралью и с вторым входом бло

ка прерываний, второй выход которого I

соединен с управляющим входом второго блока микропрограммного управления, синхронизирующий вход которого,, соединен с первым выходом блока разрешения доступа к магистрали, выход и вход блока сопряжения соединены соответственно с вторыми входом и выходом блока разрешения доступа к магистрали, а вторые группы управляющих и информационных входов-выходов и группа адресных входов - с соответствующими группами магистральных входов-выходов и входов устройства.

2. Устройство по П.1, о т.л и - чающееся тем, что блок сопряжения содержит две группы три- стабильных элементов И, шесть элементов И, группу элементов И, элемент ИЛИ и элемент задержки, причем первые входы тристабильных элементов первой группы и выходы тристабильных элементов И второй группы соединены с второй группой информационных входов-выходов блока, выходы три- стабильных элементов И первой груп- , пы соединены с первыми входами три- стабипьных элементов И второй груп- пы и с первой группой информационс

20

5

0

ных входов-выходов блока, вторые входы тристабильных элементов И первой и второй групп соединены соответственно с выходами первого и второго элементов И, первые входы которых, первые входы третьего и четвертого элементов И, первый и второй входы элемента ИЛИ и выход пятого элемента И соединены с второй группой управляющих входов-выходов блока, первые входы элементов И группы соединены с второй группой адресных входов блока вторые- входы первого, второго элементов И и элементов .И группы, вход 15 элемента задержки и первый вход пятого элемента И соединены с выходом шестого элемента И, выход элемента задержки соединен с вторыми входами третьего и четвертого элементов И, выходы которых и второй вход пятого элемента И соединены с первой группой управляющих входов-выходов блока, выходы элементов И группы сое-г динены с группой адресных выходов блока, первый вход шестого элемента, И соединен с выходом элемента ИЛИ и .выходом блока, а второй вход - с вхо- дом блока. .

. 3. Устройство по п.1, о т л и - чающееся тем, что блок разрешения доступа к магистрали содержит два элемента И и два элемента НЕ, причем первые входы первого и второго элементов И соединены соответственно с вторым и первым входами блока, выход первого элемента И соединен непосредственно с вторым выходом блока и через первьш элемент НЕ - с вторым входом второго элемента И, выход которого соединен непосредственна с первым выхо-; дом блока и через второй элемент НЕ - с вторым входом первого элемента И.

25

0

/f URIAHS Ю

данны)

Я мине 29

С wuHbi 11 С i nh-b/d с dew(,cppaniopa 35 упрс{8лен(я адреса Ф(4г.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными | 1981 |

|

SU1012235A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для обмена данными | 1988 |

|

SU1599863A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

Изобретение относится к области вычкслительной техники и может быть использовано в вычислительных систе:мах для сопряжения ЭВМ с каналами связи. Целью изобретения является расширение класса решаемых задач для уменьшения времени, затрачиваемого ЭВМ на проведение обмена с устройствами нижнего уровня. Цель достигается тем, что в устройство, содержащее генератор тактовьпс импульсов, блок микропрограммного управления, блок прерываний, линейный блок ввода- вывода, линейные согласователи, ли- . кей ный дешифратор, блок регистров, дешифратор ввода-вывода, блок памяти, управляющий дешифратор, введены вторые генератор тактовых импульсов и блок микропрограммного управления, блок сопряжения, блок разрешения захвата магистрали, второй и третий блоки памяти и группа блоков памяти. 2 з.п. ф-лы, 1 ил. (3 S (Л to 00 со 1C 4 N)

OmSem.

т

ь

„fEIii o

.iГ) I

4

:

Зап., 1Щет .

,,,4. JJ...K шине fid

W О-

ЗДМ

S5

42

ЗДЛУ

Редактор Е.Папп

Составитель В.Вертлиб

Техред О.Сопко Корректор М.Пожо

Заказ 3398/50 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

96

рдм

Фиг, 7

| .Авторское, свидетельство СССР № 101223Э, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-23—Публикация

1984-04-12—Подача