Изобретение относится к вычислительной техники и может быть использовано при организации проверки идентичности без данных- АСУ различного назначения.

Цель изобретения - повышение надежности и быстродействия.

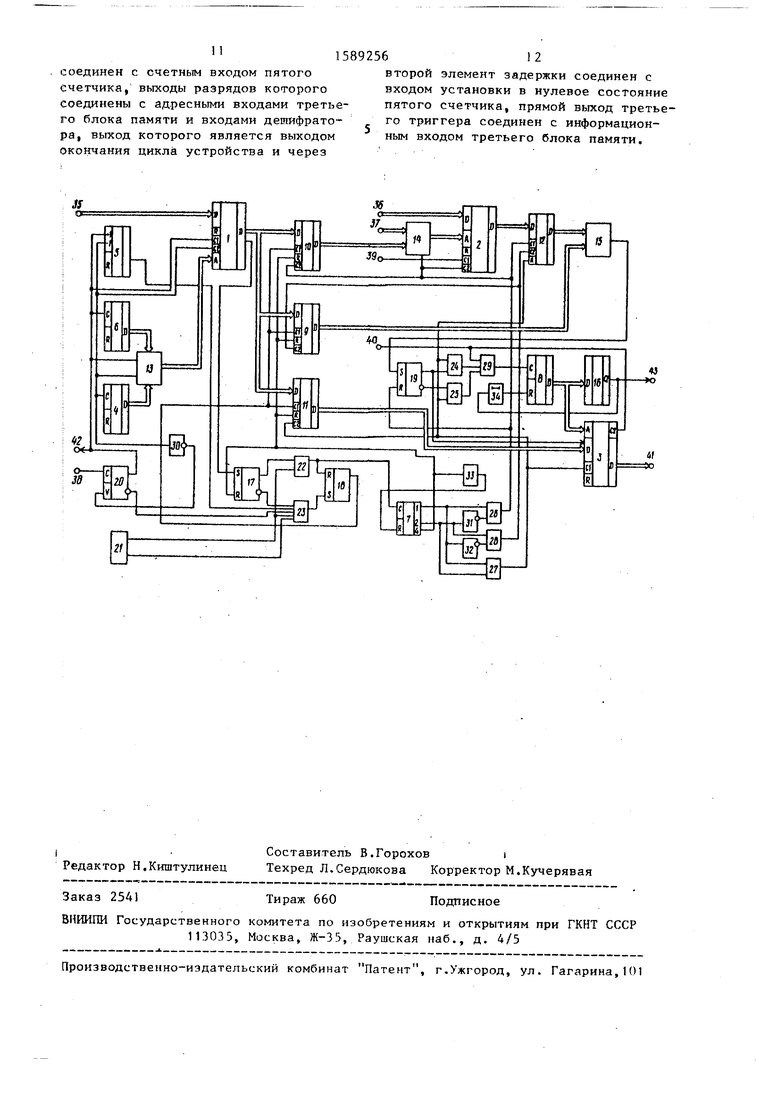

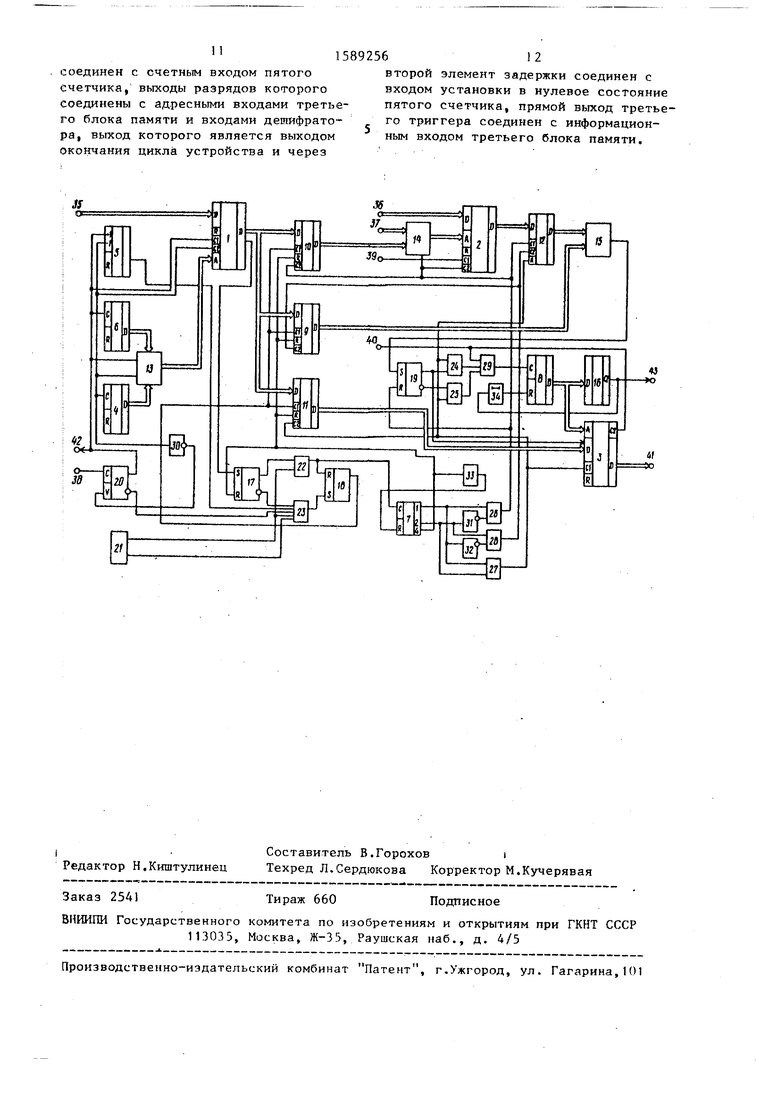

На чертеже представлена схема уст- ройства.

Устройство содержит блоки 1-3 памяти, счетчики 4-8, регистры 9-12, мультиплексоры 13 и 14, элемент 15 сравнения, дешифратор 16, триггеры 17-20, генератор 21 импульсов, элементы И 22-28, элемент ИЛИ 29, элементы НЕ 30-32, элементы 33 и 34 задержки, входы записи информации первого 35 и второго 36 объектов управления.

адресные входы 37, входы управления записью информации первого 38 и второго 39 объектов управления, вход 40 считьгеания, информационные выходы 4J, выход 42 готовности к приему сообщения, выход 43 окончания цикла.

В основу проверки информационной идентичности без данных положены следующие принципы. Все базы данных АСУ работают в реальном масштабе времени, условно разбиваемом на циклы проверки идентичности информации. При этом номера циклов привязаны к временной оси отсчета. Например, если цикл работы устройства составляет 1 ч, то в течение 1 сут номера циклов проверки соответствуют номерам отсчета часов: 1, 2, 3 ч и т.д.

У1

эо :о to

Для сокращения време ге1 проверки информаи юнной идентичности баз данных анализу подлежат следующие их признаки: число сообщений соответствующего вида информации и их контрольная сумма.

С этой целью в каждой базе данных ведется подсчет количества сообщений конкретного вида информации, пришед- ших в пределах контролируемого цикла, и их контрольное суммирование. В устройстве производится проверка ;информационной идентичности без данных АСУ путем сравнения информации основного объекта управления и запасного. Управляющие 38-40 и информационные 35 и 36 входы устройства, а таже информационные 41 и управляющие 42 и 43 выходы устройства и группа адресных входов 37 по соответствующи шинам связаны с автоматизированным рабочим местом системного оператора (АРМ СО не показано).

Устройство работает следующим об- разом.

Подготовка устройства к работе.

Нажатием клавиши Сброс на кла- риатуре АРМ СО на управляющий вход устройства (не показан) поступает импульс, по которому устанавливаются в Нулевое состояние все блоки памяти, регистры, счетчики и триггеры устройства, кроме счетчика,5, который устанавливают в состояние Все единицы. Цепи установки элементов устройства в исходное состояние при подготовке его к работе на чертеже не показаны.

Перед началом цикла сравнения массивов без данных основного и запасных объектов на АРМ СО формируются контрольные массивы, которые записываются в блок 2 памяти устройства, поступая по входу 36 устройства на информационные входы блока 2 памяти, В качестве адресов записи массивов используется код номера цикла и вида информации в проверяемых массивах. Данный код поступает с клавиатуры АРМ СО на адресный вход 37 устройства и далее через мультиплексор-14 на адресные входы блока 2 памяти. Поступающий код тактируется импульсом записи по. входу 39, который поступает на вход записи блока 2 памяти и на управляющий вход мультиплексора 14„ Сообщения от Объектов, базы которых проверяются, через АРМ СО поступалQ

5

0

5

0

5

0

5

ют на информационный вход 35 устройства.

Запись сообщений в блок 1 памяти.

При поступлении сообщения с ин формацией для осуществления проверки идентичности без данных объектов АРМ СО вырабатывает импульсы опроса, которые поступают на вход 38 опроса устройства. При этом, если на V-вход триггера 20 подается нулевой потенци-т. ал, то триггер 20 не реагирует на импульсы опроса по входу 38. Если же на V-вход триггера 20 подается единичный потенциал, то первый импульс, при-, шедщий на С-вход триггера 20 после с снятия запрета на его V-входе, устанавливает его в единичное состояние. На прямом выходе триггера -20 появляется единичный потенциал, который с выхода 42 поступает на АРМ СО, сообщая о готовности устройства к приему информации. Кроме того, импульс с прямого выхода триггера 20 поступает на счетный вход счетчика 6, который формирует адрес записи сообщения в блок 1 памяти. Код адреса с информационного выхода счетчика 6 поступает через мультиплексор 13 (на соответ- ствующий управляющий вход которого поступает разрешающий сигнал с прямого выхода триггера 20) на адресный вход блока 1 памяти, на вход записи которого поступает импульс записи. По сигналу готовности с выхода 42 устройства на вход 35 АРМ СО выдает сйобщение, которое поступает на информационный вход блока 1 памяти. По окончании передачи сообщения АРМ СО вырабатывает импульс конца записи и выдает его на вход 38 устройства, по которому триггер 20 устанавливается в нулевое состояние.

Считывание информации из блока 1 Памяти.

Для формирования импульса считывания на соответствующие входы элемента И 23 поступают разрешающие потенциалы с инверсных выходов триггера 20 (не происходит записи в блок I памяти) и триггера 17 (не осуществляется обработка информации), с выходов генератора 21, а также с выхода . О счетчика 5.

Реверсивный счетчик 5 предназначен для того, чтобы адресный счетчик 4 не обгонял адресный счетчик 6. Так как после включения устройства генератор 21 начинает вырабатывать импуль515892566

сы, то при отсутствии запрета с вько- блока 1 памяти в регистры 9-11, а да О (это выход старшего разряда) также в триггер 17.

реверсивного счетчика 5 началосьВторой импульс с выхода генератобы формирование импульсов считывания, с Р открытый элемент И 22, а, следовательно, адресный счетчик устанавливает в нулевой состояние

4начал считать в то время как ад- триггер 18, а также, поступая на ресный счетчик 6 не зафиксировал ни счетный вход счетчика У, устанав- одного поступления сообщения из АРМ СО ливает в нем число . Таким обра- в блок 1 памяти.Ю ом, на выходе первого разряда счет По входу 41 реверсивный счетчик ика 7 появляется единичный потенци5подсчитывает количество поступив- который поступает через откры- ших в блок 1 памяти сообщений, а по ™ элемент И 26 на вход записи ре- входу -1 - количество обработанных гистра 12, на управляющий вход муль- устройством сообщений. Как только все 15 типлексора 14, на вход считывания бло- пришедшие сообщения будут считаны, с/ памяти и регистра 10. Таким об- выхода О.счетчика 5 на вход эле- , по импульсу с выхода элемента мента И 23 поступает запрет на форми- блока 2 памяти контроль- рование импульса считывания информа- й массив проверяемого вида информации из блока 1 памяти. « переписывается в регистр 12. В каТаким образом, реверсивный счетчик честве адреса считывания использует- 5 запрещает работу устройства на счи- « номера цикла и вида информа- тывание информации при ее отсутст- Ч™ записанный в регистр 10, который ВИИ в блоке 1 памяти.поступает через мультиплексор 14 на

По первому импульсу, поступающему с адресный вход блока 2 памяти, с выхода генератора 21 через элемент ретий импульс, пройдя открытый И 23 на S-вход триггера 18, последний элемент И 22, поступает на счетный устанавливается в единичное состоя- °, счетчика 7 и установит в нем чис- ние. Импульс, сформированный триггером ° выходе второго раз- 18, является импульсом записи для ре- 30 Ряда счетчика 7 появляется единичный гистров 9-11., импульсом считывания потенциал, который поступает через для блока 1 памяти, управляющим сигна- элемент И 28 на входы считывания ре- лом для мультиплексора 13 и счетным гистров 12 и 9. Информация с регист- импульсом для счетчика 4, который фор- Р° « 9 поступает на входы элемен- мирует адрес считываемой, информации 35 сравнения. Если информация не из блока 1 памяти, который с выхода идентична, то на выходе элемента 15 . счетчика 4 поступает через мультиплек- сравнения остается нулевой потенциал, сор 13 иа адресный вход блока 1 памя- информация, записанная в регист- ти. По импульсу считывания сообщение Р 9 и 12, идентична, то на выходе пе1реписывается в регистры 9-11. В ре- 40 элемента 15 сравнения появляется еди- гистр 9 записывается код номера цикла ничньй потенциал, который устанавли- и вида информации, в регистр 10 - ко- ает триггер 19 в единичное состоя- личество сообщений данного вида инфор- ние.

мации за цикл и контрольная сумма Четвертый импульс, пройдя откры- проверяемого массива, в регистр 11 - 45 ™й элемент И 22, поступает на счетный код номера базы данных ( номера объек- «ход счетчика 7. Это будет третий им- та). Кроме того, один бит из кода но- пульс, сосчитанный счетчиком- 7, при мера объекта (логическая единица для том на его выходах первого и второго сообщений по проведению контроля инфор- Разрядов будут единичные потенциалы, мационной идентичности баз данных) ус- SO выходе элемента И 27 появляется танавливает триггер 17 в единичное импульс, который поступает на вход sa- состояние. На его инверсном выходе блока 3 памяти, на вход считьша- появляется нулевой потенциал, тем регистра 11, на R-вход регистра самым запрещается формирование импуль- 2, устанавливая его в нулевое состоя- са считывания информации из блока 1 55 элементов И 24 и 25, памяти.открывая их.

jВ случае, если после сравнения

Таким образом, по первому импульсу элементом 15 сравнения информации ре- осуществляется запись информации из гистров 9 и 12 на его выходе единич10

: 71589256

ный потенциал (информация идентична), то триггер 19 устанавливается в единичное состояние. При этом открыт эле мент .И 24. Импульс с выхода элемента И 27 поступает через открытый элемент И 24 и элемент ИЛИ 29 на счетный вход счетчика 8 На информационном выходе счетчика 8 формируется адрес, по которому в блок 3 памяти записывается из регистра 1 код номера объекта, информационный.массив которого , проверялся. При этом в последний бит кода номера объекта записывается единица с прямого выхода триггера 19, которая показывает, что проверяемый массив запасного объекта и аналогичный массив управляющего объекта идентичны.

В случае, если на выходе элемента 15 сравнения нулевой потенциал (информация регистров 9 и 12 не идентична) , то триггер 19 остается в нулевом состоянии. При этом открыт элемент И 25 и импульс с .выхода элемента 25 И 27 поступает на счетный адресного счетчика 8 через элемент И 25 и элемент ИЛИ 29. По сформированному коду адреса на выходе счетчика 8 в

15

20

запись результата сравнения и номера объекта в блок 3 памяти.

Так как в структуре АСУ количество объектов определено, то после сравнения сообщения от последнего объекта На выходе дешифратора 16 появляется высокий потенциал, по которому через элемент задержки 34 сбрасывается счетчик В. Кроме того, с выхода 43 устройства импульс поступает в АРМ СО. По данному импульсу с нем инициализируются программа считывания информа-. ции из блока 3 памяти устройства. По указанной программе АРМ СО вырабатывает импульсы, которые поступают на вход 40 устройства, проходят через элемент ИЛИ 29 и поступают на счетный вход счетчика 8, на выходе которого формируется код адреса считывания информации. В качестве импульсов считыг вания информации используются импульсы, поступающие с входа 40 устройства на вход считывания блока 3 памяти.

После заполнения счетчика 8 на выходе дешифратора 15 появляется импульс, сообщающий в АРМ СО о том, что считано последнее сообщение (проблок 3 памяти записывается код номера 30 грамма считывания прекращает работу),

а также сбрасывается счетчик 8. Программа АРМ СО обработки полученных данных выдает на средства отображения информации управляющего объекта результаты проверки идентичности дйн- ных и соответствующие рекомендации (не показано).

объекта, информационный массив которого подвергается контролю, а в последний бит кода записывается нуль, отмечая р что информация проверяемого объекта не идентична аналогичной информации управляющего объекта.

Пятый импульс устанавливает в счетчике 7 число 4, при котором на его зыходе третьего разряда появляется единичный потенциал, которым сбрасывается триггер 17 и регистры 9-11. Задержанный элементом 33 задержки импульс с выхода третьего разряда счетчика 7 поступает на R-вход счетчика 7, обнуляя его.

Устройство готово к следующему циклу считывания информации из блока 1 памяти и ее обработке. Если в момент прихода очередных импульсов с генера- тора 21 не осуществляется запись сообщения в блок 1 памяти (есть разрешение с инверсного выхода триггера 20 на на соответствующий вход элемента И 23), а в блоке 1 памяти .есть сообщения (нет запрета с реверсивного счетчика 5 на соответствующий вход элемента И 23), то начинается новый цикл считывания, сравнения информации и

35

Ф

ормула изобретени

40

45

50

Устройство для контроля информационной идентичности объектов управления, содержащее дв а блока памяти, два счетчика, блок сравнения, четыре регистра, три триггера, генератор импульсов, пять элементов И, элемент ИЛИ и два элемента задержки, причем входы записи информа1 ии первого объекта управления устройства соединены с информационными входами первого блока памяти, выходы которого соединены с информационными входами первого, второго и третьего регистров, входы записи которых объединены, выход первого блока памяти соединен с входом установки в единичное состояние первого триггера, прямой и инверсный выходы которого соединены с первыми входами соответственно

запись результата сравнения и номера объекта в блок 3 памяти.

Так как в структуре АСУ количество объектов определено, то после сравнения сообщения от последнего объекта На выходе дешифратора 16 появляется высокий потенциал, по которому через элемент задержки 34 сбрасывается счетчик В. Кроме того, с выхода 43 устройства импульс поступает в АРМ СО. По данному импульсу с нем инициализируются программа считывания информа-. ции из блока 3 памяти устройства. По указанной программе АРМ СО вырабатывает импульсы, которые поступают на вход 40 устройства, проходят через элемент ИЛИ 29 и поступают на счетный вход счетчика 8, на выходе которого формируется код адреса считывания информации. В качестве импульсов считыг вания информации используются импульсы, поступающие с входа 40 устройства на вход считывания блока 3 памяти.

После заполнения счетчика 8 на выходе дешифратора 15 появляется импульс, сообщающий в АРМ СО о том, что считано последнее сообщение (проФ

ормула изобретени

0

5

0

Устройство для контроля информационной идентичности объектов управления, содержащее дв а блока памяти, два счетчика, блок сравнения, четыре регистра, три триггера, генератор импульсов, пять элементов И, элемент ИЛИ и два элемента задержки, причем входы записи информа1 ии первого объекта управления устройства соединены с информационными входами первого блока памяти, выходы которого соединены с информационными входами первого, второго и третьего регистров, входы записи которых объединены, выход первого блока памяти соединен с входом установки в единичное состояние первого триггера, прямой и инверсный выходы которого соединены с первыми входами соответственно

первого и второго элементов И, вторые входы которых объединены и подключены к первому выходу генератора импульсов, выход первого элемента И соединен с входом установки второго триггера в нулевое состояние, выходы второго блока памяти соединены с ин-формационными входами четвертого регистра, выходы разрядов которого и выходы разрядов первого регистра сое,- динены с входами соответственно первой и второй групп элемента сравнения, выход которого соединен с входом установки третьего триггера в единичное состояние, прямой и инверсный выходы которого соединены с первыми входами соответственно третьего и четвертого элементов И, входы которых соединены соответственно с первым и вторым входами элемента ИЛИ, отличающееся тем, что, с целью повышения надежности и быстродействия, в него введены третий блок памяти, третий, четвертый и пятый счет- чики, два мультиплексора, четвертый триггера, шестой и седьмой элементы И и три элемента НЕ, причем второй выход генератора импульсов соединен с третьим входом второго элемента И, выход которого соединен с входом ус тановки второго триггера в единичное состояние, прямой выход которого соединен с входом записи первого регистра, входом считывания первого блока памяти, счетным входом первого счетчика, вычитающим входом второго счетчика, первым управляющим входом первого мультиплексора и через первый элемент НЕ - с входом.разрешения записи четвертого триггера, инверсный выход которого соединен с четвертым входом второго элемента И, прямой выход четвертого триггера является выходом готовности устройства и сое динен с счетным входом третьего счет

чика, входом записи первого блока памяти, вторым управляющим входом первого мультиплексора и суммирующим входом второго счетчика, выход старшего разряда которого соединен с пятым входом второго элемента И, выходы разрядов первого и третьего счетчиков со- единены соответственно с первой и второй группами информационных входов первого мультиплексора, выходы которого соединены с адресными входами первого блока памяти, вход управления записью информации первого объекта

0

5

5

0 ,

управления устройства соединен с син- хровходом четвертого триггера, выходы разрядов второго регистра соединены с первой группой информационных входов второго мультиплексора, вторая группа информационных входов которого является группой адресных входов устройства, входы записи информации второго объекта управления устройства соединены с информационными входами второго блока памяти, адресные входы которого подключены к выходам второго мультиплексора, первый управляющий вход которого является входом управления записью информации второго объекта управления устройства и соединен с входом записи второго блоке памяти, вход записи четвертого регист- 0 ра объединен с вторым управляющим входом второго мультиплексора, входами считывания второго блока памяти, второго регистра и входом установки третьего триггера в нулевое состояние и подключен к выходу пятого элемента И, выход первого элемента И соединен с счетным входом четвертого счетчика, выход первого разряда которого соединен с первыми входами пятого и шестого элементов И и через второй элемент НЕ - с первым входом седьмого элемента И, выход которого соединен с входами считывания первого и четвертого регистров, выход второго разряда четвертого счетчика соединен с вторыми входами шестого и седьмого элементов И и через третий элемент НЕ - с вторым входом пятого элемента И, выход третьего разряда четвертого счетчика соединен с входами установки в нулевое состояние первого, второго и третьего регистров и первого триггера и через первый элемент задержки - с входом установки в нулевое состояние четвертого счетчика, выход шестого элемента И соединен с вторыми входами третьего и четвертого элементов И, входом установки в нулевое состояние четвертого регистра5 входом записи третьего блока памяти и входом считывания третьего регистра, выходы разрядов которого соединены с информационными входами третьего блока памяти, выходы которого являются информационными выходами устройства, вход считывания устройства соединен с входом считывания третьего, блока памяти и третьим входом элемента ИЛИ. выход которого

0

5

0

5

158925612

соединен с счетным входом пятого второй элемент задержки соединен с

счетчика, выходы разрядов которого соединены с адресными входами третьего блока памяти и входами дешифратора, выход которого является выходом окончания цикла устройства и через

входом установки в нулевое состояни пятого счетчика, прямой выход треть го триггера соединен с информационным входом третьего блока памяти.

входом установки в нулевое состояние пятого счетчика, прямой выход третьего триггера соединен с информационным входом третьего блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигнала прерывания | 1984 |

|

SU1241242A1 |

| Устройство формирования сигнала прерывания и обмена | 1985 |

|

SU1269133A1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Устройство для обмена информацией | 1989 |

|

SU1644149A1 |

| Устройство для обработки сообщений | 1990 |

|

SU1803919A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1619326A1 |

| Устройство формирования сигнала прерывания | 1983 |

|

SU1112365A1 |

| Устройство формирования сигнала прерывания | 1985 |

|

SU1290327A1 |

| Устройство для ввода информации от датчиков | 1990 |

|

SU1691828A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

Изобретение относится к вычислительной технике и может быть использовано при организации идентичности баз данных (БД) АСУ различного назначения. Цель изобретения - повышение надежности и быстродействия. Устройство содержит блоки памяти (БП), счетчики, регистры, мультиплексоры, элемент сравнения, дешифратор, триггеры, генератор импульсов, элементы И, элемент ИЛИ, элементы НЕ, элементы задержки. В устройстве производится проверка информационной идентичности БД АСУ путем сравнения информации основного объекта управления (ОУ) и запасного. Число сообщений соответствующего вида информации и их контрольная сумма от основного и запасного ОУ записываются соответственно в БП, а затем по мере их поступления сравниваются в те интервалы времени, когда устройство не занято записью очередного сообщения. 2 ил.

| Патент США № 4327410, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Авторское свидетельство СССР № 1233678, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1990-08-30—Публикация

1988-10-12—Подача