Устройство относится к области информационно-измерительной техники и может быть использовано в системах сбора и передачи измерительной информации.

Известно адаптивное информационное устройство, содержащее блок сжатия информации, информационные входы которого подключены к измерительиым датчикам, буферный запоминающий блок, выходы которого соединены соответственно с блоком контроля и выходным блоком, который представляет собой старт-стопный магнитофон 1.

Недостатком устройства является малая экоиомичность, поскольку на включенный выходной блок поступает одно и то же количество данных вне зависимости от активности изменения измеряемого ироцесса. Таким образом, магнитный носитель выходного блока расходуется неэффективно.

Ближайшим по техиической сущности к данному устройству является адантивное устройство для сбора и обработки ииформации, содержащее блок сжатия информации, информационные входы которого подключены к датчикам и задатчику времеии, уиравляющие входы соединены соответственно с первым выходом блока контроля и с выходом синхронизатора, который через носледовательно соединенные делитель частоты и элемеит заирета подключеи к уиравляющему входу буферного

2

запоминающего блока, вход которого соединен с выходом блока сжатня информации, выход буферного запоминающего блока соединен с выходным регнстром, выходы адресных счетчиков записи и считывания буферного запоминающего блока подключены к соотвегствующим входам блока контроля, второй, третий и четвертый выходы которого соединены соответственно с управляющим входом элемеита заирета. с инверсным и прямым входами иервого триггера, прямо выход которого подключен к входу блока, выход которого с выходом хстройства 2.

Б устройстве на участках слабого 3менения параметров выходной блок ир И мает меиьшее чис.то данных, чем на участках акт вного изменения, то есть тех, ;оторые как раз 1 необход мо анализ ровать на стороне. Однако нолность о участк малого 1зменен я параметров в устройстве е удаетея, поскольку в иротивиом теряется временная р вязка параметров.

Это знач ггельно сн 1жает функц оиальные возможност устройства.

Целью 13обретения являетея фуикц ональных возможностей устройства.

Цел1) дост гается тем, что в устройство для сбора н обработк нформа U n введены де Н фратор, элемент задержкн,

ключи, триггер и регистр адреса времени, выход которого подключен через первый ключ к адресномз счетчику считывания буферного запоминающего блока, вход управления первого ключа соединен с выходом включения выходного блока и прямым входом второго триггера, инверсный вход которого подключен к выходу выключення выходного б,:1ока, -ipsiмой выход второго трнггера еоединен с нервым унравляющнм входом второго ключа, информационный вход которого подключен к выходу выходного регистра, а выход - к входу выходного блока, второй унравляющий вход второго ключа соединен с прямым выходом первого трнггера н входом элемента задержкн, выход которого соедннен с первым управляющим входом третьего ключа, выходы адресных счетчиков запнсп и счптыванпя буферного запоминающего блока подключены соответственно к входам третьего и четвертого ключей, выходы когорых соедпнепв со входамп регистра адреса временн, вв1ход блока слчатпя информации через дешифратор подключен к первому управляющему входу четвертого ключа, второн унравля ощпй вход которого нодключен к инверсному выходу первого трпггсра, третий выход блока контроля соедннен с вторым управляющим входом третьего ключа.

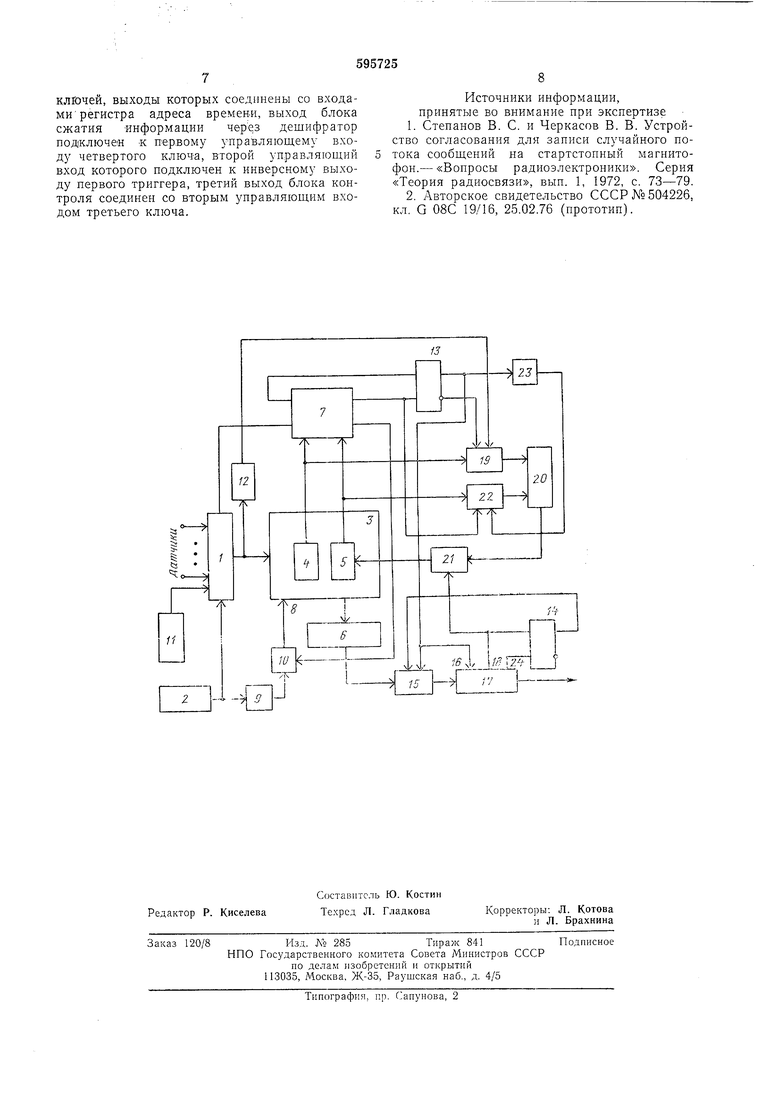

На чертеже представлена блок-схема устройетва.

Схема содерж1гг i - блок сжагня информации, 2 - синхронизатор, о - буферный заномпнающнп блок, 4 - адресньи счетипс запнсп буферного запомппающсго блока, 5- адресный счетчпк ечнтывания буфериого заномннающего блока, 6 - выходной perjicip, 7 - блок контроля, 8 - управлягощнн вход буферного заноминающего блока, 9--делнтель частоты, 10-элемент занрета, И-задатчнк времепп, 12 - дешифратор, i3--nepВЫ11 трщгер, 14 - второй грпггер, 15 --второ: ключ, 16 - вход режпма, 1/ - выходной блок, 18 - выход включеппя, 19 - четвертый ключ,. 20 - регистр адреса времепп, 21 - первый ключ, 22 - третий ключ, 23 - элемент задержки, 24 - выход выключения.

Работа адаптпвного уетройства нронсходнт следуЮЩ|НМ образом.

На пнформационные входы блока 1 сжатня нпформацпн поступают сигналы датчнков. Г1снользуя унравляющне енгпалы синхронизатора 2, блок 1 сжатня ннформацнп онределяет сущеетвениость нлн пзоыточность сигналов датчнков. Существенные сигналы нередаютея в б)чрерный запоМ1П-1ающий блок 3 и записываются поеледовательпо в его ячейки. Соетавными частями буферного заномпнающего блока должны являться адресный счетчик занпси 4 и адресный счетчик считывания 5. Адресный счетчик записи 4 указывает помер яче11ки буферного заноминающего блока 3, куда нронзводнтся заннсь еущественпого енгнала. При каждой записи содержимое адресного счетчика заппеи 4 увеличивается на единицу. Адресный счетчпк счптывання 5 указывает номер ячейки буферного запомииающего блока 3, из которой записанные ранее еущеCTBCHHBie данные ечитываются на спениальный выходной рс1истр 6. Такнм образом, чтобы онределнт) cGnteo количество ячеек в буферном зaпoм ;I;;иoнle : блоке 3 занятых суидеетвеииым дапиымн д;.)ст;:точпо вычесть нз содержимого счегчнка 4 содержимое ечетчика 5, то есть блок контроля 7, онределяющнй количество заполненных в буферном запоминающем блоке 3 существеппых еигпалов, мо}кет быть вынолпеп по схеме вычитателя. Считываиие из буферного заномннающего блока 3 на выходной региетр 6 производится при иоетуплепни импульса на специальный управляющий вход 8 буферного запоминающего блока 3. На вход 8 нодаютея импульсы сиихроннзатора 2, частота которых умепьщена делителем 9 в необходнмое число раз. Еслн в буферном заномннаюш.ем блоке 3 считана информация нз всех ячеек, то блок контроля 7, воздейетвуя на спецнал1Я1ый элемент запрета 10, запрещает поступление имнульеов на у:фавляющий вход 8, ц считывание из буферного заномннающего блока 3 не производится.

Блок контроля 7 , воздействовать и на блок 1 сжатия информации, чтобы не допуетнть режима заипси ji буферный запоминающий блок 3, в KoTOpoii все ячейкн заняты сундеетвеннымн дапиымп, ожндающи:мп счнтыв;1ния.

Одннм из датчиков, подключенных к блоку 1 сжатия информации, является задатчпк времеип 11. Информация па его выходе меияется ОЛ1П1 раз в секуп;,у (n;iii за другой выбранный нромежуток вре.гени) п выражает собой время измерепия. Когда еигнал задатчпка ;ремепн 11 изменяется, сн етановится сущеeiTseniibiM н попадает па выход блока 1 сжатия ии.рормап,;, где tn-o выделнть, ()-;деп1Н(ррпровав, i;anpH: Up, адрееную часть. Згой ivjjiii слу ;-лг1 дстнпсЬратор 12.

В состав адант ;вного стройства входят первый 13 п второй 14 триггеры. Нри включс1;ип уетройстиа оба orni паходятся в пулек) еостсяпни. Низкий е1Нпал па еднннчном В1)1ходе первого триггера 13 закрывает ключ 15 и, попадая :ia вход рея-льма 16 выходного блока 17, обеслсч1П5ает его выключешше сос-1Ч).

Нервьн триггер 13 перекидывается в едиппн нри |1ахождепни в буферном запомппглоп ем б;юке 3 оиределен1ЮГо числа еундеегиенпых еигпа;1ов, ожидающ1 х считывания, а eiOBa в пуль устаиавлппается при пекотором мепьнюм заполпепип буферпого запомппающего бло1:а 3. TpniTep 13 переключает нмиульсь:, выдаваемые блоком контроля 7. Носкольку малым занолнения.м буферного, запомипа ОП,его блока 3 соответетвуют моменты малой aKTi.iBHOCTH комплекса измеряе.мых параметров, то можпо сделать вывод, что соетойние трпггера 13 указывает на то, как изменяются входные параметры. Однако при этом существует временная задержка; вначале наступает режим активного изменения входных сигналов, который необходимо передать в выходной блок 17, затем в буферном запоминающем блоке 3 скапливается достаточно больщое число существенных сигналов и триггер 13 переходит в единичное состояние, при котором выходной блок начинает выходить на режим, обеспечивающий возможность записи. При выходе на этот режим на выходе включения 18 появляется импульс, который перебрасывает в единицу триггер 14, после чего на обоих управляющих входах ключа 15 оказываются единичные потенциалы, и на блок 17 осуществляется передача существенных сигналов.

Для1 того чтобы с больщой вероятностью захватить начало участка активного изменения входных параметров и обеспечить правильную временную привязку, применяется следующий метод,

В устройство введен ключ 19, соединяющий адресный счетчик записи 4 со специальным регистром 20 адреса времени. К управляющим входам ключа 19 подключены иулевой выход первого триггера 13 и выход дешифратора 12. Таким образом, в регистр 20 в периоды низкой активности входных процессов записывается адрес ячейки буферного запоминающего блока 3, в котором хранится слово с информацией о Бремер и - с секундной информацией. В момент включения выходного блока 17 на его выходе 18 включения выделяется импульс. Он открывает ключ 21 - и в адресный счетчик считывания 5 nepenncoiвается содержимое регистра 20 адреса времени, то есть первым словом, которое поступит на включенный выходной блок 17, будет слово с информацией о номере последней секунды, в начале которой измерительные параметры еще не вышли на участок активиого изменения. Далее в выходной блок поступает измерительная информация, записанная на той же секунде и следующих за ней, пока разность содержимого адресиых счетчиков записи 4 и считывания 5, определяемая блоком 7 контроля, не достигнет уровня, выбранного в качестие показателя возраста к невысокой активности измеряемых процессов. При этом блок 7 выдает импульс, иереключающий в нуль триггер 13 и иоетупающий на управляющий вход ключа 22. На другом управляющем входе ключа 22 при переключении триггера 13 также присутствует высокий сигнал, обеспечивающийся наличием элемента 23 задержки на время импульса (если триггер 13 обладает свойством устанавливаться в нуль задиим фронтом установочного имиульса, иаличпе элемента 23 не обязательно). При открывании ключа 22 на регистр 20 адреса времени иоступает содержимое адресного счетчика считывания 5. После переключения триггера 13 в нуль, запись на выходной блок 17 прекращается, ПОСКОЛЬКУ запирается ключ 15. Затем выходной блок 17 переходит в режим

выключения, которьи заканчивается появлением импульса на выходе выключения 24, переключающего в нуль триггер 14. Если следующий выход нараметров на участок активного из.меиения ироизошел до момента начала новой после выключения выходного блока 17 секунды, то в адресный счетчик 5 будет при включении переписано его нрежнее содержимое. При этом запись данных в

выходной блок будет просто продолжена.

Применение предлагаемого адаптивного устройства для сбора и обработки информации позволит снизить требования ио быетродействию выходного блока и в случае использования на передающей стороне магнитофона в 2-f-3 раза уменьшить расход носителя.

Формула изобретения

Адаптивное устройство для сбора и обработки информации, содержащее блок сжатня информации, информационные входы которого подключены к датчикам и задатчику вреЛ1ен ;, зправляющие входы соединеиы соответственно с первым выходо.м блока контроля и с выходом синхронизатора, который через поеледовательно соединенные делитель частоты и элемент заирета подключен к управляющему входу буферного запоминающего блока,

вход которого соединен с выходом блока сжатия информации, выход буферного запоминающего б,чока соединен с выходным регистром, выходы адресных счетчиков заииси и считывания буфериого заиоминающего блока

подключены к соответствующим входам блока контроля, второй, третий и четвертый выходы которого соединены соответственпо с управляющим входом элемента заирета, с инверсным и ирямым входами первого триггера,

ирямо11 выход которого подключен к входу режима выходного б.юка, выход которого соединен с выходом устройства, отличающееся тем, что, с д.мью расширения функциональных возможностей устройства, в него

введены дешифратор, элемент задержки, ключи, триггер и регистр адреса времени, выход которого подключен через первый ключ к адресному счетчику считьшаиия буферного заио.микающего блока, вход управлсиия первого ключа соединен с выходом вк.почеиия выходного блока и прямы.ч входом второго триггера, инверсный вход которого подключен к выходу выключения выходного б.юка, иря.мой выход второго триггера соедппсн с первым

управляющим входом второго ключа, информациоииый вход которого подключен к выход выходного регистра, а выход-ко входу Быход1юго блока, второй управляюихий вход второго ключа соед1;;1е с iipH ibnt выходом

первого триггера и Бxoдo i элемента задержки, выход которого соедииеи е ервым управляющим входом третьего ключа, выходы адресных счетчиков записи и считывания буфериого запоминающего Г),;ока подключены соответственно ко входам третьего и четвертого

ключей, выходы которых соединены со входамирегистра адреса времени, выход блока сжатия информации через дешифратор подключен к первому управляющему входу четвертого ключа, второй управляюн1,ий вход которого подключен к инверсному выходу первого триггера, третий выход блока контроля соединен со вторым управляющим входом третьего ключа.

Источники информации, принятые во внимание при экспертизе

1.Степанов В. С. и Черкасов В. В. Устройство согласования для записи случайного потока сообщений на стартстопный магнитофон.- «Вопросы радиоэлектроники. Серия «Теория радиосвязи, вып. 1, 1972, с. 73-79.

2.Авторское свидетельство СССР №504226, кл. G 08С 19/16, 25.02.76 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1981 |

|

SU1008793A1 |

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363309A1 |

| Устройство для контроля оперативной памяти | 1986 |

|

SU1401520A2 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Многокоординатный цифровой интерполятор | 1984 |

|

SU1200246A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1019495A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

Авторы

Даты

1978-02-28—Публикация

1976-06-07—Подача